查询TPS40190DRCTG4供应商

捷多邦,专业PCB打样工厂,24小时加急出货

TPS40190

NSTRUMENTS

**TEXAS**

SLUS658A-JULY 2005-REVISED AUGUST 2005

## LOW PIN COUNT SYNCHRONOUS BUCK CONTROLLER

### **FEATURES**

- Input Operating Voltage Range: 4.5 V to 15 V

- Reference 0.591 V ±1%

- Voltage Mode Control

- Internal 5-V Regulator For Internal Housekeeping, Driver Power and Light External Loads

- Selectable Short-Circuit Protection

Thresholds

- Pre-Bias Ouput Safe

- Fixed Switching Frequency of 300 kHz

- Internal Soft-Start

- Small 3 mm × 3 mm, 10-Pin SON Package

- Bootstrapped Drivers for N-Channel MOSFET

- Adaptive Anti-Cross Conduction

- Internal Bootstrap Diode

- 1.2-A Drivers for Decreased Switching Loss

#### **APPLICATIONS**

- Cable modem CPE

- Digital Set Top Box

- Graphics/Audio Cards

- Entry-level and Mid-Range Servers

## DESCRIPTION

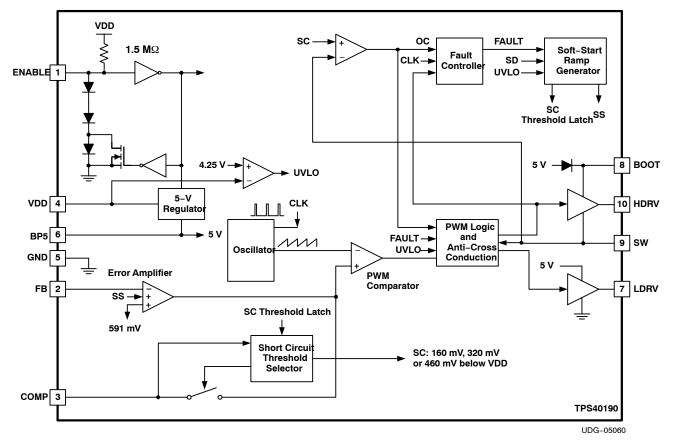

The TPS40190 is a cost-optimized synchronous buck controller that operates from 4.5 V to 15 V nominally, and implements a fixed frequency voltage mode power supply. The controller uses an adaptive anti-cross conduction scheme to prevent both the high-side and the rectifier MOSFET to be turned on at the same time, preventing shoot through current in the two MOSFETs.

The controller also provides a short circuit protection threshold that is user selectable between one of three values. The protection level is set with a single external resistor connected from COMP to GND. During start-up, the impedance connected to COMP is sensed, and the information is decoded to select one of the three thresholds. When the controller senses an output short circuit, both MOSFETs are turned off and a timeout period is observed before attempting to restart. This provides limited power dissipation in the event of a sustained fault.

The TPS40190 provides strong drivers to minimize switching losses in the power stage, reducing heat build up in the MOSFETs and allowing larger MOSFETs to be used without undue switching time penalty.

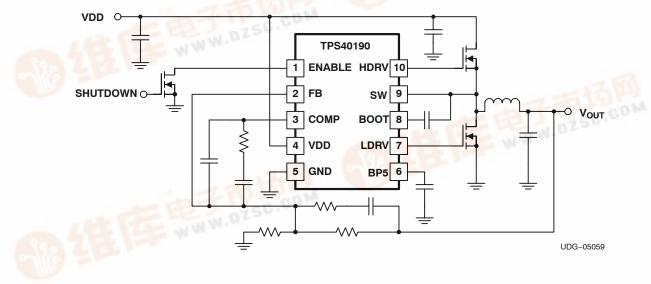

#### SIMPLIFIED APPLICATION DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

| ORDERING INFORMATION               |                   |              |  |  |  |  |  |

|------------------------------------|-------------------|--------------|--|--|--|--|--|

| T <sub>A</sub> PACKAGE PART NUMBER |                   |              |  |  |  |  |  |

| -40°C to 85°C                      | Plastic DRC (SON) | TPS40190DRCR |  |  |  |  |  |

| -40 C 10 85 C                      | Flastic DHC (SON) | TPS40190DRCT |  |  |  |  |  |

The TPS40190 is available taped and reeled only. Use large reel device type R to order quantities of 3000 units per reel. Use small reel device type T to order quantities of 250 per reel.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                  |                         |                                                           | TPS40190     | UNIT |

|------------------|-------------------------|-----------------------------------------------------------|--------------|------|

| V <sub>DD</sub>  |                         | VDD                                                       | –0.3 to 16.5 |      |

|                  |                         | SW                                                        | -5 to 22     |      |

|                  | Input voltage range     | BOOST-SW, HDRV-SW (differential from BOOST or HDRV to SW) | -0.3 to 6    | V    |

|                  |                         | COMP                                                      | -0.3 to 3    |      |

|                  |                         | FB, BP5, LDRV, ENABLE                                     | –0.3 to 6    |      |

| TJ               | Operating junction temp | -40 to 125                                                | - °C         |      |

| T <sub>stg</sub> | Storage temperature     |                                                           | –55 to 150   |      |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATINGS**

| PACKAGE | R <sub>θJA</sub> High-K Board <sup>(1)</sup><br>(°C/W) | R <sub>θJC</sub> <sup>(2)</sup><br>(°C/W) |

|---------|--------------------------------------------------------|-------------------------------------------|

| DRC     | 47.9                                                   | 14.1                                      |

(1) The JEDEC High-K (2s2p) board design used to derive this data was a 3-inch x 3-inch (7.5-cm x 7.5-cm), multilayer board with one-ounce internal power and ground planes and two-ounce copper traces on top and bottom of the board.

(2) The junction-to-case impedance is measured from the die to the thermal pad on the device package.

#### **RECOMMENDED OPERATING CONDITIIONS**

|                |                                | MIN | NOM MAX |     |

|----------------|--------------------------------|-----|---------|-----|

| $V_{DD}$       | Input voltage                  | 4.5 | 15      | V   |

| T <sub>A</sub> | Operating free-air temperature | -40 | 85      | 5°C |

#### **ELECTRICAL CHARACTERISTICS**

$T_A = -40^{\circ}C$  to 85°C,  $V_{VDD} = 12 V_{dc}$ ,  $T_A = T_J$ , all parameters at zero power dissipation (unless otherwise noted)

|                       | PARAMETER                                         | TEST CONDITIONS                                                          | MIN | TYP  | MAX  | UNIT    |  |

|-----------------------|---------------------------------------------------|--------------------------------------------------------------------------|-----|------|------|---------|--|

| REFEREN               | NCE                                               |                                                                          |     |      |      |         |  |

| V                     | Feedback voltage range                            | $0^{\circ}C \le T_{J} \le 85^{\circ}C$                                   | 585 | 591  | 597  | m\/     |  |

| V <sub>FB</sub>       | Feedback voltage lange                            | $-40^{\circ}C \le T_{J} \le 85^{\circ}C$                                 | 582 | 591  | 597  | mV      |  |

| INPUT SU              | JPPLY                                             |                                                                          |     |      |      |         |  |

| V <sub>VDD</sub>      | Input voltage range                               |                                                                          | 4.5 |      | 15.0 | V       |  |

|                       | Operating ourrant                                 | V <sub>ENABLE</sub> = 2.5 V, Outputs switching                           |     | ·    | 2.5  | mA      |  |

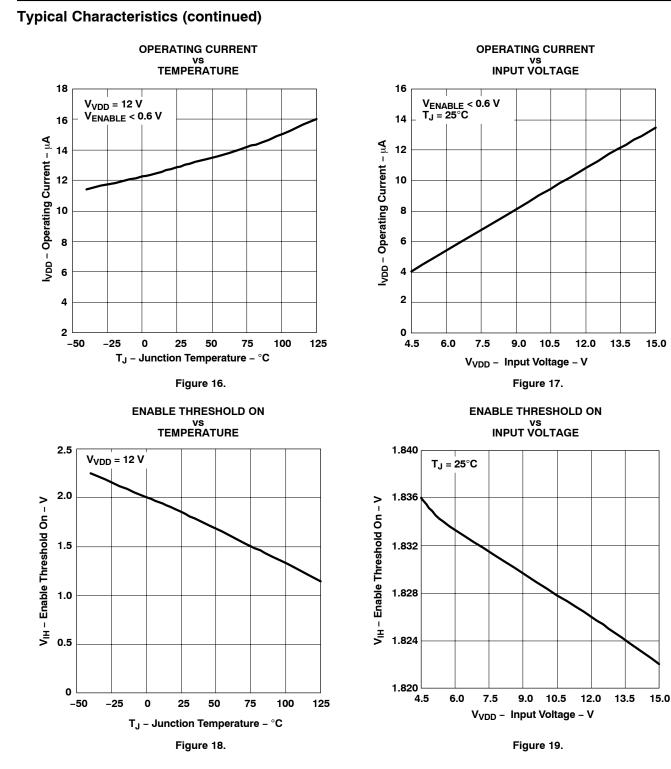

| I <sub>VDD</sub>      | Operating current                                 | V <sub>ENABLE</sub> = 0.6 V                                              |     |      | 20   | μA      |  |

| ON BOAF               | RD REGULATOR                                      | · ·                                                                      |     |      |      |         |  |

| V <sub>5VBP</sub>     | Output voltage                                    | V <sub>VDD</sub> > 6 V, I <sub>5VBP</sub> ≤ 10 mA                        | 5.1 | 5.3  | 5.5  | V       |  |

| V <sub>DO</sub>       | Regulator dropout voltage                         | $V_{VDD}$ - $V_{BP5}$ , $V_{VDD}$ = 5 V, $I_{BP5} \le 25 \text{ mA}$     |     | 270  | 400  | mV      |  |

| I <sub>SC</sub>       | Regulator current limit threshold                 |                                                                          | 40  |      |      | mA      |  |

| I <sub>BP5</sub>      | Average current <sup>(1)</sup>                    |                                                                          |     |      | 40   |         |  |

| OSCILLA               | TOR                                               | · ·                                                                      | ,   |      |      |         |  |

| f <sub>SW</sub>       | Switching frequency                               |                                                                          | 240 | 300  | 360  | kHz     |  |

| V <sub>RMP</sub>      | Ramp amplitude <sup>(2)</sup>                     |                                                                          |     | 0.75 |      |         |  |

| V <sub>VALLEY</sub>   | Valley voltage <sup>(2)</sup>                     |                                                                          |     | 0.5  |      | V       |  |

| PWM                   |                                                   |                                                                          | ,   |      |      |         |  |

| D <sub>MAX</sub>      | Maximum duty cycle <sup>(2)</sup>                 |                                                                          | 85% |      |      |         |  |

| t <sub>ON(min)</sub>  | Minimum controlled pulse <sup>(2)</sup>           |                                                                          |     |      | 130  |         |  |

|                       | HDRV off to LDRV on                               |                                                                          |     | 50   |      | ns      |  |

| t <sub>DEAD</sub>     | Output driver dead time                           | LDRV off to HDRV on                                                      |     | 25   |      |         |  |

| SOFT-ST               | ART                                               |                                                                          |     |      |      |         |  |

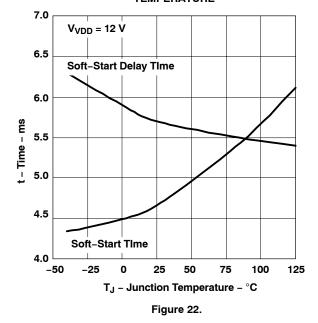

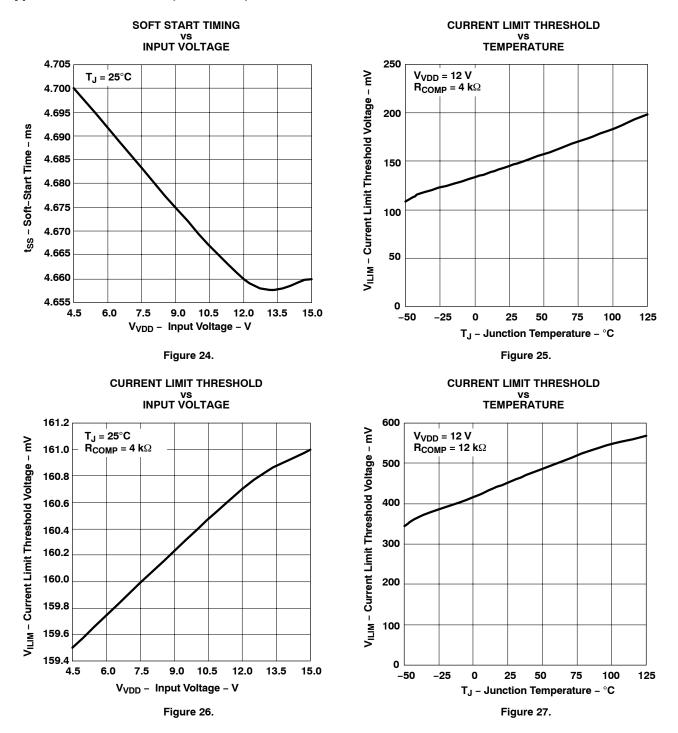

| t <sub>SS</sub>       | Soft-start time                                   |                                                                          | 3.0 | 4.7  | 7.0  |         |  |

| t <sub>SSDLY</sub>    | Soft-start delay time <sup>(3)</sup>              |                                                                          |     | 6    |      | ms      |  |

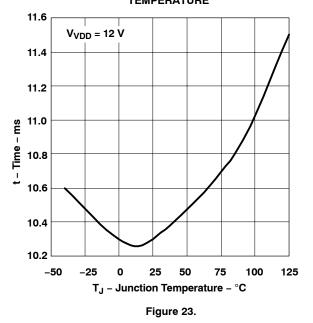

| t <sub>REG</sub>      | Time to regulation                                |                                                                          |     | 10.5 |      |         |  |

| ERROR A               | MPLIFIER                                          |                                                                          | ,   |      |      |         |  |

| GBWP                  | Gain bandwidth product <sup>(2)</sup>             |                                                                          | 5   |      |      | MHz     |  |

| A <sub>OL</sub>       | DC gain <sup>(2)</sup>                            |                                                                          | 60  |      |      | dB      |  |

| I <sub>IB</sub>       | Input bias current (current out of FB pin)        |                                                                          | 100 |      | 0    | nA      |  |

| I <sub>EAOP</sub>     | Output source current                             | V <sub>FB</sub> = 0 V                                                    | 1   |      |      |         |  |

| I <sub>EAOM</sub>     | Output sink current                               | V <sub>FB</sub> = 2 V                                                    | 1   |      |      | mA      |  |

| SHORT C               | IRCUIT PROTECTION                                 |                                                                          | ,   |      |      |         |  |

| t <sub>PSS(min)</sub> | Minimum pulse during short circuit <sup>(2)</sup> |                                                                          |     |      | 250  |         |  |

| t <sub>BLNK</sub>     | Blanking time <sup>(2)</sup>                      |                                                                          | 100 | 140  | 180  | ns<br>) |  |

| t <sub>OFF</sub>      | Off-time between restart attempts                 |                                                                          | 25  | 95   |      | ms      |  |

|                       |                                                   | $R_{COMP(GND)} = OPEN, T_{J} = 25^{\circ}C$                              | 256 | 320  | 384  |         |  |

| V <sub>ILIM</sub>     | Short circuit comparator threshold voltage        | $R_{COMP(GND)} = 4 \text{ k}\Omega, T_{J} = 25^{\circ}\text{C}$          | 128 | 160  | 192  | mV      |  |

|                       | -                                                 | $R_{COMP(GND)} = 12 \text{ k}\Omega, \text{ T}_{J} = 25^{\circ}\text{C}$ | 368 | 460  | 552  |         |  |

(1) 40 mA is the current available for MOSFET gate drive, the device itself and any external loads. The sum of these must not exceed 40 mA.

(2) Ensured by design. Not production tested.

(3) The delay time is the time delay from application of power to the device or from assertion of ENABLE until the output begins to rise.

#### **ELECTRICAL CHARACTERISTICS (continued)**

$T_A = -40^{\circ}C$  to 85°C,  $V_{VDD}$ = 12  $V_{dc}$ ,  $T_A = T_J$ , all parameters at zero power dissipation (unless otherwise noted)

|                      | PARAMETER                                 | TEST CONDITIONS                                     | MIN  | TYP  | MAX  | UNIT |  |  |  |

|----------------------|-------------------------------------------|-----------------------------------------------------|------|------|------|------|--|--|--|

| OUTPUT DRIVERS       |                                           |                                                     |      |      |      |      |  |  |  |

| R <sub>HDHI</sub>    | High-side driver pull-up resistance       | $V_{BOOT}$ - $V_{SW}$ = 4.5 V, $I_{HDRV}$ = -100 mA |      | 3    | 6    |      |  |  |  |

| R <sub>HDLO</sub>    | High-side driver pull-down resistance     | $V_{BOOT}$ - $V_{SW}$ = 4.5 V, $I_{HDRV}$ = 100 mA  |      | 1.5  | 3.0  | Ω    |  |  |  |

| R <sub>LDHI</sub>    | Low-side driver pull-up resistance        | I <sub>LDRV</sub> = -100 mA                         |      | 2.5  | 5.0  | 52   |  |  |  |

| R <sub>LDLO</sub>    | Low-side driver pull-down resistance      | I <sub>LDRV</sub> = 100 mA                          |      | 0.80 | 1.50 |      |  |  |  |

| t <sub>HRISE</sub>   | High-side driver rise time <sup>(4)</sup> |                                                     |      | 15   | 35   |      |  |  |  |

| t <sub>HFALL</sub>   | High-side driver fall time <sup>(4)</sup> |                                                     |      | 10   | 25   |      |  |  |  |

| t <sub>LRISE</sub>   | Low-side driver rise time <sup>(4)</sup>  | $C_{LOAD} = 1 \text{ nF}$                           |      | 15   | 35   | ns   |  |  |  |

| t <sub>LFALL</sub>   | Low-side driver fall time <sup>(4)</sup>  |                                                     |      | 10   | 25   |      |  |  |  |

| UVLO                 |                                           | ·                                                   |      |      |      |      |  |  |  |

| V <sub>UVLO</sub>    | Turn-on voltage                           |                                                     | 4.10 | 4.25 | 4.40 | V    |  |  |  |

| UVLO <sub>HYST</sub> | Hysteresis                                |                                                     | 270  | 320  | 370  | mV   |  |  |  |

| SHUTDOW              | N                                         |                                                     |      |      |      |      |  |  |  |

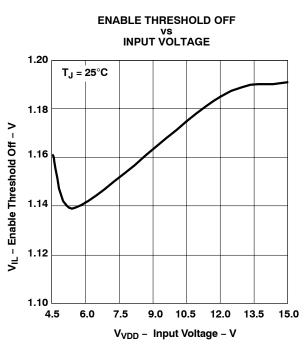

| V <sub>IH</sub>      | High-level input voltage, ENABLE          |                                                     |      |      | 2.8  |      |  |  |  |

| V <sub>IL</sub>      | Low-level input votlage, ENABLE           |                                                     | 0.6  |      |      | V    |  |  |  |

| BOOT DIO             | DE                                        | ·                                                   |      |      |      |      |  |  |  |

| V <sub>DFWD</sub>    | Bootstrap diode forward voltage           | I <sub>BOOT</sub> = 5 mA                            | 0.6  | 0.8  | 1.2  | V    |  |  |  |

(4) Ensured by design. Not production tested.

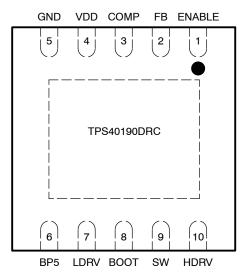

#### **DEVICE INFORMATION**

#### **TERMINAL FUNCTIONS**

| TERMINAL |     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| BOOT     | 8   | I   | Power supply for the flying high-side driver                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| BP5      | 6   | 0   | Output bypass for the internal regulator. Connect 4.7- $\mu$ F capacitor from this pin to GND. Low power, low noise loads may be connected here if desired. The sum of the external load and the gate drive requirements must not exceed 40 mA.                                                                                                                                    |  |  |  |

| COMP     | 3   | 0   | Output of the error amplifier. Connecting a resistance from COMP to GND sets the output short circuit detection threshold. See applications information for details.                                                                                                                                                                                                               |  |  |  |

| ENABLE   | 1   | I   | Logic level input that starts or stops the controller from an external user command. A high level turns the controller on. This pin has a high-impedance internal pull-up integrated into the device. Because this pin is high impedance, a 10-nF capacitor to ground or an external pull-up resistor (100 k $\Omega$ ) to VDD is recommended to avoid noise coupling to this pin. |  |  |  |

| FB       | 2   | I   | Inverting input to the error amplifier                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| GND      | 5   | -   | Common connection for the controller                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| HDRV     | 10  | 0   | Bootstrapped output for driving the gate of the high side N channel FET.                                                                                                                                                                                                                                                                                                           |  |  |  |

| LDRV     | 7   | 0   | Output to the rectifier FET gate                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| SW       | 9   | I   | Sense line for the adaptive anti cross conduction circuitry. Serves as common connection for the flying high side FET driver                                                                                                                                                                                                                                                       |  |  |  |

| VDD      | 4   | Ι   | Power input to the controller                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

#### DRC PACKAGE (TOP VIEW)

#### APPLICATION INFORMATION

#### Introduction

The TPS40190 is a cost optimized controller providing all the necessary features to construct a high-performance DC-DC converter while keeping costs to a minimum. Support for pre-biased outputs eliminates concerns about damaging sensitive loads during startup. Strong gate drivers for the high side and rectifier N-channel MOSFETs decrease switching losses for increased efficiency. Adaptive gate drive timing minimizes body diode conduction in the rectifier MOSFET, also increasing efficiency. Selectable short circuit protection thresholds and hiccup recovery from a short-circuit increase design flexibility and minimize power dissipation in the event of a prolonged output fault. A dedicated enable pin (ENABLE) allows the converter to be placed in a very low quiescent current shutdown mode.

Internally fixed switching frequency and soft-start time reduce external component count, simplifying design and layout, as well as reducing footprint and cost. The 3 mm  $\times$  3 mm package size also contributes to a reduced overall converter footprint.

#### **Internally Fixed Parameters**

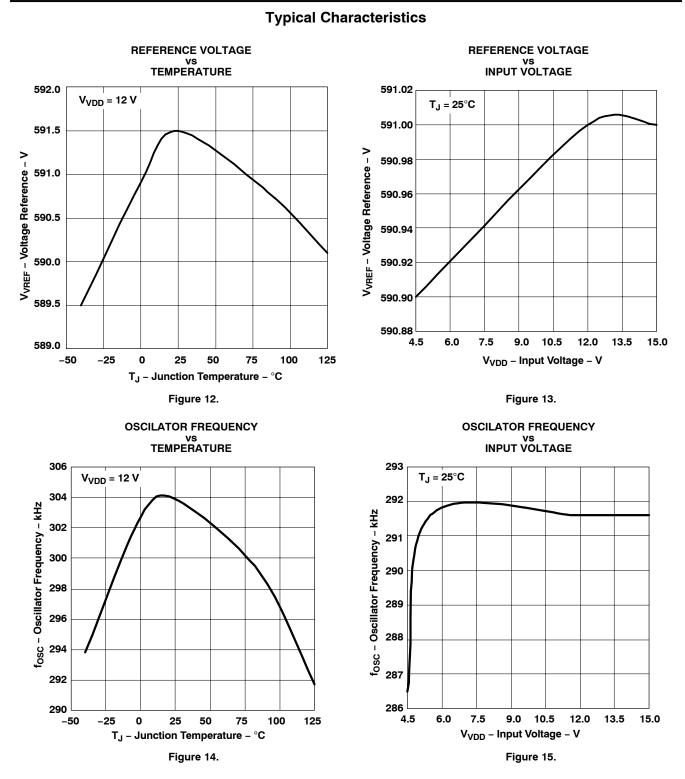

The TPS40190 has a fixed internal switching frequency of 300 kHz. Soft-start time is fixed at 4.7 ms typical and the UVLO level is set between 4.1 V and 4.4 V.

#### **APPLICATION INFORMATION (continued)**

#### **Output Short Circuit Protection**

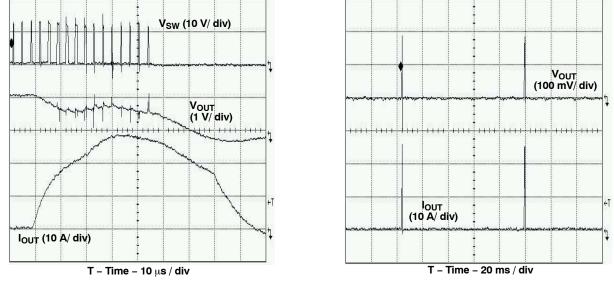

The short circuit detection in the TPS40190 is done by sensing the voltage drop across the high side FET when it is on. If the voltage drop across this FET exceeds the selected threshold in any given switching cycle, a counter counts up one count and the FET is turned off early. If the voltage drop across that FET does not exceed this threshold, the counter is decremented for that cycle and the FET is allowed to remain on for the normal pulse width commanded by the internal pulse width modulator. If the counter fills up (a count of 7) a fault condition is declared and the drivers turn both FETs off. After a timeout of approximately 95 ms, the controller attempts to restart. If a short circuit is still present at the output, the current ramps quickly up to the short-circuit threshold and another fault condition is declared. The device then waits 95 ms to attempt to restart again.

Typical waveforms during a short circuit event are shown in Figure 1 and Figure 2.

Figure 1. Output Short Circuit Detected (Nominal Threshold 25 A)

Figure 2. Output Fault Hiccup Restart Timing

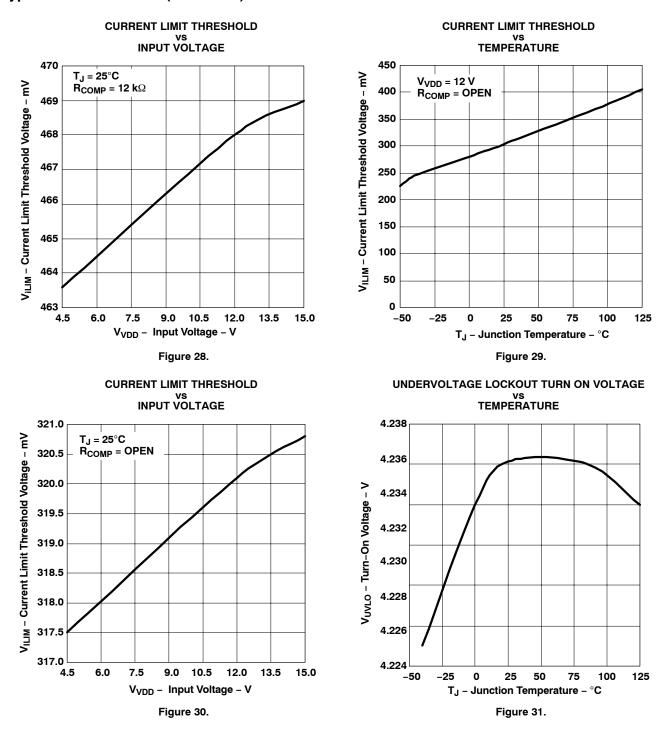

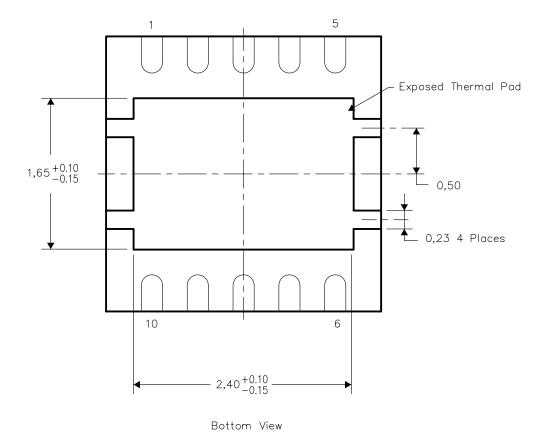

The TPS40190 provides three selectable short circuit protection thresholds: 160 mV, 320 mV and 460 mV. The particular threshold is selected by connecting a resistor from COMP to GND. Table 1 gives the short circuit thresholds for corresponding resistors from COMP to GND. Note that since the TPS40190 measures the resistance from COMP to GND during a 2-ms window, the compensation network from COMP to FB should have a time constant significantly less than 1 ms or there can be issues detecting the resistance and setting the correct short circuit threshold. This network should have no DC path from COMP to FB.

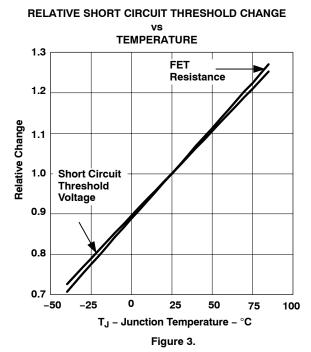

The short circuit detection threshold in the TPS40190 has some temperature compensation built in to help offset the high-side FET rise in resistance as its temperature rises. A typical FET has a resistance temperature coefficient of about 4500 ppm/°C. The temperature coefficient of the short circuit threshold is approximately 4200 ppm/°C. Figure 3 shows how the short circuit threshold increases with temperature to help compensate for the FET resistance increase. The relative FET resistance change is based on an estimate of a linear 4500 ppm/°C temperature coefficient. The effectiveness of this compensation depends on how tight the thermal coupling between the TPS40190 and the high-side FET is. Better thermal coupling between the TPS40190 and the high-side FET gives better compensation effectiveness.

#### **APPLICATION INFORMATION (continued)**

| Short Circuit Protection<br>Resistance<br>R <sub>COMP</sub> (kΩ) | Nominal Current Limit<br>Voltage<br>V <sub>ILIM</sub> (mV) |

|------------------------------------------------------------------|------------------------------------------------------------|

| 10.8 to 13.2                                                     | 460                                                        |

| OPEN                                                             | 320                                                        |

| 3.6 to 4.4                                                       | 160                                                        |

The range of short circuit current thresholds that can be expected is given by Equation 1 and Equation 2.

$I_{SCP(max)} = \frac{V_{ILIM(max)}}{R_{DS(onMIN)}}$  $I_{SCP(min)} = \frac{V_{ILIM(min)}}{R_{DS(onMAX)}}$

(1)

(2)

where

- $I_{SCP}$  is the short circuit current

- VILIM is the short circuit threshold

- R<sub>DS(on)</sub> is the channel resistance of the high-side MOSFET

TEXAS INSTRUMENTS www.ti.com

SLUS658A-JULY 2005-REVISED AUGUST 2005

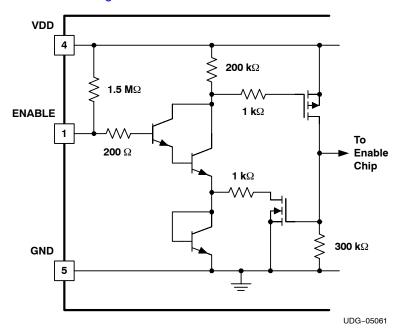

The TPS40190 has a dedicated ENABLE pin. This simplifies user level interface design since no multiplexed functions exist. Another benefit is a true low power shutdown mode of operation. When the ENABLE pin is pulled to GND, the TPS40190 consumes a typical  $20-\mu$ A of current. A functionally equivalent circuit to the enable circuitry on the TPS40190 is shown in Figure 4.

Figure 4. TPS40190 ENABLE Pin Internal Circuitry

If the ENABLE pin is left floating, the chip starts automatically. The pin must be pulled to less than 600 mV to guarantee that the TPS40190 is in shutdown mode. Note that the ENABLE pin is relatively high impedance. In some situations, there could be enough noise nearby to cause the ENABLE pin to swing below the 600 mV threshold and give erroneous shutdown commands to the rest of the device. There are two solutions to this problem should it arise.

- 1. Place a capacitor from ENABLE to GND. A side effect of this is to delay the start of the converter while the capacitor charges past the enable threshold

- Place a resistor from VDD to ENABLE. This causes more current to flow in the shutdown mode, but does not delay converter startup. If a resistor is used, the total current into the ENABLE pin should be limited to no more than 500 μA.

(3)

SLUS658A-JULY 2005-REVISED AUGUST 2005

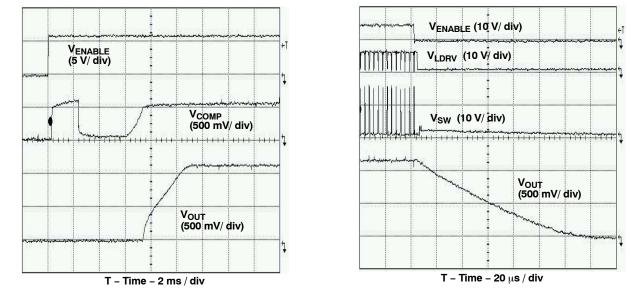

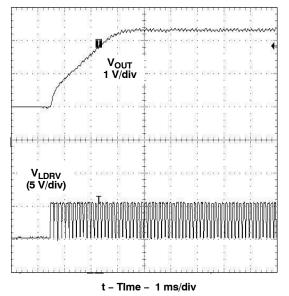

Typical waveforms for startup and shutdown using the ENABLE pin are shown in Figure 5 and Figure 6.

Figure 5. Startup Using ENABLE Pin

Figure 6. Shutdown Using ENABLE Pin

#### 5-V Regulator

The TPS40190 has an on board 5-V regulator that allows the part to operate from a single voltage feed. No separate 5-V feed to the part is required. This regulator needs to have  $4.7-\mu$ F of capacitance on the BP5 pin to guarantee stability. A ceramic capacitor is suggested for this purpose.

This regulator can also be used to supply power to nearby circuitry, eliminating the need for a separate LDO in some cases. If this pin is used for external loads, keep in mind that this is the power supply for the internals of the TPS40190. While efforts have been made to reduce sensitivity, any noise induced on this line has an adverse effect on the overall performance of the internal circuitry and shows up as increased pulse jitter, skewed reference voltage, etc.

The amount of power available from this pin varies with the size of the power MOSFETs that the drivers must operate. Larger MOSFETs require more gate drive current and reduces the amount of power available on this pin for other tasks.

The total amount of current required by the gate drive and the external circuitry should not exceed 40 mA. The current required to drive the FET gates can be found from Equation 3.

$$I_{G} = f_{SW} \times (Q_{G (high)} + Q_{G (low)})$$

Where

- I<sub>G</sub> is the required gate drive current

- $f_{SW}$  is the switching frequency (300 kHz)

- $Q_{G(high)}$  is the gate charge requirement for the high-side FET at 5 V V<sub>GS</sub>

- $Q_{G(low)}$  is the gate charge requirement for the low-side FET at 5 V V<sub>GS</sub>

#### **Startup Sequence and Timing**

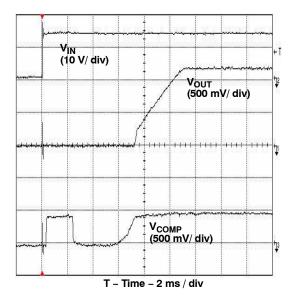

The TPS40190 startup sequence is as follows. After input power is applied, the 5-V onboard regulator comes up. Once this regulator comes up, the TPS40190 goes through a period where it samples the impedance at the COMP pin and decides the short circuit protection threshold voltage. This is accomplished by placing 400 mV on the COMP pin for approximately 2 ms. During this time, the current is measured and compared against internal thresholds to select the short circuit protection threshold. After this, the COMP pin is brought low for 4 ms. This ensures that the feedback loop is preconditioned at startup and no sudden output rise occurs at the output of the converter when the converter is allowed to start switching. After these initial 6 milliseconds, the internal soft-start circuitry is engaged and the converter is allowed to start. See Figure 7.

#### **Pre-Bias Outputs**

Some applications require that the converter not sink current during startup if a pre-existing voltage is higher than the output. Since synchronous buck converters inherently sink current some method of overcoming this characteristic must be employed. Applications that require this operation are typically power rails for a multi supply processor or ASIC. The method used in this controller, is to not allow the low side or rectifier FET to turn on until there the output voltage commanded by the start up ramp is higher than the pre-existing output voltage. This is detected by monitoring the internal pulse width modulator (PWM) for its first output pulse. Since this controller uses a closed loop startup, the first output pulse from the PWM does not occur until the output voltage is commanded to be higher than the pre-existing voltage. This effectively limits the controller to sourcing current only during the startup sequence.

If the pre-existing voltage is higher than the intended regulation point for the output of the converter, the converter starts and sinks current when the soft-start time has completed. A typical pre-biased startup is shown in Figure 8.

Figure 7. TPS40190 Startup Timing

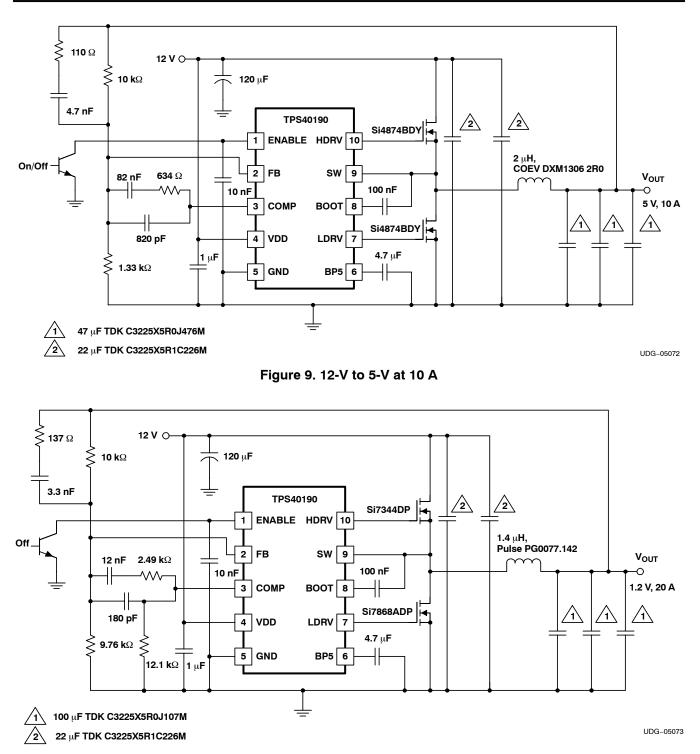

#### **Typical Applications**

Some typical applications.

Figure 8. Prebiased Startup Timing

SLUS658A-JULY 2005-REVISED AUGUST 2005

Figure 10. 12-V to 1.2-V at 20 A

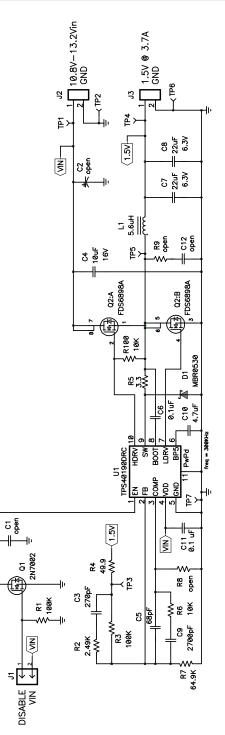

Figure 11. PMP1285, 12-V to 1.5-V, at 3.7 A

SLUS658A-JULY 2005-REVISED AUGUST 2005

#### 14

SLUS658A-JULY 2005-REVISED AUGUST 2005

0.2

0

-50

-25

0

SLUS658A-JULY 2005-REVISED AUGUST 2005

**Typical Characteristics (continued)**

# ENABLE THRESHOLD OFF vs TEMPERATURE 1.4 V<sub>VDD</sub> = 12 V 1.2 V<sub>IL</sub> – Enable Threshold Off – V 1.0 0.8 0.6 0.4

T<sub>J</sub> – Junction Temperature – °C Figure 20.

50

75

100

125

25

# TOTAL STARTUP TIME vs TEMPERATURE

SLUS658A-JULY 2005-REVISED AUGUST 2005

#### **Typical Characteristics (continued)**

SLUS658A-JULY 2005-REVISED AUGUST 2005

#### **Typical Characteristics (continued)**

#### TEXAS INSTRUMENTS www.ti.com

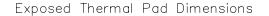

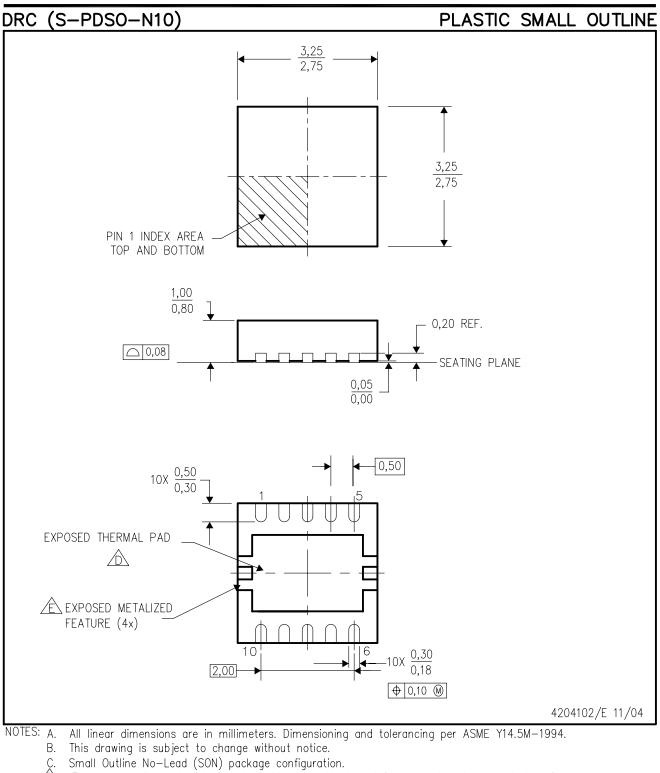

## THERMAL PAD MECHANICAL DATA

## DRC (S-PDSO-N10)

THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB), the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to a ground plane or special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, Quad Flatpack No-Lead Logic Packages, Texas Instruments Literature No. SCBA017. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

27-Sep-2005

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup>  | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| TPS40190DRCR     | ACTIVE                | SON             | DRC                | 10   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS40190DRCRG4   | ACTIVE                | SON             | DRC                | 10   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS40190DRCT     | ACTIVE                | SON             | DRC                | 10   | 250            | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS40190DRCTG4   | ACTIVE                | SON             | DRC                | 10   | 250            | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **MECHANICAL DATA**

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- $\not E$  Metalized features are supplier options and may not be on the package.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

#### Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated