SLLS382 - DECEMBER 1999

- 80 mA × 16 Bits and 120 mA × 8 Bits

Drive Capability and Output Counts

- 5 mA to 80 mA/10 mA to 120 mA Constant Current Output Range

- Constant Currency Accuracy of ±4% (Maximum Error Between Bits)

- Constant Current Output Terminals

- 0.4 V (Output Current 0 to 40 mA)

- 0.7 V (Output Current 40 to 80 mA)

- 256 Gray Scale Display With Pulse Width Control 256 Steps

- Brightness Adjustment

- Output Current Adjustment for 32 Steps (Adjustment for Brightness Deviation Between LEDs)

- 8 Steps Brightness Control by 8 Times Speed Gray Scale Control Clock (Brightness Adjustment for Panel)

- Protection

- WDT Function

- TSD Function

- Clock Synchronized 8-Bit Parallel Input

- Anode Common LED Type Applied

- CMOS Input Signal Level

(Schmitt-Triggered Input for All Input Terminals)

- 4.5 V to 5.5 V Power Supply Voltage

- 15 V Maximum Output Voltage

- 15 MHz Maximum Data Transfer Rate

- 4 MHz Maximum Gray Scale Clock Frequency

- -20°C to 85°C Operating Free-Air Temperature Range

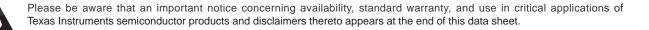

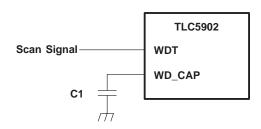

- 100-Pin HTQFP Package (PD = 4.7 W, T<sub>A</sub> = 25°C)

## description

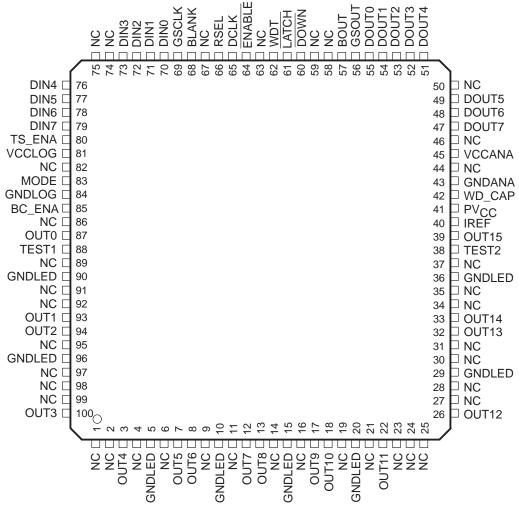

The TLC5902 is a constant current driver that incorporates shift register, data latch, and constant current circuitry with a current value adjustable and 256 gray-scale display that uses pulse width control. The output current can be selected as maximum 80 mA with 16 bits or 120 mA with 8 bits. The current value of the constant current output is set by one external resister. After this device is mounted on a printed-circuit board (PCB), the brightness deviation between LEDs (ICs) can be adjusted using an external data input, and the brightness control for the panel can be adjusted using the brightness adjustment circuitry. Moreover, the device incorporates watchdog timer (WDT) circuitry, which turns the constant current output off when the scan signal is stopped during dynamic scanning operation, and thermal shutdown (TSD) circuitry, which turns constant current output off when the junction temperature exceeds the limit.

# functional block diagram

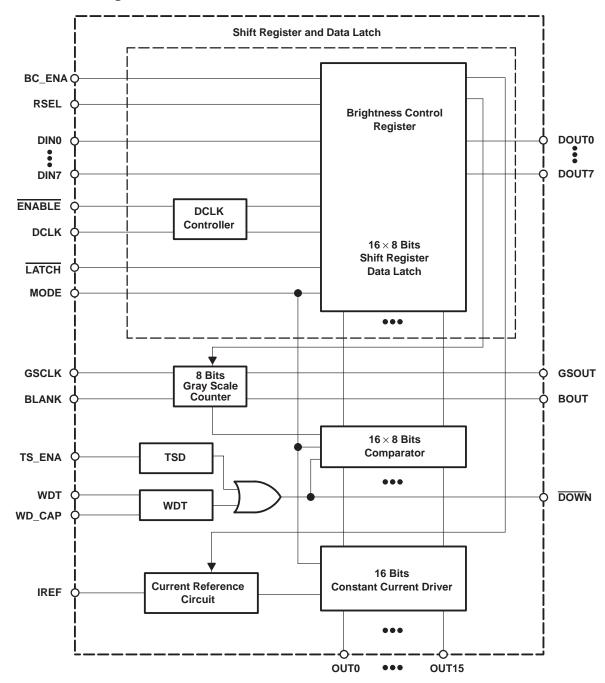

# functional block diagram for shift register and data latch

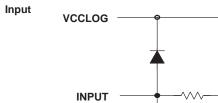

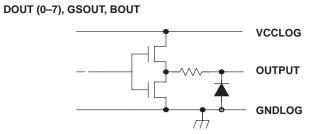

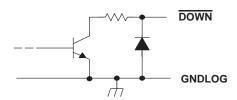

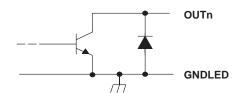

# equivalent input and output schematic diagrams

**GNDLOG**

$\mathcal{F}$

DOWN

**OUT**n

# **Terminal Functions**

| TERM             | IINAL                                                     | 1/0                                                                                                                                                                                                                                                                                                                                                  | DESCRIPTION                                                                                                                                                                                                                                                                     |  |  |  |  |

|------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME             | NO.                                                       | 1/0                                                                                                                                                                                                                                                                                                                                                  | DESCRIPTION                                                                                                                                                                                                                                                                     |  |  |  |  |

| BC_ENA           | 85                                                        | ı                                                                                                                                                                                                                                                                                                                                                    | Brightness control enable. When BC_ENA is low, the brightness control function is disabled. At this time, the brightness control latch is reset to 1Fh. Output current value is 100% of setting value by an external resistor and the frequency division ratio of GSCLK is 1/1. |  |  |  |  |

| BLANK            | 68                                                        | ı                                                                                                                                                                                                                                                                                                                                                    | Blank (Light off). When BLANK is high, all the output of the constant current driver is turned off. All the output is turned on (LED on) synchronizing to the falling edge of GCLK after next rising edge of GCLK when BLANK goes from high to low.                             |  |  |  |  |

| BOUT             | 57                                                        | 0                                                                                                                                                                                                                                                                                                                                                    | Blank signal delay. BOUT is output with the addition of delay time to BLANK.                                                                                                                                                                                                    |  |  |  |  |

| CONDUCTIVE PAD   | package<br>surface                                        |                                                                                                                                                                                                                                                                                                                                                      | Heat sink pad                                                                                                                                                                                                                                                                   |  |  |  |  |

| DCLK             | 65                                                        | ı                                                                                                                                                                                                                                                                                                                                                    | Clock input for data transfer. The input data of DIN is synchronized to the rising edge of DCLK, and transferred to DOUT. DCLK is valid at the rising edge after ENABLE goes low.                                                                                               |  |  |  |  |

| DIN7-DIN0        | 70,71,72,73,<br>76,77,78,79                               | ı                                                                                                                                                                                                                                                                                                                                                    | Input for shift register for both gray scale data and brightness control. It is 8 bits parallel data.                                                                                                                                                                           |  |  |  |  |

| DOUT7-DOUT0      | 47,48,49,51,<br>52,53,54,55                               | 0                                                                                                                                                                                                                                                                                                                                                    | Output for shift register for both gray scale data and brightness control.                                                                                                                                                                                                      |  |  |  |  |

| DOWN             | 60                                                        | 0                                                                                                                                                                                                                                                                                                                                                    | Shutdown. DOWN is configured as an open collector. It goes low when the constant current output is shut down by the WDT or TSD function.                                                                                                                                        |  |  |  |  |

| ENABLE           | 64                                                        | I                                                                                                                                                                                                                                                                                                                                                    | Data transfer enable. When ENABLE is high, data is not transferred.                                                                                                                                                                                                             |  |  |  |  |

| GNDANA           | 43                                                        |                                                                                                                                                                                                                                                                                                                                                      | Analog ground. (Internally connected to GNDLOG and GNDLED)                                                                                                                                                                                                                      |  |  |  |  |

| GNDLED           | 5,10,15,20,29,<br>36,90,96                                |                                                                                                                                                                                                                                                                                                                                                      | LED driver ground (Internally connected to GNDANA and GNDLOG)                                                                                                                                                                                                                   |  |  |  |  |

| GNDLOG           | 84                                                        |                                                                                                                                                                                                                                                                                                                                                      | Logic ground. (Internally connected to GNDANA and GNDLED)                                                                                                                                                                                                                       |  |  |  |  |

| GSCLK            | 69                                                        | ı                                                                                                                                                                                                                                                                                                                                                    | Clock input for gray scale. The gray scale display is accomplished by lighting the LED until the number of GSCLK counted is equal to the data latched.                                                                                                                          |  |  |  |  |

| GSOUT            | 56                                                        | 0                                                                                                                                                                                                                                                                                                                                                    | Clock delay for gray scale. GSOUT is output with addition of delay time to GSCLK                                                                                                                                                                                                |  |  |  |  |

| IREF             | 40                                                        | ı                                                                                                                                                                                                                                                                                                                                                    | Constant current control setting. LED current is set to the desired value by connecting an external resistor between IREF and GND. The 38 times current is compared to current across external resistor sink on output terminal.                                                |  |  |  |  |

| LATCH            | 61                                                        | ı                                                                                                                                                                                                                                                                                                                                                    | Latch. When LATCH is high, data on shift register goes through the latch. When LATCH is low, data is latched. Accordingly, if data on the shift register is changed during LATCH high, this new value is latched.                                                               |  |  |  |  |

| MODE             | 83                                                        | 1                                                                                                                                                                                                                                                                                                                                                    | 8/16 bits select. When the MODE is high, the 16 bits output is selected. When the MODE is low, the 8 bits output is selected.                                                                                                                                                   |  |  |  |  |

| OUT0-OUT15       | 87,93,94,100,<br>3,7,8,12,13,17,<br>18,22,26,32,<br>33,39 | 0                                                                                                                                                                                                                                                                                                                                                    | Constant current output                                                                                                                                                                                                                                                         |  |  |  |  |

| PV <sub>CC</sub> | 41                                                        |                                                                                                                                                                                                                                                                                                                                                      | LED driver power supply voltage                                                                                                                                                                                                                                                 |  |  |  |  |

| RSEL             | 66                                                        | ı                                                                                                                                                                                                                                                                                                                                                    | Shift register latch switching. When RSEL is low, the shift register and latch for gray scale are selected. When RSEL is high, the shift register and latch for brightness control are selected.                                                                                |  |  |  |  |

| TEST1, TEST2     | 88,38                                                     | I                                                                                                                                                                                                                                                                                                                                                    | TEST. Factory test terminal. TEST should be connected to GND for normal operation.                                                                                                                                                                                              |  |  |  |  |

| TS_ENA           | 80                                                        | ı                                                                                                                                                                                                                                                                                                                                                    | TSD (Thermal shutdown) enable. When TS_ENA is high, TSD is enabled. When TS_ENA is low, TSD is disabled.                                                                                                                                                                        |  |  |  |  |

| VCCANA           | 45                                                        |                                                                                                                                                                                                                                                                                                                                                      | Analog power supply voltage                                                                                                                                                                                                                                                     |  |  |  |  |

| VCCLOG           | 81                                                        |                                                                                                                                                                                                                                                                                                                                                      | Logic power supply voltage                                                                                                                                                                                                                                                      |  |  |  |  |

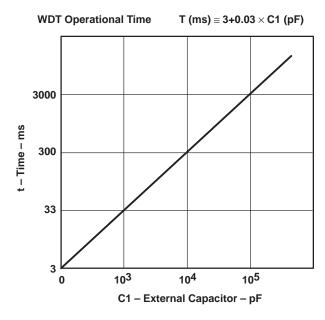

| WD_CAP           | 42                                                        | ı                                                                                                                                                                                                                                                                                                                                                    | WDT detection time adjustment. The capacitor for WDT detection time adjustment is connected between WD_CAP and GND. When WD_CAP is directly connected to GND, the WDT function is disabled.                                                                                     |  |  |  |  |

| WD               | 62                                                        | WDT scan input. By applying a scan signal to this terminal, the scan signal can be monitore constant current output can be turned off. LED is protected from damage from burning where scan signal is stopped during the constant period. The scan signal should be applied terminal by connecting W_CAP to GND even though no WDT function is used. |                                                                                                                                                                                                                                                                                 |  |  |  |  |

# **Function Tables**

### Truth Table (Data)

| BC_ENA | ENABLE | DCLK     | RSEL | LATCH | MODE | DOUT0 – DOUT7                                                               | OPERATION/FUNCTION                                                                             |

|--------|--------|----------|------|-------|------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| L      | Х      | Х        | Х    | Х     | Х    | No change                                                                   | Data latch for brightness control is set to 1Fh.                                               |

| Х      | Н      | Х        | Х    | Х     | Х    | No change                                                                   | Data transfer for gray scale and brightness control does not occur.                            |

| Х      | L      | 1        | Н    | Х     | Х    | Shift register for brightness control                                       | Data of DIN0 to DIN7 is clocked into the shift register for brightness control.                |

| Х      | L      | <b>↑</b> | L    | Х     | Н    | Data for shift register<br>before 16 bytes (written<br>before 16 times)     | Data of DIN0 to DIN7 is clocked into the first byte of the shift register for gray scale data. |

| Х      | L      | <b></b>  | L    | Х     | L    | Shift register for gray<br>scale before 8 bytes<br>(written before 8 times) | Data of DIN0 to DIN7 is clocked into the first byte of the shift register for gray scale data. |

| Н      | Х      | Х        | Н    | Н     | Х    | No change                                                                   | Shift register for brightness control goes through data latch for brightness control.          |

| Х      | Х      | Х        | L    | Н     | Х    | No change                                                                   | Shift register for gray scale goes through data latch for gray scale.                          |

| Н      | Х      | Х        | Х    | L     | Х    | No change                                                                   | The value for the shift register selected by RSEL is latched.                                  |

# Truth Table (Display/Protection)

| BLANK | GSCLK    | MODE | WDT | WD_CAP    | TS_ENA | OUT0~15                                                                                                                                                                                                                                                                            | DOWN | OPERATION/<br>FUNCTION                 |

|-------|----------|------|-----|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------|

| Н     | Х        | X    | Х   | Х         | Х      | Off                                                                                                                                                                                                                                                                                | Hi–Z |                                        |

| L     | <b>\</b> | Н    | х   | Х         | х      | 16 bits operation mode. The output is turned on if all the gray scale data is not zero on the falling edge of GCLK after the next rising edge of GCLK when BLANK goes from high to low. Each output turns off on the falling edge of GSCLK, corresponding to each gray scale data. | Hi–Z |                                        |

| L     | <b>\</b> | L    | х   | Х         | х      | 8 bits operation mode. The output is turned on if all the gray scale data is not zero on the falling edge of GCLK after the next rising edge of GCLK when BLANK goes from high to low. Each output turns off on the falling edge of GSCLK corresponding to each gray scale data.   | Hi–Z |                                        |

| L     | х        | Х    | CLK | capacitor | Х      | X Turn off if the level of WDT is not changed within time set by capacitor connected to WD_CAP.                                                                                                                                                                                    |      | Recover when the level of WDT changes. |

| L     | Х        | Х    | CLK | L         | Х      | WDT function is disabled.                                                                                                                                                                                                                                                          | Hi–Z |                                        |

| L     | Х        | Х    | CLK | Н         | Х      | WDT function is disabled.                                                                                                                                                                                                                                                          | Hi–Z |                                        |

| L     | Х        | Х    | Х   | Х         | Н      | Turn off if junction temperature exceeds the limit.                                                                                                                                                                                                                                | L    | Set TS_ENA to low for recovery         |

SLLS382 - DECEMBER 1999

# absolute maximum ratings (see Note 1)†

| Logic supply voltage, V <sub>CC(LOG)</sub>                                        | 0.3 V to 7 V                        |

|-----------------------------------------------------------------------------------|-------------------------------------|

| Supply voltage for constant current circuit, PV <sub>CC</sub>                     |                                     |

| Analog supply voltage, V <sub>CC(ANA)</sub>                                       | –0.3 V to 7 V                       |

| Output current (DC), I <sub>OL(C)</sub>                                           |                                     |

| Input voltage range                                                               | 0.3 V to V <sub>CC(LOG)</sub> 0.3 V |

| Output voltage range, V(OUTn), V(BOUT) and V(GSOUT)                               | 0.3 V to V <sub>CC(LOG)</sub> 0.3 V |

| Output voltage range, V(OUTn) and V(DOWN)                                         |                                     |

| Continuous total power dissipation at (or below) $T_A = 25^{\circ}C$ (see Note 2) | 4.7 W                               |

| Operating free air temperature range, T <sub>A</sub>                              | –20°C to 85°C                       |

| Storage temperature range, T <sub>stg</sub>                                       | –55°C to 150°C                      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# recommended operating conditions

dc characteristics over recommended ranges of operating free-air temperature,  $V_{CC(LOG)} = V_{CC(ANA)} = PV_{CC} = 4.5 \text{ V}$  to 5.5 V (unless otherwise noted)

|                                                               |                                                                                          | MIN          | NOM | MAX          | UNIT |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------|-----|--------------|------|

| Logic supply voltage, VCC(LOG)                                |                                                                                          | 4.5          | 5   | 5.5          | V    |

| Supply voltage for constant current circuit, PV <sub>CC</sub> |                                                                                          | 4.5          | 5   | 5.5          | V    |

| Analog power supply, V <sub>CC</sub> (ANA)                    |                                                                                          | 4.5          | 5   | 5.5          | V    |

| Voltage between V <sub>CC</sub> , V(DEF1) (see Note 3)        | VDEF1 = VCC(LOG) - VCC(ANA)<br>VCC(LOG) - PVCC, VCC(ANA) - PVCC                          | -0.3         | 0   | 0.3          | V    |

| Voltage between GND, V(DEF2) (see Note 3)                     | V <sub>(DEF2)</sub> = GND(LOG) – GND(ANA)<br>GND(LOG) – GND(LED), GND(ANA) –<br>GND(LED) | -0.3         | 0   | 0.3          | V    |

| High-level input voltage, VIH                                 |                                                                                          | 0.8 VCC(LOG) |     | VCC(LOG)     | V    |

| Low-level input voltage, V <sub>IL</sub>                      |                                                                                          | GND(LOG)     |     | 0.2 VCC(LOG) | V    |

| High-level output current, IO(H)                              | VCC(LOG) = 4.5 V, DOUT0 to DOUT7,<br>BOUT, GSOUT                                         |              |     | -1           | A    |

| Low-level output current, IO(L)                               | V <sub>CCLOG</sub> = 4.5 V, DOUT0 to DOUT7,<br>BOUT, GSOUT                               |              |     | 1            | mA   |

| - (-/                                                         | V <sub>CC(LOG)</sub> = 4.5 V, DOWN                                                       |              |     | 5            | mA   |

| Constant output current, IOL(C)                               | OUT0 to OUT15                                                                            | 5            |     | 80           | mA   |

NOTE 3: Each voltage is supplied by single power supply, not a separated power supply.

NOTES: 1. All voltage values are with respect to GNDLOG terminal.

<sup>2.</sup> For operation above 25°C free-air temperature, derate linearly at the rate of 38.2 mW/°C.

# recommended operating conditions (continued)

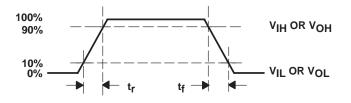

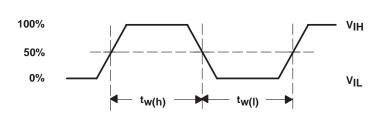

# ac characteristics over recommended ranges of operating free-air temperature, $V_{CC(LOG)} = V_{CC(ANA)} = PV_{CC} = 4.5 \text{ V}$ to 5.5 V (unless otherwise noted)

|                                                                              |                                                                                   | MIN | TYP | MAX | UNIT    |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-----|---------|

| DCI V clock fraguency for a con-                                             | At single operation                                                               |     |     | 15  | N 41 1- |

| DCLK clock frequency, f(DCLK)                                                | At cascade operation                                                              |     |     | 10  | MHz     |

| DCLK pulse duration (high or low level), $t_{W(h)}/t_{W(l)}$                 |                                                                                   | 20  |     |     | ns      |

|                                                                              | Frequency division ratio 1/1                                                      |     |     | 4   | MHz     |

| GSCLK clock frequency, f(GSCLK)                                              | Frequency division ratio 1/1, T <sub>A</sub> = 25°C, VCCLOG = VCCANA = PVCC = 5 V |     | 8   |     | MHz     |

| GSCLK pulse duration (high or low level), tw(h)/tw(l)                        |                                                                                   | 75  |     |     | ns      |

| WDT clock frequency, f(WDT)                                                  |                                                                                   |     |     | 5   | MHz     |

| WDT pulse duration (high or low level), t <sub>W(h)</sub> /t <sub>W(l)</sub> |                                                                                   | 50  |     |     | ns      |

| LAT pulse duration (high or low level), t <sub>W(h)</sub>                    | LATCH                                                                             | 50  |     |     | ns      |

| Rise/fall time, t <sub>r</sub> /t <sub>f</sub>                               |                                                                                   |     |     | 100 | ns      |

|                                                                              | DINn – DCLK                                                                       | 10  |     |     |         |

|                                                                              | LATCH – DCLK                                                                      | 15  |     |     |         |

|                                                                              | BLANK – GSCLK                                                                     | 20  |     |     |         |

| Setup time, t <sub>su</sub>                                                  | ENABLE – DCLK                                                                     | 15  |     |     | ns      |

|                                                                              | LATCH – GSCLK                                                                     | 10  |     |     |         |

|                                                                              | RSEL – DCLK                                                                       | 10  |     |     |         |

|                                                                              | RSEL – LATCH                                                                      | 20  |     |     |         |

|                                                                              | DINn – DCLK                                                                       | 15  |     |     |         |

|                                                                              | LATCH - DCLK                                                                      | 30  |     |     |         |

| Hold time, t <sub>n</sub>                                                    | ENABLE – DCLK                                                                     |     |     |     | ns      |

|                                                                              | RSEL – DCLK                                                                       | 20  |     |     |         |

|                                                                              | RSEL – LATCH                                                                      | 20  |     |     |         |

# TLC5902 LED DRIVER

SLLS382 - DECEMBER 1999

# electrical characteristics, MIN/MAX: $V_{CC(LOG)} = V_{CCANA} = PV_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$ , $T_A = -20 ^{\circ}\text{C}$ to $85 ^{\circ}\text{C}$ TYP: $V_{CC(LOG)} = V_{CC(ANA)} = PV_{CC} = 5 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$ (unless otherwise noted)

|                     | PARAMETER                                                   | TEST CONDITIONS                                                                                                                                                                                     | MIN               | TYP  | MAX | UNIT |  |

|---------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|-----|------|--|

| VOH                 | High-level output voltage                                   | IOH = -1 mA, DOUT0 to DOUT7,<br>GSOUT, BOUT                                                                                                                                                         | VCC(LOG)<br>-0.5V |      |     | V    |  |

| VOL                 | Low-level output voltage                                    | I <sub>OL</sub> = 1 mA, DOUT0 to DOUT7, GSOUT, BOUT                                                                                                                                                 |                   |      | 0.5 | V    |  |

|                     |                                                             | I <sub>OL</sub> = 5 mA DOWN                                                                                                                                                                         |                   |      | 0.5 |      |  |

| lį                  | Input current                                               | $V_I = V_{CC(LOG)}$ or $GND(LOG)$                                                                                                                                                                   |                   |      | ±1  | μΑ   |  |

| I(OG)               | Supply current (logic)                                      | Input signal is static, TS_ENA = H, WD_CAP = OPEN                                                                                                                                                   |                   |      | 1   | mA   |  |

| I(LOG)              | Supply current (logic)                                      | Data transfer, DCLK = 15 MHz, GSCLK = 1 MHz                                                                                                                                                         |                   | 18   | 30  | IIIA |  |

| 1,,,,,,             | Supply current (analog)                                     | LED turns on, $R_{(IREF)} = 590 \Omega$                                                                                                                                                             |                   | 3    | 5   | mA   |  |

| <sup>I</sup> (ANA)  | Supply current (analog)                                     | LED turns off, $R_{(IREF)} = 590 \Omega$                                                                                                                                                            |                   | 3    | 5   | IIIA |  |

|                     |                                                             | $R_{(IREF)} = 1180 \Omega$ , LED turns off                                                                                                                                                          |                   | 15   | 20  |      |  |

|                     |                                                             | $R(IREF) = 590 \Omega$ , LED turns off                                                                                                                                                              |                   | 30   | 40  |      |  |

| I <sub>(PVCC)</sub> | Supply current (constant current driver)                    | $V_O = 1 \text{ V},$ $R_{(IREF)} = 1180 \Omega,$ 16 bits output turns on                                                                                                                            |                   | 25   | 35  | mA   |  |

|                     |                                                             | $V_O = 1 \text{ V}, \qquad R_{(IREF)} = 590 \Omega,$ 16 bits output turns on                                                                                                                        |                   | 50   | 70  |      |  |

| I <sub>OL(C1)</sub> | Constant output oursel                                      | $V_O = 1 \text{ V}, \qquad V_{(IREF)} = 1.24 \text{ V}, \\ R_{(IREF)} = 1180 \Omega$                                                                                                                | 35                | 40   | 45  | mA   |  |

| I <sub>OL(C2)</sub> | - Constant output current                                   | $V_O = 1 \text{ V}, V_{(IREF)} = 1.24 \text{ V},$ $R_{(IREF)} = 590 \Omega$                                                                                                                         | 70                | 80   | 90  | mA   |  |

| l <sub>lkg</sub>    | Constant output leakage current                             | $V_O$ = 15 V, $R_{(IREF)}$ = 590 $\Omega$ , LED turn off                                                                                                                                            |                   |      | 10  | μΑ   |  |

| ΔlOL(C)             | Constant output current error between bit                   | $ \begin{array}{l} V_{CC(LOG)} = V_{CC(ANA)} = PV_{CC} = 5 \ \ V, \\ V_{(IREF)} = 1.24 \ \ V, \qquad R_{(IREF)} = 590 \ \Omega, \\ All \ bits \ turns \ on, \qquad V_{O} = 1 \ \ V \\ \end{array} $ |                   | ±1%  | ±4% |      |  |

| I∆OL(C1)            | Changes in constant output current depend on supply voltage | V(IREF) = 1.24 V                                                                                                                                                                                    |                   | ±1%  | ±4% | V    |  |

| I∆OL(C2)            | Changes in constant output current depend on output voltage | V(IREF) = 1.24 V, $R$ (IREF) = 1180 Ω, 1 bit output turns on, $V$ O = 1 V to 3 V                                                                                                                    |                   | ±1%  | ±2% | V    |  |

| T(tsd)              | TSD detection temperature (thermal shutdown circuit)        | Junction temperature                                                                                                                                                                                | 150               | 160  | 170 | °C   |  |

| T(wdt)              | WDT detection time (watch-dog timer circuit)                | No external capacitor                                                                                                                                                                               | 1                 | 3    | 8   | ms   |  |

| V(IREF)             | Voltage reference                                           | BC_ENA = L, $R_{(IREF)} = 590 \Omega$                                                                                                                                                               |                   | 1.24 |     | V    |  |

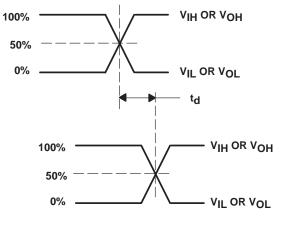

# switching characteristics, $C_L = 15 pF$

|                | PARAMETER              | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |

|----------------|------------------------|-----------------|-----|-----|-----|------|--|

|                |                        | DOUT            |     | 12  | 30  |      |  |

| l.             | Rise time              | OUT             |     | 250 |     |      |  |

| t <sub>r</sub> | Rise time              | GSOUT           |     | 13  | 30  | ns   |  |

|                |                        | BOUT            |     | 13  | 30  |      |  |

|                |                        | DOUT            |     | 8   | 20  |      |  |

| ١.             | Fall time              | OUT             |     | 150 |     |      |  |

| tf             | Fall time              | GSOUT           | 10  |     | 25  | ns   |  |

|                |                        | BOUT            |     | 10  | 25  |      |  |

|                |                        | OUTn+1 – OUTn   |     | 8   | 15  |      |  |

|                |                        | BLANK ↑ – OUT0  |     | 350 | 500 |      |  |

| <b> </b>       | Drangation delay time  | GSCLK ↓ – OUT0  |     | 350 | 500 |      |  |

| <sup>t</sup> d | Propagation delay time | DCLK ↑ – DOUT   | 15  | 30  | 50  | ns   |  |

|                |                        | GSCLK – GSOUT   | 10  | 25  | 50  |      |  |

|                |                        | BLANK – BOUT    | 10  | 25  | 50  |      |  |

# timing requirements

#### constant current output selection by user (80 mA $\times$ 16 bits or 120 mA $\times$ 8 bits)

When MODE terminal is set to high, output is selected as 80 mA  $\times$  16 bits. When MODE terminal is set to low, output is selected as 120 mA  $\times$  8 bits. By this setting, the internal shift register and latch are changed. Note that two constant output terminals should be tied, such as OUT0 to OUT1 and OUT2 to OUT3 when 8-bit output is selected.

| MODE | OUTPUT          |  |  |  |

|------|-----------------|--|--|--|

| Н    | 80 mA x 16 bits |  |  |  |

| L    | 120 mA x 8 bits |  |  |  |

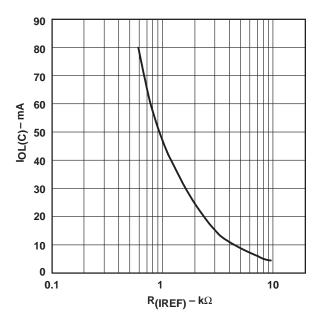

#### setting for constant current value

On the constant current output terminals (OUT0 to OUT15), approximately 38 times the current that flows through the external resistor,  $R_{(IREF)}$  (connected between IREF and GND), can flow. The external resistor value is calculated using the following equation.

$$\frac{I_{(OUTn)}(mA) \approx 38 \times 1.24(V)}{R_{(IREF)}(k\Omega)}$$

(1)

More current flows if IREF is connected to GND directly.

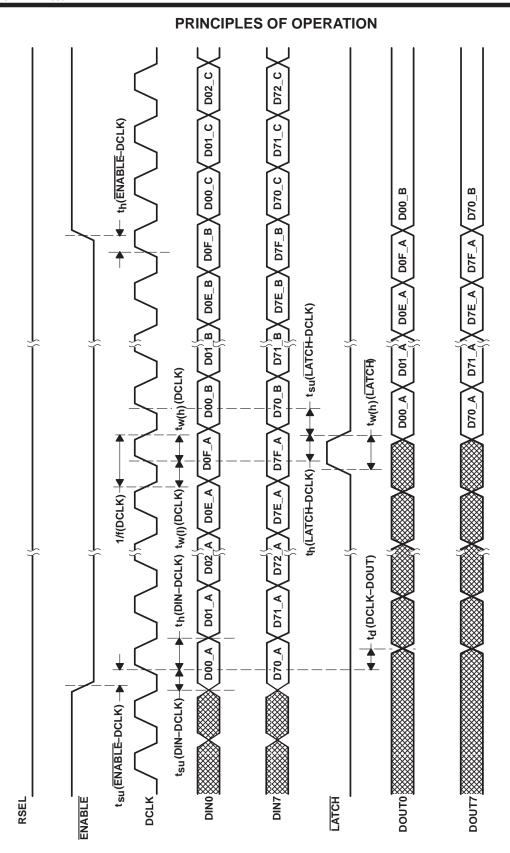

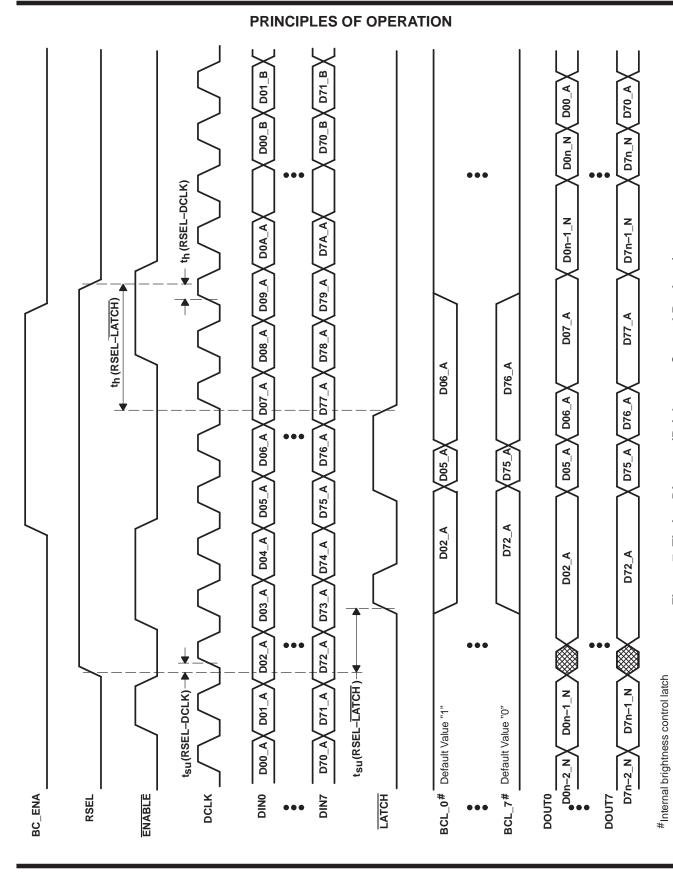

### shift register latch for gray scale data

The shift register latch for gray scale data is set as  $8 \times 8$  bits configuration each at 8 bits mode, and as  $16 \times 8$  bits configuration each at 16-bit mode. By setting RSEL to low, the shift register latch for gray scale data is selected. Data structure shows that DIN0 corresponds to LSB, and DIN7 to MSB. This results in  $2^8 = 256$  steps gray scale. The latched data is compared to GSCLK (clock for gray scale) counts, and constant current output continues to turn on until these values are equal.

#### shift register latch for brightness control

The shift register latch for brightness control is configured with  $1 \times 8$  bits each. The data input terminal and latch terminal are common to shift register latch for gray scale data. By setting RSEL to low, the shift register latch for gray scale data is selected, and by setting RSEL to high, the shift register latch for brightness control is selected. If the brightness control function is not used, BC\_ENA terminal should be pulled low. Since the brightness control latch is reset to initial value of 00011111h, it is not necessary to write data to shift register latch for brightness control. When power is up, latch data is undetermined. Data should be written to shift register latch when the brightness control function is used. Also, rewriting the latch value for brightness control is inhibited when the LED is turned on.

| RSEL | SHIFT REGISTER LATCH SELECTED               |  |  |  |

|------|---------------------------------------------|--|--|--|

| L    | Shift register latch for gray scale data    |  |  |  |

| Н    | Shift register latch for brightness control |  |  |  |

#### write data to both shift register latches

The shift register latch is selected using the RSEL terminal. The data input method is the same for both shift register latches. The data is applied to DIN0 to DIN7 of 8-bits data input terminal, and transferred synchronizing to DCLK. The data of DIN0 to DIN7 is transferred to the direction from OUT0 to OUT15 synchronizing to DCLK. The shift register for brightness control is 1-bit length resulting in one time of DCLK input. The shift register for gray scale data is 8-bits length at 8-bit mode resulting in eight times of DCLK, and 16-bit length at 16-bit mode resulting in 16 times of DCLK input. At the number of DCLK input for each case, output data appear on DOUT0 to DOUT7. When  $\overline{\text{LATCH}}$  goes from low to high, data is latched internally. Then, when  $\overline{\text{LATCH}}$  goes low, data is held. RSEL switching should be done when DCLK and  $\overline{\text{LATCH}}$  are low.

## brightness control latch configuration

The brightness control latch is configured as DIN0 corresponds to LSB, and DIN7 to MSB. The lower 5 bits are assigned for output current adjustment, and the upper 3 bits are for a frequency division ratio setting of GSCLK.

| DIN7        | DIN6                                      | DIN5 | DIN4 | DIN3                   | DIN2 | DIN1 | DIN0 |

|-------------|-------------------------------------------|------|------|------------------------|------|------|------|

| MSB         |                                           |      |      |                        |      |      | LSB  |

| 0†          | 0                                         | 0    | 1    | 1                      | 1    | 1    | 1    |

| Frequency d | Frequency division ratio setting of GSCLK |      |      | Output current setting |      |      |      |

†BC ENA is low.

#### output current adjustment – brightness adjustment between ICs

By using the lower 5 bits of the brightness control latch, output current can be adjusted to 32 steps. When output current is set to 100% by the external resistor at 11111h of the latched value, it is adjusted as 1 step or 32 steps of 1.6% current ratio between 100 and 51.6%. By using this function, the brightness control between modules (ICs) can be adjusted, sending the desired data externally even if ICs are mounted on PCB. When BC\_ENA is pulled low, the latch is reset to the initial value of 00011111h, and the output current is set to 100%.

| CODE          | CURRENT RATIO (%) | 20 (mA) | 80 (mA) | V <sub>IREF</sub> (TYP) |

|---------------|-------------------|---------|---------|-------------------------|

| MSB 00000 LSB | 51.6              | 10.3    | 41.3    | 0.64                    |

|               |                   |         |         |                         |

|               |                   |         |         | •                       |

|               |                   |         |         | •                       |

|               | •                 |         |         | •                       |

| 11110         | 98.4              | 19.7    | 78.7    | 1.22                    |

| 11111†        | 100               | 20.0    | 80.0    | 1.24                    |

<sup>†</sup>BC\_ENA is low.

#### frequency division ratio setting for GSCLK(clock for gray scale) – panel brightness adjustment

By using the upper 3 bits of the brightness control latch, GSCLK can be divided into 1/1 to 1/8. If GSCLK is set to 8 times the speed ( $256 \times 8 = 2048$ ) of the frequency during the horizontal scanning time, the brightness can be adjusted to 8 steps by selecting the frequency division ratio. Thus, the total panel brightness can be adjusted at once and applied to the brightness of day or night. When BC\_ENA is pulled low, GSCLK is not divided. When BC\_ENA is pulled high, the brightness can be adjusted as shown in the following table.

| CODE                     | FREQUENCY DIVISION RATIO | RELATIVE BRIGHTNESS RATIO (%) |

|--------------------------|--------------------------|-------------------------------|

| MSB 000 LSB <sup>†</sup> | 1/1                      | 12.5                          |

| 001                      | 1/2                      | 25.0                          |

| 010                      | 1/3                      | 37.5                          |

| 011                      | 1/4                      | 50.0                          |

| 100                      | 1/5                      | 62.5                          |

| 101                      | 1/6                      | 75.0                          |

| 110                      | 1/7                      | 87.5                          |

| 111                      | 1/8                      | 100                           |

<sup>†</sup>BC\_ENA is low.

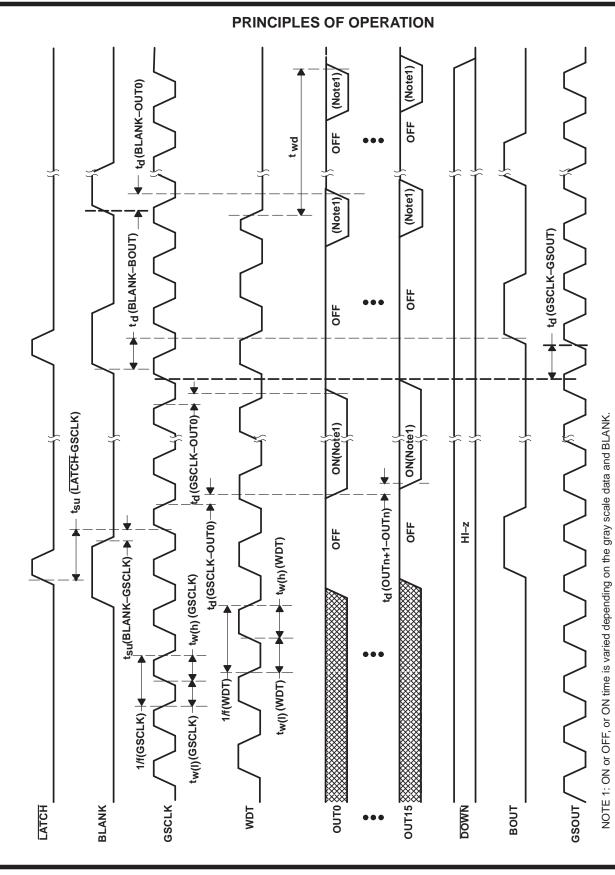

## constant output current operation

The constant current output turns on (sink constant current) if all the gray-scale data latched into the gray-scale latch is not zero on the falling edge of GCLK, after the next rising edge of GCLK when BLANK goes from high to low. After that, the number of the falling edge is counted by the 8-bit gray scale counter. Output counted that corresponds to gray-scale data is turned off (stop to sink constant current). If the shift register for gray scale is updated during LATCH high, data on the gray-scale data latch is also updated, affecting the number of gray scale of constant current output. Accordingly, during the on state of constant current output, LATCH is kept to low and the gray-scale data latch is held. When unconnected constant current output terminals exist, operation is complete after writing zero (data for LED turn off) to the corresponding gray-scale data latch. If this action is not completed, the supply current (I<sub>PVCC</sub>) in the constant current driver portion increases.

#### protection

This device incorporates WDT and TSD functions. In WDT or TSD functions, the current output is stopped (Logic portion is still operating). By monitoring the  $\overline{\text{DOWN}}$  terminal, these failures are detected immediately. Since  $\overline{\text{DOWN}}$  output is configured as an open collector, outputs of multiple ICs are brought together.

#### **WDT**

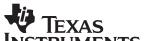

When the scan signal is stopped during a fixed period in dynamic scanning operation, the constant current output is turned off, preventing the LED from burning damage. The time detected can be set using the external capacitor (C1). The typical value is approximately 3 ms without a capacitor, 33 ms with a 1000 pF capacitor, and 300 ms with a 0.01  $\mu\text{F}$  capacitor. Once the scan signal is applied again, the abnormal status is released and normal operation is resumed. During static operation, the WDT function is disabled, connecting WD\_CAP to GND. The scan signal should be applied to the WDT terminal even though the WDT function is not used.

Figure 2. WDT Usage Example

Figure 1. WDT Operational Time

#### TSD (thermal shutdown)

When the junction temperature exceeds the limit, TSD functions and turns the constant current output off. When TSD is used, TS\_ENA is pulled high. When TSD is not used, TS\_ENA is pulled low. To recover to normal operation, the power supply is turned off or TS\_ENA is pulled low.

#### noise reduction

#### concurrent switching noise reduction

The concurrent switching noise has a potential to occur when multiple outputs turn on or off at the same time. To prevent this noise, the device has delay output terminals such as GSOUT and BOUT for GSCLK and BLANK respectively. Connecting these outputs to GSCLK and BLANK terminals of the next stage IC allows differences in the switching time between ICs to be made. When GSCLK is output to GSOUT through the device, duty is changed, so that the number of stages to be connected will be limited to a maximum of 10 at GSCLK = 4 MHz.

#### output slope

The on and off time of constant current output at an output current of 80 mA is approximately 150 ns and 250 ns respectively. It is effective in reducing concurrent switching noise that occurs when multiple outputs turn on or off at the same time.

#### delay between constant current output

The constant current output has a delay time of approximately 8 ns between output. It means approximately 120 ns delay time exists between OUT0 and OUT15. This time difference by delay is effective for reduction of concurrent switching noise as well as output slope. This delay time has the same value at 8-bits or 16-bits operation mode.

#### noise reduction (continued)

#### power supply

VCCLOG, VCCANA, and PVCC are supplied by a single power supply to minimize voltage differences between these terminals.

The bypass capacitor is located between power supply and GND to eliminate the variation of power supply voltage.

#### **GND**

Although GNDLOG, GNDANA, and GNDLED are internally tied together, these terminals should be externally connected to reduce noise influence.

## heat sink pad

The heat sink pad should be connected to GND to eliminate the noise influence since it is connected to the bottom side of the IC chip. Also, the desired thermal effect is obtained by connecting this pad to the PCB pattern with better thermal conductivity.

NOTES: A. IC is mounted on PCB. PCB size:  $102 \times 76 \times 1.6$  [mm<sup>3</sup>], four layers with internal two layer having plane. The thermal pad is soldered to PCB pattern of 10 mm<sup>2</sup>. For operation above 25°C free-air temperature, derate linearly at the rate of 38.2 mW/°C.

$VCCLOG = VCCANA = PVCC = 5 \text{ V}, I_{OL(C)} = 80 \text{ mA}, I_{CC} \text{ is typical value}$

B. Consider thermal characteristics when selecting the material for the PCB, since the temperature will rise around the thermal pad.

Figure 3. Power Rating

$$\begin{split} \text{Conditions: V}_O &= 1 \text{ V, V}_{(IREF)} &= 1.24 \text{ V} \\ I_{OL(C)}(mA) &\neq \frac{V_{(IREF)}(V)}{R_{(IREF)}(k\Omega)} \times 38 \\ R_{(IREF)}(k\Omega) &\neq \frac{47}{I_{OL(C)}(mA)} \end{split}$$

NOTE: The output current is at 16 bit output.

When 8-bit output, it will be the current of sum of two outputs. This sum current should be set up with the range of 10 mA to 120 mA. The resistor, R<sub>IRF</sub>, should be located as close as possible to IREF terminal to eliminate the noise influence.

Figure 4. Current on Constant Current Output vs External Resistor

NOTE: VCCLOG = VCCANA = PVCC = 5 V, T<sub>A</sub> = 25°C.

Figure 5. Current on Constant Current Output vs Voltage Applied To Constant Current Output Terminal

Figure 6. Timing Diagram (Shift Register for Gray Scale Data)

Figure 7. Timing Diagram (Brightness Control Register)

TEXAS

Figure 8. Timing Diagram (Constant Current Output)

TEXAS

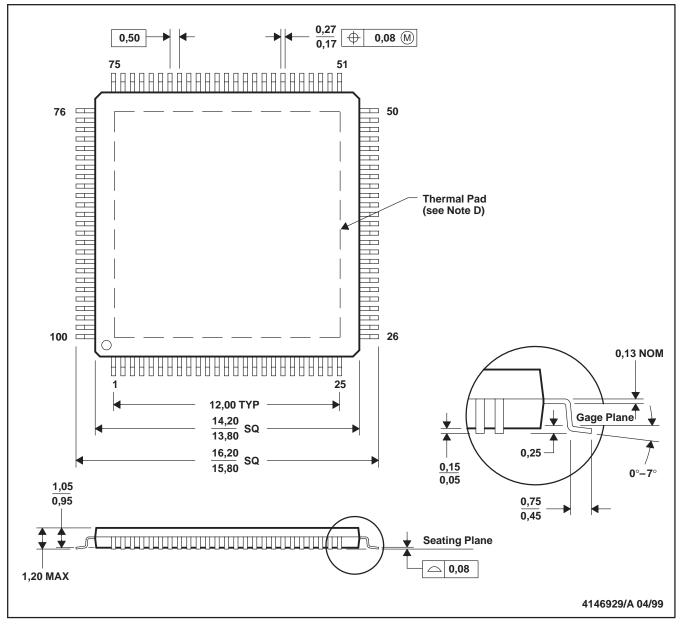

#### **MECHANICAL DATA**

# PZP (S-PQFP-G100)

#### PowerPAD™ PLASTIC QUAD FLATPACK

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane.

This pad is electrically and thermally connected to the backside of the die and possibly selected leads. The dimensions of the thermal pad are 2 mm × 2 mm (maximum). The pad is centered on the bottom of the package.

- E. Falls within JEDEC MS-026

PowerPAD is a trademark of Texas Instruments Incorporated.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated