## Features

- Low cost 32768Hz crystal

- Low power consumption

- Operating voltage: 2.5V to 5.5V (CPT mode) 2.0V to 5.5V (ABR mode)

- Call progress tone decoder

- Fully decoded tristate call progress status output

- Works with traditional precision or PBX call progress tones

## **General Description**

The HT9020 provides two modes; Call progress tone decoder and Busy redial controller, to support the application fields.

### Standard call progress tone decoder

This feature detects a specified input signal and then outputs relative envelopes during a 2.32sec interval. Three tristate output pins (DIAL, RBK, BUSY) indicate the presence of a dial tone, ringback tone or busy/reorder tone respectively, so it provides information that enables the microprocessor to decide whether to initiate, continue or terminate calls.

## **Selection Table**

| Busy redial controller |  |

|------------------------|--|

| - Depect times 2 10 cm |  |

- Repeat times: 3, 10 or 15 times

(2, 5, 15 times by mask option)

- 4.65<mark>, 32.6 and 62.8 se</mark>c break time

- (16.3sec by mask option)

- Auto-terminate after 30 times (default) ringback tone receipt

### **Busy redial controller**

This feature implements a busy redial function. After decoding, if the line is busy, this device forces the dialer to break for 62.8 sec, then triggers the redial key after the dial tone receipt. If the receiver is still busy, the redial sequence will be repeated 10 times. If the receiver is ringing, the redial sequence will be terminated after 30 times of ringback tone receipt.

| Function<br>Part No. | Operating<br>Voltage                           | OSC<br>Frequency | CPT Decoder       | ABR<br>Repeat Times                          | ABR<br>Break Time                                   | Package    |

|----------------------|------------------------------------------------|------------------|-------------------|----------------------------------------------|-----------------------------------------------------|------------|

| HT9020A              | CPT mode<br>2.5V~5.5V<br>ABR mode<br>2.0V~5.5V | 32768Hz          | Full decoded      | 3/10/15 times<br>[2/5/15 by<br>metal option] | 4.65/32.6/62.8 sec<br>[16.3 sec by<br>metal option] | 18 DIP/SOP |

| НТ9020В              | CPT mode<br>2.5V~5.5V                          | 32768Hz          | CPT envelope only | _                                            | _                                                   | 8 DIP      |

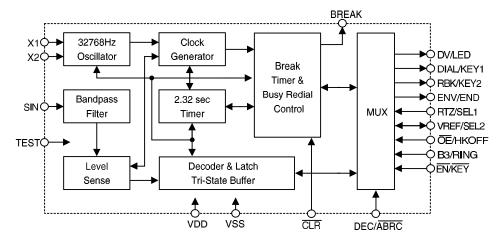

## **Block Diagram**

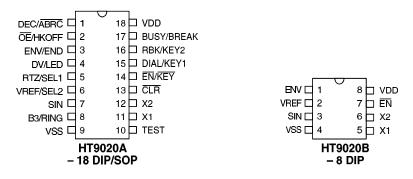

## **Pin Assignment**

## **Pin Description**

| Pin Name | I/O | Internal<br>Connection | Description                                                                                                                                                                                                                                                             |

|----------|-----|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEC/ABRC | I   | CMOS IN                | When this pin is connected to $V_{DD}$ , the chip is in the call progress tone decoder mode ( <b>CPTD mode</b> ) When this pin is connected to $V_{SS}$ , the chip is in the auto busy redial controller mode ( <b>ABRC mode</b> )                                      |

| OE/HKOFF | Ι   | CMOS IN                | $\begin{array}{c} \textbf{CPTD mode:} DIAL, RBK, BUSY and ENV pin tristate output \\ control pin. \overline{OE} = V_{DD}: Tristate output selected \\ \textbf{ABRC mode:} Off hook sense pin \\ HKOFF = V_{DD}: Reset controller and disable ABR operation \end{array}$ |

| Pin Name       | I/O | Internal<br>Connection         | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|-----|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENV/END        | 0   | CMOS OUT                       | <b>CPTD mode:</b> While an input signal is within specification, this pin will output the envelope relative to the input signal with a typical 40ms timing delay.<br><b>ABRC mode:</b> This is an ABR finished indicating signal output pin. When an ABR counter is full, this pin will output a 100ms pulse.                                                                                                                      |

| DV/LED         | 0   | CMOS OUT                       | <b>CPTD mode:</b> The call progress tone is decoded in this ready output pin. This pin can be used to trigger a microcontroller to read the latched data at DIAL, RBK and BUSY <b>ABRC mode:</b> ABR indicating signal output. While ABR is active, this pin will output a 0.86Hz, 25% duty cycle clock.                                                                                                                           |

| RTZ/SEL1       | Ι   | CMOS IN                        | <b>CPTD mode:</b> Output data return to zero select pin<br>RTZ=V <sub>DD</sub> ; The outputs of DIAL, RBK and BUSY will be<br>cleared when the input signal is out of specification while in<br>the 2.32 sec time window.<br>RTZ=V <sub>SS</sub> ; The outputs of DIAL, RBK and BUSY will be<br>latched until the next valid data is received.<br><b>ABRC mode:</b> Numbers of the busy redial and time of break<br>selection pin. |

| VREF/SEL2      | I/O | CMOS I/O<br>(VREF:O<br>SEL2:I) | $\begin{array}{c} \textbf{CPTD mode: } 1/2 \ V_{DD} \ reference \ voltage \ output \ pin \\ When \ \overline{EN} = V_{DD}, \ the \ device \ will \ be \ turned \ off \ and \ VREF \\ disabled. \ All \ outputs \ will \ be \ pulled \ low \ to \ reduce \ power \\ consumption. \\ \textbf{ABRC mode: } Number \ of \ the \ busy \ redial \ and \ time \ of \ break \\ selection \ pin. \end{array}$                               |

| SIN            | Ι   | CMOS IN                        | AC coupled analog signal input pin                                                                                                                                                                                                                                                                                                                                                                                                 |

| B3/RING        | Ι   | CMOS IN                        | <b>CPTD mode:</b> Received busy tone pattern select pin<br>B3=V <sub>DD</sub> ; BUSY will be set after three successive busy tones<br>are received.<br>B3=V <sub>SS</sub> ; BUSY will be set immediately after a busy tone is<br>received.<br><b>ABRC mode:</b> Ringer detection input pin                                                                                                                                         |

| VSS            | _   | _                              | Negative power supply<br>2.5~5.5V for CPT mode operation<br>2.0~5.5V for ABR mode operation                                                                                                                                                                                                                                                                                                                                        |

| VDD            | —   |                                | Positive power supply, 2.5~5.5V for normal operation                                                                                                                                                                                                                                                                                                                                                                               |

| BUSY/<br>BREAK | 0   | CMOS OUT                       | <b>CPTD mode:</b> BUSY=HIGH: The detected input signal is a busy or reorder tone<br><b>ABRC mode:</b> When in ABR mode, the BREAK pin will be high. After a busy tone is detected it will return low.<br>When the break timer has timed out, it will return high.                                                                                                                                                                  |

| Pin Name  | I/O | Internal<br>Connection | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-----|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBK/KEY2  | 0   | CMOS OUT               | <b>CPTD mode:</b> RBK=HIGH: The detected input signal is a ringback tone.<br><b>ABRC mode:</b> Transmission gate input or output pin. Used to trigger the row and column pin of the redial key when a dial tone is received. It will output a 100ms pulse.                                                                                                                                                                                                                                         |

| DIAL/KEY1 | 0   | CMOS OUT               | <b>CPTD mode:</b> DIAL=HIGH; The detected input signal is a dial tone.<br><b>ABRC mode:</b> Transmission gate input or output pin. Used to trigger the row and column pin of the redial key when a dial tone is received. It will output a 100ms pulse.                                                                                                                                                                                                                                            |

| EN/KEY    | Ι   | CMOS IN                | $\label{eq:cptd} \begin{array}{ c c c c c } \hline \textbf{CPTD mode: } \overline{EN} = V_{SS}; \text{ Normal operation mode} \\ \hline \overline{EN} = V_{DD}; \text{ Device disabled. The oscillator stops and all output} \\ \text{pins are pulled low or high impedance.} \\ \hline \textbf{ABRC mode: } \text{The pin is schmitt trigger input structure.} \\ \text{Active low. Applying a negative going pulse to this pin can} \\ \text{toggle the auto-busy-redial function.} \end{array}$ |

| CLR       | Ι   | CMOS IN                | When $\overline{\text{CLR}}$ is low and BREAK is high, the tone decoder is reset. This pin can be connected to the mute pin of the dialer IC for tone elimination.                                                                                                                                                                                                                                                                                                                                 |

| X1        | Ι   | OSCILLATOR             | The system oscillator consists of an inverter, a bias resistor<br>and the necessary load capacitor on-chip. Connect a standard<br>32.768kHz crystal or ceramic resonator.                                                                                                                                                                                                                                                                                                                          |

| X2        | 0   | OSCILLATOR             | X1 and X2 terminals implement the oscillator function.<br>The oscillator is turned off in the standby mode, and is<br>actuated whenever a keyboard entry is detected.                                                                                                                                                                                                                                                                                                                              |

| TEST      | Ι   | CMOS IN<br>Pull-low    | For testing only, active high                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

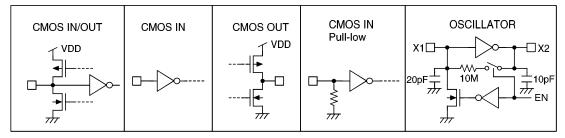

## Approximate internal connection circuits

## **Absolute Maximum Ratings\***

| Supply Voltage | –0.3V to 6V                           |

|----------------|---------------------------------------|

| Input Voltage  | $V_{SS}0.3V$ to $V_{DD}\mbox{+-}0.3V$ |

| Storage Temperature   | –55°C to 150°C |

|-----------------------|----------------|

| Operating Temperature | .–20°C to 75°C |

\*Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

## **Electrical Characteristics**

| Chal                               | Demonster                       |                 | <b>Test Conditions</b>                    | Min.    | <b>T</b> | Max. | Unit |  |

|------------------------------------|---------------------------------|-----------------|-------------------------------------------|---------|----------|------|------|--|

| Symbol                             | Parameter                       | V <sub>DD</sub> | Conditions                                | wiin.   | Тур.     | max. | Unit |  |

| V                                  | On anoting Valtage              |                 | CPT mode                                  | 2.5     | _        | 5.5  | V    |  |

| V <sub>DD</sub>                    | Operating Voltage               |                 | ABR mode                                  | 2.0     | _        | 5.5  | V    |  |

| I                                  | Openeting Current               | 5V              | Functions enabled                         | _       | _        | 2    | mA   |  |

| I <sub>DD</sub>                    | Operating Current               |                 | No load                                   | _       | _        | 0.8  | mA   |  |

| I <sub>STB</sub>                   | Standby Current                 | 2.5V            | Functions disabled or EN=1                | _       | _        | 1    | μΑ   |  |

| CDV                                | Detection Lovel                 | 5V              | f <sub>IN</sub> =305~640Hz                | -36     | _        | 0    | dBm  |  |

| GDV                                | Detection Level                 |                 | ENV=1                                     | -42     | _        | -8   | dBm  |  |

| Grl                                | Rejection Level                 | _               | All frequency, ENV=0                      | _       | _        | -50  | dBm  |  |

| f <sub>RL</sub><br>f <sub>RH</sub> | Rejection Out-band<br>Frequency | _               | V≤ 0 dBm, ENV=0                           | <br>800 | _        | 200  | Hz   |  |

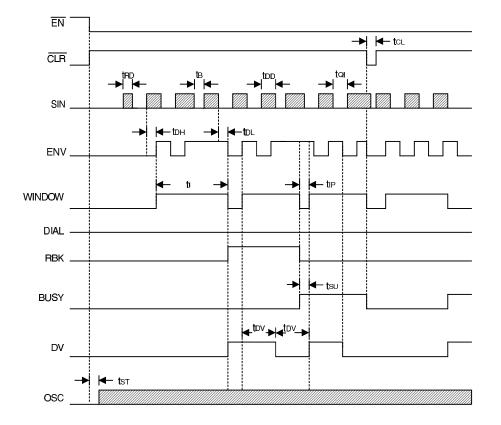

| t <sub>DD</sub>                    | Detection Signal Time           |                 | In-band signal input,<br>ENV=1            | 40      | _        |      | ms   |  |

| t <sub>RD</sub>                    | Rejection Noise Time            |                 | Any signal input,<br>ENV=0                | _       | _        | 20   | ms   |  |

| t <sub>DH</sub><br>t <sub>DL</sub> | Envelope Output<br>Delay Time   | _               | Time to output high<br>Time to output low | _       | 40       | _    | ms   |  |

| t <sub>DV</sub>                    | Data Valid Output Time          | _               | Time to output high/low                   | 1.05    | 1.16     | 1.2  | sec  |  |

| tsu                                | Data Setup Time                 | _               | _                                         | 3       | 4        | 5    | ms   |  |

| tI                                 | Interval Time                   | _               | Internal signal                           | _       | 2.32     | _    | sec  |  |

| t <sub>IP</sub>                    | Interval Pause Time             | _               | Internal signal                           | 8       |          | _    | ms   |  |

| tCL                                | Clear Time                      | _               | _                                         | _       | 250      | _    | ns   |  |

| t <sub>ST</sub>                    | OSC Start Up Time               | _               | _                                         | _       | 0.8      | 2    | sec  |  |

| ZI                                 | Input Impedance                 |                 | f <sub>IN</sub> =200~3.4kHz               | 1.0     | _        | _    | MΩ   |  |

| V <sub>REF</sub>                   | Reference Voltage               | —               | No load                                   | 2.4     | 2.5      | 2.6  | V    |  |

| Ch - l           | Demonstern                           | Test Conditions                         |                                                |      | <b>T</b> |      | T    |  |

|------------------|--------------------------------------|-----------------------------------------|------------------------------------------------|------|----------|------|------|--|

| Symbol           | Parameter                            | V <sub>DD</sub>                         | DD Conditions                                  |      | Тур.     | Max. | Unit |  |

| Z <sub>REF</sub> | Output Impedance                     | _                                       | _                                              |      | 10       | 20   | MΩ   |  |

| V <sub>IH</sub>  | Logic Input High Voltage             | 5V                                      | _                                              | 3.5  | _        | _    | V    |  |

| V <sub>IL</sub>  | Logic Input Low Voltage              | 5V                                      | _                                              |      | _        | 1.5  | V    |  |

| I <sub>IH</sub>  | Logic Input High Current             | 5V                                      | V <sub>IH</sub> =5.0V                          |      | _        | 0.1  | μA   |  |

| I <sub>IL</sub>  | Logic Input Low Current              | 5V                                      | V <sub>IL</sub> =0V                            | -0.1 | _        | _    |      |  |

| Іон              | Output High Current                  | 5V                                      | V <sub>OH</sub> =4.5V                          |      | _        | -0.5 | mA   |  |

| IOL              | Output Low Current                   | 5V                                      | V <sub>OL</sub> =0.5V                          | 2.0  | _        | _    | mA   |  |

| I <sub>LKH</sub> | Output Disable                       | 5V                                      | V <sub>LKH</sub> =5.0V                         | _    | _        | 0.1  | μA   |  |

| I <sub>LKL</sub> | Leakage Current                      | 5V                                      | V <sub>LKL</sub> =0V                           | -0.1 | _        |      | μA   |  |

| I <sub>SO</sub>  | Pull Down Current                    | 5V                                      | _                                              | _    | 25       | 35   | μA   |  |

| I <sub>DR</sub>  | Pull Up Current                      | 5V                                      | _                                              |      | 25       | 35   | μA   |  |

| Gdl              | Detection Land                       | 2.5V                                    | 2.5V                                           | -42  | _        | -8   | dBm  |  |

| GDL              | Detection Level                      | 1 Level 5.0V f <sub>IN</sub> =305~640Hz |                                                | -36  | _        | 0    | dBm  |  |

| Grl              | Rejection Level                      | 5V                                      | All frequency                                  |      | _        | -50  | dBm  |  |

| f <sub>ROL</sub> | Rejection Out-band<br>Low Frequency  | 5V                                      | V<0 dBm, ENV=0                                 |      |          | 200  | Hz   |  |

| f <sub>ROH</sub> | Rejection Out-band<br>High Frequency | 5V                                      | V<0 dBm, ENV=0                                 | 800  | _        | _    | Hz   |  |

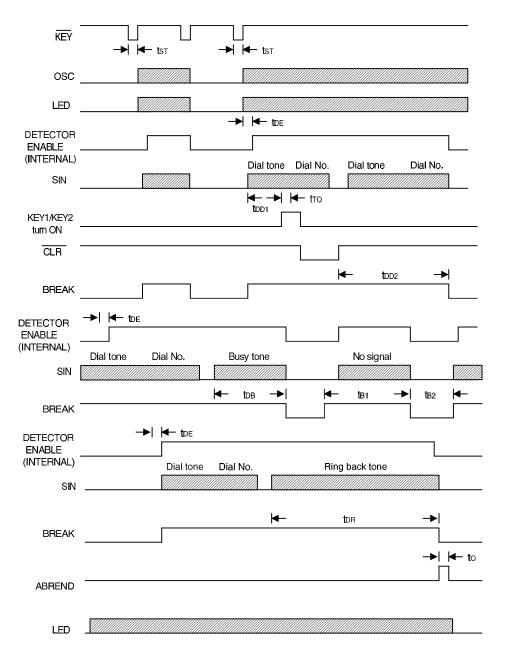

| t <sub>DD1</sub> | Detection Time                       | 5V                                      | In-band dial tone                              | 2.1  | 3.32     | 3.0  | sec  |  |

| t <sub>DD2</sub> | Detection Time                       | 5V                                      | In-band dial tone                              | 6.5  | 7.0      | 8.0  | sec  |  |

| t <sub>DB</sub>  | Detection Busy Time                  | 5V                                      | In-band busy tone                              | 6.8  | 7.5      | 8.2  | sec  |  |

| t <sub>DR</sub>  | Detection Ringer Time                | 5V                                      | 30 Times ringback tone<br>(2 sec On/4 sec Off) | 150  | 180      | 210  | sec  |  |

| t <sub>DN</sub>  | Detection Time                       | 5V                                      | No signal                                      | 25   | 30.2     | 35   | sec  |  |

| tDE              | Detection Enable Time                | 5V                                      | _                                              | 0.2  | 30.2     | 35   | sec  |  |

| t <sub>TO</sub>  | RELI, O Turn on Time                 | 5V                                      | _                                              | 80   | 100      | 120  | ms   |  |

| to               | ABREND Output Time                   | 5V                                      | —                                              | 80   | 100      | 120  | ms   |  |

| t <sub>B1</sub>  | Break Time                           | 5V                                      | After a busy tone is detected                  | 60.0 | 62.8     | 65.0 | sec  |  |

| t <sub>B2</sub>  | (t <sub>B1</sub> +2.3sec)            | 5V                                      | After no signal is detected                    | 62.0 | 65.1     | 68.0 | sec  |  |

| Ron              | Transition on Resistor               | 5V                                      | V <sub>RDLI</sub> =5.0V, V <sub>RDLO</sub> =0V | _    | 500      | 100  | Ω    |  |

| Roff             | Gate Output off Resistor             | 5V                                      | V <sub>RDLI</sub> =0V, V <sub>RDLO</sub> =5.0V | 10   | _        | _    | MΩ   |  |

# **Functional Description**

## Decoder

The HT9020 call progress tone decoder (DEC/ $\overline{ABRC}$ =V<sub>DD</sub>) can be used in the U.S.A. and many other countries in the world. The signal format, truth table and timing of the decoder are shown below.

| Tone                     | Frequency                    | Condition                                                 |  |  |

|--------------------------|------------------------------|-----------------------------------------------------------|--|--|

| Precision Dial Tone      | 350Hz + 440Hz                | Continuous                                                |  |  |

| Old Dial Tone            | 120Hz(or 133Hz,) + 600Hz     | Continuous                                                |  |  |

| Precision Busy Tone      | 480Hz + 620Hz                | 0.5sec On and 0.5sec Off                                  |  |  |

| Old Busy Tone            | 120Hz + 600Hz                | 0.5sec On and 0.5sec Off                                  |  |  |

| Precision Reorder Tone   | 480Hz + 620Hz                | 0.3sec On and 0.2sec Off                                  |  |  |

| Old Reorder Tone         | 120Hz + 600Hz                | 0.2sec On and 0.3sec Off or 0.25sec<br>On and 0.25sec Off |  |  |

| Precision Ring-back Tone | 440Hz + 480Hz                | 2sec On and 4sec Off                                      |  |  |

| Old Ring-back Tone       | 40Hz (or the others) + 420Hz | 2sec On and 4sec Off                                      |  |  |

### The signal format of the call progress tone

## The truth table of the decoder

| Tone           | Transition No. | DIAL | RBK  | BUSY | DV | <b>OE</b> /HKOFF |

|----------------|----------------|------|------|------|----|------------------|

| Initial        | _              | 0    | 0    | 0    | 0  | 0                |

| Dial           | 1              | 1    | 0    | 0    | 1  | 0                |

| Ringback       | 2~4            | 0    | 1    | 0    | 1  | 0                |

| Busy/Reorder   | 5~16           | 0    | 0    | 1    | 1  | 0                |

| Overflow       | over 16        | 0    | 0    | 0    | 1  | 0                |

| Output Disable | —              | Hi-Z | Hi-Z | Hi-Z | *  | 1                |

Notes: Hi-Z: Hi impedance

\*: previous state

## Decoder timing diagrams

#### **ABR controller**

Initial state:

- RDLO=Hi-Impedance

- RDLI=Hi-Impedance

- BREAK=Low

- ABRI=Low

If a negative transition is received on the ABR pin, then the Auto-busy-dial function will be executed, and the LED pin will output a 0.86Hz (duty=0.25) clock. If the device detects a dial tone, KEY1 and KEY2 pins output a 100ms pulse to trigger the redial key of the telephone dialer. The dial tone will be ignored after the redial key is triggered.

If a busy/reorder tone for three successive windows is received or the line signal is off for 30.2secs or a dial tone appears again for more than 7 secs after the number is dialed-out, the device will turn on the internal register to implement the following control:

- Turn off the filter

- BREAK pin output low for on-hook switch control

- The on-hook timer starts counting the break time

After the break timer has timed-out, the redial will be executed again. If the repeat-number ends, the OVER pin will output a 100ms high pulse to automatically reset to the initial state.

If the receiver does not answer within 30 cycles, a ringback tone is produced, and the OVER pin will output a 100ms high pulse to automatically reset to the initial state.

| The bre | eak tim | e and | repeat i | nu | mber setting |

|---------|---------|-------|----------|----|--------------|

|         |         |       |          |    |              |

| SEL1 | SEL2 | Repeat No.<br>(times) | Break Time<br>(seconds) |                 |

|------|------|-----------------------|-------------------------|-----------------|

|      |      |                       | t <sub>B1</sub>         | t <sub>B2</sub> |

| 0    | 0    | 10                    | 62.8                    | 84.9            |

| 0    | 1    | 10                    | 32.6                    | 34.9            |

| 1    | 0    | 3                     | 62.8                    | 64.9            |

| 1    | 1    | 15                    | 4.65                    | 6.97            |

### ABR controller timing diagrams

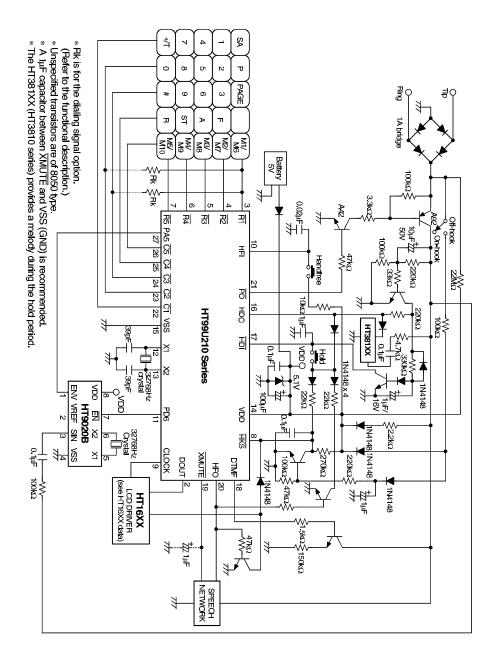

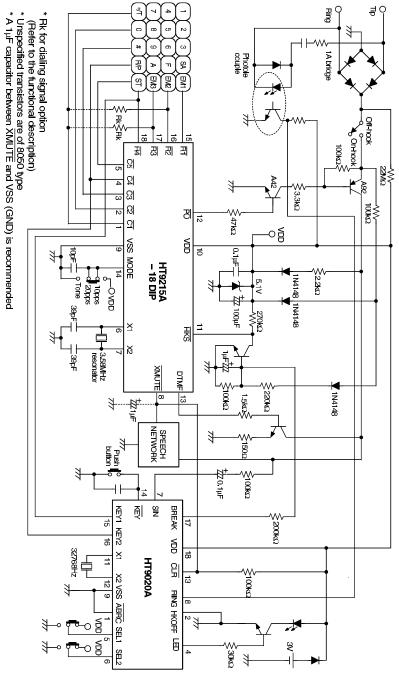

# **Application Circuits**

## **Application Circuit 1**

### **Application Circuit 2**