# 查询LT6555供应商 LINEAR TECHNOLOGY

### 捷多邦,专业PCB打样工厂,24小时加急出货

## LT6555

## FEATURES

- 650MHz 3dB Small Signal Bandwidth

- 450MHz –3dB 2V<sub>P-P</sub> Large-Signal Bandwidth

- **120MHz ±0.1dB Bandwidth**

- High Slew Rate: 2200V/µs

- Fixed Gain of 2; No External Resistors Required

- 72dB Channel Separation at 10MHz

- 50dB Channel Separation at 100MHz

- –80dBc 2nd Harmonic Distortion at 10MHz, 2V<sub>P-P</sub>

- –70dBc 3rd Harmonic Distortion at 10MHz, 2V<sub>P-P</sub>

- Low Supply Current: 9mA per Amplifier

- 6.5ns 0.1% Settling Time for 2V Step

- I<sub>SS</sub>  $\leq$  500µA per Amplifier when Disabled

- Differential Gain of 0.033%, Differential Phase of 0.022°

- Wide Supply Range: ±2.25V (4.5V) to ±6V (12V)

- Available in 24-Lead SSOP and 24-Lead QFN Packages

## **APPLICATIONS**

- RGB Amplifiers

- UXGA Video Multiplexing

- LCD Projectors

## TYPICAL APPLICATION

#### **RGB** Multiplexer and Line Driver I T6555 RINA G<sub>INA</sub> B<sub>INA</sub> ₹ $75\Omega$ 750 Rout 75Ω Ž<sup>75Ω</sup> $75\Omega$ 75C GOUT 75Ω RINB GINB ₹75Ω ▼ 75Ω ≹<sub>75Ω</sub> ∀ B<sub>OUT</sub> 75Ω SELECT A/B ENABLE $75\Omega$ DGND c.com

650MHz Gain of 2 Triple 2:1Video Multiplexer

## DESCRIPTION

The LT<sup>®</sup>6555 is a high speed triple 2:1 video multiplexer with an internally fixed gain of 2. The individual amplifiers are optimized for performance with a double terminated 75 $\Omega$  video load and feature a –3dB 2V<sub>P-P</sub> bandwidth of 450MHz, making them ideal for driving very high resolution video signals. Separate power supply pins for each amplifier boost channel separation to 72dB, allowing the LT6555 to excel in many high speed applications.

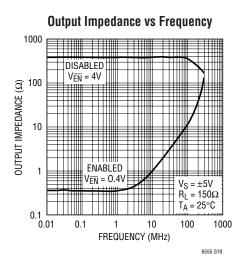

While the performance of the LT6555 is optimized for dual supply operation, it can also be operated with a single supply as low as 4.5V. Using dual 5V supplies, each amplifier draws only 9mA. When disabled, the amplifiers draw less than  $500\mu$ A and the outputs become high impedance.

The LT6555 is manufactured on Linear Technology's proprietary low voltage complementary bipolar process and is available in 24-lead SSOP and ultra-compact 24-lead QFN packages.

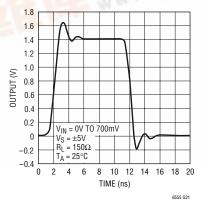

#### Video Amplitude Transient Response

## ABSOLUTE MAXIMUM RATINGS (Note 1)

| Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> ) | 12.6V      |

|----------------------------------------------------------|------------|

| Input Current (Note 2)                                   | ±10mA      |

| Output Current (Continuous)                              | ±70mA      |

| EN to DGND Voltage (Note 2)                              | 5.5V       |

| SEL to DGND Voltage (Note 2)                             | 8V         |

| Output Short-Circuit Duration (Note 3)                   | Indefinite |

| Operating Temperature Range (Note 4) –40                 | °C to 85°C |

| Specified Temperature Range (Note 5) –40                 | °C to 85°C |

| Junction Temperature                 |                  |

|--------------------------------------|------------------|

| SSOP                                 | 150°C            |

| QFN                                  | 125°C            |

| Storage Temperature Range            |                  |

| SSOP                                 | .–65°C to 150°C  |

| QFN                                  | . –65°C to 125°C |

| Lead Temperature (Soldering, 10 sec) |                  |

| SSOP                                 | 300°C            |

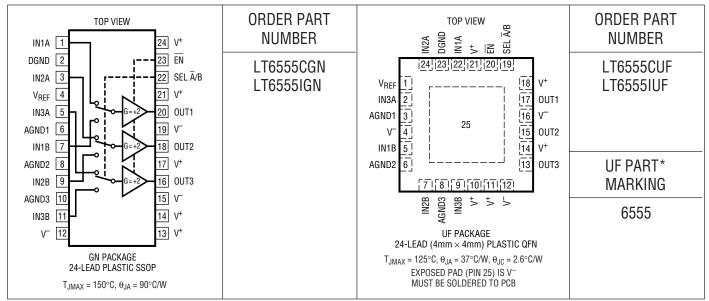

## PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>S</sub> = ±5V, R<sub>L</sub> = 150 $\Omega$ , C<sub>L</sub> = 1.5pF, V<sub>EN</sub> = 0.4V, V<sub>AGND</sub>, V<sub>DGND</sub>, V<sub>VREF</sub> = 0V.

| SYMBOL               | PARAMETER                            | CONDITIONS                                                    |   | MIN   | ТҮР   | MAX        | UNITS    |

|----------------------|--------------------------------------|---------------------------------------------------------------|---|-------|-------|------------|----------|

| V <sub>OS</sub>      | Input Referred Offset Voltage        | $V_{IN} = 0V, V_{OS} = V_{OUT}/2$                             |   |       | 5     | ±16<br>±24 | mV<br>mV |

| I <sub>IN</sub>      | Input Current                        |                                                               | • |       | -17   | ±45        | μΑ       |

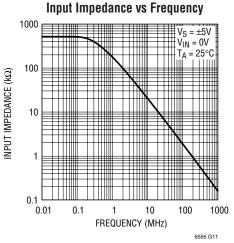

| R <sub>IN</sub>      | Input Resistance                     | $V_{IN} = \pm 1 V$                                            | • | 100   | 400   |            | kΩ       |

| CIN                  | Input Capacitance                    | f = 100kHz                                                    |   |       | 1     |            | pF       |

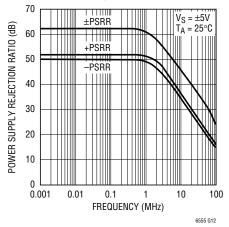

| PSRR                 | Power Supply Rejection Ratio         | $V_{\rm S} = \pm 2.25 V \text{ to } \pm 6 V \text{ (Note 6)}$ | • | 56    | 62    |            | dB       |

| I <sub>PSRR</sub>    | Input Current Power Supply Rejection | $V_{\rm S} = \pm 2.25 V \text{ to } \pm 6 V \text{ (Note 6)}$ | • |       | 1     | ±4         | μA/V     |

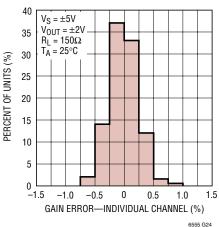

| A <sub>V</sub> ERR   | Gain Error                           | $V_{OUT} = \pm 2V$ , Nominal Gain 2V/V                        | • |       |       | ±2.5       | %        |

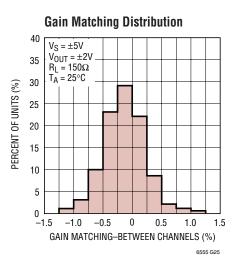

| A <sub>V</sub> MATCH | Gain Matching                        | Any One Channel to Another                                    |   |       | ±0.33 |            | %        |

| V <sub>OUT</sub>     | Output Voltage Swing                 | (Note 7)                                                      |   | ±3.15 | ±3.4  |            | V        |

|                      |                                      |                                                               | • | ±3.0  |       |            | V        |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>S</sub> = ±5V, R<sub>L</sub> = 150 $\Omega$ , C<sub>L</sub> = 1.5pF, V<sub>EN</sub> = 0.4V, V<sub>AGND</sub>, V<sub>DGND</sub>, V<sub>VREF</sub> = 0V.

| SYMBOL                          | PARAMETER                                           | CONDITIONS                                                                            |   | MIN         | ТҮР        | MAX        | UNITS             |

|---------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------|---|-------------|------------|------------|-------------------|

| I <sub>S</sub>                  | Supply Current, Per Amplifier                       | $R_L = \infty$                                                                        | • |             | 9          | 12<br>14   | mA<br>mA          |

|                                 | Supply Current, Disabled, Per Amplifier             | $V_{\overline{EN}} = 4V, R_L = \infty$<br>$V_{\overline{EN}} = 0$ pen, $R_L = \infty$ | • |             | 47<br>42   | 500<br>500 | μA<br>μA          |

| IEN                             | Enable Pin Current                                  | $ \begin{array}{l} V_{\overline{EN}} = 0.4 V \\ V_{\overline{EN}} = 4 V \end{array} $ | • | -200<br>-75 | -95<br>-21 |            | μΑ<br>μΑ          |

| I <sub>SEL</sub>                | Select Pin Current                                  | V <sub>SEL</sub> = 0.4V<br>V <sub>SEL</sub> = 4V                                      | • | -50<br>-50  | 5<br>1     |            | μΑ<br>μΑ          |

| I <sub>SC</sub>                 | Output Short-Circuit Current                        | $R_L = 0\Omega, V_{IN} = \pm 1V$                                                      | • | ±50         | ±105       |            | mA                |

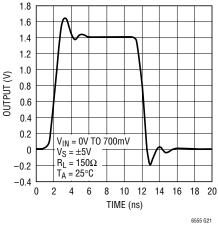

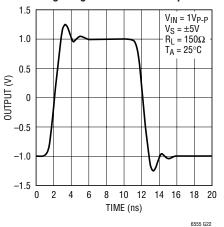

| SR                              | Slew Rate                                           | ±1V on ±2.5V Output Step (Note 8)                                                     |   | 1600        | 2200       |            | V/µs              |

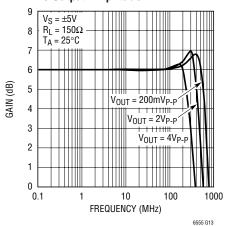

| –3dB BW                         | Small-Signal –3dB Bandwidth                         | $V_{OUT} = 200 \text{mV}_{P-P}$                                                       |   |             | 650        |            | MHz               |

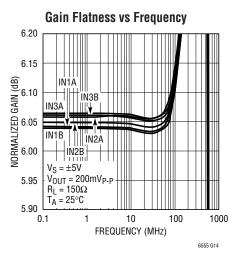

| 0.1dB BW                        | Gain Flatness ±0.1dB Bandwidth                      | $V_{OUT} = 200 \text{mV}_{P-P}$                                                       |   |             | 120        |            | MHz               |

| FPBW                            | Full Power Bandwidth 2V                             | $V_{OUT} = 2V_{P-P}$ (Note 9)                                                         |   | 250         | 350        |            | MHz               |

|                                 | Full Power Bandwidth 4V                             | $V_{OUT} = 4V_{P-P}$ (Note 9)                                                         |   |             | 175        |            | MHz               |

|                                 | All-Hostile Crosstalk                               | $f = 10MHz, V_{IN} = 1V_{P-P}$<br>f = 100MHz, V <sub>IN</sub> = 1V <sub>P-P</sub>     |   |             | -72<br>-50 |            | dB<br>dB          |

|                                 | Selected Channel to Unselected<br>Channel Crosstalk | $f = 10MHz$ , $V_{IN} = 1V_{P-P}$<br>$f = 100MHz$ , $V_{IN} = 1V_{P-P}$               |   |             | -80<br>-55 |            | dB<br>dB          |

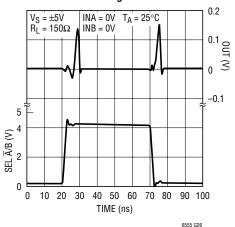

|                                 | Channel Select Output Transient                     | INA = INB = 0V                                                                        |   |             | 200        |            | mV <sub>P-P</sub> |

|                                 | Channel-to-Channel Select Time                      | INA = -1V, INB = 1V<br>from 50% SEL to V <sub>OUT</sub> = 0V                          |   |             | 8          |            | ns                |

| t <sub>S</sub>                  | Settling Time                                       | 0.1% of V <sub>FINAL</sub> , V <sub>STEP</sub> = 2V                                   |   |             | 6.5        |            | ns                |

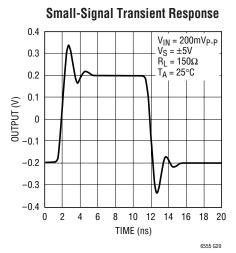

| t <sub>R</sub> , t <sub>F</sub> | Small-Signal Rise and Fall Time                     | 10% to 90%, V <sub>OUT</sub> = 400mV <sub>P-P</sub>                                   |   |             | 520        |            | ps                |

| dG                              | Differential Gain                                   | (Note 10)                                                                             |   |             | 0.033      |            | %                 |

| dP                              | Differential Phase                                  | (Note 10)                                                                             |   |             | 0.022      |            | Deg               |

| HD2                             | 2nd Harmonic Distortion                             | $f = 10MHz, V_{OUT} = 2V_{P-P}$                                                       |   |             | -80        |            | dBc               |

| HD3                             | 3rd Harmonic Distortion                             | $f = 10MHz, V_{OUT} = 2V_{P-P}$                                                       |   |             | -70        |            | dBc               |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** This parameter is guaranteed to meet specified performance through design and characterization. It is not production tested.

**Note 3:** As long as output current and junction temperature are kept below the Absolute Maximum Ratings, no damage to the part will occur. Depending on the supply voltage, a heat sink may be required.

**Note 4:** The LT6555C is guaranteed functional over the operating temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C.

**Note 5:** The LT6555C is guaranteed to meet specified performance from 0°C to 70°C. The LT6555C is designed, characterized and expected to meet specified performance from -40°C and 85°C but is not tested or QA sampled at these temperatures. The LT6555I is guaranteed to meet specified performance from -40°C to 85°C.

**Note 6:** In order to follow the constraints for 4.5V operation for PSRR and  $I_{PSRR}$  testing at ±2.25V, the DGND pin is set to V<sup>-</sup>, the EN pin is set to V<sup>-</sup> + 0.4V, and the SEL pin is set to either V<sup>-</sup> + 0.4V or V<sup>-</sup> + 4V. At ±6V and all other cases, DGND is set to ground and the EN and SEL pins are referenced from it.

**Note 7:** The  $V_{REF}$  pin is set to 1V when testing positive swing and -1V when testing negative swing to ensure that the internal input clamps do not limit the output swing.

**Note 8:** Slew rate is 100% production tested using both inputs of channel 2. Slew rates of channels 1 and 3 are guaranteed through design and characterization.

Note 9: Full power bandwidth is calculated from the slew rate:

$\mathsf{FPBW} = \mathsf{SR}/(\pi \bullet \mathsf{V}_{\mathsf{P}-\mathsf{P}})$

**Note 10:** Differential gain and phase are measured using a Tektronix TSG120YC/NTSC signal generator and a Tektronix 1780R video measurement set. The resolution of this equipment is better than 0.05% and 0.05°. Nine identical amplifier stages were cascaded giving an effective resolution of better than 0.0056% and 0.0056%.

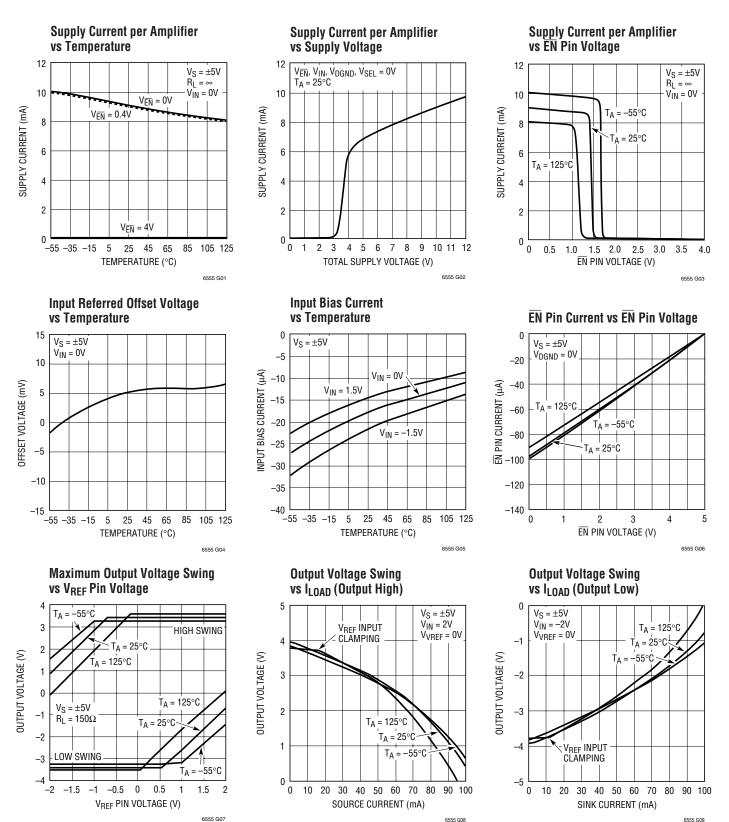

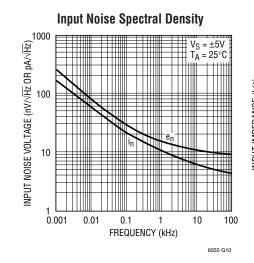

## **TYPICAL PERFORMANCE CHARACTERISTICS**

6555 G09

## TYPICAL PERFORMANCE CHARACTERISTICS

Input Referred PSRR vs Frequency

Frequency Response vs Output Amplitude

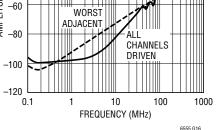

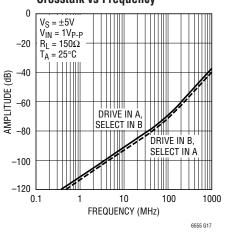

Crosstalk vs Frequency  $V_S = \pm 5V$   $V_{OUT} = 2V_{P,P}$   $R_L = 150\Omega$   $T_A = 25^{\circ}C$   $T_A = 25^{\circ}C$  MORST ADJACENT ADJACENTALL

**Crosstalk vs Frequency**

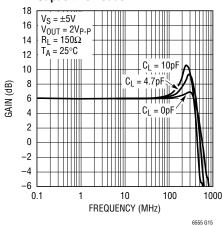

Frequency Response with Capacitive Loads

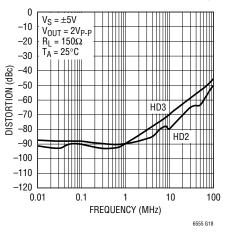

Harmonic Distortion vs Frequency

## TYPICAL PERFORMANCE CHARACTERISTICS

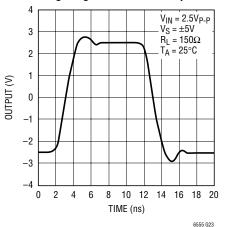

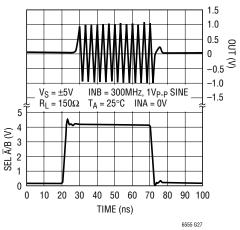

Video Amplitude Transient Response

Large-Signal Transient Response

Large-Signal Transient Response

Channel Switching Transient

**Gain Error Distribution**

**Channel Switching Transient**

## PIN FUNCTIONS (GN24 Package)

**IN1A (Pin 1):** Channel 1 Input A. This pin has a nominal impedance of  $400k\Omega$  and does not have any internal termination resistor.

**DGND (Pin 2):** Digital Ground Reference for Enable Pin. This pin is normally connected to ground.

**IN2A (Pin 3):** Channel 2 Input A. This pin has a nominal impedance of  $400k\Omega$  and does not have any internal termination resistor.

**V<sub>REF</sub> (Pin 4):** Voltage Reference for Input Clamping. This is the tap to an internal voltage divider that defines mid-supply. It is normally connected to ground in dual supply, DC coupled applications.

**IN3A (Pin 5):** Channel 3 Input A. This pin has a nominal impedance of  $400k\Omega$  and does not have any internal termination resistor.

**AGND1 (Pin 6):** Analog Ground for the  $360\Omega$  Gain Resistor of Channel 1.

**IN1B (Pin 7):** Channel 1 Input B. This pin has a nominal impedance of  $400k\Omega$  and does not have any internal termination resistor.

**AGND2 (Pin 8):** Analog Ground for the  $360\Omega$  Gain Resistor of Channel 2.

**IN2B (Pin 9):** Channel 2 Input B. This pin has a nominal impedance of  $400k\Omega$  and does not have any internal termination resistor.

**AGND3 (Pin 10):** Analog Ground for the  $360\Omega$  Gain Resistor of Channel 3.

**IN3B (Pin 11):** Channel 3 Input B. This pin has a nominal impedance of  $400k\Omega$  and does not have any internal termination resistor.

**V<sup>-</sup> (Pin 12):** Negative Supply Voltage. V<sup>-</sup> pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section.

V<sup>+</sup> (Pins 13, 14, 24): Positive Supply Voltage. V<sup>+</sup> pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section. **V**<sup>-</sup> (**Pin 15**): Negative Supply Voltage for Channel 3 Output Stage. V<sup>-</sup> pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section.

**OUT3 (Pin 16):** Channel 3 Output. It is twice the selected channel 3 input and performs optimally with a  $150\Omega$  load (a double terminated  $75\Omega$  cable).

**V**<sup>+</sup> (**Pin 17**): Positive Supply Voltage for Channels 2 and 3 Output Stages. V<sup>+</sup> pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section.

**OUT2 (Pin 18):** Channel 2 Output. It is twice the selected channel 2 input and performs optimally with a  $150\Omega$  load (a double terminated  $75\Omega$  cable).

**V<sup>-</sup> (Pin 19):** Negative Supply Voltage for Channels 1 and 2 Output Stages. V<sup>-</sup> pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section.

**OUT1 (Pin 20):** Channel 1 Output. It is twice the selected channel 1 input and performs optimally with a  $150\Omega$  load (a double terminated  $75\Omega$  cable).

**V**<sup>+</sup> (**Pin 21**): Positive Supply Voltage for Channel 1 Output Stage. V<sup>+</sup> pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section.

**SEL (Pin 22):** Select Pin. This high impedance pin selects which set of inputs are sent to the output pins. When the pin is pulled low, the A inputs are selected. When the pin is pulled high, the B inputs are selected.

**EN** (**Pin 23**): Enable Control Pin. An internal pull-up resistor of 46k defines the pin's impedance and will turn the part off if the pin is unconnected. When the pin is pulled low, the amplifiers are enabled.

**Exposed Pad (Pin 25, QFN Only):** The Exposed Pad is V<sup>-</sup> and must be soldered to the PCB. It is internally connected to the QFN Pin 4, V<sup>-</sup>.

## **APPLICATIONS INFORMATION**

#### **Power Supplies**

The LT6555 is optimized for  $\pm$ 5V supplies but can be operated on as little as  $\pm$ 2.25V or a single 4.5V supply and as much as  $\pm$ 6V or a single 12V supply. Internally, each supply is independent to improve channel isolation. **Do not leave any supply pins disconnected or the part may not function correctly!**

#### Enable/Shutdown

The LT6555 has a shutdown mode controlled by the  $\overline{EN}$  pin and referenced to the DGND pin. If the amplifier will be enabled at all times, the  $\overline{EN}$  pin can be connected directly to DGND. If the enable function is desired, either driving the pin above 2V or allowing the internal 46k pull-up resistor to pull the  $\overline{EN}$  pin to the top rail will disable the amplifier. When disabled, the DC output impedance will rise to approximately 360 $\Omega$  through the internal feedback and gain resistors. Supply current into the amplifier in the disabled state will be:

$$I_S = \frac{V^+ - V_{\overline{EN}}}{46k} + \frac{V^+ - V^-}{80k}$$

It is important that the following constraints on the DGND,  $\overline{EN}$  and SEL pins are always followed:

$$\begin{array}{l} V^{+}-V_{DGND} \geq 4.5V \\ V_{EN}-V_{DGND} \leq 5.5V \\ V_{SEL}-V_{DGND} \leq 8V \end{array}$$

In dual supply cases where V<sup>+</sup> is less than 4.5V, DGND should be connected to a potential below ground, such as V<sup>-</sup>. Since the EN and SEL pins are referenced to DGND, they may need to be pulled below ground in those cases.

In single supply applications above 5.5V, an additional resistor may be needed from the EN pin to DGND if the pin is ever allowed to float. For example, on a 12V single supply, a 33k resistor would protect the pin from floating too high while still allowing the internal pull-up resistor to disable the part.

On dual ±2.25V supplies, connecting the DGND pin to V<sup>-</sup> is the only way of ensuring that V<sup>+</sup> – V<sub>DGND</sub>  $\geq$  4.5V.

The DGND pin should not be pulled above the  $\overline{EN}$  pin since doing so will turn on an ESD protection diode. If the  $\overline{EN}$  pin voltage is forced a diode drop below the DGND pin, current should be limited to 10mA or less.

The enable/disable times of the LT6555 are fast when driven with a logic input. Turn on (from 50% EN input to 50% output) typically occurs in less than 50ns. Turn off is slower, but is typically below 500ns.

### **Channel Select**

The SEL pin uses the same internal threshold as the  $\overline{EN}$  pin and is also referenced to DGND. When the pin is logic low, the channel A inputs are passed to the output. When the pin is logic high, the channel B inputs are passed to the output. The pin should not be floated but can be tied to DGND to force the outputs to always be channel A or to V<sup>+</sup> (when less than 8V) to force the outputs to always be channel B.

| SEL A/B | EN | OUT          |

|---------|----|--------------|

| 0       | 0  | 2 	imes IN A |

| 1       | 0  | 2 	imes IN B |

| Х       | 1  | OFF          |

### **Input Considerations**

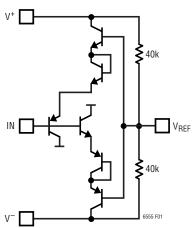

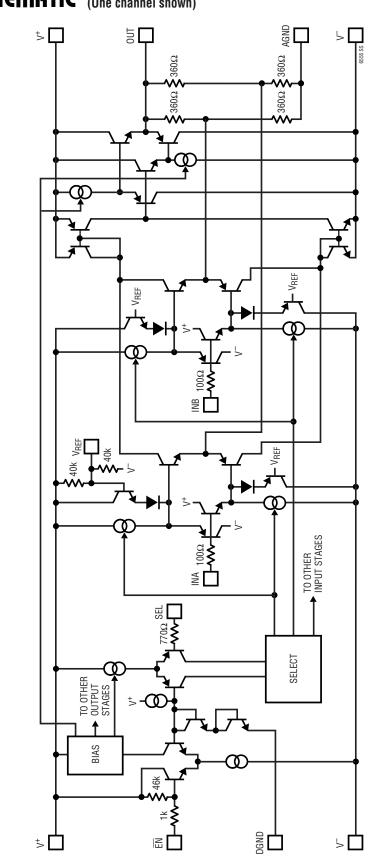

The LT6555 uses input clamps referenced to the V<sub>REF</sub> pin to prevent damage to the input stage on the unselected channel. Three transistors in series limit the input voltage to within three diode drops ( $\pm$ ) from V<sub>REF</sub>. V<sub>REF</sub> is nominally set to half of the sum of the supplies by the 40k resistors. A simplified schematic is shown in Figure 1.

To improve clamping, the pin's DC impedance should be minimized by connecting the  $V_{REF}$  pin directly to ground in the symmetric dual supply case with a common mode voltage of 0V. While loaded output swing limits the useful input voltage range in that case, if the common mode voltage is not centered at ground or the input voltage exceeds plus or minus three diodes from ground, an external resistor to either supply can be added to shift the

### **APPLICATIONS INFORMATION**

Figure 1. Simplified Schematic of V<sub>REF</sub> Pin and Input Clamping

$V_{REF}$  voltage to the desired level. The only way to cover the full common mode voltage range of V<sup>-</sup> + 1V to V<sup>+</sup> – 1V is to shift V<sub>REF</sub> up or down. Note that on a single supply, the unclamped input range limits the output low swing to 2V (1V multiplied by the internal gain of 2).

The  $V_{\text{REF}}$  pin can also be directly driven with a DC source. Bypassing the  $V_{\text{REF}}$  pin is not necessary.

The inputs can be driven beyond the point at which the output clips so long as input currents are limited to less than  $\pm 10$ mA. Continuing to drive the input beyond the output limit can result in increased current drive and slightly increased swing, but will also increase supply current and may result in delays in transient response at larger levels of overdrive.

#### Layout and Grounding

It is imperative that care is taken in PCB layout in order to benefit from the very high speed and very low crosstalk of the LT6555. Separate power and ground planes are highly recommended and trace lengths should be kept as short as possible. If input or output traces must be run over a distance of several centimeters, they should use a controlled impedance with matching series and shunt resistances (nominally 75 $\Omega$ ) to maintain signal fidelity. Series termination resistors should be placed as close to the output pins as possible to minimize output capacitance. See the Typical Performance Characteristics section for a plot of frequency response with various output capacitors—only 10pF of parasitic output capacitance before the series termination resistor causes 6dB of peaking in the frequency response!

Low ESL/ESR bypass capacitors should be placed as close to the positive and negative supply pins as possible. One 4700pF ceramic capacitor is recommended for both V<sup>+</sup> and V<sup>-</sup> supply busses. Additional 470pF ceramic capacitors with minimal trace length on each supply pin will further improve AC and transient response as well as channel isolation. For high current drive and large-signal transient applications, additional 1 $\mu$ F to 10 $\mu$ F tantalums should be added on each supply. The smallest value capacitors should be placed closest to the package.

If the AGND pins are not connected to ground, they must be carefully bypassed to maintain minimal impedance over frequency. Although crosstalk will vary depending upon board layout, a recommended starting point for bypass capacitors would be 470pF as close as possible to each AGND pin with a single 4700pF capacitor in parallel.

## **APPLICATIONS INFORMATION**

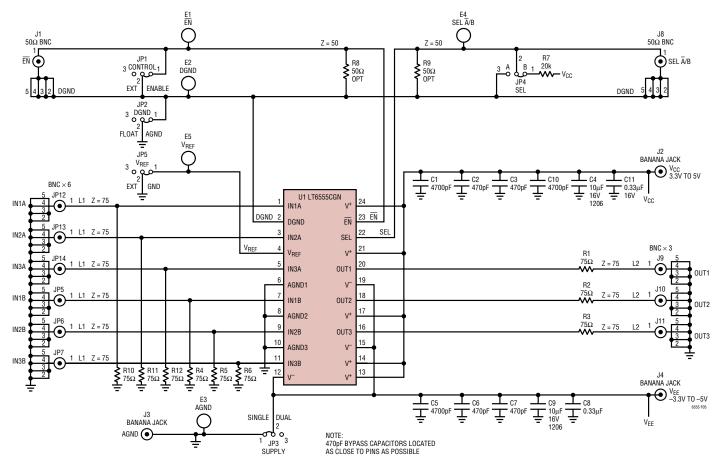

To maintain the LT6555's channel isolation, it is beneficial to shield parallel input and parallel output traces using a ground plane or power supply traces. Vias between topside and backside metal may be required to maintain a low inductance ground near the part where numerous traces converge. See Figures 6 and 7 for photos of an optimized layout.

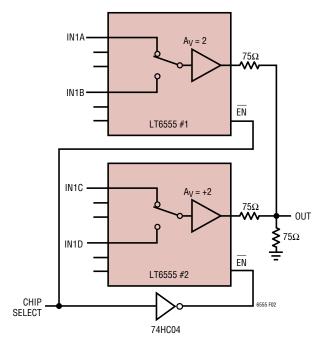

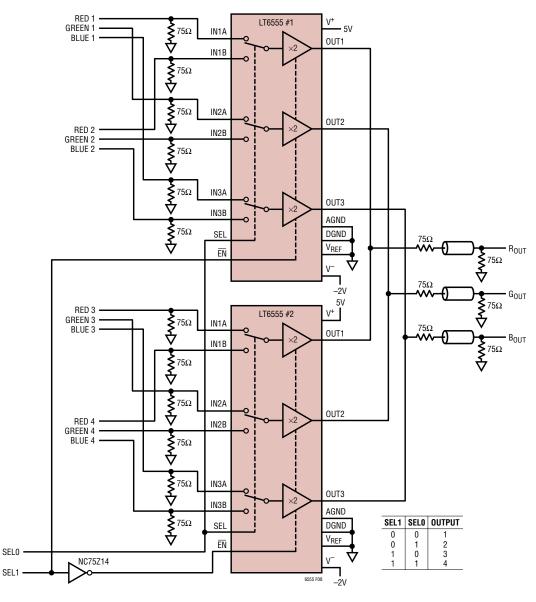

#### **Input Expansion**

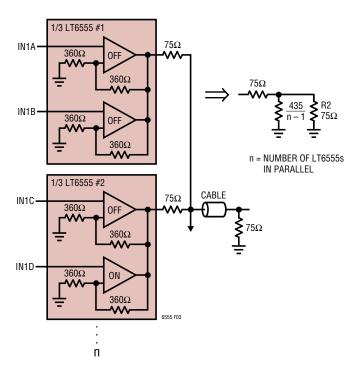

In applications with more than two inputs per channel, multiple LT6555s can be connected by several different methods. The simplest method is to connect the outputs after the 75 $\Omega$  series termination, as shown in Figure 2. The compromise of this approach is that the internal gain setting resistors cause a 435 $\Omega$  shunt across the 75 $\Omega$  cable termination, resulting in increased gain error.

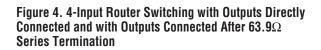

Figure 2. Two LT6555s Build a 4-Input Router

Figure 3 illustrates the loading effect of expanding the number of inputs. The resultant gain error can be calculated by the following formula using n as the number of LT6555s:

Gain Error (dB) = 6dB + 20log

$$\left(\frac{\frac{435\Omega}{n-1}}{75 + \frac{435\Omega}{n-1}} \right) dB$$

For example, two LT6555s would result in a gain error of -0.74dB per channel. Three LT6555s (i.e., six red inputs, six green inputs and six blue inputs), would have a gain error of -1.4dB.

Figure 3. Disabled Amplifiers Load the Cable Termination with 435  $\Omega$  Each

## **APPLICATIONS INFORMATION**

This systematic gain error can be significantly reduced by lowering the value of the  $75\Omega$  series termination resistors. The compromise of this approach is an increased dependence on the accuracy of the  $75\Omega$  shunt termination at the receiving end of the line. A table of values for 1% series termination resistors from n = 2 to n = 4 is shown below.

| NUMBER OF DEVICES (n) | SERIES R <sub>T</sub> |

|-----------------------|-----------------------|

| 2                     | 63.9                  |

| 3                     | 56.2                  |

| 4                     | 49.9                  |

Another approach that does not compromise gain accuracy is to connect the outputs directly together before the series termination. In this case, there will be slightly increased output glitching and supply current spiking during the EN pin switching, but the additional output loading will not increase the gain error, and the series termination resistors remain at their ideal value for AC response. See Figure 4 for a scope photo showing the result of the outputs connected both before and after the series terminations, and Figure 8 for a full schematic of a 4:1 RGB multiplexer with the output pins directly connected together. It is imperative that the output traces be as short as possible before the series termination in order to reduce capacitance and minimize AC peaking.

#### 1.5 1.5 1.0 (V) 1.0 (V $V_{S} = \pm 5V$ $V_{IN(AMP1)} = -0.5V$ $V_{IN(AMP2)} = 0.5V$ 0.5 $R_L = 150\Omega$ SERIES 63.9Ω AT EACH OUTPUT SUPPLY CURRENT (mA) OUTPUTS 150 DIRECTLY CONNECTED 100 $/Is^{-}$ اد 50 0 0 0.5 1 1.5 2 2.5 3 3.5 4 TIME (µs) 6555 E04

#### **ESD** Protection

The LT6555 has reverse-biased ESD protection diodes on all pins. If any pins are forced a diode drop above the positive supply or a diode drop below the negative supply, large currents may flow through these diodes. If the current is kept below 10mA, no damage to the devices will occur.

## TYPICAL APPLICATION

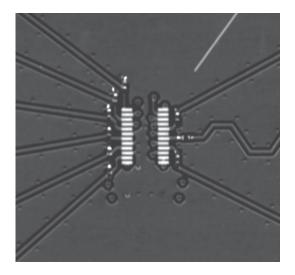

#### **RGB Multiplexer Demo Board**

The DC858A Demo Board illustrates optimal routing, bypassing and termination using the LT6555 as an RGB video multiplexer. The schematic is shown in Figure 5. All inputs and outputs are routed to have a characteristic impedance of  $75\Omega$  and  $75\Omega$  input shunt and output series terminations are connected as close to the part as

possible. The board is fabricated with four layers with internal ground and power planes. For ideal operation, a 75 $\Omega$  load termination should be connected at the output. The LT6555's gain of 2 will compensate for the resulting divider between the series and load termination resistors. Figures 6 and 7 show the topside and bottom side board layout and placement.

## TYPICAL APPLICATION

Figure 5. Demo Board Schematic

Figure 6. Demo Board Topside (IC Removed for Clarity)

**C8**

Figure 7. Demo Board Bottom Side

SIMPLIFIED SCHEMATIC (One channel shown)

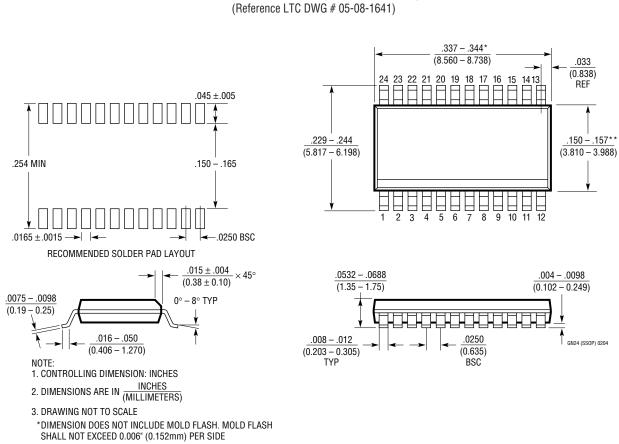

## PACKAGE DESCRIPTION

GN Package 24-Lead Plastic SSOP (Narrow .150 Inch)

\*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

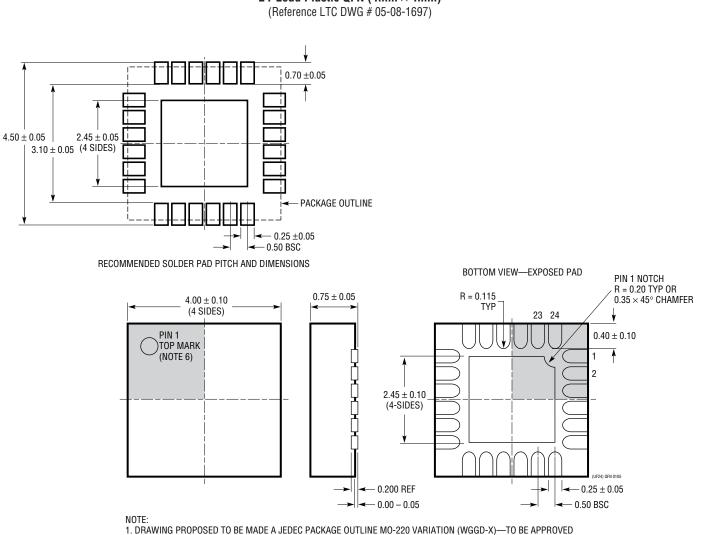

## **PACKAGE DESCRIPTION**

**UF Package** 24-Lead Plastic QFN ( $4mm \times 4mm$ )

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

- MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE, IF PRESENT 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

- ON THE TOP AND BOTTOM OF PACKAGE

## TYPICAL APPLICATION

Figure 8. 4:1 RGB Multiplexer

## **RELATED PARTS**

| PART NUMBER   | DESCRIPTION                              | COMMENTS                                                               |  |

|---------------|------------------------------------------|------------------------------------------------------------------------|--|

| LT1203        | 150MHz Single 2:1 Multiplexer            | Single SPDT Video Switch                                               |  |

| LT1399        | 300MHz Triple Current Feedback Amplifier | 0.1dB Gain Flatness to 150MHz, Shutdown                                |  |

| LT1675        | 250MHz Triple RGB Multiplexer            | 100MHz Pixel Switching, 1100V/µs Slew Rate, 16-Lead SSOP               |  |

| LT6550/LT6551 | 3.3V Triple and Quad Video Buffers       | 110MHz Gain of 2 Buffers in MS Package                                 |  |

| LT6553        | 650MHz Gain of 2 Triple Video Amplifier  | Performance Similar to the LT6555 with One Set of Inputs, 16-Lead SSOP |  |

| LT6554        | 650MHz Gain of 1 Triple Video Amplifier  | Same Pinout as the LT6553 but Optimized for High Impedance Loads       |  |

6555f