查询AD7228AUQ/883B供应商

### 捷多邦,专业PCB打样工厂,24小时 加急出货 Cotal 8-Bit D/A Converter

AD7228

### 1.1 Scope.

This specification covers the detail requirements for an octal CMOS digital-to-analog converter.

### 1.2 Part Number.

The complete part number per Table 1 of this specification is as follows:

| Device | Part Number <sup>1</sup> |

|--------|--------------------------|

| -1     | AD7228T(X)/883B          |

| -2     | AD7228U(X)/883B          |

NOTE

<sup>1</sup>To complete the part number substitute the package identifier as shown in paragraph 1.2.3.

### 1.2.3 Case Outline.

See Appendix 1 of General Specification ADI-M-1000: package outline:

#### (X) Package Description

| Q | Q-24 | 24-Pin | Cerdip, | 0.3" | Width |

|---|------|--------|---------|------|-------|

|---|------|--------|---------|------|-------|

E E-28A 28-Contact LCC

#### 1.3 Absolute Maximum Ratings. $(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| V <sub>DD</sub> to GND0.3 V to +17 V                         |

|--------------------------------------------------------------|

| $V_{DD}$ to $V_{SS}$                                         |

| Digital Input Voltage $-0.3 \text{ V}, \text{V}_{\text{DD}}$ |

| $V_{REF}$ to GND                                             |

| $V_{OUT}$ to $GND^1$                                         |

| Power Dissipation                                            |

| Up to +75°C                                                  |

| Derates above +75°C 2.0 mW/°C                                |

| Operating Temperature Range                                  |

| Thermal Resistance $(\theta_{IC})$ :                         |

| Case 1 (Q-24)                                                |

| Case 3 (E-28A) See MIL-M-38510, Appendix C                   |

| Storage Temperature                                          |

| Lead Temperature (Soldering 10 sec)+300°C                    |

| Junction Temperature + 175°C                                 |

|                                                              |

### NOTE

<sup>1</sup>Outputs may be shorted to any voltage in the range  $V_{SS}$  to  $V_{DD}$  provided that the power dissipation of the package is not exceeded. Typical short circuit for a short to  $V_{SS}$  is 50 mA.

8

# AD7228 — SPECIFICATIONS

Table 1.

| Test                                                                    | Symbol                | Device | Des<br>Min | sign<br>Max | Sub<br>Group | Test Condition <sup>1</sup>                           | Units |

|-------------------------------------------------------------------------|-----------------------|--------|------------|-------------|--------------|-------------------------------------------------------|-------|

| Total Unadjusted Error <sup>2</sup>                                     | TUE                   | -1, 2  | -2         | +2          | 1            | $V_{DD} = 15 V \pm 10\%,$                             | LSB   |

|                                                                         |                       | -1     | -2         | +2          | 2, 3         | $V_{\text{REF}} = +10 \text{ V}$                      |       |

|                                                                         |                       | -2     | -1         | +1          | 2,3          | (Single Supply Only)                                  |       |

|                                                                         |                       | -2     | -1         | +1          | 4            | 1                                                     |       |

| Total Unadjusted Error                                                  | TUE                   | -1     | -2         | +2          | 13, 14, 15   | Dual Supply Only                                      | LSB   |

|                                                                         |                       | -2     | -1         | +1          | 1            |                                                       |       |

| Relative Accuracy                                                       | RA                    | -1, 2  | -1         | +1          | 1            |                                                       | LSB   |

|                                                                         |                       | -1     | -1         | +1          | 2, 3         | 1                                                     |       |

|                                                                         |                       | -2     | -0.5       | +0.5        | 2,3          | 1                                                     |       |

|                                                                         |                       | -2     | -0.5       | +0.5        | 12           | Ī                                                     |       |

| Differential Nonlinearity                                               | DNL                   | -1, 2  | -1         | +1          | 1, 2, 3      | Guaranteed Monotonic<br>(Single Supply Only)          | LSB   |

| Differential Nonlinearity                                               | DNL                   | -1, 2  | -1         | +1          | 13, 14, 15   | Dual Supply Only                                      | LSB   |

| Full-Scale Error <sup>3</sup>                                           | A <sub>E</sub>        | -1,2   | -1         | +1          | 1            |                                                       | mV    |

|                                                                         |                       | -1     | -1         | +1          | 2, 3         | 1                                                     |       |

|                                                                         |                       | -2     | -0.5       | +0.5        | 2,3          |                                                       |       |

|                                                                         |                       | -2     | -0.5       | +0.5        | 12           |                                                       |       |

| Zero Code Error                                                         | Azce                  | -1,2   | -25        | +25         | 1            |                                                       | mV    |

|                                                                         |                       | -1     | -30        | + 30        | 2, 3         |                                                       |       |

|                                                                         |                       | -2     | -20        | +20         | 2, 3         | •                                                     |       |

|                                                                         |                       | -2     | -15        | +15         | 12           |                                                       |       |

| Load Resistance                                                         | R <sub>L</sub>        | -1, 2  | 2          |             | 1, 2, 3      | $V_{OUT} = \pm 10 V$<br>(Dual Supply & Single Supply) | kΩ    |

| Reference Input Voltage Range                                           | V <sub>REF</sub>      | -1, 2  | 2          | 10          | 1, 2, 3      |                                                       | v     |

| Reference Input Resistance                                              | R <sub>IN</sub>       | -1, 2  | 2          |             | 1, 2, 3      | Dual Supply Only                                      | kΩ    |

| Reference Input Capacitance <sup>4</sup>                                | C <sub>IN</sub> (REF) | -1,2   |            | 500         | 13, 14, 15   | Dual and Single Supply                                | pF    |

| Digital Input High Voltage                                              | V <sub>INH</sub>      | -1,2   | 2.4        |             | 1, 2, 3      | Dual Supply Only                                      | v     |

| Digital Input Low Voltage                                               | V <sub>INL</sub>      | -1, 2  |            | 0.8         | 1, 2, 3      | Input Coding Is Binary                                | v     |

| Digital Input Leakage Current                                           | I <sub>ILC</sub>      | -1, 2  | -1         | + 1         | 1, 2, 3      | · · · · · · · · · · · · · · · · · · ·                 | μΑ    |

| Digital Input Capacitance                                               | C <sub>IN</sub>       | -1, 2  |            | 8           | 13, 14, 15   |                                                       | pF    |

| Voltage Output Slew Rate                                                | SR                    | -1,2   | 2          |             | 13, 14, 15   | Dual and Single Supply                                | V/µs  |

| Voltage Output Settling Time <sup>5</sup><br>Positive Full-Scale Change | t <sub>SL</sub>       | -1, 2  |            | 5           | 13, 14, 15   | Dual and Single Supply                                | μs    |

| Negative Full-Scale Change                                              |                       | -1, 2  |            | 5<br>7      |              | Dual Supply<br>Single Supply                          |       |

| Power Supply Current                                                    | I <sub>DD</sub>       | -1, 2  |            | 16<br>22    | 1<br>2, 3    | Dual Supply Only                                      | mA    |

|                                                                         | I <sub>ss</sub>       | -1, 2  |            | 14<br>20    | 1<br>2, 3    |                                                       |       |

| Function Tests <sup>6</sup>                                             |                       | -1, 2  |            |             | 7            |                                                       |       |

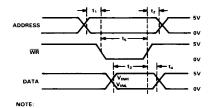

| Address to WR Setup Time                                                | t <sub>1</sub>        | -1,2   | 0          |             | 9, 10, 11    | Dual and Single Supply                                | ns    |

| Address to WR Hold Time                                                 | t <sub>2</sub>        | -1,2   | 0          |             | 9, 10, 11    | See Figure 2 and Note 7                               |       |

| Data Valid to WR Setup Time                                             | t <sub>3</sub>        | -1,2   | 70         |             | 9            |                                                       |       |

| <b>-</b>                                                                | ,                     |        | 100        |             | 10, 11       |                                                       |       |

| Data Valid to WR Hold Time                                              | t <sub>4</sub>        | -1, 2  | 10         |             | 9, 10, 11    |                                                       | ns    |

8-86 DIGITAL-TO-ANALOG CONVERTERS

### AD7228

| Test              | Symbol | Device | Design<br>Min Max | Sub<br>Group | Test Condition <sup>1</sup> | Units |

|-------------------|--------|--------|-------------------|--------------|-----------------------------|-------|

| Write Pulse Width | t5     | -1, 2  | 95                | 9            |                             | ns    |

|                   |        |        | 150               | 10, 11       |                             |       |

NOTES

$^{1}-55^{\circ}C < T_{A} < +125^{\circ}C$ , Dual Supply unless otherwise specified.  $R_{L} = 2k$ ,  $C_{L} = 100 \text{ pF}$  unless otherwise stated. Parameters in subgroups 13, 14, 15 are characterized at initial design and after any subsequent redesigns.

<sup>2</sup> Includes zero code error, relative accuracy and full-scale error.

'Calculated after zero code error has been adjusted out.

<sup>4</sup>Occurs when each DAC is loaded with all 1s.

${}^{5}V_{REF} = +10$  V; settling time to  $\pm 1/2$  LSB.

<sup>6</sup>Subgroup 7 tests are for the purpose of verifying the truth table.

<sup>7</sup>All input rise and fall times measured from 10% to 90% of +5 V,  $t_R = t_F = 5$  ns.

Timing measurement reference level is  $\frac{V_{INH} + V_{INL}}{2}$

### 1.3.1 Recommended Operating Conditions.

###

### NOTE

<sup>1</sup>V<sub>OUT</sub> must be less than V<sub>DD</sub> by 3.5 V to ensure correct operation.

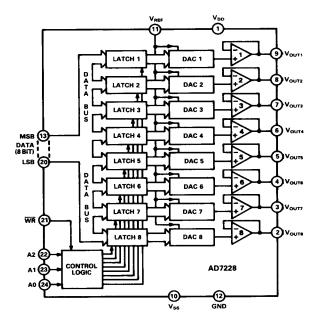

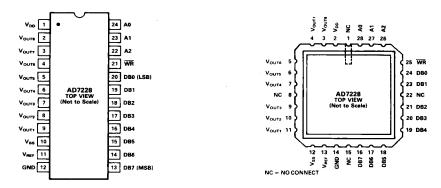

### 3.2.1 Functional Block Diagram and Terminal Assignments.

ma Pro 12

8

## AD7228

Q Package (Cerdip)

Table 2. Truth Table

| WR | A2 | A1 | A0 | Operation                        |

|----|----|----|----|----------------------------------|

| Н  | х  | X  | Х  | No Operation Device Not Selected |

| L  | L  | L  | L  | DAC 1 Transparent                |

|    | L  | L  | L  | DAC 1 Latched                    |

| L  | L  | L  | н  | DAC 2 Transparent                |

| L  | L  | н  | L  | DAC 3 Transparent                |

| L  | L  | н  | н  | DAC 4 Transparent                |

| L  | н  | L  | L  | DAC 5 Transparent                |

| L  | н  | L  | н  | DAC 6 Transparent                |

| L  | н  | н  | L  | DAC 7 Transparent                |

| L  | н  | Н  | H  | DAC 8 Transparent                |

**AD7228 Control Inputs**

H = High State L = Low State X = Don't Care

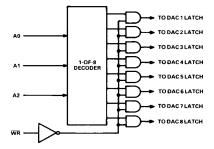

Figure 1. Input Control Logic

THE SELECTED INPUT LATCH IS TRANSPARENT WHILE WR IS LOW. THUS INVALID DATA DURING THIS TIME CAN CAUSE SPURIOUS OUTPUTS

m

### 3.2.4 Microcircuit Technology Group.

This microcircuit is covered by technology group (80).

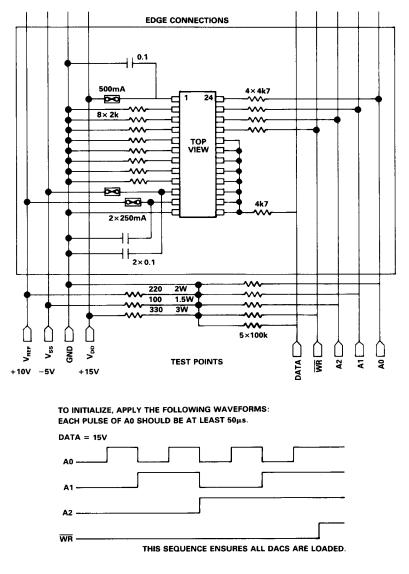

### 4.2.1 Life Test/Burn-In Circuit.

Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per MIL-STD-883 Method 1015 test condition (B).

**Burn-In Conditions**

8