# 10 MHz, 20 V/μs, G = 1, 2, 4, 8 iCMOS® Programmable Gain Instrumentation Amplifier

### **Preliminary Technical Data**

AD8251

### **FEATURES**

Small package: 10-lead MSOP Programmable gains: 1, 2, 4, 8

Digital or pin-programmable gain setting

Wide supply: ±5 V to ±15 V

Excellent dc performance

High CMRR 96 dB (min), G = 8

Low gain drift: 10 ppm/°C (max)

Low offset drift: 1.8 µV/°C (max), G = 8

**Excellent ac performance**

Fast settling time: 615 ns to 0.001% (max)

High slew rate: 20 V/μs (min)

Low distortion: -110 dB THD at 1 kHz

High CMRR over frequency: 80 dB to 50 kHz (min)

Low noise: 18 nV/ $\sqrt{\text{Hz}}$ , G = 8 (max)

Low power: 4 mA

### **APPLICATIONS**

Data acquisition

Biomedical analysis

Test and measurement

### **GENERAL DESCRIPTION**

The AD8251 is an instrumentation amplifier with digitally programmable gains that has  $G\Omega$  input impedance, low output noise, and low distortion making it suitable for interfacing with sensors and driving high sample rate analog-to-digital converters (ADCs). It has high bandwidth of 10 MHz, low THD of -110~dB and fast settling time of 615 ns to 0.001%. Offset drift and gain drift are guaranteed to 1.8  $\mu V/^{\circ}C$  and 10 ppm/°C, respectively for G=8. In addition to its wide input common voltage range, it boasts a high common-mode rejection of 80 dB at G=1 from dc to 50 kHz. The combination of precision dc performance coupled with high speed capabilities make the AD8251 an excellent candidate for data acquisition. Furthermore, this monolithic solution simplifies design and manufacturing, and boosts performance of instrumentation by maintaining a tight match of internal resistors and amplifiers.

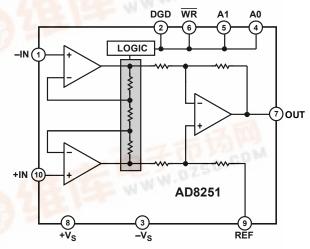

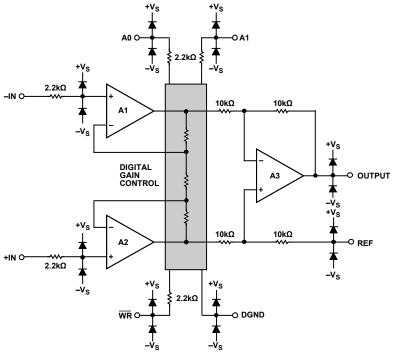

The AD8251 user interface consists of a parallel port that allows users to set the gain in one of two different ways (see Figure 1 for the functional block diagram). A 2-bit word sent via a bus can be latched using the WR input. An alternative is to use transparent gain mode where the state of logic levels at the gain port determines the gain.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Table 1. Instrumentation and Difference Amplifiers by Category

| High<br>Performance | Low<br>Cost | High<br>Voltage | Mil<br>Grade | Low<br>Power       | Digital<br>Gain     |

|---------------------|-------------|-----------------|--------------|--------------------|---------------------|

| AD82201             | AD6231      | AD628           | AD620        | AD627 <sup>1</sup> | AD8231 <sup>1</sup> |

| AD8221              | AD85531     | AD629           | AD621        |                    | AD8250              |

| AD8222              |             |                 | AD524        |                    | AD85551             |

| AD82241             |             |                 | AD526        |                    | AD8556 <sup>1</sup> |

|                     |             |                 | AD624        |                    | AD8557 <sup>1</sup> |

<sup>1</sup> Rail-to-rail output.

The AD8251 is available in a 10-lead MSOP package and is specified over the -40°C to +85°C temperature range, making it an excellent solution for applications where size and packing density are important considerations.

# AD8251

# **SPECIFICATIONS**

$+V_{S}=+15~V, -V_{S}=-15~V, V_{REF}=0~V~@~T_{A}=25^{o}C, G=1, R_{L}=2~k\Omega, unless~otherwise~noted.$

Table 2.

| Parameter                                        | Conditions                                   | Min | Тур | Max               | Unit   |

|--------------------------------------------------|----------------------------------------------|-----|-----|-------------------|--------|

| COMMON-MODE REJECTION RATIO (CMRR)               |                                              |     | -   |                   |        |

| CMRR to 60 Hz with 1 k $\Omega$ Source Imbalance | +IN = -IN = -10 V  to  +10 V                 |     |     |                   |        |

| G = 1                                            |                                              | 80  | 94  |                   | dB     |

| G = 2                                            |                                              | 86  | 104 |                   | dB     |

| G = 4                                            |                                              | 92  | 105 |                   | dB     |

| G = 8                                            |                                              | 96  | 105 |                   | dB     |

| CMRR to 50 kHz                                   | +IN = -IN = -10  V to  +10  V                |     |     |                   |        |

| G = 1                                            |                                              | 80  |     |                   | dB     |

| G = 2                                            |                                              | 86  |     |                   | dB     |

| G = 4                                            |                                              | 89  |     |                   | dB     |

| G = 8                                            |                                              | 90  |     |                   | dB     |

| NOISE                                            |                                              |     |     |                   |        |

| Voltage Noise, 1 kHz, RTI                        |                                              |     |     |                   |        |

| G = 1                                            |                                              |     |     | 40                | nV/√Hz |

| G = 2                                            |                                              |     |     | 27                | nV/√Hz |

| G = 4                                            |                                              |     |     | 22                | nV/√Hz |

| G = 8                                            |                                              |     |     | 18                | nV/√Hz |

| 0.1 Hz to 10 Hz, RTI                             |                                              |     |     |                   |        |

| G = 1                                            |                                              |     |     | 2.5               | μV p-p |

| G = 2                                            |                                              |     |     | 2.5               | μV p-p |

| G = 4                                            |                                              |     |     |                   | μV p-p |

| G = 8                                            |                                              |     |     |                   | μV p-p |

| Current Noise, 1 kHz                             |                                              |     | 5   |                   | pA/√Hz |

| Current Noise, 0.1 Hz to 10 Hz                   |                                              |     | 60  |                   | рА р-р |

| VOLTAGE OFFSET                                   |                                              |     |     |                   |        |

| Offset RTI Vos                                   | G = 1, 2, 4, 8                               |     |     | $\pm 200 + 600/G$ | μV     |

| Over Temperature                                 | $T = -40^{\circ}C \text{ to } +85^{\circ}C$  |     |     | $\pm 260 + 900/G$ | μV     |

| Average TC                                       | $T = -40^{\circ}C \text{ to } +85^{\circ}C$  |     |     | ±1.2 + 5/G        | μV/°C  |

| Offset Referred to the Input vs. Supply (PSR)    | $V_S = \pm 5 \text{ V to } \pm 15 \text{ V}$ |     |     | $\pm 6 + 20/G$    | μV/V   |

| INPUT CURRENT                                    |                                              |     |     |                   |        |

| Input Bias Current                               |                                              |     | 5   | 30                | nA     |

| Over Temperature                                 | $T = -40^{\circ}C \text{ to } +85^{\circ}C$  |     |     | 40                | nA     |

| Average TC                                       |                                              |     |     | 400               | pA/°C  |

| Input Offset Current                             |                                              |     | 5   | 30                | nA     |

| Over Temperature                                 | $T = -40^{\circ}C \text{ to } +85^{\circ}C$  |     |     | 30                | nA     |

| Average TC                                       |                                              |     |     | 160               | pA/°C  |

| DYNAMIC RESPONSE                                 |                                              |     |     |                   |        |

| Small Signal –3 dB Bandwidth                     |                                              |     |     |                   |        |

| G = 1                                            |                                              | 10  |     |                   | MHz    |

| G = 2                                            |                                              | 10  |     |                   | MHz    |

| G = 4                                            |                                              | 10  |     |                   | MHz    |

| G = 8                                            |                                              | 3   |     |                   | MHz    |

| Settling Time 0.01%                              | $\Delta OUT = 10 V step$                     |     |     |                   |        |

| G = 1                                            |                                              |     |     | 585               | ns     |

| G = 2                                            |                                              |     |     | 605               | ns     |

| G = 4                                            |                                              |     |     | 605               | ns     |

| G = 8                                            |                                              |     |     | 648               | ns     |

| Parameter                        | Conditions                                                      | Min                    | Тур            | Max                   | Unit    |

|----------------------------------|-----------------------------------------------------------------|------------------------|----------------|-----------------------|---------|

| Settling Time 0.001%             | ΔOUT = 10 V step                                                |                        |                |                       |         |

| G = 1                            | ·                                                               |                        |                | 615                   | ns      |

| G = 2                            |                                                                 |                        |                | 635                   | ns      |

| G = 4                            |                                                                 |                        |                | 635                   | ns      |

| G = 8                            |                                                                 |                        |                | 685                   | ns      |

| Slew Rate                        |                                                                 |                        |                |                       |         |

| G = 1                            |                                                                 | 20                     |                |                       | V/µs    |

| G = 2                            |                                                                 | 25                     |                |                       | V/μs    |

| G = 4                            |                                                                 | 25                     |                |                       | V/μs    |

| G = 8                            |                                                                 | 25                     |                |                       | V/μs    |

| Total Harmonic Distortion        | $f = 1 \text{ kHz}, R_L = 10 \text{ k}\Omega, G = 1$            |                        | -110           |                       | dB      |

| GAIN                             | ,                                                               |                        |                |                       |         |

| Gain Range                       | G = 1, 2, 4, 8                                                  | 1                      |                | 8                     | V/V     |

| Gain Error                       | OUT = ±10 V                                                     |                        |                |                       | 1, 1    |

| G = 1                            |                                                                 |                        |                | 0.03                  | %       |

| G = 2, 4, 8                      |                                                                 |                        |                | 0.04                  | %       |

| Gain Nonlinearity                | OUT = -10  V to  +10  V                                         |                        |                | 0.01                  | / "     |

| G = 1                            | $R_L = 10 \text{ k}\Omega$ , $2 \text{ k}\Omega$ , $600 \Omega$ |                        |                | 6                     | ppm     |

| G = 2                            | $R_L = 10 \text{ k}\Omega$ , $2 \text{ k}\Omega$ , $600 \Omega$ |                        |                | 8                     | ppm     |

| G = 4                            | $R_L = 10 \text{ k}\Omega$ , $2 \text{ k}\Omega$ , $600 \Omega$ |                        |                | 8                     | ppm     |

| G = 8                            | $R_L = 10 \text{ k}\Omega$ , $2 \text{ k}\Omega$ , $600 \Omega$ |                        |                | 10                    | ppm     |

| Gain vs. Temperature             | All gains                                                       |                        |                | 10                    | ppm/°C  |

| INPUT                            | 7th gams                                                        |                        |                | 10                    | ррии/ С |

| Input Impedance                  |                                                                 |                        |                |                       |         |

| Differential                     |                                                                 | 1                      |                |                       | GΩ∥pF   |

| Common Mode                      |                                                                 | 1                      |                |                       |         |

|                                  | V 15V4-115V                                                     |                        |                |                       | GΩ∥pF   |

| Input Operating Voltage Range    | $V_S = \pm 5 \text{ V to } \pm 15 \text{ V}$                    | $-V_{s} + 1.0$         |                | +V <sub>s</sub> – 1.1 | V       |

| Over Temperature                 | $T = -40^{\circ}C \text{ to } +85^{\circ}C$                     | -V <sub>S</sub> + 1.1  |                | +V <sub>s</sub> – 1.4 | V       |

| OUTPUT                           |                                                                 | 42.5                   |                | 40.5                  | 1,,     |

| Output Swing                     |                                                                 | -13.5                  |                | +13.5                 | V       |

| Over Temperature                 | $T = -40^{\circ}C \text{ to } +85^{\circ}C$                     | -13.5                  |                | +13.5                 | V       |

| Short-Circuit Current            |                                                                 |                        | 37             |                       | mA      |

| REFERENCE INPUT                  |                                                                 |                        |                |                       |         |

| R <sub>IN</sub>                  |                                                                 |                        | 20             |                       | kΩ      |

| I <sub>IN</sub>                  | +IN, -IN, REF = 0                                               |                        |                | 1                     | μΑ      |

| Voltage Range                    |                                                                 | -V <sub>S</sub>        |                | $+V_S$                | V       |

| Gain to Output                   |                                                                 |                        | $1 \pm 0.0001$ |                       | V/V     |

| DIGITAL LOGIC                    |                                                                 |                        |                |                       |         |

| Digital Ground Voltage, DGND     | Referred to GND                                                 | -V <sub>s</sub> + 4.25 | 0              | $+V_{S}-2.7$          | V       |

| Digital Input Voltage Low        | Referred to GND                                                 | DGND                   |                | 2.1                   | V       |

| Digital Input Voltage High       | Referred to GND                                                 | 2.8                    |                | +V <sub>S</sub>       | v       |

| Digital Input Current            |                                                                 |                        | 1              | 3                     | μA      |

| Gain Switching Time <sup>1</sup> |                                                                 |                        | •              | 325                   | ns      |

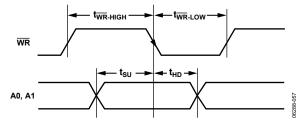

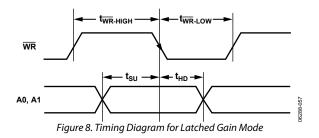

| t <sub>su</sub>                  | See Figure 2 timing diagram                                     | 20                     |                | 323                   | ns      |

| t <sub>HD</sub>                  | See Figure 2 timing diagram                                     | 10                     |                |                       | ns      |

| t WR-LOW                         |                                                                 | 20                     |                |                       | ns      |

|                                  |                                                                 |                        |                |                       |         |

| t WR-HIGH                        |                                                                 | 40                     |                |                       | ns      |

| Parameter                          | Conditions                                  | Min | Тур | Max | Unit |

|------------------------------------|---------------------------------------------|-----|-----|-----|------|

| POWER SUPPLY                       |                                             |     |     |     |      |

| Operating Range                    |                                             | ±5  |     | ±15 | V    |

| Quiescent Current, +I <sub>s</sub> |                                             |     | 4.1 | 4.5 | mA   |

| Quescent Current, -Is              |                                             |     | 3.7 | 4.5 | mA   |

| Over Temperature                   | $T = -40^{\circ}C \text{ to } +85^{\circ}C$ |     |     | 4.5 | mA   |

| TEMPERATURE RANGE                  |                                             |     |     |     |      |

| Specified Performance              |                                             | -40 |     | +85 | °C   |

$<sup>^{\</sup>rm 1}$  Add time for the output to slew and settle to calculate the total time for a gain change.

### **TIMING DIAGRAM**

Figure 2. Timing Diagram for Latched Gain Mode (See the Timing for Latched Gain Mode Section)

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

|                   | Parameter                                    | Rating                  |

|-------------------|----------------------------------------------|-------------------------|

|                   | Supply Voltage                               | ±17 V                   |

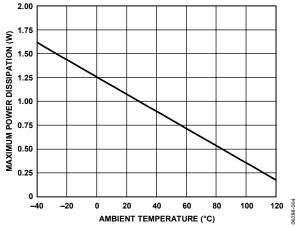

| Power Dissipation |                                              | See Figure 3            |

|                   | Output Short-Circuit Current                 | Indefinite <sup>1</sup> |

|                   | Common-Mode Input Voltage                    | ±V <sub>S</sub>         |

|                   | Differential Input Voltage                   | ±V <sub>S</sub>         |

|                   | Digital Logic Inputs                         | ±V <sub>S</sub>         |

|                   | Storage Temperature Range                    | −65°C to +125°C         |

|                   | Operating Temperature Range <sup>2</sup>     | -40°C to +85°C          |

|                   | Lead Temperature (Soldering 10 sec)          | 300°C                   |

|                   | Junction Temperature                         | 140°C                   |

|                   | $\theta_{JA}$ (4-Layer JEDEC Standard Board) | 112°C/W                 |

|                   | Package Glass Transition Temperature         | 140°C                   |

|                   |                                              |                         |

<sup>&</sup>lt;sup>1</sup> Assumes the load is referenced to mid supply.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **MAXIMUM POWER DISSIPATION**

The maximum safe power dissipation in the AD8251 package is limited by the associated rise in junction temperature ( $T_J$ ) on the die. The plastic encapsulating the die locally reaches the junction temperature. At approximately 140°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, permanently shifting the parametric performance of the AD8251. Exceeding a junction temperature of 140°C for an extended period can result in changes in silicon devices, potentially causing failure.

The still-air thermal properties of the package and PCB ( $\theta_{JA}$ ), the ambient temperature ( $T_A$ ), and the total power dissipated in the package ( $P_D$ ) determine the junction temperature of the die. The junction temperature is calculated as

$$T_J = T_A + \left(P_D \times \theta_{JA}\right)$$

The power dissipated in the package  $(P_D)$  is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive for all outputs. The quiescent

power is the voltage between the supply pins  $(V_s)$  times the quiescent current  $(I_s)$ . Assuming the load  $(R_L)$  is referenced to midsupply, the total drive power is  $V_s/2 \times I_{OUT}$ , some of which is dissipated in the package and some in the load  $(V_{OUT} \times I_{OUT})$ .

The difference between the total drive power and the load power is the drive power dissipated in the package.

$P_D = Quiescent Power + (Total Drive Power - Load Power)$

$$P_D = \left(V_S \times I_S\right) + \left(\frac{V_S}{2} \times \frac{V_{OUT}}{R_L}\right) - \frac{{V_{OUT}}^2}{R_L}$$

In single-supply operation with  $R_L$  referenced to  $-V_S$ , worst case is  $V_{\rm OUT} = V_S/2$ .

Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ . In addition, more metal directly in contact with the package leads from metal traces, through holes, ground, and power planes reduces the  $\theta_{JA}$ .

Figure 3 shows the maximum safe power dissipation in the package vs. the ambient temperature on a 4-layer JEDEC standard board.

Figure 3. Maximum Power Dissipation vs. Ambient Temperature

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Temperature for specified performance is -40°C to +85°C..

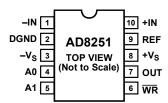

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. 10-Lead MSOP (RM-10), Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Name            | Description                                           |  |

|---------|-----------------|-------------------------------------------------------|--|

| 1       | -IN             | Inverting Input Terminal. True differential input.    |  |

| 2       | DGND            | Digital Ground.                                       |  |

| 3       | -V <sub>S</sub> | Negative Supply Terminal.                             |  |

| 4       | A0              | Gain Setting Pin (LSB).                               |  |

| 5       | A1              | Gain Setting Pin (MSB).                               |  |

| 6       | WR              | Write Enable.                                         |  |

| 7       | OUT             | Output Terminal.                                      |  |

| 8       | +V <sub>S</sub> | Positive Supply Terminal.                             |  |

| 9       | REF             | Reference Voltage Terminal.                           |  |

| 10      | +IN             | Noninverting Input Terminal. True differential input. |  |

### THEORY OF OPERATION

Figure 5. Simplified Schematic

The AD8251 is a monolithic instrumentation amplifier based on the classic, three-op amp topology as shown in Figure 5. It is fabricated on the Analog Devices, Inc. proprietary *i*CMOS process that provides precision, linear performance and a robust digital interface. A parallel interface allows users to digitally program gains of 1, 2, 4, and 8. Gain control is achieved by switching resistors in an internal, precision, resistor array (as shown in Figure 5). Although the AD8251 has a voltage feedback topology, gain bandwidth product increases for gains of 1, 2, and 4 because each gain has its own frequency compensation. This results in maximum bandwidth at higher gains.

All internal amplifiers employ distortion cancellation circuitry and achieve high linearity and ultralow THD. Laser trimmed resistors allow for a maximum gain error of less than 0.03% for G=1, and minimum CMRR of 96 dB for G=8. A pinout optimized for high CMRR over frequency enables the AD8251 to offer a guaranteed minimum CMRR over frequency of 80 dB at 50 kHz (G=1). The balanced input reduces the parasitics that, in the past, had adversely affected CMRR performance.

#### **GAIN SELECTION**

This section shows users how to configure the AD8251 for basic operation. Logic low and Logic high voltage limits are listed in the Specifications section. Typically, Logic low is 0 V and Logic high is 5 V; both voltages are measured with respect to DGND. Refer to the specifications table (see Table 2) for the permissible voltage range of DGND. The gain of the AD8251 can be set using two methods.

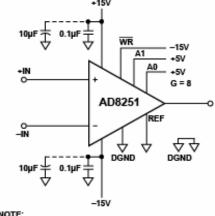

#### **Transparent Gain Mode**

The easiest way to set the gain is to program it directly via a Logic high or Logic low voltage applied to A0 and A1. Figure 6 shows an example of this gain setting method, referred to throughout the data sheet as transparent gain mode. Tie  $\overline{WR}$  to the negative supply to engage transparent gain mode. In this mode, any change in voltage applied to A0 and A1 from Logic low to Logic high, or vice versa, immediately results in a gain change. Table 5 is the truth table for transparent gain mode and Figure 6 shows the AD8251 configured in transparent gain mode.

NOTE:

1. IN TRANSPARENT GAIN MODE, WR IS TIED TO -V<sub>8</sub>.

THE VOLTAGE LEVELS ON A0 AND A1 DETERMINE

THE GAIN. IN THIS EXAMPLE, BOTH A0 AND A1 ARE

SET TO LOGIC HIGH, RESULTING IN A GAIN OF 8.

Figure 6. Transparent Gain Mode, A0 and A1 = High, G = 8

Table 5. Truth Table Logic Levels for Transparent Gain Mode

| WR              | A1   | A0   | Gain |

|-----------------|------|------|------|

| -V <sub>S</sub> | Low  | Low  | 1    |

| $-V_S$          | Low  | High | 2    |

| $-V_S$          | High | Low  | 4    |

| -Vs             | High | High | 8    |

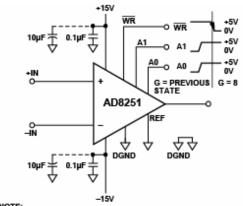

#### LATCHED GAIN MODE

Some applications have multiple programmable devices such as multiplexers or other programmable gain instrumentation amplifiers on the same PCB. In such cases, devices can share a data bus. The gain of the AD8251 can be set using  $\overline{WR}$  as a latch, allowing other devices to share A0 and A1. Figure 7 shows a schematic using this method, known as latched gain mode. The AD8251 is in this mode when  $\overline{WR}$  is held at Logic high or Logic low, typically 5 V and 0 V, respectively. The voltages on A0 and A1 are read on the downward edge of the  $\overline{WR}$  signal as it transitions from Logic high to Logic low. This latches in the logic levels on A0 and A1, resulting in a gain change. See the truth table listing in Table 6 for more on these gain changes.

NOTE.

1. ON THE DOWNWARD EDGE OF WR, AS IT TRANSITIONS

FROM LOGIC HIGH TO LOGIC LOW, THE VOLTAGES ON AO

AND A1 ARE READ AND LATCHED IN, RESULTING IN A

GAIN CHANGE. IN THIS EXAMPLE, THE GAIN SWITCHES TO G = 8.

Figure 7. Latched Gain Mode, G = 8

Table 6. Truth Table Logic Levels for Latched Gain Mode

| WR           | A1                    | A0             | Gain        |

|--------------|-----------------------|----------------|-------------|

| High to Low  | Low                   | Low            | Change to 1 |

| High to Low  | Low                   | High           | Change to 2 |

| High to Low  | High                  | Low            | Change to 4 |

| High to Low  | High                  | High           | Change to 8 |

| Low to Low   | X <sup>1</sup>        | X <sup>1</sup> | No Change   |

| Low to High  | <b>X</b> <sup>1</sup> | X <sup>1</sup> | No Change   |

| High to High | X <sup>1</sup>        | X <sup>1</sup> | No Change   |

$<sup>^{1}</sup>$  X = don't care.

Upon power up, the AD8251 defaults to a gain of 1 when in latched gain mode. In contrast, if the AD8251 is configured in transparent gain mode, it starts at the gain indicated by the voltage levels on A0 and A1 upon power-up.

### Timing for Latched Gain Mode

In latched gain mode, logic levels at A0 and A1 have to be held for a minimum setup time,  $t_{\text{SU}}$ , before the downward edge of  $\overline{WR}$  latches in the gain. Similarly, they must be held for a minimum hold time of  $t_{\text{HD}}$  after the downward edge of  $\overline{WR}$  to ensure that the gain is latched in correctly. After  $t_{\text{HD}}$ , A0 and A1 may change logic levels but the gain does not change (until the next downward edge of  $\overline{WR}$ ). The minimum duration that  $\overline{WR}$  can be held high is t  $\overline{w_{R-HIGH}}$ , and t  $\overline{w_{R-LOW}}$  is the minimum duration that  $\overline{WR}$  can be held low. Digital timing specifications are listed in Table 2. The time required for a gain change is dominated by the settling time of the amplifier. A timing diagram is shown in Figure 8.

When sharing a data bus with other devices, logic levels applied to those devices can potentially feed through to the output of the AD8251. Feedthrough can be minimized by decreasing the edge rate of the logic signals. Furthermore, careful layout of the PCB also reduces coupling between the digital and analog portions of the board.

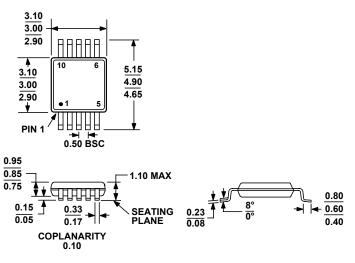

### **OUTLINE DIMENSIONS**

### **COMPLIANT TO JEDEC STANDARDS MO-187-BA**

Figure 9. 10-Lead Mini Small Outline Package [MSOP] (RM-10) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                      | Temperature Range | Package Description | Package Option | Branding |

|----------------------------|-------------------|---------------------|----------------|----------|

| AD8251ARMZ <sup>1</sup>    | -40°C to +85°C    | 10-Lead MSOP        | RM-10          | H0T      |

| AD8251ARMZ-RL <sup>1</sup> | -40°C to +85°C    | 10-Lead MSOP        | RM-10          | H0T      |

| AD8251ARMZ-R7 <sup>1</sup> | -40°C to +85°C    | 10-Lead MSOP        | RM-10          | H0T      |

| AD8251-EVALZ <sup>1</sup>  |                   | Evaluation Board    |                |          |

<sup>&</sup>lt;sup>1</sup> Z = Pb-free part.

AD8251

**Preliminary Technical Data**

NOTES

**Preliminary Technical Data**

AD8251

# **NOTES**

ma Pen