### 查询THS4141供应商

# 捷多邦,专业PCB打样工厂,24小町**时多414**0,THS4141 HIGH-SPEED FULLY DIFFERENTIAL I/O AMPLIFIERS

Simple Single-Ended To Differential

**Differential Transmitter And Receiver**

<sup>V</sup>осм 🗖

VCC+

VOUT\_VOUT+

HIGH-SPEED DIFFERENTIAL I/O FAMILY

CHANNELS

1

1

key applications

Conversion

THS4140 D OR DGN PACKAGE

(TOP VIEW)

2

3

7

6

DEVICE

THS4140

THS4141

Differential ADC Driver

**Differential Antialiasing**

VINI

PD

**Output Level Shifter**

SLOS320A - MAY 2000 - REVISED AUGUST 2000

THS4141 D OR DGN PACKAGE

(TOP VIEW)

3

SHUTDOWN

Х

\_

8

6

$\square V_{IN+}$

Vcc-

VOUT-

#### features

- High Performance

- 160 MHz 3 dB Bandwidth ( $V_{CC} = \pm 15 V$ )

- 450 V/μs Slew Rate

- - 79 dB HD3 at 1 MHz

- 6.5 nV/\/Hz Input-Referred Noise

- Differential Input/Differential Output

- Balanced Outputs Reject Common-Mode Noise

- Differential Reduced Second Harmonic Distortion

- Wide Power Supply Range – V<sub>CC</sub> = 5 V Single Supply to ±15 V

- Low-Power Shutdown Option  $-I_{CC} = 880 \,\mu A$  in Shutdown Mode

- (THS4140)

### description

The THS414x is one in a family of fully differential input/differential output devices fabricated using Texas Instruments' state-of-the-art BiCom I complementary bipolar process.

The THS414x consists of a true fully differential signal path from input to output. This results in excellent common-mode noise rejection and improved total harmonic distortion. Not only does the device provide balanced, differential outputs, but internal feedback reduces the effects of parametric differences in gain-setting components between sides.

VIN-

<sup>V</sup>осм Ц

V<sub>CC+</sub> L

V<sub>OUT+</sub> l

|                                      |                      | TOTAL HARMONIC DISTORTION                                                              |

|--------------------------------------|----------------------|----------------------------------------------------------------------------------------|

| RELATED DEVICES                      |                      | FREQUENCY                                                                              |

| DEVICE DESCRIPTION                   | -30                  |                                                                                        |

| THS412x RRO, 3.3 V CMOS              | <del>д</del><br>В    |                                                                                        |

| THS413x 150 MHz, 51 V/μs, 1.3 nV/√Hz | I –40                |                                                                                        |

| THS415x 180 MHz, 850 V/μs, 9 nV/√Hz  | Distortion           |                                                                                        |

| typical A/D application circuit      | -100<br>-00-<br>100k | V <sub>CC</sub> = 5 V to ± 15 V           M           10M           f - Frequency - Hz |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLOS320A - MAY 2000 - REVISED AUGUST 2000

| AVAILABLE OPTIONS |                        |                            |            |              |  |  |  |  |  |

|-------------------|------------------------|----------------------------|------------|--------------|--|--|--|--|--|

|                   | PACKAGE                | D DEVICES                  | MSOP       | EVALUATION   |  |  |  |  |  |

| TA                | SMALL OUTLINE<br>(D)   | MSOP PowerPAD™<br>(DGN)    | CODES      | MODULES      |  |  |  |  |  |

| 0°C to 70°C       | THS4140CD<br>THS4141CD | THS4140CDGN<br>THS4141CDGN | AOF<br>AOH | THS4140/1EVM |  |  |  |  |  |

| -40°C to 85°C     | THS4140ID<br>THS4141ID | THS4140IDGN<br>THS4141IDGN | AOG<br>AOK |              |  |  |  |  |  |

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub> to V <sub>CC+</sub>          | ±16.5 V       |

|--------------------------------------------------------------|---------------|

| Input voltage, V <sub>1</sub>                                |               |

| Output current, I <sub>O</sub>                               |               |

| Differential input voltage, V <sub>ID</sub>                  |               |

| Continuous total power dissipation                           |               |

| Operating free-air temperature, T <sub>A</sub> :C suffix     | 0°C to 70°C   |

| l suffix                                                     | –40°C to 85°C |

| Storage temperature, T <sub>stg</sub>                        |               |

| Lead temperature 1,6 mm (1/16 Inch) from case for 10 seconds | 300°C         |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### DISSIPATION RATING TABLE

| PACKAGE | θJA<br>(°C/W) | θJC<br>(°C/W) | T <sub>A</sub> = 25°C<br>POWER RATING |

|---------|---------------|---------------|---------------------------------------|

| D       | 167‡          | 38.3          | 740 mW                                |

| DGN§    | 58.4          | 4.7           | 2.14 W                                |

| DGN§    |               | 4.7           | 2.14 W                                |

<sup>‡</sup> This data was taken using the JEDEC standard Low-K test PCB. For the JEDEC Proposed High-K test PCB, the  $\theta_{JA}$  is 95°C/W with a power rating at  $T_A = 25$ °C of 1.32 W.

$\$  This data was taken using 2 oz. trace and copper pad that is soldered directly to a 3 in.  $\times$  3 in. PC.

### recommended operating conditions

|                                                        |               | MIN  | TYP M | IAX | UNIT |

|--------------------------------------------------------|---------------|------|-------|-----|------|

| Supply voltage, V <sub>CC</sub> + to V <sub>CC</sub> - | Dual supply   | ±2.5 |       | ±15 | V    |

|                                                        | Single supply | 5    |       | 30  | v    |

| Operating free-air temperature, T <sub>A</sub>         | C suffix      | 0    |       | 70  | °C   |

|                                                        | l suffix      | -40  |       | 85  | C    |

SLOS320A - MAY 2000 - REVISED AUGUST 2000

# electrical characteristics, V<sub>CC</sub> = $\pm$ 5 V, R<sub>L</sub> = 800 $\Omega$ , T<sub>A</sub> = 25°C (unless otherwise noted)<sup>†</sup>

#### dynamic performance

|                                   | PARAMETER                                              | TEST CONDITIONS                |                                |     | TYP | MAX | UNIT |

|-----------------------------------|--------------------------------------------------------|--------------------------------|--------------------------------|-----|-----|-----|------|

| BW Small signal bandwidth (–3 dB) | Small signal bandwidth ( $2 dD$ ) V <sub>CC</sub> = ±5 |                                | Gain = 1, $R_f$ = 390 $\Omega$ |     | 150 |     | MHz  |

|                                   | $V_{CC} = \pm 15$                                      | Gain = 1, $R_f$ = 390 $\Omega$ |                                | 160 |     | MHz |      |

| SR                                | Slew rate (see Notes 1)                                | Gain = 1                       |                                |     | 450 |     | V/µs |

|                                   | Settling time to 0.1%                                  | Differential step              | Coin 1                         |     | 96  |     |      |

| ts                                | Settling time to 0.01%                                 | voltage = 2 V <sub>PP</sub> ,  | Gain = 1                       |     | 304 |     | ns   |

NOTE 1: Slew rate is measured from an output level range of 25% to 75%.

<sup>†</sup> The full range temperature is 0°C to 70°C for the C suffix, and –40°C to 85°C for the I suffix.

#### distortion performance

|         | PARAMETER                                                   | TES                                      | T CONDITIONS       | MIN TYP MAX | UNIT  |

|---------|-------------------------------------------------------------|------------------------------------------|--------------------|-------------|-------|

| Saaaaa  | harmonic distortion, differential in/differential out       | 1 MHz V <sub>O</sub> = 2 V <sub>PP</sub> |                    | -85         | dB    |

| Second  |                                                             | 8 MHz                                    | $V_{O} = 2 V_{PP}$ | -65         | uв    |

| Third h | ormonia distortion differential in/differential out         | 1 MHz                                    | $V_{O} = 2 V_{PP}$ | -79         | dB    |

| minana  | Third harmonic distortion, differential in/differential out | 8 MHz                                    | $V_{O} = 2 V_{PP}$ | -55.5       | UD UD |

|         | Total harmonic distortion                                   | $V_{CC} = 5$                             | f= 1 MHz           | -78         |       |

| THD     | Differential input differential output                      | $V_{CC} = \pm 5$                         | f = 1 MHz          | -78         | dB    |

|         | $V_{O} = 2 V_{PP}$                                          | $V_{CC} = \pm 15$                        | f = 1 MHz          | -79         | 1     |

| Spuriou | us free dynamic range (SFDR)                                |                                          |                    | -79         | dB    |

| Intermo | odulation distortion                                        | 5 MHz                                    |                    | -103        | dBc   |

| Third-o | rder intercept                                              | 20 MHz                                   |                    | 37          | dB    |

<sup>†</sup> The full range temperature is  $0^{\circ}$ C to  $70^{\circ}$ C for the C suffix, and  $-40^{\circ}$ C to  $85^{\circ}$ C for the I suffix.

#### noise performance

|                | PARAMETER           | TEST CONDITIONS MIN TYP MAX |  |      | MAX | UNIT   |

|----------------|---------------------|-----------------------------|--|------|-----|--------|

| Vn             | Input voltage noise | f = 10 kHz                  |  | 6.5  |     | nV/√Hz |

| ۱ <sub>n</sub> | Input current noise | f = 10 kHz                  |  | 1.25 |     | pA/√Hz |

<sup>†</sup> The full range temperature is  $0^{\circ}$ C to  $70^{\circ}$ C for the C suffix, and  $-40^{\circ}$ C to  $85^{\circ}$ C for the I suffix.

#### dc performance

|                 | PARAMETER                          | TEST CONDITIONS             | MIN | TYP | MAX | UNIT  |

|-----------------|------------------------------------|-----------------------------|-----|-----|-----|-------|

| Open loop gain  |                                    | $T_A = 25^{\circ}C$         | 63  | 67  |     | dB    |

|                 |                                    | T <sub>A</sub> = full range | 60  |     |     | uБ    |

|                 | Input offset voltage, differential | $T_A = 25^{\circ}C$         |     | 1   | 7   |       |

|                 |                                    | T <sub>A</sub> = full range |     |     | 8.5 | mV    |

| Vos             |                                    | $T_A = 25^{\circ}C$         |     | 0.5 | 8   |       |

|                 | Offset drift                       | T <sub>A</sub> = full range |     | 7   |     | μV/°C |

| I <sub>IB</sub> | Input bias current                 |                             |     | 5.1 | 15  | μΑ    |

| los             | Input offset current               | T <sub>A</sub> = full range |     | 0.1 | 1   | μΑ    |

| Offset of       | lrift                              |                             |     | 0.3 |     | nA/°C |

<sup>†</sup> The full range temperature is 0°C to 70°C for the C suffix, and –40°C to 85°C for the I suffix.

SLOS320A - MAY 2000 - REVISED AUGUST 2000

# electrical characteristics, V<sub>CC</sub> = $\pm$ 5 V, R<sub>L</sub> = 800 $\Omega$ , T<sub>A</sub> = 25°C (unless otherwise noted) (continued)<sup>†</sup>

#### input characteristics

|                | PARAMETER                     | TEST CONDITIONS                   | MIN TYP MAX |      |  | UNIT |

|----------------|-------------------------------|-----------------------------------|-------------|------|--|------|

| CMRR           | Common-mode rejection ratio   | T <sub>A</sub> = full range       | 75          | 84   |  | dB   |

| RI             | Input resistance, closed loop | Measured into each input terminal |             | 14.4 |  | MΩ   |

| Cl             | Input capacitance             |                                   |             | 3.9  |  | pF   |

| r <sub>o</sub> | Output resistance             | Open loop                         |             | 43   |  | Ω    |

<sup>†</sup> The full range temperature is 0°C to 70°C for the C suffix, and –40°C to 85°C for the I suffix.

#### output characteristics

| PARAMETER                                                            | TEST C                  | ONDITIONS                   | MIN        | ТҮР        | MAX | UNIT |

|----------------------------------------------------------------------|-------------------------|-----------------------------|------------|------------|-----|------|

| Output voltage swing I <sub>O</sub> Output current, $R_L = 7 \Omega$ | V <sub>CC</sub> = 5 V   | $T_A = 25^{\circ}C$         | 1.2 to 3.8 | 0.9 to 4.1 |     |      |

|                                                                      | vCC = 2 v               | T <sub>A</sub> = full range | 1.3 to 3.7 |            |     |      |

|                                                                      | V <sub>CC</sub> = ±5 V  | $T_A = 25^{\circ}C$         | 3.7        | 3.9        |     | V    |

|                                                                      | vCC = ±2 v              | T <sub>A</sub> = full range | 3.6        |            |     | v    |

|                                                                      | V <sub>CC</sub> = ±15 V | $T_A = 25^{\circ}C$         | 12         | 12.9       |     |      |

|                                                                      | $\int CC = \pm 12 V$    | T <sub>A</sub> = full range | 11         |            |     |      |

|                                                                      | V <sub>CC</sub> = 5 V   | $T_A = 25^{\circ}C$         | 35         | 45         |     |      |

|                                                                      |                         | T <sub>A</sub> = full range | 25         |            |     |      |

| $P_{\rm e} = -70$                                                    |                         | $T_A = 25^{\circ}C$         | 45         | 60         |     | mA   |

|                                                                      | V <sub>CC</sub> = ±5 V  | T <sub>A</sub> = full range | 35         |            |     | mA   |

|                                                                      |                         | $T_A = 25^{\circ}C$         | 65         | 85         |     |      |

|                                                                      | V <sub>CC</sub> = ±15 V | T <sub>A</sub> = full range | 50         |            |     |      |

<sup>†</sup> The full range temperature is 0°C to 70°C for the C suffix, and –40°C to 85°C for the I suffix.

#### power supply

|                                      | PARAMETER                                      | TEST                    | TEST CONDITIONS             |      | TYP   | MAX | UNIT |

|--------------------------------------|------------------------------------------------|-------------------------|-----------------------------|------|-------|-----|------|

| V <sub>CC</sub> Supply voltage range | Single supply                                  |                         | 4                           |      | 33    | v   |      |

|                                      | Split supply                                   |                         | ±2                          |      | ±16.5 | v   |      |

| ICC Quiescent current                |                                                | $T_A = 25^{\circ}C$     |                             | 13.2 | 16    |     |      |

|                                      | Quiescent current                              | $V_{CC} = \pm 5 V$      | $T_A = full range$          |      |       | 18  | mA   |

|                                      |                                                | V <sub>CC</sub> = ±15 V | $T_A = 25^{\circ}C$         |      | 15    |     |      |

|                                      | Quiescent current (shutdown) (THS4140)         | $T_A = 25^{\circ}C$     |                             |      | 0.88  | 1.2 | mA   |

|                                      | ICC(SD) Quiescent current (shutdown) (THS4140) | $T_A = $ full range     | T <sub>A</sub> = full range |      |       | 1.4 | mA   |

|                                      | PSRR Power supply rejection ratio              | T <sub>A</sub> = 25°C   |                             | 70   | 90    |     |      |

| PSRR                                 |                                                | $T_A = $ full range     | T <sub>A</sub> = full range |      |       |     | dB   |

<sup>†</sup> The full range temperature is  $0^{\circ}$ C to  $70^{\circ}$ C for the C suffix, and  $-40^{\circ}$ C to  $85^{\circ}$ C for the I suffix.

SLOS320A - MAY 2000 - REVISED AUGUST 2000

# **TYPICAL CHARACTERISTICS**

# Table of Graphs

|                |                              |                                    | FIGURE |

|----------------|------------------------------|------------------------------------|--------|

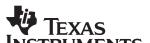

| PSRR           | Power supply rejection ratio | vs Frequency (differential out)    | 1      |

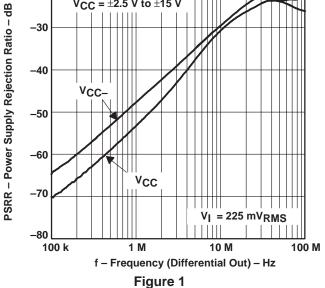

|                | Output amplitude             | vs AC response                     | 2      |

|                | Normalized output amplitude  | vs Frequency response              | 3      |

| CMMR           | Common-mode rejection ratio  | vs Frequency                       | 4      |

|                | Output amplitude             | vs Small signal frequency response | 5      |

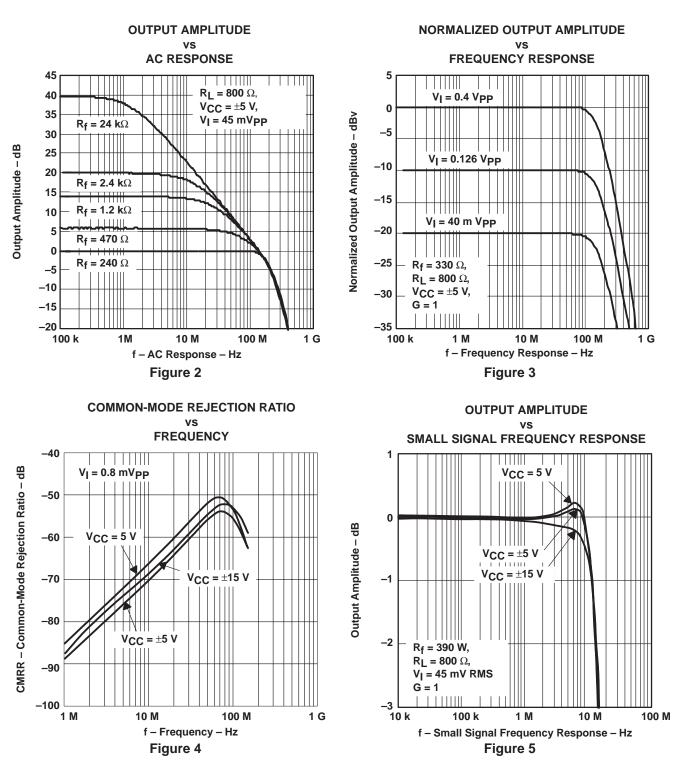

| SR             | Slew rate                    |                                    | 6      |

|                | Second harmonic distortion   | vs Frequency                       | 7      |

|                |                              | vs Output voltage                  | 8, 9   |

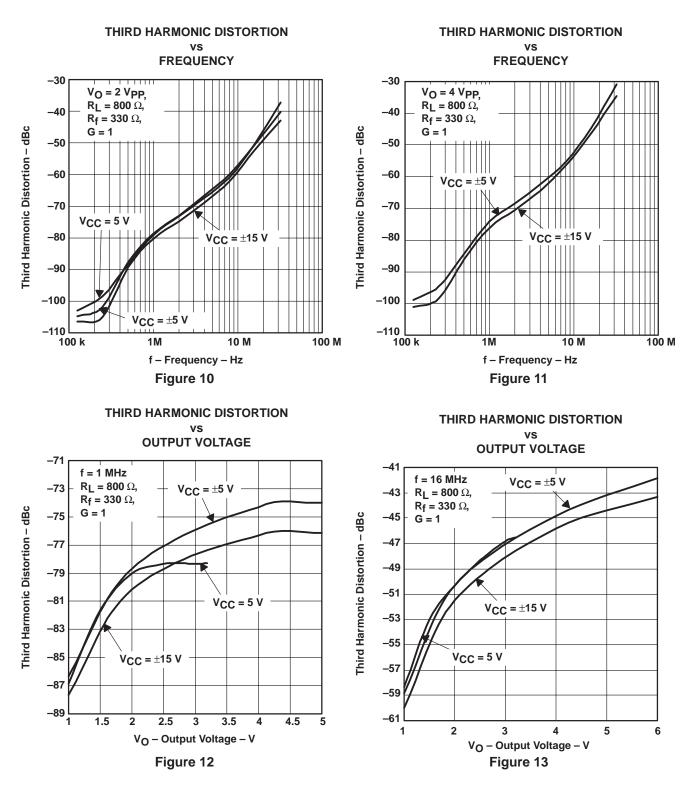

|                | Third harmonic distortion    | vs Frequency                       | 10, 11 |

|                |                              | vs Output voltage                  | 12, 13 |

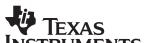

|                | Settling time                |                                    | 14     |

| V <sub>n</sub> | Voltage noise                | vs Frequency                       | 15     |

|                | Single-ended output voltage  | vs Common-mode output voltage      | 16     |

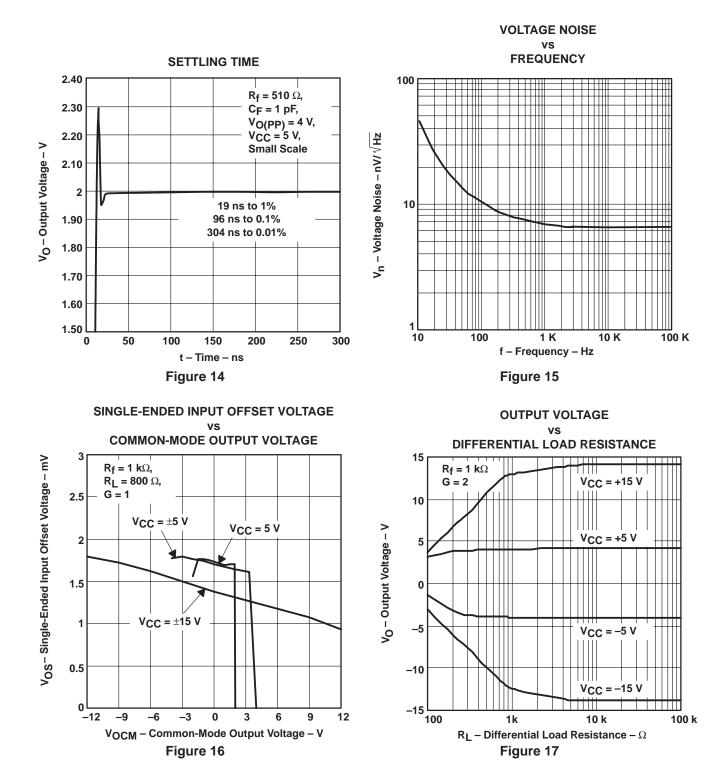

| VO             | Output voltage               | vs Differential load resistance    | 17     |

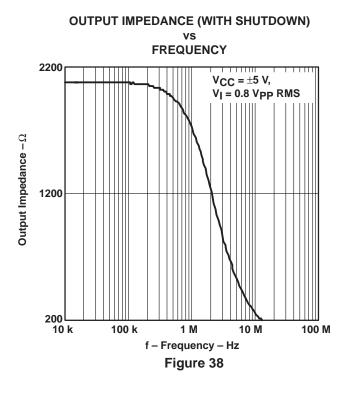

| z <sub>o</sub> | Output impedance             | vs Frequency                       | 18     |

|                | Input bias current           | vs Supply voltage                  | 19     |

|                | Output current range         | vs Supply voltage                  | 20     |

# POWER SUPPLY REJECTION RATIO vs FREQUENCY (DIFFERENTIAL OUT) V<sub>CC</sub> = ±2.5 V to ±15 V

-20

SLOS320A - MAY 2000 - REVISED AUGUST 2000

SLOS320A - MAY 2000 - REVISED AUGUST 2000

SLOS320A - MAY 2000 - REVISED AUGUST 2000

SLOS320A - MAY 2000 - REVISED AUGUST 2000

SLOS320A - MAY 2000 - REVISED AUGUST 2000

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### **APPLICATION INFORMATION**

### resistor matching

Resistor matching is important in fully differential amplifiers. The balance of the output on the reference voltage depends on matched ratios of the resistors. CMRR, PSRR, and cancellation of the second harmonic distortion will diminish if resistor mismatch occurs. Therefore, it is recommended to use 0.1% tolerance resistors or better to keep the performance optimized.

V<sub>OCM</sub> sets the dc level of the output signals. If no voltage is applied to the V<sub>OCM</sub> pin, it will be set to the midrail voltage internally defined as:

$$\frac{\left(\mathsf{V}_{\mathsf{C}\mathsf{C}}^{+}\right)+\left(\mathsf{V}_{\mathsf{C}\mathsf{C}}^{-}\right)}{2}$$

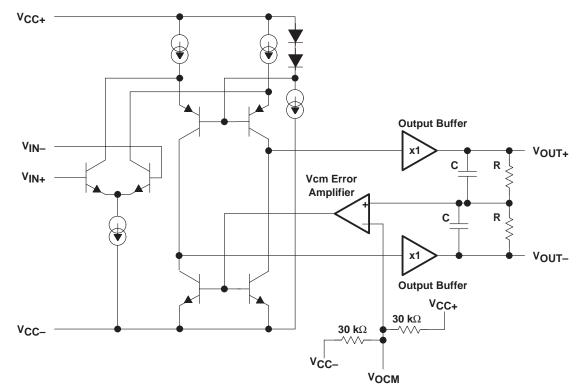

In the differential mode, the V<sub>OCM</sub> on the two outputs cancel each other. Therefore, the output in the differential mode is the same as the input in the gain of 1. V<sub>OCM</sub> has a high bandwidth capability up to the typical operation range of the amplifier. For the prevention of noise going through the device, use a 0.1  $\mu$ f capacitor on the V<sub>OCM</sub> pin as a bypass capacitor. The following graph shows the simplified diagram of the THS414x.

Figure 21. THS414x Simplified Diagram

SLOS320A - MAY 2000 - REVISED AUGUST 2000

# **APPLICATION INFORMATION**

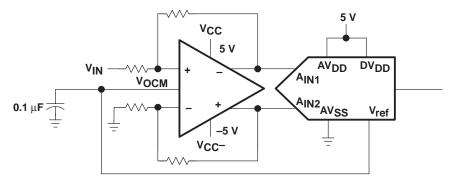

#### data converters

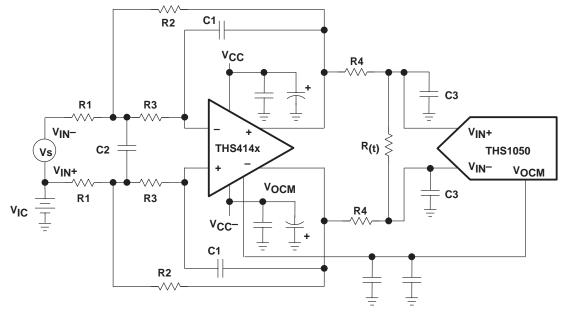

Data converters are one of the most popular applications for the fully differential amplifiers. The following schematic shows a typical configuration of a fully differential amplifier attached to a differential ADC.

Fully differential amplifiers can operate with a single supply.  $V_{OCM}$  defaults to the midrail voltage,  $V_{CC}/2$ . The differential output may be fed into a data converter. This method eliminates the use of a transformer in the circuit. If the ADC has a reference voltage output ( $V_{ref}$ ), then it is recommended to connect it directly to the  $V_{OCM}$  of the amplifier using a bypass capacitor for stability.

Figure 23. Differential Amplifier Using a Single Supply

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### **APPLICATION INFORMATION**

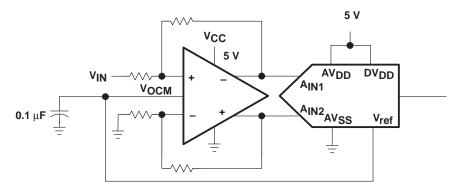

### driving a capacitive load

Driving capacitive loads with high performance amplifiers is not a problem as long as certain precautions are taken. The first is to realize that the THS414x has been internally compensated to maximize its bandwidth and slew rate performance. When the amplifier is compensated in this manner, capacitive loading directly on the output will decrease the device's phase margin leading to high frequency ringing or oscillations. Therefore, for capacitive loads of greater than 10 pF, it is recommended that a resistor be placed in series with the output of the amplifier, as shown in Figure 24. A minimum value of 20  $\Omega$  should work well for most applications. For example, in 50- $\Omega$  transmission systems, setting the series resistor value to 50  $\Omega$  both isolates any capacitance loading and provides the proper line impedance matching at the source end.

Figure 24. Driving a Capacitive Load

### circuit layout considerations

To achieve the levels of high frequency performance of the THS414x, follow proper printed-circuit board high frequency design techniques. A general set of guidelines is given below. In addition, a THS414x evaluation board is available to use as a guide for layout or for evaluating the device performance.

- Ground planes It is highly recommended that a ground plane be used on the board to provide all components with a low inductive ground connection. However, in the areas of the amplifier inputs and output, the ground plane can be removed to minimize the stray capacitance.

- Proper power supply decoupling Use a 6.8-μF tantalum capacitor in parallel with a 0.1-μF ceramic capacitor on each supply terminal. It may be possible to share the tantalum among several amplifiers depending on the application, but a 0.1-μF ceramic capacitor should always be used on the supply terminal of every amplifier. In addition, the 0.1-μF capacitor should be placed as close as possible to the supply terminal. As this distance increases, the inductance in the connecting trace makes the capacitor less effective. The designer should strive for distances of less than 0.1 inches between the device power terminals and the ceramic capacitors.

- Sockets Sockets are not recommended for high-speed operational amplifiers. The additional lead inductance in the socket pins will often lead to stability problems. Surface-mount packages soldered directly to the printed-circuit board is the best implementation.

- Short trace runs/compact part placements Optimum high frequency performance is achieved when stray

series inductance has been minimized. To realize this, the circuit layout should be made as compact as

possible, thereby minimizing the length of all trace runs. Particular attention should be paid to the inverting

input of the amplifier. Its length should be kept as short as possible. This will help to minimize stray

capacitance at the input of the amplifier.

SLOS320A - MAY 2000 - REVISED AUGUST 2000

# **APPLICATION INFORMATION**

### circuit layout considerations (continued)

Surface-mount passive components – Using surface-mount passive components is recommended for high

frequency amplifier circuits for several reasons. First, because of the extremely low lead inductance of

surface-mount components, the problem with stray series inductance is greatly reduced. Second, the small

size of surface-mount components naturally leads to a more compact layout thereby minimizing both stray

inductance and capacitance. If leaded components are used, it is recommended that the lead lengths be

kept as short as possible.

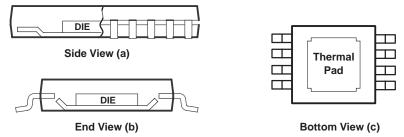

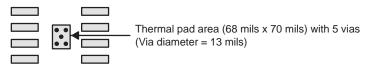

#### general PowerPAD<sup>™</sup> design considerations

The THS414x is available packaged in a thermally-enhanced DGN package, which is a member of the PowerPAD<sup>™</sup> family of packages. This package is constructed using a downset leadframe upon which the die is mounted [see Figure 25(a) and Figure 25(b)]. This arrangement results in the lead frame being exposed as a thermal pad on the underside of the package [see Figure 25(c)]. Because this thermal pad has direct thermal contact with the die, excellent thermal performance can be achieved by providing a good thermal path away from the thermal pad.

The PowerPAD<sup>™</sup> package allows for both assembly and thermal management in one manufacturing operation. During the surface-mount solder operation (when the leads are being soldered), the thermal pad can also be soldered to a copper area underneath the package. Through the use of thermal paths within this copper area, heat can be conducted away from the package into either a ground plane or other heat dissipating device.

The PowerPAD<sup>™</sup> package represents a breakthrough in combining the small area and ease of assembly of the surface mount with the, heretofore, awkward mechanical methods of heatsinking.

NOTE A: The thermal pad is electrically isolated from all terminals in the package.

Figure 25. Views of Thermally Enhanced DGN Package

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### **APPLICATION INFORMATION**

### general PowerPAD<sup>™</sup> design considerations (continued)

Although there are many ways to properly heatsink this device, the following steps illustrate the recommended approach.

- 1. Prepare the PCB with a top side etch pattern as shown in Figure 26. There should be etch for the leads as well as etch for the thermal pad.

- 2. Place five holes in the area of the thermal pad. These holes should be 13 mils in diameter. Keep them small so that solder wicking through the holes is not a problem during reflow.

- 3. Additional vias may be placed anywhere along the thermal plane outside of the thermal pad area. This helps dissipate the heat generated by the THS414xDGN IC. These additional vias may be larger than the 13-mil diameter vias directly under the thermal pad. They can be larger because they are not in the thermal pad area to be soldered so that wicking is not a problem.

- 4. Connect all holes to the internal ground plane.

- 5. When connecting these holes to the ground plane, *do not* use the typical web or spoke via connection methodology. Web connections have a high thermal resistance connection that is useful for slowing the heat transfer during soldering operations. This makes the soldering of vias that have plane connections easier. In this application, however, low thermal resistance is desired for the most efficient heat transfer. Therefore, the holes under the THS414xDGN package should make their connection to the internal ground plane with a complete connection around the entire circumference of the plated-through hole.

- 6. The top-side solder mask should leave the terminals of the package and the thermal pad area with its five holes exposed. The bottom-side solder mask should cover the five holes of the thermal pad area. This prevents solder from being pulled away from the thermal pad area during the reflow process.

- 7. Apply solder paste to the exposed thermal pad area and all of the IC terminals.

- 8. With these preparatory steps in place, the THS414xDGN IC is simply placed in position and run through the solder reflow operation as any standard surface-mount component. This results in a part that is properly installed.

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### **APPLICATION INFORMATION**

### general PowerPAD<sup>™</sup> design considerations (continued)

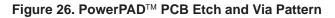

The actual thermal performance achieved with the THS414xDGN in its PowerPAD<sup>TM</sup> package depends on the application. In the example above, if the size of the internal ground plane is approximately 3 inches × 3 inches, then the expected thermal coefficient,  $\theta_{JA}$ , is about 58.4°C/W. For comparison, the non-PowerPAD<sup>TM</sup> version of the THS414x IC (SOIC) is shown. For a given  $\theta_{JA}$ , the maximum power dissipation is shown in Figure 27 and is calculated by the following formula:

$$\mathsf{P}_{\mathsf{D}} = \left(\frac{\mathsf{T}_{\mathsf{MAX}} - \mathsf{T}_{\mathsf{A}}}{\theta_{\mathsf{JA}}}\right)$$

Where:

P<sub>D</sub> = Maximum power dissipation of THS414x IC (watts)

$T_{MAX}$  = Absolute maximum junction temperature (150°C)

$T_A$  = Free-ambient air temperature (°C)

$\theta_{JA} = \theta_{JC} + \theta_{CA}$

$\theta_{JC}$  = Thermal coefficient from junction to case (°C/W)  $\theta_{CA}$  = Thermal coefficient from case to ambient air (°C/W)

Figure 27. Maximum Power Dissipation vs Free-Air Temperature

More complete details of the PowerPAD<sup>™</sup> installation process and thermal management techniques can be found in the Texas Instruments Technical Brief, *PowerPAD<sup>™</sup> Thermally Enhanced Package*. This document can be found at the TI web site (www.ti.com) by searching on the key word PowerPAD<sup>™</sup>. The document can also be ordered through your local TI sales office. Refer to literature number SLMA002 when ordering.

SLOS320A - MAY 2000 - REVISED AUGUST 2000

#### **APPLICATION INFORMATION**

### general PowerPAD<sup>™</sup> design considerations (continued)

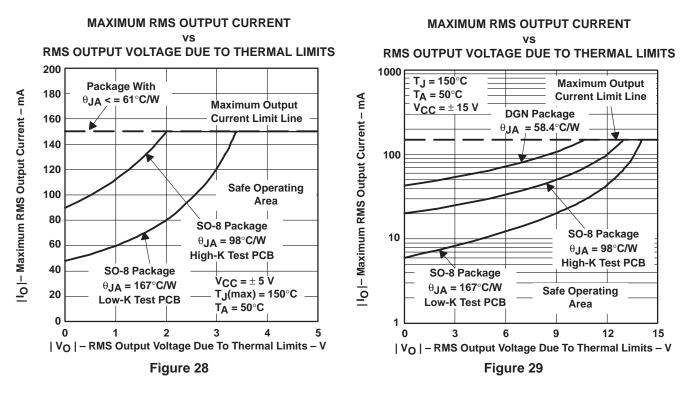

The next consideration is the package constraints. The two sources of heat within an amplifier are quiescent power and output power. The designer should never forget about the guiescent heat generated within the device, especially devices with multiple amplifiers or output stages. Because these devices have linear output stages (Class A-B), most of the heat dissipation is at low output voltages with high output currents. Figure 28 to Figure 29 show this effect, along with the quiescent heat, with an ambient air temperature of 50°C. Obviously, as the ambient temperature increases, the limit lines shown will drop accordingly. The area under each respective limit line is considered the safe operating area. Any condition above this line will exceed the amplifier's limits and failure may result. When using  $V_{CC} = \pm 5$  V, there is generally not a heat problem, even with SOIC packages. But, when using  $V_{CC} = \pm 15$  V, the SOIC package is severely limited in the amount of heat it can dissipate. The other key factor when looking at these graphs is how the devices are mounted on the PCB. The PowerPAD™ devices are extremely useful for heat dissipation. But, the device should always be soldered to a copper plane to fully utilize the heat dissipation properties of the PowerPAD™. The SOIC package, on the other hand, is highly dependent on how it is mounted on the PCB. As more trace and copper area is placed around the device,  $\theta_{IA}$  decreases and the heat dissipation capability increases. The currents and voltages shown in these graphs are for the total package. The sum of the RMS output currents and voltages should be used to choose the proper package. The graphs shown assume that both of the amplifier's outputs are symmetrical.

SLOS320A - MAY 2000 - REVISED AUGUST 2000

# **APPLICATION INFORMATION**

# Active antialias filtering

For signal conditioning in ADC applications, it is important to limit the input frequency to the ADC. Low-pass filters can prevent the aliasing of the high frequency noise with the frequency of operation. The following figure presents a method by which the noise may be filtered in the THS414x.

Figure 30. Antialias Filtering

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### **PRINCIPLES OF OPERATION**

### theory of operation

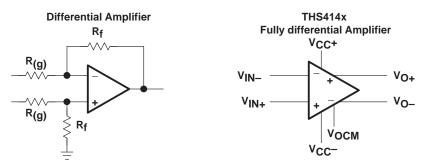

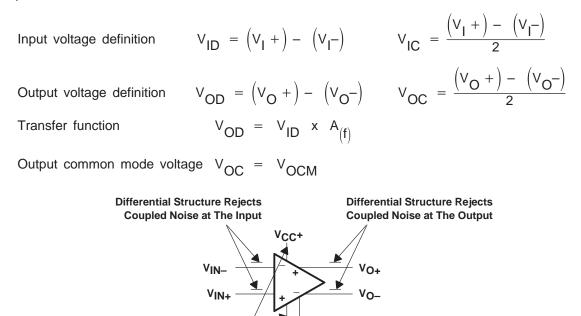

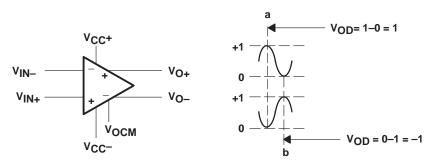

The THS414x is a fully differential amplifier. Differential amplifiers are typically *differential in/single out*, whereas fully differential amplifiers are *differential in/differential out*.

Figure 31. Differential Amplifier Versus a Fully Differential Amplifier

To understand the THS414x fully differential amplifiers, the definition for the pinouts of the amplifier are provided.

Differential Structure Rejects Coupled Noise at The Power Supply

Vосм

Vcc-

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### PRINCIPLES OF OPERATION

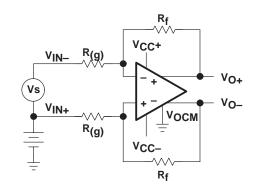

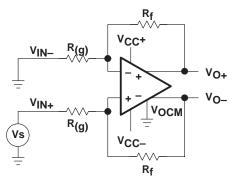

The following schematics depict the differences between the operation of the THS414x, fully differential amplifier, in two different modes. Fully differential amplifiers can work with differential input or can be implemented as single in/differential out.

Note: For proper operation, maintain symmetry by setting  $R_{f1} = R_{f2} = R_{f}$  and  $R_{(g)}1 = R_{(g)}2 = R_{(g)}$  $\Rightarrow A = R_{f}/R_{(g)}$

Figure 33. Amplifying Differential Signals

Figure 34. Single In With Differential Out

If each output is measured independently, each output is one-half of the input signal when gain is 1. The following equations express the transfer function for each output:

$$V_{O} = \frac{1}{2} V_{I}$$

The second output is equal and opposite in sign:

$$V_{O} = -\frac{1}{2} V_{I}$$

Fully differential amplifiers may be viewed as two inverting amplifiers. In this case, the equation of an inverting amplifier holds true for gain calculations. One advantage of fully differential amplifiers is that they offer twice as much dynamic range compared to single-ended amplifiers. For example, a 1-V<sub>PP</sub> ADC can only support an input signal of 1 V<sub>PP</sub>. If the output of the amplifier is 2 V<sub>PP</sub>, then it will not be practical to feed a 2-V<sub>PP</sub> signal into the targeted ADC. Using a fully differential amplifier enables the user to break down the output into two 1-V<sub>PP</sub> signals with opposite signs and feed them into the differential input nodes of the ADC. In practice, the designer has been able to feed a 2-V peak-to-peak signal into a 1-V differential ADC with the help of a fully differential amplifier. The final result indicates twice as much dynamic range. Figure 35 illustrates the increase in dynamic range. The gain factor should be considered in this scenario. The THS414x fully differential amplifier offers an improved CMRR and PSRR due to its symmetrical input and output. Furthermore, second harmonic distortion is improved. Second harmonics tend to cancel because of the symmetrical output.

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### **PRINCIPLES OF OPERATION**

Figure 35. Fully Differential Amplifier With Two 1-V<sub>PP</sub> Signals

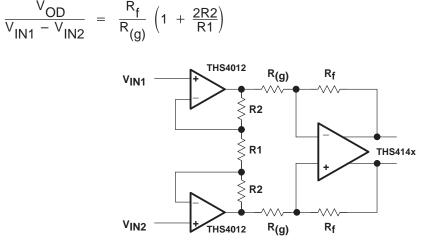

Similar to the standard inverting amplifier configuration, input impedance of a fully differential amplifier is selected by the input resistor,  $R_{(g)}$ . If input impedance is a constraint in design, the designer may choose to implement the differential amplifier as an instrumentation amplifier. This configuration improves the input impedance of the fully differential amplifier. The following schematic depicts the general format of instrumentation amplifiers.

The general transfer function for this circuit is:

Figure 36. Instrumentation Amplifier

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### PRINCIPLES OF OPERATION

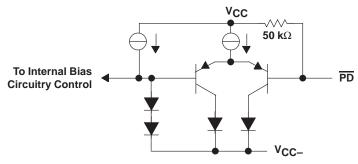

#### power-down mode

The power-down mode is used when power saving is required. The power-down terminal ( $\overline{PD}$ ) found on the THS414x is an active low terminal. If it is left as a no-connect terminal, the device will always stay on due to an internal 50 k $\Omega$  resistor to V<sub>CC</sub>. The threshold voltage for this terminal is approximately 1.4 V above V<sub>CC</sub>–. This means that if the  $\overline{PD}$  terminal is 1.4 V above V<sub>CC</sub>–, the device is active. If the  $\overline{PD}$  terminal is less than 1.4 V above V<sub>CC</sub>–, the device is off. For example, if V<sub>CC</sub>–=-5 V, then the device is on when PD reaches -3.6 V, (-5 V + 1.4 V = -3.6 V). By the same calculation, the device is off below -3.6 V. It is recommended to pull the terminal to V<sub>CC</sub>– in order to turn the device off. The following graph shows the simplified version of the power-down circuit. While in the power-down state, the amplifier goes into a high impedance state. The amplifier output impedance is typically greater than 1 M $\Omega$  in the power-down state.

Figure 37. Simplified Power-Down Circuit

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### **PRINCIPLES OF OPERATION**

Due to the similarity of the standard inverting amplifier configuration, the output impedance appears to be very low while in the power-down state. This is because the feedback resistor ( $R_f$ ) and the gain resistor ( $R_{(g)}$ ) are still connected to the circuit. Therefore, a current path is allowed between the input of the amplifier and the output of the amplifier. An example of the closed loop output impedance is shown in Figure 38.

### resistor values

Suggested resistor values for various gains.

| GAIN | <b>R<sub>(g)</sub></b> Ω | $R_{f}\Omega$ |

|------|--------------------------|---------------|

| 1    | 390                      | 390           |

| 2    | 374                      | 750           |

| 5    | 402                      | 2010          |

| 10   | 402                      | 4020          |

SLOS320A - MAY 2000 - REVISED AUGUST 2000

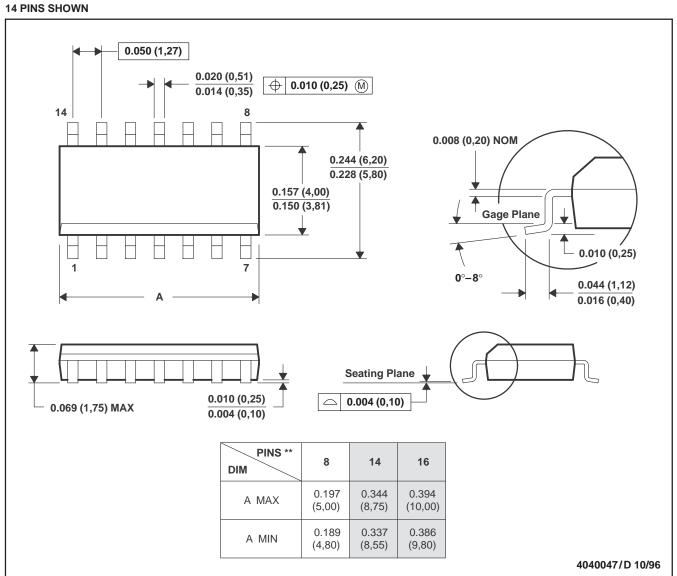

### **MECHANICAL DATA**

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: B. All linear dimensions are in inches (millimeters).

C. This drawing is subject to change without notice.

D. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

E. Falls within JEDEC MS-012

SLOS320A - MAY 2000 - REVISED AUGUST 2000

### **MECHANICAL DATA**

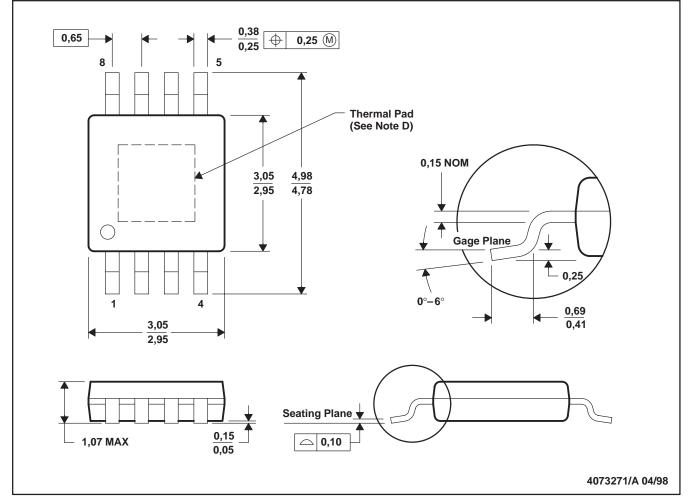

#### DGN (S-PDSO-G8)

### PowerPAD<sup>™</sup> PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions include mold flash or protrusions.

- D. The package thermal performance may be enhanced by attaching an external heat sink to the thermal pad. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MO-187

PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated