256 x 4 Static RAM

## DISTINCTIVE CHARACTERISTICS

- Low operating power dissipation

125 mW typ.; 290 mW maximum standard power

100 mW typ.; 175 mW maximum low power

- High noise immunity full 400 mV

- Uniform switching characteristics access times insensitive to supply variations, address patterns and data patterns

- Bus-oriented I/O data

- Zero address, setup and hold times guaranteed for simpler timing

- Direct plug-in replacement for 2112 type devices

#### GENERAL DESCRIPTION

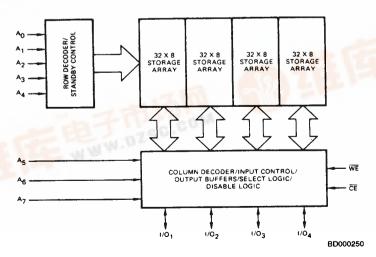

The Am9112/Am91L12 series of products are high-performance, low-power, 1024-bit, static read/write random-access memories. They offer a range of speeds and power dissipations including versions as fast as 200 ns and as low as 100 mW typical.

Each memory is implemented as 256 words by 4 bits per word. This organization allows efficient design of small memory systems and permits finer resolution of incremental memory word size relative to 1024 by 1 devices. The output and input data signals are internally bussed together and share 4 common I/O pins. This feature keeps the package size small and provides a simplified interface to bus-oriented systems.

The Am9112/Am91L12 memories may be operated in a DC standby mode for reductions of as much as 84% of the normal operating power dissipation. Though the memory cannot be operated, data can be retained in the storage cells with a power supply as low as 1.5 volts. The Am91L12 versions offer reduced power during normal operating

conditions as well as even lower dissipation in standby mode.

The eight Address inputs are decoded to select 1 of 256 locations within the memory. The Chip Enable input acts as a high-order address in multiple chip systems. It also controls the write amplifier and the output buffers in conjunction with the Write Enable input. When CE is LOW and WE is HIGH, the write amplifiers are disabled, the output buffers are enabled, and the memory will execute a read cycle. When CE is LOW and WE is LOW, the write amplifiers are enabled, the output buffers are disabled, and the memory will execute a write cycle. When CE is HIGH, both the write amplifiers and the output buffers are disabled.

These memories are fully static and require no refresh operations or sense amplifiers or clocks. All input and output voltage levels are identical to standard TTL specifications, including the power supply.

## **BLOCK DIAGRAM**

Publication # Rev. Amendment 03257 D /0

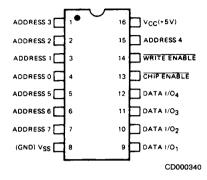

# CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

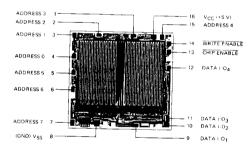

# METALLIZATION AND PAD LAYOUT

Die Size 0.132" x 0.131"

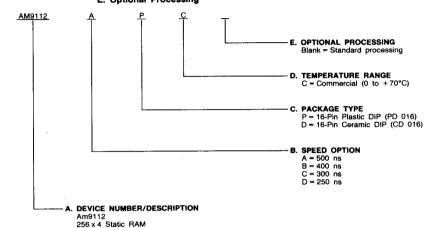

## **ORDERING INFORMATION (Cont'd.)**

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: **A. Device Number**

- B. Speed Option (if applicable)

- C. Package Type

Am91L12 = Low-Power Version

- D. Temperature Range

- E. Optional Processing

| Valid Combinations |        |  |  |  |  |

|--------------------|--------|--|--|--|--|

| AM9112A            |        |  |  |  |  |

| √ ÁM9112B          |        |  |  |  |  |

| AM9112C            |        |  |  |  |  |

| \_AM9112D          | PC, DC |  |  |  |  |

| AM91L12A           |        |  |  |  |  |

| , AM91L12B         |        |  |  |  |  |

| AM91L12C           |        |  |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

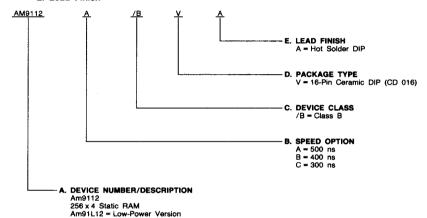

## ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

| Valid Combinations |      |  |  |  |  |

|--------------------|------|--|--|--|--|

| AM9112A            |      |  |  |  |  |

| AM9112B            |      |  |  |  |  |

| AM9112C            |      |  |  |  |  |

| AM91L12A           | /BVA |  |  |  |  |

| AM91L12B           |      |  |  |  |  |

| AM91L12C           |      |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

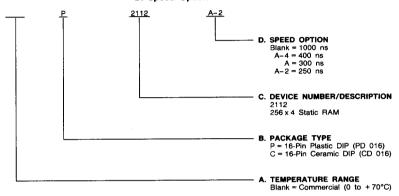

## ORDERING INFORMATION

## **Commodity Products**

AMD commodity products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: **A. Temperature Range**

- B. Package Type

- C. Device Number

- D. Speed Option

## **Valid Combinations**

|      | Valid Comb | oinations   |

|------|------------|-------------|

| P, C | 2112       | A-4, A, A-2 |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTION

## A<sub>0</sub> - A<sub>7</sub> Addresses (Input)

The 8-bit field presented at the address inputs selects one of the 256 memory locations to be read from — or written into — via the Data Input/Output lines.

I/O<sub>1</sub>-1/O<sub>4</sub> Data Input/Output Lines (Input/Output)

If WE is LOW, the data represented on the Data I/O lines can be written into the selected memory location. If WE is

HIGH, the Data I/O lines represent the data read from the selected memory location.

## CE Chip Enable (Input, Active LOW)

Read and Write cycles can be executed only when  $\overline{\text{CE}}$  is LOW.

## WE Write Enable (Input, Active LOW)

Data is written into the memory if WE is LOW and read from the memory if WE is HIGH.

# FUNCTIONAL DESCRIPTION

#### **Applications**

These memory products provide all of the advantages of AMD's other static N-channel memory circuits: +5 only power supply, all TTL interface, no clocks, no sensing, no refreshing, military temperature range available, low-power versions available, high speed, high output drive, etc. In addition, the Am9112 series features a 256 x 4 organization with common pins used for both Data In and Data Out signals.

This bussed I/O approach keeps the package pin count low, allowing the design of higher density memory systems. It also provides a direct interface to bus-oriented systems, eliminating bussing logic that could otherwise be required. Most microprocessor systems, for example, transfer information on a bidirectional data bus. The Am9112 memories can connect directly to such a processor since the common I/O pins act as a bidirectional data bus.

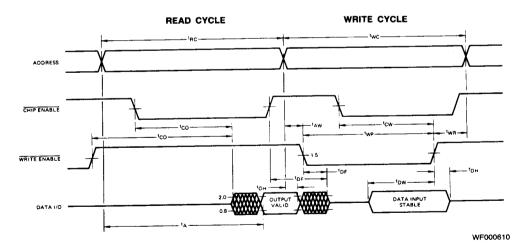

If the chip is enabled (CE LOW) and the memory is in the Read state (WE HIGH), the output buffers will be turned on and will be driving data on the I/O bus lines. If the external system tries to drive the bus with data, there may be contention for control of the data lines and large current surges can result. Since the condition can occur at the beginning of a write cycle, it is important that incoming data to be written not be entered until the output buffers have been turned off.

These operational suggestions for write cycles may be of some help for memory system designs:

- 1. For systems where CE is always LOW or is derived directly from addresses and so is LOW for the whole cycle, make sure twp is at least tpw + tpr and delay the input data until tpr following the falling edge of WE. With zero address set-up and hold times, it will often be convenient to make WE a cycle-width level (twp = twc) so that the only subcycle timing required is the delay of the input data.

- For systems where \(\overline{CE}\) is HIGH for at least t<sub>DF</sub> preceeding the falling edge of \(\overline{WE}\), t<sub>WP</sub> may assume the minimum specified value. When \(\overline{CE}\) is HIGH for t<sub>DF</sub> before the start of the cycle, then no other subcycle timing is required and \(\overline{WE}\) and data-in may be cyclewidth levels.

- 3. Notice that because both CE and WE must be LOW to cause a write to take place, either signal can be used to determine the effective write pulse. Thus, WE could be a level with CE becoming the write timing signal. In such a case, the data set-up and hold times are specified with respect to the rising edge of CE. The value of the data set-up time remains the same and the value of the data hold time should change to a minimum of 25 ns.

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| Storage Temperature           | 65 to    | + 150°C  |

|-------------------------------|----------|----------|

| Ambient Temperature with      |          |          |

| Power Applied                 | 55 to    | + 125°C  |

| Supply Voltage                | -0.5 V t | o +7.0 V |

| DC Voltage Applied to Outputs | -0.5 V t | o +7.0 V |

| DC Layout Voltage             | -0.5 V t | o +7.0 V |

| Power Description             |          |          |

| DC Output Current             |          |          |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES** (Note 2)

| Commercial (C) Devices |                      |

|------------------------|----------------------|

| Temperature            | 0 to +70°C           |

| Supply Voltage         | + 4.75 V to + 5.25 V |

| Military (M) Devices*  |                      |

| Temperature            | 55 to +125°C         |

| Supply Voltage         | +4.5 V to +5.5 V     |

Operating ranges define those limits between which the functionality of the device is guaranteed.

\*Military product 100% tested at  $T_C$  = +25°C, +125°C, and -55°C.

## DC CHARACTERISTICS over operating range unless otherwise specified\*

|                     |                          |                                                             |                                                                 |            | C De     | vices    | M De     | vices                  |          |  |  |      |    |   |

|---------------------|--------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|------------|----------|----------|----------|------------------------|----------|--|--|------|----|---|

| Parameter<br>Symbol | Parameter<br>Description | т                                                           | Min.                                                            | Max.       | Min.     | Max.     | Units    |                        |          |  |  |      |    |   |

| Voн                 | Output HIGH Voltage      | V <sub>CC</sub> = Min., I <sub>OH</sub> =                   | -200 μA                                                         |            | 2.4      |          | 2.2      |                        | V        |  |  |      |    |   |

| VOL                 | Output LOW Voltage       | V <sub>CC</sub> = Min., I <sub>OL</sub> = 1                 | 3.2 mA                                                          |            |          | 0.4      |          | 0.4                    | V        |  |  |      |    |   |

| VIH                 | Input HIGH Voltage       |                                                             |                                                                 |            | 2.0      | Vcc      | 2.0      | Vcc                    | V        |  |  |      |    |   |

| VIL                 | Input LOW Voltage        |                                                             |                                                                 |            | -0.5     | 0.8      | -0.5     | 0.8                    | V        |  |  |      |    |   |

| ILI.                | Input Load Current       | V <sub>CC</sub> = Max., 0 V ≤                               | < V <sub>IN</sub> ≤ V <sub>CC</sub>                             |            |          | 10       |          | 10                     | μΑ       |  |  |      |    |   |

|                     |                          |                                                             | Vo = Vcc                                                        |            |          | 5        |          | 10                     | μА       |  |  |      |    |   |

| 110                 | I/O Leakage Current      | V=CE = V <sub>IH</sub>                                      | V <sub>O</sub> = 0.4 V                                          |            |          | -10      |          | -10                    |          |  |  |      |    |   |

|                     |                          |                                                             | T <sub>A</sub> = 25°C                                           | 9112A/B    |          | 50       |          | 50                     | mA       |  |  |      |    |   |

|                     |                          |                                                             |                                                                 | 9112C/D/E  |          | 55       |          | 55                     |          |  |  |      |    |   |

|                     |                          |                                                             |                                                                 | 91L12A/B   |          | 31       |          | 31                     |          |  |  |      |    |   |

|                     |                          |                                                             |                                                                 | 91L12C/D/E |          | 34       |          | 34                     |          |  |  |      |    |   |

|                     |                          |                                                             |                                                                 | 9112A/B    | T        | 55       |          |                        |          |  |  |      |    |   |

|                     |                          | Data Out Open                                               | T 0°C                                                           | 9112C/D/E  |          | 60       |          |                        |          |  |  |      |    |   |

| ICC                 | Power Supply Current     | V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = V <sub>CC</sub> | T <sub>A</sub> = 0°C<br>(Note 3)                                | (Note 3)   | (Note 3) | (Note 3) | 91L12A/B |                        | 33       |  |  | ] "" |    |   |

|                     |                          | VIIN VCC                                                    |                                                                 | 91L12C/D/E |          | 36       |          |                        | ]        |  |  |      |    |   |

|                     |                          |                                                             |                                                                 | 9112A/B    |          |          |          | 60                     |          |  |  |      |    |   |

|                     |                          |                                                             |                                                                 | 9112C/D/E  |          |          |          | 65                     | 1        |  |  |      |    |   |

|                     |                          | TA*                                                         |                                                                 |            |          |          |          | T <sub>A</sub> = -55°C | 91L12A/B |  |  |      | 37 | 1 |

|                     |                          |                                                             | 91L12C/D                                                        |            |          |          |          | 40                     | 1        |  |  |      |    |   |

| CIN                 | Input Capacitance        | V <sub>IN</sub> = 0 V, T <sub>A</sub> = 2                   | 5°C, f = 1 MHz (                                                | Note 3)    |          | 9        |          | 9                      | ρF       |  |  |      |    |   |

| Co                  | Output Capacitance       |                                                             | V <sub>O</sub> = 0 V, T <sub>A</sub> = 25°C, f = 1 MHz (Note 3) |            |          |          |          | 11                     | ] pr     |  |  |      |    |   |

Notes: See notes following Switching Characteristics table.

# STANDBY OPERATING CONDITIONS over temperature range unless otherwise specified

| Parameter<br>Symbol | Parameter<br>Description        | Test Conditions                                        |                         | Min.                                                   | Тур.                   | Max.        | Units       |          |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

|---------------------|---------------------------------|--------------------------------------------------------|-------------------------|--------------------------------------------------------|------------------------|-------------|-------------|----------|----|----|----|----|--|--|--|--|--|--|--|--|--|--|--|--|--|--------------------|--------|---------|----|----|----|

| V <sub>PD</sub>     | V <sub>CC</sub> in Standby Mode |                                                        |                         |                                                        | 1.5                    |             |             | <u> </u> |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

|                     |                                 |                                                        |                         |                                                        |                        | 11          | 25          | İ        |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

|                     |                                 | T <sub>A</sub> = 0°C<br>All Inputs = V <sub>PD</sub>   |                         | V <sub>PD</sub> = 1.5 V                                | VPD = 1.5 V            | VPD = 1.5 V | VPD = 1.5 V | Am9112   |    | 13 | 31 | mA |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

|                     |                                 |                                                        |                         | Am91L12                                                |                        | 13          | 31          |          |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

| Į                   |                                 |                                                        |                         | Am9112                                                 |                        | 17          | 41          | 1        |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

| IPD                 | ICC in Standby Mode             | T <sub>A</sub> = -55°C<br>All inputs = V <sub>PD</sub> |                         | T <sub>A</sub> = -55°C<br>All inputs = V <sub>PD</sub> | T <sub>A</sub> = -55°C | Am91L12     |             | 11       | 28 |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

|                     |                                 |                                                        |                         |                                                        |                        |             |             |          |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  | VPD = 1.5 V Am9112 | Am9112 |         | 13 | 34 | mA |

|                     |                                 |                                                        |                         |                                                        |                        |             |             |          |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  | Ail inputs = VPD   |        | Am91L12 |    | 13 | 34 |

|                     |                                 |                                                        | V <sub>PD</sub> = 2.0 V | Am9112                                                 |                        | 17          | 46          |          |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

| dv/dt               | Rate of Change of VCC           |                                                        |                         |                                                        |                        |             | 1.0         | V/µs     |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

| t <sub>R</sub>      | Standby Recovery Time           | 1.                                                     |                         |                                                        | tac                    |             |             | ns       |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

| tCP                 | Chip Deselect Time              |                                                        |                         |                                                        | 0                      |             |             | ns       |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

| VCES                | CE Bias in Standby              |                                                        |                         |                                                        | V <sub>PD</sub>        |             | L           | Volts    |    |    |    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |                    |        |         |    |    |    |

\*See the last page of this spec for Group A Subgroup Testing information.

#### **Power-Down Standby Operation**

The Am9112/Am91L12 Family is designed to maintain storage in a standby mode. The standby mode is entered by lowering V<sub>CC</sub> to around 1.5 – 2.0 volts (see table and graph). When the voltage to the device is reduced, the storage cells are isolated from the data lines, so their contents will not change. The standby mode may be used by a battery operated

backup power supply system, or, in a large system, memory pages not being accessed can be placed in standby to save power. A standby recovery time must elapse following restoration of normal power before the memory may be accessed.

To ensure that the output of the device is in a high-impedance OFF state during standby, the chip select should be held at  $V_{\rm IH}$  or  $V_{\rm CES}$  during the entire standby cycle.

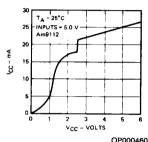

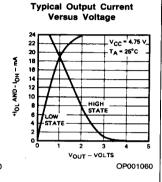

# TYPICAL DC and AC CHARACTERISTICS

VCC

VIH

VES

VIL

DESELECT

CHIP

STANDBY MODE

RECOVERY

READ OR

WRITE

CYCLE

WFOOO300

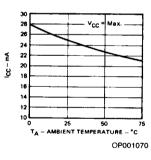

Typical Power Supply Current

Versus Voltage

1.05 T<sub>A</sub> - 70°C 1.0 0.90 0.90 0.90 0.90 0.05 0.00 6.5 6.0 0.0000100

**Access Time**

Versus V<sub>CC</sub> Normalized to

V<sub>CC</sub> = +5.0 Volts

Typical Power Supply Current

Versus Ambient Temperature

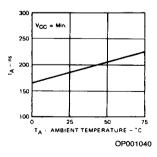

Typical V<sub>IN</sub> Limits

Versus Ambient Temperature

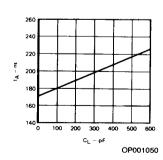

Typical t<sub>A</sub> Versus Ambient Temperature

Typical ta Versus Cu

# SWITCHING CHARACTERISTICS over operating range unless otherwise specified (Note 4)\*

|     |                     | _                                                       |      | 112A<br>1L12A | 1    | 112B<br>1L12B |      | 112C<br>1L12C | Am9  | 112D |       |

|-----|---------------------|---------------------------------------------------------|------|---------------|------|---------------|------|---------------|------|------|-------|

| No. | Parameter<br>Symbol | Parameter<br>Description                                | Min. | Max.          | Min. | Max.          | Min. | Max.          | Min. | Max. | Units |

| 1   | tRC                 | Read Cycle Time                                         | 500  |               | 400  |               | 300  |               | 250  |      | ns    |

| 2   | tA                  | Access Time                                             |      | 500           |      | 400           |      | 300           |      | 250  | ns    |

| 3   | tco                 | Output Enabled to Output ON Delay (Note 5)              | 5.0  | 175           | 5.0  | 150           | 5.0  | 125           | 5.0  | 100  | ns    |

| 4   | t <sub>OH</sub>     | Previous Read Data Valid with Respect to Address Change | 40   |               | 40   |               | 40   |               | 30   |      | ns    |

| 5   | t <sub>OF</sub>     | Output Disabled to Output OFF Delay (Note 6)            | 5.0  | 125           | 5.0  | 100           | 5.0  | 100           | 5.0  | 75   | ns    |

| 6   | twc                 | Write Cycle Time                                        | 500  |               | 400  |               | 300  |               | 250  |      | ns    |

| 7   | taw                 | Address Setup Time                                      | 20   |               | 20   | I             | 20   |               | 20   |      | ns    |

| 8   | twn                 | Address Hold Time                                       | 0    |               | 0    |               | 0    |               | 0    | ļ    | ns    |

| 9   | twp                 | Write Pulse Width (Note 7)                              | 225  |               | 200  |               | 175  |               | 150  |      | ns    |

| 10  | tcw                 | Chip Enable Setup Time                                  | 175  |               | 150  |               | 125  | <u> </u>      | 100  | ļ    | ns    |

| 11  | t <sub>DW</sub>     | Input Data Setup Time                                   | 150  |               | 125  |               | 100  |               | 85   | ļ    | ns    |

| 12  | t <sub>DH</sub>     | Input Data Hold Time (Note 8)                           | 15   |               | 15   |               | 15   | <u> </u>      | 15   |      | ns    |

Notes: 1. Absolute maximum ratings are intended for user guidelines and are not tested.

2. For test and correlation purposes, ambient temperature is defined as the stabilized case temperature.

3. Guaranteed by characterization data. Data will be updated upon any process or design change which affects this parameter.

4. Test conditions assume signal transition times of 10 ns or less. Output load equals 1 TTL gate + 100 pF. Input signal timing reference levels = 0.5 V, with input pulse levels of 0 to 3.0 V. Data output timing reference levels = 0.8 and 2.0 V.

5. Output is enabled and top defined from either the rising edge of CE or the falling edge of WE.

7. Minimum twp is valid when CE has been HIGH at least top before WE goes LOW. Otherwise twp(Min). \* tDF(Min.).

8. When WE goes HIGH at the end of the write cycle, it will be possible to turn on the output buffers if CE is still LOW. The data out will be the same as the data just written and so will not conflict with input data that may still be on the I/O bus.

## SWITCHING WAVEFORMS (Note 9)

<sup>\*</sup>See the last page of this spec for Group A Subgroup Testing information.

# GROUP A SUBGROUP TESTING

## DC CHARACTERISTICS

| Parameter<br>Symbol | Subgroups |

|---------------------|-----------|

| VoH                 | 1, 2, 3   |

| VOL                 | 1, 2, 3   |

| ViH                 | 1, 2, 3   |

| VIL                 | 1, 2, 3   |

| l <sub>L</sub> i    | 1, 2, 3   |

| ILO                 | 1, 2, 3   |

| lcc                 | 1, 2, 3   |

| V <sub>PD</sub>     | 1, 2, 3   |

| lpD                 | 1, 2, 3   |

# SWITCHING CHARACTERISTICS

| No. | Parameter<br>Symbol | Subgroups       |

|-----|---------------------|-----------------|

| 1   | tRC                 | 7, 8, 9, 10, 11 |

| 2   | t <sub>A</sub>      | 7, 8, 9, 10, 11 |

| 3   | tco                 | 7, 8, 9, 10, 11 |

| 4   | tон                 | 7, 8, 9, 10, 11 |

| 5   | t <sub>DF</sub>     | 7, 8, 9, 10, 11 |

| 6   | twc                 | 7, 8, 9, 10, 11 |

| 7   | taw                 | 7, 8, 9, 10, 11 |

| 8   | twr                 | 7, 8, 9, 10, 11 |

| 9   | twp                 | 7, 8, 9, 10, 11 |

| 10  | tcw                 | 7, 8, 9, 10, 11 |

| 11  | tow                 | 7, 8, 9, 10, 11 |

| 12  | t <sub>DH</sub>     | 7, 8, 9, 10, 11 |

## MILITARY BURN-IN

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Method 1015, Conditions A through E. Test conditions are selected at AMD's option.