### 查询MAX8529供应商

19-2696; Rev 0; 1/03

EVALUATION KIT AVAILABLE

# 1.5MHz Dual 180° Out-of-Phase PWM Step-Down Controller with POR

# **General Description**

The MAX8529 dual, synchronized, step-down controller generates two outputs from input supplies ranging from 4.75V to 23V. Each output is adjustable from sub-1V to 18V. Input voltage ripple and total RMS input ripple current are reduced by synchronized 180-degree out-of-phase operation.

The switching frequency is adjustable from 600kHz to 1.5MHz with an external resistor. Alternatively, the controller can be synchronized to an external clock generated to another MAX8529 or a system clock. One MAX8529 can be set to generate an in-phase, or 90-degree out-of-phase, clock signal for synchronization with additional controllers. This allows two controllers to operate either as an interleaved two- or four-phase system with each output shifted by 90 degrees. These devices also feature soft-start and soft-stop.

The MAX8529 eliminates the need for current-sense resistors by utilizing the low-side MOSFET's on-resistance as a current-sense element. This protects the DC-to-DC components from damage during output overload conditions or when output short circuit faults without requiring a current-sense resistor. Adjustable foldback current limit reduces power dissipation during short-circuit conditions. The MAX8529 includes a power-on reset output to signal the system when both outputs reach regulation.

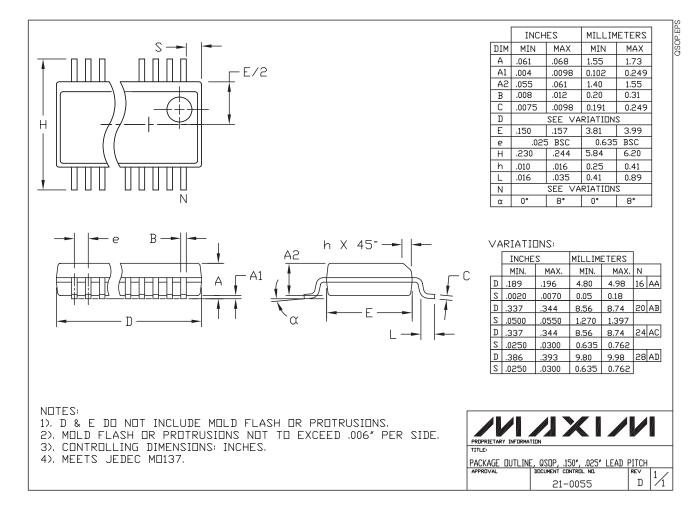

The MAX8529 is available in a 24-pin QSOP package. An evaluation kit is available to speed designs.

Applications

xDSL Modems and Routers DSP, ASIC, and FPGA Power Supplies Set-Top Boxes Broadband Routers

- Low Output Noise in DSL Band

- Ceramic Input/Output Capacitors

- Step-Down or Step-Up/Step-Down Operation

- Four Output, 90-Degree Out-of-Phase Operation (Using Two MAX8529s)

- Foldback Current Limit

- ♦ 4.75V to 23V Input Supply Range

- ♦ 0 to 18V Output Voltage Range (Up to 6A)

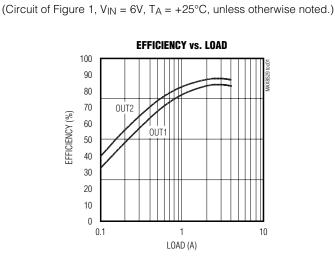

- >90% Efficiency

- Fixed-Frequency PWM Operation

- Adjustable 600kHz to 1.5MHz Switching Frequency

- External SYNC Input

- Clock Output for Master/Slave Synchronization

- Soft-Start and Soft-Stop

- ◆ RST Output with 140ms Minimum Delay

- Lossless Current Limit (No Sense Resistor)

# Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX8529EEG | -40°C to +85°C | 24 QSOP     |

# Pin Configuration

TOP VIEW COMP2 24 EN 23 DH2 FB2 2 ILIM2 22 LX2 21 BST2 OSC 4 V+ 5 20 DL2 MAXIM MAX8529 REF 6 19 V<sub>L</sub> 18 PGND GND 7 CKO 8 17 DL1 16 BST1 SYNC 9 15 LX1 ILIM1 10 14 DH1 FB1 11 COMP1 12 13 RST QSOP

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

捷多邦,专业PCB打样工厂,24小时加急出货

# **ABSOLUTE MAXIMUM RATINGS**

| V+ to GND                       | 0.3V to +25V                     |

|---------------------------------|----------------------------------|

| PGND to GND                     | 0.3V to +0.3V                    |

| VL to GND0.3V to the lower of - | +6V and (V+ + 0.3V)              |

| BST1, BST2 to GND               | 0.3V to +30V                     |

| LX1 to BST1                     | 6V to +0.3V                      |

| LX2 to BST2                     | 6V to +0.3V                      |

| DH1 to LX10.                    | 3V to (V <sub>BST1</sub> + 0.3V) |

| DH2 to LX20.                    | 3V to (V <sub>BST2</sub> + 0.3V) |

| DL1, DL2 to PGND                | 0.3V to (V <sub>L</sub> + 0.3V)  |

| CKO, REF, OSC, ILIM1, ILIM2,    |                                  |

| COMP1, COMP2 to GND             | 0.3V to (V <sub>L</sub> + 0.3V)  |

| FB1, FB2, RST, SYNC, EN to GND                        | 0.3V to +6V   |

|-------------------------------------------------------|---------------|

| VL to GND Short Circuit                               | Continuous    |

| REF to GND Short Circuit                              | Continuous    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

| 24-Pin QSOP (derate 9.4mW/°C above +70°               | C)762mW       |

| Operating Temperature Range                           | 40°C to +85°C |

| Junction Temperature                                  | +150°C        |

| Storage Temperature Range                             |               |

| Lead Temperature (soldering, 10s)                     | +300°C        |

|                                                       |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V + = 12V, EN = ILIM_ = V_L, SYNC = GND, I_{VL} = 0mA, PGND = GND, C_{REF} = 0.22\mu$ F,  $C_{VL} = 4.7\mu$ F (ceramic),  $R_{OSC} = 10k\Omega$ , compensation components for COMP\_ are from Figure 1,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C (Note 1), unless otherwise noted.)

| PARAMETER                                         | CONDITIONS                                                                  |                                                 |                       | MIN  | ТҮР                    | MAX   | UNITS |  |

|---------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------|-----------------------|------|------------------------|-------|-------|--|

| GENERAL                                           |                                                                             |                                                 |                       |      |                        |       |       |  |

|                                                   | (Note 2)                                                                    | (Note 2)                                        |                       |      |                        | 23.00 | V     |  |

| V+ Operating Range                                | $V_L = V + (Note 2)$                                                        | $V_L = V_+$ (Note 2)                            |                       |      |                        | 5.50  |       |  |

| V+ Operating Supply Current                       | VL unloaded, no M                                                           | 10SFETs (                                       | connected             | 4.0  | 4.8                    | 7.0   | mA    |  |

| V+ Standby Supply Current                         | EN = LX_ = FB_ =                                                            | 0V                                              | $R_{OSC} = 10k\Omega$ | 0.50 | 0.65                   | 1.00  | mA    |  |

| Thermal Shutdown                                  | Rising temperature                                                          | Rising temperature, typical hysteresis = 10°C   |                       |      | 160                    |       | °C    |  |

| Current-Limit Threshold                           |                                                                             | ILIN                                            | 1_ = VL               | 75   | 100                    | 125   | mV    |  |

|                                                   | PGND - LX_                                                                  | RILI                                            | $M_{-} = 100 k\Omega$ | 32   | 50                     | 62    |       |  |

|                                                   |                                                                             | RILI                                            | $M_{-} = 600 k\Omega$ | 225  | 300                    | 375   | 1     |  |

| V <sub>L</sub> REGULATOR                          |                                                                             |                                                 |                       |      |                        |       |       |  |

| Output Voltage                                    | 5.5V < V + < 23V,                                                           | 5.5V < V+ < 23V, 1mA < I <sub>LOAD</sub> < 50mA |                       | 4.75 | 5                      | 5.25  | V     |  |

| V <sub>L</sub> Undervoltage Lockout<br>Trip Level |                                                                             |                                                 |                       | 4.4  | 4.55                   | 4.7   | V     |  |

| REFERENCE                                         |                                                                             |                                                 |                       |      |                        |       | 1     |  |

| Output Voltage                                    | $I_{REF} = 0\mu A$                                                          | $I_{\text{REF}} = 0\mu A$                       |                       |      | 2.00                   | 2.02  | V     |  |

| Reference Load Regulation                         | 0μA < I <sub>REF</sub> < 50μA                                               | $0\mu A < I_{REF} < 50\mu A$                    |                       | 0    | 4                      | 10    | mV    |  |

| SOFT-START                                        | ·                                                                           |                                                 |                       | •    |                        |       |       |  |

| Digital Ramp Period                               | Internal 6-bit DAC for one converter to ramp from 0V to full scale (Note 3) |                                                 | 1024                  |      | DC-to-<br>DC<br>Clocks |       |       |  |

| Soft-Start Steps                                  |                                                                             |                                                 |                       | 64   |                        | Steps |       |  |

| FREQUENCY                                         |                                                                             |                                                 |                       |      |                        |       |       |  |

| Low End of Range                                  | $R_{OSC} = 10k\Omega$                                                       | $R_{OSC} = 10k\Omega$                           |                       |      | 600                    | 600   | kHz   |  |

| High End of Range                                 | $R_{OSC} = 5k\Omega$                                                        | $R_{OSC} = 5k\Omega$                            |                       | 1020 | 1200                   | 1380  | kHz   |  |

| DH_ Minimum Off-Time                              | $R_{OSC} = 5k\Omega$                                                        |                                                 |                       | 110  | 160                    | ns    |       |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V + = 12V, EN = ILIM_ = V_L, SYNC = GND, I_{VL} = 0mA, PGND = GND, C_{REF} = 0.22\mu$ F,  $C_{VL} = 4.7\mu$ F (ceramic),  $R_{OSC} = 10k\Omega$ , compensation components for COMP\_ are from Figure 1,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C (Note 1), unless otherwise noted.)

| PARAMETER                                                | CONDITIONS                                                                                                                 |        |      | ТҮР  | MAX  | UNITS |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------|------|------|------|-------|--|--|

| SYNC Range                                               | Internal oscillator nominal frequency must be set to half of the SYNC frequency                                            |        | 1000 |      | 2800 | kHz   |  |  |

| SYNC Input Pulse Width                                   | (Nete 2)                                                                                                                   | High   | 100  |      |      |       |  |  |

|                                                          | (Note 3)                                                                                                                   | Low    | 100  |      |      | ns    |  |  |

| SYNC Rise/Fall Time                                      | (Note 3)                                                                                                                   |        |      |      | 100  | ns    |  |  |

| ERROR AMPLIFIER                                          |                                                                                                                            |        |      |      |      |       |  |  |

| FB_ Input Bias Current                                   |                                                                                                                            |        |      |      | 250  | nA    |  |  |

| FB_ Input Voltage Set Point                              |                                                                                                                            |        | 0.99 | 1.00 | 1.01 | V     |  |  |

|                                                          | 0°C to +85°C                                                                                                               |        |      | 1.8  | 2.70 | mS    |  |  |

| FB_ to COMP_ Transconductance                            | -40°C to +85°C                                                                                                             |        |      | 1.8  | 2.9  |       |  |  |

| DRIVERS                                                  |                                                                                                                            |        |      |      |      |       |  |  |

| DL_, DH_ Break-Before-Make Time                          | $C_{LOAD} = 5nF$                                                                                                           |        |      | 30   |      | ns    |  |  |

|                                                          | Low                                                                                                                        |        |      | 1.5  | 2.5  |       |  |  |

| DH_ On-Resistance                                        | High                                                                                                                       |        |      |      | 5    | Ω     |  |  |

|                                                          | Low                                                                                                                        |        |      | 0.6  | 1.5  |       |  |  |

| DL_ On-Resistance                                        | High                                                                                                                       |        |      | 3    | 5    | Ω     |  |  |

| LOGIC INPUTS (EN, SYNC)                                  |                                                                                                                            |        |      |      |      |       |  |  |

| Input Low Level                                          | Typical 15% hysteresis, $V_L = 4.75V$                                                                                      |        |      |      | 0.8  | V     |  |  |

| Input High Level                                         | $V_L = 5.5V$                                                                                                               |        | 2.4  |      |      | V     |  |  |

| Input High/Low Bias Current                              | V <sub>EN</sub> = 0 or 5.5V                                                                                                |        | -1   | +0.1 | +1   | μA    |  |  |

| LOGIC OUTPUTS (CKO)                                      |                                                                                                                            |        |      |      |      |       |  |  |

| Output Low Level                                         | V <sub>L</sub> = 5V, sinkir                                                                                                | ng 5mA |      |      | 0.4  | V     |  |  |

| Output High Level                                        | $V_L = 5V$ , sourcing 5mA                                                                                                  |        | 4.0  |      |      | V     |  |  |

| COMP_                                                    |                                                                                                                            |        |      |      |      |       |  |  |

| Pulldown Resistance During<br>Shutdown and Current Limit |                                                                                                                            |        |      | 17   |      | Ω     |  |  |

| RST OUTPUT                                               |                                                                                                                            |        |      |      |      |       |  |  |

| Output-Voltage Trip Level                                | Both FBs must be over this to allow the reset timer to start; there is no hysteresis                                       |        | 0.87 | 0.9  | 0.93 | V     |  |  |

|                                                          | $V_L = 5V$ , sinking 3.2mA                                                                                                 |        |      |      | 0.4  |       |  |  |

| Output Low Level                                         | $V_L = 1V$ , sinking 0.4mA                                                                                                 |        |      |      | 0.3  | V     |  |  |

| Output Leakage                                           | $V_{\rm L} = 1V$ , sinking statistic<br>$V_{\rm H} = V_{\rm L} = 5V$ , $V_{\rm \overline{RST}} = 5.5V$ , $V_{\rm FB} = 1V$ |        |      |      | 1    | μA    |  |  |

| Reset Timeout Period                                     | V <sub>FB</sub> = 1V                                                                                                       |        | 140  | 315  | 560  | ms    |  |  |

| FB_ to Reset Delay                                       | FB_ overdrive from 1V to 0.85V                                                                                             |        | -    | 4    |      | μs    |  |  |

|                                                          |                                                                                                                            |        |      |      |      | μο    |  |  |

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

Note 2: Operating supply range is guaranteed by VL line regulation test. Connect V+ to VL for 5V operation.

Note 3: Guaranteed by design and not production tested.

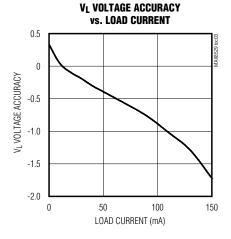

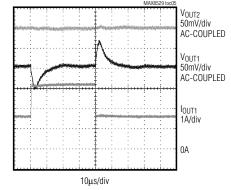

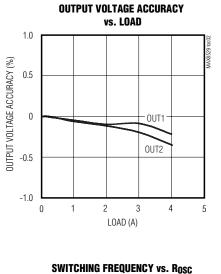

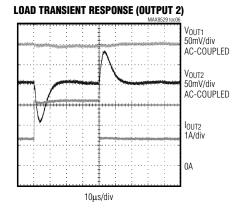

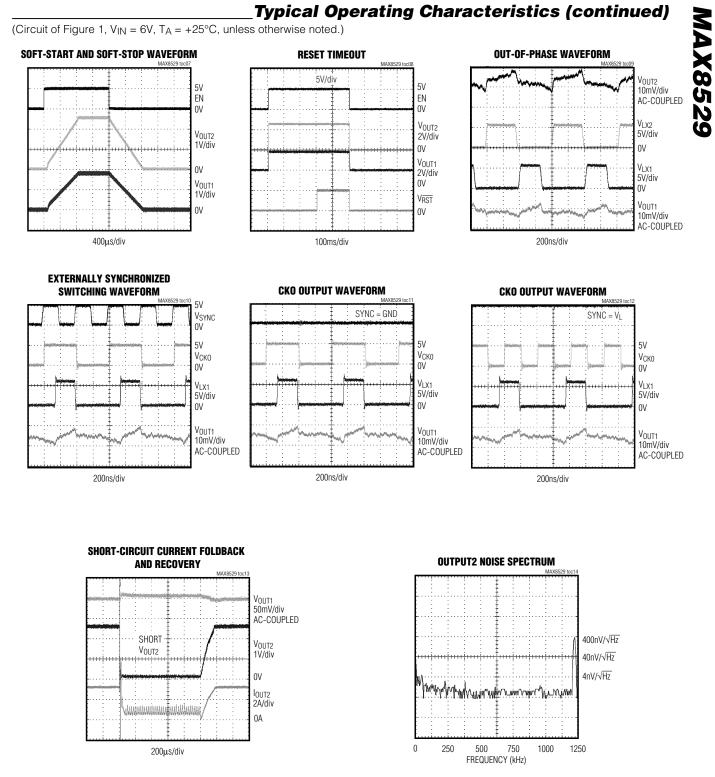

# **Typical Operating Characteristics**

$\begin{array}{c} 1600 \\ 1400 \\ 1200 \\ 1200 \\ 600 \\ 600 \\ 4 \\ 6 \\ 8 \\ 800 \\ 600 \\ 4 \\ 6 \\ 8 \\ 10 \end{array}$

M/X/W

# Pin Description

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

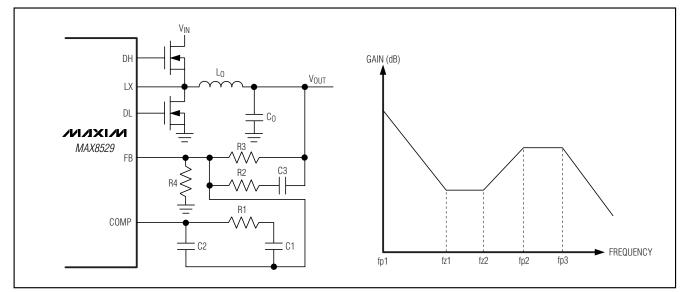

| 1   | COMP2 | Compensation Pin for Regulator 2 (REG2). Compensate REG2's control loop as shown in Figure 1.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | FB2   | Feedback Input for Regulator 2 (REG2). Connect FB2 to a resistive-divider between REG2's output and GND to adjust the output voltage between 1V and 18V. To set the output voltage below 1V, connect FB2 to a resistive voltage-divider from REF to REG2's output (see the <i>Setting the Output Voltage</i> section).                                                                                                                                                                                                     |

| 3   | ILIM2 | Current-Limit Adjustment for Regulator 2 (REG2). The PGND–LX2 current-limit threshold defaults to 100mV if ILIM2 is connected to V <sub>L</sub> . Connect a resistor (R <sub>ILIM2</sub> ) from ILIM2 to GND to adjust the REG2's current-limit threshold (V <sub>ITH2</sub> ) from 50mV (R <sub>ILIM2</sub> = 100k $\Omega$ ) to 300mV (R <sub>ILIM2</sub> = 600k $\Omega$ ) (see the Setting the Valley Current Limit section).                                                                                          |

| 4   | OSC   | Oscillator Frequency Set Input. The controller generates the clock signal by dividing down the oscillator, so the switching frequency equals half the synchronization frequency ( $f_{SW} = f_{OSC} / 2$ ). Connect a resistor from OSC to GND ( $R_{OSC}$ ) to set the switching frequency from 600kHz ( $R_{OSC} = 10k\Omega$ ) to 1500kHz ( $R_{OSC} = 4k\Omega$ ). The controller still requires $R_{OSC}$ when an external clock is connected to SYNC. When using SYNC, set $R_{OSC}$ for one half of the SYNC input. |

| 5   | V+    | Input Supply Voltage (4.75V to 23V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6   | REF   | 2V Reference Output. Bypass to GND with a 0.22µF or greater ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7   | GND   | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8   | СКО   | Clock Output. Clock Output for external 2- or 4-phase synchronization (see the <i>Clock Synchronization</i> ( <i>SYNC, CKO</i> ) section).                                                                                                                                                                                                                                                                                                                                                                                 |

| 9   | SYNC  | Synchronization Input or Clock Output Selection Input. SYNC has three operating modes. Connect SYNC to a 1200kHz to 2800kHz clock for external synchronization. Connect SYNC to GND for 2-phase operation as a master controller. Connect SYNC to V <sub>L</sub> for 4-phase operation as a master controller (see the <i>Clock Synchronization (SYNC, CKO)</i> section).                                                                                                                                                  |

| 10  | ILIM1 | Current-Limit Adjustment for Regulator 1 (REG1). The PGND–LX1 current-limit threshold defaults to 100mV if ILIM1 is connected to V <sub>L</sub> . Connect a resistor (R <sub>ILIM1</sub> ) from ILIM1 to GND to adjust REG1's current-limit threshold (V <sub>ITH1</sub> ) from 50mV (R <sub>ILIM1</sub> = 100k $\Omega$ ) to 300mV (R <sub>ILIM1</sub> = 600k $\Omega$ ) (see the <i>Setting the Valley Current Limit</i> section).                                                                                       |

| 11  | FB1   | Feedback Input for Regulator 1 (REG1). Connect FB1 to a resistive-divider between REG1's output and GND to adjust the output voltage between 1V and 18V. To set the output voltage below 1V, connect FB1 to a resistive voltage-divider from REF and REG1's output (see the <i>Setting the Output Voltage</i> section).                                                                                                                                                                                                    |

| 12  | COMP1 | Compensation Pin for Regulator 1 (REG1). Compensate REG1's control loop as shown in Figure 1.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13  | RST   | Open-Drain Reset Output. $\overline{\text{RST}}$ is low when either output voltage is more than 10% below its regulation point. After soft-start is completed and both outputs exceed 90% of their nominal output voltage (V <sub>FB</sub> > 0.9V), $\overline{\text{RST}}$ becomes high impedance after a 140ms delay and remains high impedance as long as both outputs maintain regulation. Connect a resistor between $\overline{\text{RST}}$ and the logic supply for logic-level voltages.                           |

# Pin Description (continued)

| PIN | NAME | FUNCTION                                                                                                                                                                      |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | DH1  | High-Side Gate Driver Output for Regulator 1 (REG1). DH1 swings from LX1 to BST1.                                                                                             |

| 15  | LX1  | External Inductor Connection for Regulator 1 (REG1). Connect LX1 to the switched side of the inductor. LX1 serves as the lower supply rail for the DH1 high-side gate driver. |

| 16  | BST1 | Boost Flying-Capacitor Connection for Regulator 1 (REG1). Connect BST1 to an external ceramic capacitor and diode according to Figure 1.                                      |

| 17  | DL1  | Low-Side Gate-Driver Output for Regulator 1 (REG1). DL1 swings from PGND to VL.                                                                                               |

| 18  | PGND | Power Ground                                                                                                                                                                  |

| 19  | VL   | Internal 5V Linear-Regulator Output. Supplies the regulators and powers the low-side gate drivers and external boost circuitry for the high-side gate drivers.                |

| 20  | DL2  | Low-Side Gate-Driver Output for Regulator 2 (REG2). DL2 swings from PGND to $V_L$ .                                                                                           |

| 21  | BST2 | Boost Flying-Capacitor Connection for Regulator 2 (REG2). Connect BST2 to an external ceramic capacitor and diode according to Figure 1.                                      |

| 22  | LX2  | External Inductor Connection for Regulator 2 (REG2). Connect LX2 to the switched side of the inductor. LX2 serves as the lower supply rail for the DH2 high-side gate driver. |

| 23  | DH2  | High-Side Gate-Driver Output for Regulator 2 (REG2). DH2 swings from LX2 to BST2.                                                                                             |

| 24  | EN   | Active-High Enable Input. A logic low shuts down both controllers. Connect to $V_{\mbox{\scriptsize L}}$ for always-on operation.                                             |

# **Detailed Description**

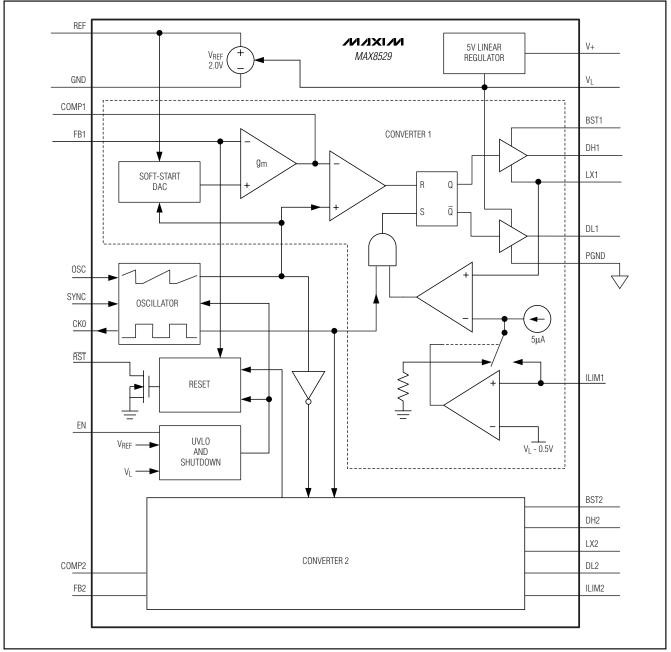

# **DC-to-DC PWM Controller**

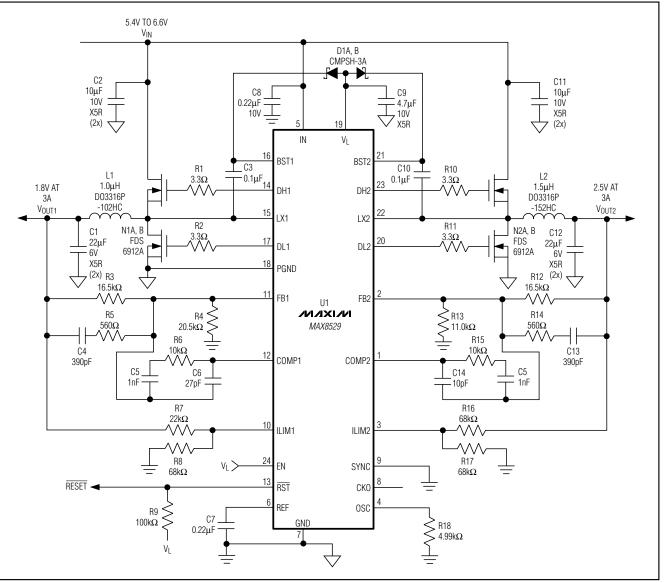

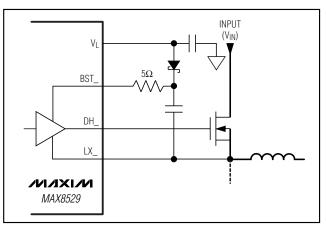

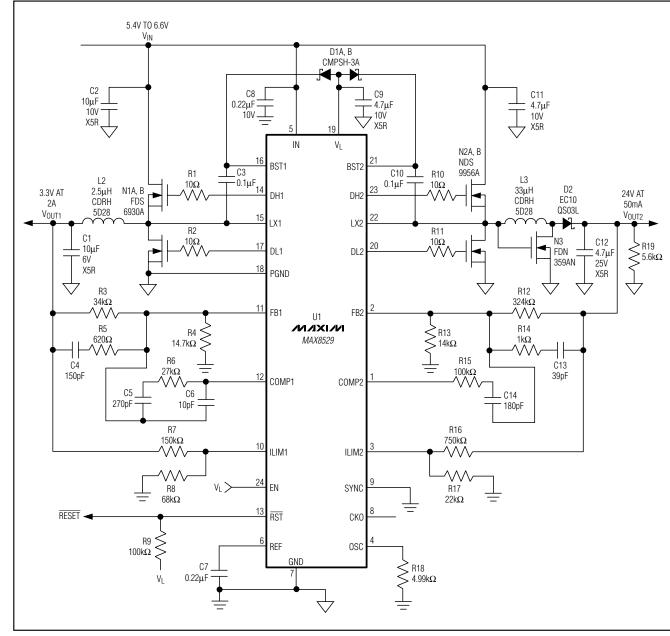

The MAX8529 step-down converter uses a PWM voltage-mode control scheme (Figure 2) for each out-ofphase controller. The controller generates the clock signal by dividing down the internal oscillator or SYNC input when driven by an external clock, so each controller's switching frequency equals half the oscillator frequency ( $f_{SW} = f_{OSC} / 2$ ). An internal transconductance error amplifier produces an integrated error voltage at the COMP pin, providing high DC accuracy. The voltage at COMP sets the duty cycle using a PWM comparator and a ramp generator. At each rising edge of the clock, REG1's high-side N-channel MOSFET turns on and remains on until either the appropriate duty cycle or until the maximum duty cycle is reached. REG2 operates outof-phase, so the second high-side MOSFET turns on at each falling edge of the clock. During each high-side MOSFET's on-time, the associated inductor current ramps up.

During the second-half of the switching cycle, the highside MOSFET turns off and the low-side N-channel MOSFET turns on. Now the inductor releases the stored energy as its current ramps down, providing current to the output. Under overload conditions, when the inductor current exceeds the selected valley current limit (see the *Current-Limit Circuit (ILIM\_)* section), the highside MOSFET does not turn on at the appropriate clock edge and the low-side MOSFET remains on to let the inductor current ramp down.

# Synchronized Out-of-Phase Operation

The two independent regulators in the MAX8529 operate 180 degrees out-of-phase to reduce input filtering requirements, reduce electromagnetic interference (EMI), and improve efficiency. This effectively lowers component cost and saves board space, making the MAX8529 ideal for cost-sensitive applications.

Dual-switching regulators typically operate both controllers in-phase, and turn on both high-side MOSFETs at the same time. The input capacitor must then support the instantaneous current requirements of both controllers simultaneously, resulting in increased ripple voltage and current when compared to a single switching regulator. The higher RMS ripple current lowers efficiency due to power loss associated with the input capacitor's effective series resistance (ESR). This typically requires more low-ESR input capacitors in parallel to minimize input voltage ripple and ESR-related losses, or to meet the necessary ripple-current rating.

**MAX8529**

Figure 1. Standard Application Circuit

With dual synchronized out-of-phase operation, the MAX8529's high-side MOSFETs turn on 180 degrees outof-phase. The instantaneous input current peaks of both regulators no longer overlap, resulting in reduced RMS ripple current and input voltage ripple. This reduces the required input capacitor ripple-current rating, allowing fewer or less expensive capacitors, and reduces shielding requirements for EMI. The out-of-phase waveforms in the *Typical Operating Characteristics* demonstrate synchronized 180-degree out-of-phase operation.

# Internal 5V Linear Regulator (VL)

All MAX8529 functions are internally powered from an on-chip, low-dropout 5V regulator. The maximum regulator input voltage (V+) is 23V. Bypass the regulator's output (V<sub>L</sub>) with a 4.7µF ceramic capacitor to PGND. The V<sub>L</sub> dropout voltage is typically 500mV, so when V+ is greater than 5.5V, V<sub>L</sub> is typically 5V. The MAX8529 also employs an undervoltage lockout circuit that disables both regulators when V<sub>L</sub> falls below 4.5V.

Figure 2. Functional Diagram

The internal V<sub>L</sub> linear regulator can source over 50mA to supply the IC, power the low-side gate driver, charge the external boost capacitor, and supply small external loads. When driving large FETs, little or no regulator current may be available for external loads.

For example, when switched at 600kHz, a single large FET with 18nC total gate charge requires  $18nC \times 600kHz = 11mA$ . To drive larger MOSFETs, or deliver larger loads, connect V<sub>L</sub> to an external power supply from 4.75V to 5.5V.

**MAX8529**

### High-Side Gate-Drive Supply (BST\_)

Gate-drive voltages for the high-side N-channel switches are generated by the flying-capacitor boost circuits (Figure 3). A boost capacitor (connected from BST\_ to LX\_) provides power to the high-side MOSFET driver. On startup, the synchronous rectifier (low-side MOSFET) forces LX\_ to ground and charges the boost capacitor to 5V. On the second half-cycle, after the low-side MOSFET turns off, the high-side MOSFET is turned on by closing an internal switch between BST\_ and DH\_. This provides the necessary gate-to-source voltage to turn on the high-side switch, an action that boosts the 5V gate-drive signal above VIN. The current required to drive the high-side MOSFET gates (fSWITCH  $\times$  QG) is ultimately drawn from VI.

### MOSFET Gate Drivers (DH\_, DL\_)

The DH and DL drivers are optimized for driving moderate-size N-channel high-side and larger low-side power MOSFETs. This is consistent with the low duty factor seen with a large VIN - VOUT differential. The DL\_ low-side drive waveform is always the complement of the DH\_ high-side drive waveform (with controlled dead time to prevent cross-conduction or "shoot-through"). An adaptive dead-time circuit monitors the DL\_ output and prevents the high-side FET from turning on until DL\_ is fully off. There must be a low-resistance, lowinductance path from the DL\_ driver to the MOSFET gate in order for the adaptive dead-time circuit to work properly. Otherwise, the sense circuitry in the MAX8529 interprets the MOSFET gate as "off" while there is actually charge still left on the gate. Use very short, wide traces (50mils to 100mils wide if the MOSFET is 1in from the device). The dead time at the DH off edge is determined by a fixed 30ns internal delay.

Synchronous rectification reduces conduction losses in the rectifier by replacing the normal low-side Schottky catch diode with a low-resistance MOSFET switch. Additionally, the MAX8529 uses the synchronous rectifier to ensure proper startup of the boost gate-driver circuit and to provide the current-limit signal.

The internal pulldown transistor that drives DL\_ low is robust, with a  $0.5\Omega$  (typ) on-resistance. This low onresistance helps prevent DL\_ from being pulled up during the fast rise-time of the LX\_ node, due to capacitive coupling from the drain to the gate of the low-side synchronous-rectifier MOSFET. However, for high-current applications, some combinations of high- and low-side FETs can cause excessive gate-drain coupling, leading to poor efficiency, EMI, and shoot-through currents. This can be remedied by adding a resistor (typically less than  $5\Omega$ ) in series with BST\_, which increases the turn-on time of the high-side FET without degrading the turn-off time (Figure 3).

### Current-Limit Circuit (ILIM\_)

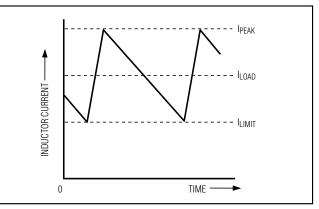

The current-limit circuit employs a "valley" current-sensing algorithm that uses the on-resistance of the low-side MOSFET as a current-sensing element. If the currentsense signal is above the current-limit threshold, the MAX8529 does not initiate a new cycle (Figure 4). Since valley current sensing is employed, the actual peak current is greater than the current-limit threshold by an amount equal to the inductor ripple current. Therefore, the exact current-limit characteristic and maximum load capability are a function of the low-side MOSFET's onresistance, current-limit threshold, inductor value, and input voltage. The reward for this uncertainty is robust, lossless overcurrent sensing that does not require costly sense resistors.

The adjustable current limit accommodates MOSFETs with a wide range of on-resistance characteristics (see the *Design Procedure* section). The current-limit threshold is adjusted with an external resistor at ILIM\_(Figure 1). The adjustment range is from 50mV to 300mV, corresponding to resistor values of  $100k\Omega$  to

Figure 3. Reducing the Switching-Node Rise Time

Figure 4. "Valley" Current-Limit Threshold Point

600k $\Omega$ . In adjustable mode, the current-limit threshold across the low-side MOSFET is precisely 1/10th the voltage seen at ILIM\_. However, the current-limit threshold defaults to 100mV when ILIM is connected to V<sub>L</sub>. The logic threshold for switchover to this 100mV default value is approximately V<sub>L</sub> - 0.5V.

Adjustable foldback current limit reduces power dissipation during short-circuit conditions (see the *Design Procedure* section).

Carefully observe the PC board layout guidelines to ensure that noise and DC errors do not corrupt the current-sense signals seen by LX\_ and PGND. The IC must be mounted close to the low-side MOSFET with short direct traces making a Kelvin sense connection so that trace resistance does not add to the intended sense resistance of the low-side MOSFET.

## **Undervoltage Lockout and Startup**

If V<sub>L</sub> drops below 4.5V, the MAX8529 assumes that the supply and reference voltages are too low to make valid decisions and activates the undervoltage lockout (UVLO) circuitry, which forces DH low and DL high to inhibit switching. RST is also forced low during UVLO. After V<sub>L</sub> rises above 4.5V, the controller powers up the outputs.

### Enable (EN), Soft-Start, and Soft-Stop

Pull EN high to enable or low to shut down both regulators. During shutdown the supply current drops to 1mA (max), LX enters a high-impedance state (DH\_ connected to LX\_, and DL\_ connected to PGND), and COMP\_ is discharged to GND through a 17 $\Omega$  resistor. V<sub>L</sub> and REF remain active in shutdown. For "always-on" operation, connect EN to V<sub>L</sub>.

On the rising edge of EN both controllers enter softstart. Soft-start gradually ramps up to the reference voltage seen by the error amplifier in order to control the outputs' rate of rise and reduce input surge currents during startup. The soft-start period is 1024 clock cycles (1024/fsw), and the internal soft-start DAC ramps up the voltage in 64 steps. The output reaches regulation when soft-start is completed. On the falling edge of EN both controllers simultaneously enter softstop, which reverses the soft-start ramp. The part enters shutdown after soft-stop is complete.

### **Reset Output**

RST is an open-drain output. RST pulls low when either output falls below 90% of its nominal regulation voltage. Once both outputs exceed 90% of their nominal regulation voltages and both soft-start cycles are completed, RST goes high impedance. To obtain a logic-voltage output, connect a pullup resistor from RST to the logic supply voltage. A 100k $\Omega$  resistor works well for most applications. If unused, leave  $\overline{\text{RST}}$  grounded or unconnected.

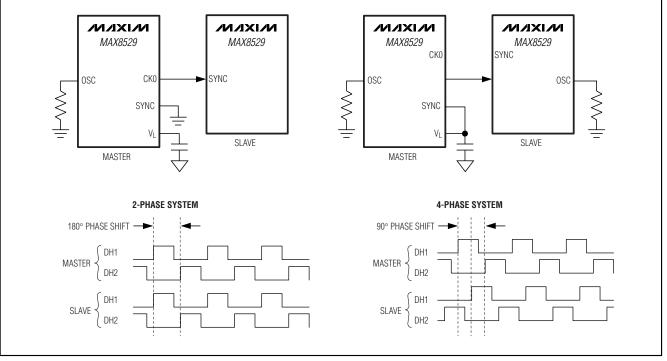

## **Clock Synchronization (SYNC, CKO)**

SYNC serves two functions: SYNC selects the clock output (CKO) type used to synchronize slave controllers, or it serves as a clock input so the MAX8529 can be synchronized with an external clock signal. This allows the MAX8529 to function as either a master or slave. CKO provides a clock signal synchronized to the MAX8529's switching frequency, allowing either inphase (SYNC = GND) or 90-degrees out-of-phase (SYNC = V<sub>L</sub>) synchronization of additional DC-to-DC controllers (Figure 5). The MAX8529 supports the following three operating modes:

- **SYNC = GND:** The CKO output frequency equals REG1's switching frequency ( $f_{CKO} = f_{DH1}$ ) and the CKO signal is in phase with REG1's switching frequency. This provides 2-phase operation when synchronized with a second slave controller.

- SYNC = VL: The CKO output frequency equals two times REG1's switching frequency (fCKO = 2fDH1) and the CKO signal is phase shifted by 90 degrees with respect to REG1's switching frequency. This provides 4-phase operation when synchronized with a second MAX8529 (slave controller).

- SYNC Driven by External Oscillator: The controller generates the clock signal by dividing down the SYNC input signal, so that the switching frequency equals half the synchronization frequency (fsw =  $f_{SYNC} / 2$ ). REG1's conversion cycles initiate on the rising edge of the internal clock signal. The CKO output frequency and phase match REG1's switching frequency (fCKO =  $f_{DH1}$ ) and the CKO signal is in phase. Note that the MAX8529 still requires ROSC when SYNC is externally clocked and the internal oscillator frequency should be set to 50% of the synchronization frequency ( $f_{OSC} = 0.5 f_{SYNC}$ ).

### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the MAX8529. When the device's die junction temperature exceeds  $T_J = +160^{\circ}$ C, an on-chip thermal sensor shuts down the device, forcing DL\_ and DH\_ low, allowing the IC to cool. The thermal sensor turns the part on again after the junction temperature cools by 10°C. During thermal shutdown, the regulators shut down, RST goes low, and soft-start is reset. If the V<sub>L</sub> linear-regulator output is short-circuited, thermal-overload protection is triggered.

Figure 5. Synchronized Controllers

# \_Design Procedure

# **Effective Input Voltage Range**

Although the MAX8529 controllers can operate from input supplies ranging from 4.75V to 23V, the input voltage range can be effectively limited by the MAX8529's duty-cycle limitations. The maximum input voltage is limited by the minimum on-time (ton(MIN)):

$$V_{\text{IN(MAX)}} \leq \frac{V_{\text{OUT}}}{t_{\text{ON(MIN)}} f_{\text{SW}}}$$

where  $t_{ON(MIN)}$  is 100ns. The minimum input voltage is limited by the maximum duty cycle ( $D_{MAX} = 0.875$ ):

$$V_{\text{IN(MIN)}} = \left[\frac{V_{\text{OUT}} + V_{\text{DROP1}}}{0.875}\right] + V_{\text{DROP2}} - V_{\text{DROF}}$$

where V<sub>DROP1</sub> is the sum of the parasitic voltage drops in the inductor discharge path, including synchronous rectifier, inductor, and PC board resistances. V<sub>DROP2</sub> is the sum of the resistances in the charging path, including high-side switch, inductor, and PC board resistances.

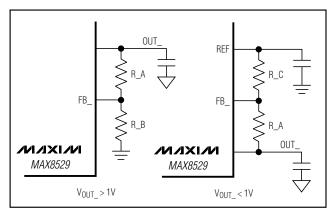

# **Setting the Output Voltage**

For 1V or greater output voltages, set the MAX8529 output voltage by connecting a voltage-divider from the output to FB\_ to GND (Figure 6). Select R\_B (FB\_ to GND resistor) to between 1k $\Omega$  and 10k $\Omega$ . Calculate R\_A (OUT\_ to FB\_ resistor) with the following equation:

$$R_A = R_B \left[ \left( \frac{V_{OUT}}{V_{SET}} \right) - 1 \right]$$

where  $V_{SET} = 1V$  (see the *Electrical Characteristics*) and  $V_{OUT}$  can range from  $V_{SET}$  to 18V.

For output voltages below 1V, set the MAX8529 output voltage by connecting a voltage-divider from the output to FB\_ to REF (Figure 6). Select R\_C (FB to REF resistor) in the 1k $\Omega$  to 10k $\Omega$  range. Calculate R\_A with the following equation:

$$R_A = R_C \left( \frac{V_{SET} - V_{OUT}}{V_{REF} - V_{SET}} \right)$$

where  $V_{SET} = 1V$ ,  $V_{REF} = 2V$  (see the *Electrical Characteristics*), and  $V_{OUT}$  can range from 0 to  $V_{SET}$ .

Figure 6. Adjustable Output Voltage

### **Setting the Switching Frequency**

The controller generates the clock signal by dividing down the internal oscillator or SYNC input signal when driven by an external oscillator, so the switching frequency equals half the oscillator frequency (fsw =  $f_{OSC}/2$ ). The internal oscillator frequency is set by a resistor (R<sub>OSC</sub>) connected from OSC to GND. The relationship between fsw and R<sub>OSC</sub> is:

$$R_{OSC} = \frac{6 \times 10^9 \frac{\Omega - Hz}{S}}{f_{SW}}$$

where f<sub>SW</sub> is in Hz, f<sub>OSC</sub> is in Hz, and R<sub>OSC</sub> is in  $\Omega$ . For example, a 600kHz switching frequency is set with R<sub>OSC</sub> = 10k $\Omega$ . Higher frequencies allow designs with lower inductor values and less output capacitance. Consequently, peak currents and I<sup>2</sup>R losses are lower at higher switching frequencies, but core losses, gatecharge currents, and switching losses increase.

A rising clock edge on SYNC is interpreted as a synchronization input. If the SYNC signal is lost, the internal oscillator takes control of the switching rate, returning the switching frequency to that set by Rosc. This maintains output regulation even with intermittent SYNC signals. When an external synchronization signal is used, Rosc should set the switching frequency to one half SYNC rate (f<sub>SYNC</sub>).

### **Inductor Selection**

Three key inductor parameters must be specified for operation with the MAX8529: inductance value (L), peak-inductor current (IPEAK), and DC resistance (R<sub>DC</sub>). The following equation assumes a constant ratio of inductor peak-to-peak AC current to DC average current (LIR). For LIR values too high, the RMS currents are

high, and therefore I<sup>2</sup>R losses are high. Large inductances must be used to achieve very low LIR values. Typically inductance is proportional to resistance (for a given package type), which again makes I<sup>2</sup>R losses high for very low LIR values. A good compromise between size and loss is a 30% peak-to-peak ripple current to average-current ratio (LIR = 0.3). The switching frequency, input voltage, output voltage, and selected LIR determine the inductor value as follows:

$$L = \frac{V_{OUT}(V_{IN} - V_{OUT})}{V_{IN}f_{SW}I_{OUT}LIR}$$

where V<sub>IN</sub>, V<sub>OUT</sub>, and I<sub>OUT</sub> are typical values (so that efficiency is optimum for typical conditions). The switching frequency is set by R<sub>OSC</sub> (see the *Setting the Switching Frequency* section). The exact inductor value is not critical and can be adjusted in order to make trade-offs among size, cost, and efficiency. Lower inductor values minimize size and cost, but also improve transient response and reduce efficiency due to higher peak currents. On the other hand, higher inductance increases efficiency by reducing the RMS current. However, resistive losses due to extra wire turns can exceed the benefit gained from lower AC current levels, especially when the inductance is increased without also allowing larger inductor dimensions.

Find a low-loss inductor having the lowest possible DC resistance that fits in the allotted dimensions. The inductor's saturation rating must exceed the peak-inductor current at the maximum defined load current (ILOAD(MAX)):

$$I_{PEAK} = I_{LOAD(MAX)} + \left(\frac{LIR}{2}\right)I_{LOAD(MAX)}$$

### **Setting the Valley Current Limit**

The minimum current-limit threshold must be high enough to support the maximum expected load current with the worst-case low-side MOSFET on-resistance value since the low-side MOSFET's on-resistance is used as the current-sense element. The inductor's valley current occurs at I<sub>LOAD</sub>(MAX) minus half of the ripple current. The current-sense threshold voltage (VITH) should be greater than the voltage on the low-side MOS-FET during the ripple-current valley:

$$V_{\text{ITH}} > R_{\text{DS(ON,MAX)}} \times I_{\text{LOAD(MAX)}} \times \left(1 - \frac{\text{LIR}}{2}\right)$$

where  $R_{DS(ON)}$  is the on-resistance of the low-side MOSFET (NL). Use the maximum value for  $R_{DS(ON)}$

from the low-side MOSFET's data sheet, an additional margin to account for RDS(ON) rise with temperature is also recommended. A good general rule is to allow 0.5% additional resistance for each °C of the MOSFET junction temperature rise.

Connect ILIM\_ to V<sub>L</sub> for the default 100mV (typ) currentlimit threshold. For an adjustable threshold, connect a resistor (R<sub>ILIM</sub>) from ILIM\_ to GND. The relationship between the current-limit threshold (V<sub>ITH</sub>) and R<sub>ILIM</sub> is:

$$\mathsf{R}_{\mathsf{ILIM}} = \frac{\mathsf{V}_{\mathsf{ITH}}}{0.5\mu\mathsf{A}}$$

where  $R_{ILIM}$  is in  $\Omega$  and  $V_{ITH}$  is in V.

An R<sub>ILIM</sub> resistance range of 100k $\Omega$  to 600k $\Omega$  corresponds to a current-limit threshold of 50mV to 300mV. When adjusting the current limit, 1% tolerance resistors minimize error in the current-limit threshold.

For foldback current limit, a resistor ( $R_{FBI}$ ) is added from ILIM pin to output. The value of  $R_{ILIM}$  and  $R_{FBI}$  can then be calculated as follows:

First select the percentage of foldback,  $\mathsf{P}_{\mathsf{FB}}$ , from 15% to 30%, then:

$$R_{FBI} = \frac{P_{FB} \times V_{OUT}}{5 \times 10^{-6} (1 - P_{FB})}$$

and

$$R_{ILIM} = \frac{10 \times V_{ITH}(1 - P_{FB}) \times R_{FBI}}{\left[V_{OUT} - 10 \times V_{ITH}(1 - P_{FB})\right]}$$

### **Input Capacitor**

The input filter capacitor reduces peak currents drawn from the power source and reduces noise and voltage ripple on the input caused by the circuit's switching. The input capacitor must meet the ripple current requirement (I<sub>RMS</sub>) imposed by the switching currents as defined by the following equation:

$$I_{\text{RMS}} = I_{\text{LOAD}} \frac{\sqrt{V_{\text{OUT}}(V_{\text{IN}} - V_{\text{OUT}})}}{V_{\text{IN}}}$$

IRMS has a maximum value when the input voltage equals twice the output voltage (VIN =  $2V_{OUT}$ ), so IRMS(MAX) = I<sub>LOAD</sub> / 2. For most applications, nontantalum capacitors (ceramic, aluminum, polymer, or OS-CON) are preferred at the input due to their robustness with high inrush currents typical of systems that can be powered from very low impedance sources. Additionally, two (or more) smaller-value low-ESR capacitors can be connected in parallel for lower cost. Choose an input capacitor that

exhibits less than 10°C temperature rise at the RMS input current for optimal long-term reliability.

### **Output Capacitor**

The key selection parameters for the output capacitor are capacitance value, ESR, and voltage rating. These parameters affect the overall stability, output ripple voltage, and transient response. The output ripple has two components: variations in the charge stored in the output capacitor, and the voltage drop across the capacitor's ESR caused by the current flowing into and out of the capacitor:

$$V_{RIPPLE} \cong V_{RIPPLE(ESR)} + V_{RIPPLE(C)}$$

The output voltage ripple as a consequence of the ESR and output capacitance is:

$$V_{\text{RIPPLE(ESR)}} = I_{\text{P-P}}R_{\text{ESR}}$$

$$V_{\text{RIPPLE(C)}} = \frac{I_{\text{P-P}}}{8C_{\text{OUT}}f_{\text{SW}}}$$

$$I_{\text{P-P}} = \left(\frac{V_{\text{IN}} - V_{\text{OUT}}}{f_{\text{SW}}L}\right) \left(\frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

where IP-P is the peak-to-peak inductor current (see the *Inductor Selection* section). These equations are suitable for initial capacitor selection, but final values should be verified by testing in a prototype or evaluation circuit.

As a general rule, a smaller inductor ripple current results in less output ripple voltage. Since inductor ripple current depends on the inductor value and input voltage, the output ripple voltage decreases with larger inductance and increases with higher input voltages. However, the inductor ripple current also impacts transient-response performance, especially at low V<sub>IN</sub> - V<sub>OUT</sub> differentials. Low inductor values allow the inductor current to slew faster, replenishing charge removed from the output filter capacitors by a sudden load step. The amount of output-voltage sag is also a function of the maximum duty factor, which can be calculated from the minimum off-time and switching frequency:

$$V_{SAG} = \frac{L(I_{LOAD1} - I_{LOAD2})^{2} \left[ \left( \frac{V_{OUT}}{V_{IN} f_{SW}} \right) + t_{OFF(MIN)} \right]}{2C_{OUT} V_{OUT} \left[ \left( \frac{V_{IN} - V_{OUT}}{V_{IN} f_{SW}} \right) - t_{OFF(MIN)} \right]}$$

where t<sub>OFF(MIN)</sub> is the minimum off-time (see the *Electrical Characteristics*), and f<sub>SW</sub> is set by R<sub>OSC</sub> (see the *Setting the Switching Frequency* section).

### Compensation

The high switching frequency range of the MAX8529 allows the use of ceramic output capacitors. Since the ESR of ceramic capacitors is typically very low, the frequency of the associated transfer function zero is higher than the unity-gain crossover frequency and the zero cannot be used to compensate for the double pole created by the output inductor and capacitor. The solution is Type 3 compensation which takes advantage of local feedback to create two zeros and three poles (Figure 7). The frequency of the poles and zeros are described below:

$$f_{P1} = 0$$

$$f_{P2} = \frac{1}{2\pi \times R2 \times C3}$$

$$f_{P3} = \frac{1}{2\pi \times R1 \times \frac{(C1 \times C2)}{(C1 + C2)}}$$

$$f_{LC} = \frac{1}{2\pi \sqrt{L_O \times C_O}}$$

$$f_{Z1} = \frac{1}{2\pi \times R1 \times C1}$$

$$f_{Z2} = \frac{1}{2\pi \times (R2 + R3) \times C3}$$

$$f_{ZESR} = \frac{1}{2\pi \times R_{ESR} \times C_O}$$

Unity-gain crossover frequency:

$$f_{0} = R1 \times C3 \times \frac{V_{VIN,MAX}}{V_{OSC}} \times \frac{1}{2\pi \times L_{O} \times C_{O}}$$

where:

VIN,MAX = Maximum input voltage

V<sub>OSC</sub> = Oscillator ramp voltage = 1V

L<sub>O</sub> = Output inductance

C<sub>O</sub> = Output capacitance

The goal is to place the two zeros below crossover and the two poles above crossover so that crossover occurs with a single-pole slope. The compensation procedure is as follows:

1) Select the crossover frequency such that:

$$f_0 < f_{ZESR}$$

and  $f_0 < \frac{1}{5} \times f_S$

f<sub>S</sub> = switching frequency

2) Select R1 such that:

$$R1 > \frac{2}{g_m}$$

3) Place the first zero before the double pole:

$$C1 \ge \frac{1}{2\pi \times (0.75) \times f_{LC} \times R1}$$

Figure 7. Compensation Network and Asymptotic Transfer Function

MIXIM

# MAX8529

4) Place the third pole at 1/2 the switching frequency.

1.5MHz Dual 180° Out-of-Phase

**PWM Step-Down Controller with POR**

$$C2 \leq \frac{1}{2\pi \times (0.5) \times f_{\rm S} \times R1}$$

C2 < 10pF can be omitted.

5) C3

$$\leq \frac{2\pi \times f_0 \times L_0 \times C_0}{R1} \times \frac{V_{OSC}}{V_{IN}}$$

6) Place the second pole afer the ESR zero:

$$R2 \leq \frac{1}{2\pi \times f_{ZESR} \times C3}$$

If R2 <  $\frac{1}{g_m}$  (=550 $\Omega$ ), increase R1 and go back to step 2.

u siep z.

7) Place the second zero at the double pole frequency:

$$R3 \geq \frac{1}{2\pi \times f_{LC} \times C3} - R2$$

8) Set the output voltage:

$$R4 = \frac{V_{FB}}{V_{OUT} - V_{FB}} \times R3, V_{FB} = 1V$$

# **MOSFET Selection**

The MAX8529's step-down controller drives two external logic-level N-channel MOSFETs as the circuit switch elements. The key selection parameters are:

- On-resistance (R<sub>DS(ON)</sub>)

- Maximum drain-to-source voltage (V<sub>DS(MAX)</sub>)

- Minimum threshold voltage (V<sub>TH(MIN)</sub>)

- Total gate charge (Qg)

- Reverse transfer capacitance (CRSS)

- Power dissipation

All four N-channel MOSFETs must be a logic-level type with guaranteed on-resistance specifications at  $V_{GS} \ge 4.5V$ . For maximum efficiency, choose a high-side MOSFET (N<sub>H</sub>) that has conduction losses equal to the switching losses at the optimum input voltage. Check to ensure that the conduction losses at minimum input voltage do not exceed MOSFET package thermal limits, or violate the overall thermal budget. Also, check to ensure that the conduction losses plus switching losses at the maximum input voltage do not exceed package ratings or violate the overall thermal budget.

Ensure that the MAX8529 DL\_ gate drivers can drive NL\_. In particular, check that the dv/dt caused by NH\_ turning on does not pull up the NL\_ gate through NL\_'s drain-to-gate capacitance. This is the most frequent cause of cross-conduction problems.

Gate-charge losses are dissipated by the driver and do not heat the MOSFET. All MOSFETs must be selected so that their total gate charge is low enough that  $V_L$  can power all four drivers without overheating the IC:

$$P_{VL} = V_{IN} \times Q_{G_{TOTAL}} \times f_{SW}$$

MOSFET package power dissipation often becomes a dominant design factor. I<sup>2</sup>R power losses are the greatest heat contributor for both high-side and low-side MOSFETs. I<sup>2</sup>R losses are distributed between N<sub>H</sub>\_ and N<sub>L</sub>\_ according to duty factor as shown in the equations below. Switching losses affect only the high-side MOSFET, since the low-side MOSFET is a zero-voltage switched device when used in the buck topology.

Calculate MOSFET temperature rise according to package thermal-resistance specifications to ensure that both MOSFETs are within their maximum junction temperature at high ambient temperature. The worst-case dissipation for the high-side MOSFET ( $P_{NH}$ ) occurs at both extremes of input voltage, and the worst-case dissipation for the low-side MOSFET ( $P_{NL}$ ) occurs at maximum input voltage.

$$P_{NH(SWITCHING)} = \frac{V_{IN}I_{LOAD}f_{OSC}}{2} \left( \frac{Q_{GS} + Q_{GD}}{I_{GATE}} \right)$$

$\mathsf{I}_{\mathsf{GATE}}$  is the average DH driver output current capability determined by:

$$I_{GATE} = \frac{V_L}{2(R_{DS(ON)DH} + R_{GATE})}$$

where RDS(ON)DH is the high-side MOSFET driver's onresistance (5 $\Omega$  max), and RGATE is any series resistance between DH and BST (Figure 3).

$$P_{NH}(CONDUCTION) = I_{LOAD}^2 R_{DS}(ON)NH\left(\frac{V_{OUT}}{V_{IN}}\right)$$

$P_{NH(TOTAL)} = P_{NH(SWITCHING)} + P_{NH(CONDUCTION)}$

$$P_{NL} = I_{LOAD}^{2}R_{DS(ON)NL}\left(1 - \left(\frac{V_{OUT}}{V_{IN}}\right)\right)$$

where  $\mathsf{P}_{\mathsf{NH}(\mathsf{CONDUCTION})}$  is the conduction power loss in the high-side MOSFET, and  $\mathsf{P}_{\mathsf{NL}}$  is the total low-side power loss.

To reduce EMI caused by switching noise, add a  $0.1\mu$ F ceramic capacitor from the high-side switch drain to the low-side switch source or add resistors in series with DL\_ and DH\_ to increase the MOSFETs' turn-on and turn-off times.

# **Applications Information**

### **Independent Shutdown**

The two controllers in the MAX8529 can be shut down independently by pulling COMP to ground. DH is forced low and DL is forced high to inhibit switching. Digital soft-stop is not active when using this method for shutdown and the output voltage can go negative. Use a Schottky clamp diode to limit the negative swing of the output voltage.

When COMP is released, DH and DL resume switching. In this mode, digital soft-start is not active and the inrush current is limited by the foldback current limit.

### **Dropout Performance**

When working with low input voltages, the output voltage adjustable range for continuous-conduction operation is restricted by the minimum off-time (toFF(MIN)). For best dropout performance, use the lowest (600kHz) switching-frequency setting. Manufacturing tolerances and internal propagation delays introduce an error to the switching frequency and minimum off-time specifications. This error is more significant at higher frequencies. Also, keep in mind that transient response performance of buck regulators operated close to dropout is poor, and bulk output capacitance must often be added (see the VSAG equation in the *Design Procedure* section).

The absolute point of dropout is when the inductor current ramps down during the minimum off-time ( $\Delta I_{DOWN}$ ) as much as it ramps up during the maximum on-time ( $\Delta I_{UP}$ ). The ratio h =  $\Delta I_{UP}$  /  $\Delta I_{DOWN}$  is an indicator of the ability to slew the inductor current higher in response to increased load, and must always be greater than 1. As h approaches 1, the absolute minimum dropout point, the inductor current cannot increase as much during each switching cycle and VSAG greatly increases unless additional output capacitance is used.

A reasonable minimum value for h is 1.5, but adjusting this up or down allows tradeoffs between  $V_{SAG}$ , output capacitance, and minimum operating voltage.

For a given value of h, the minimum operating voltage can be calculated as:

$$V_{IN(MIN)} = \left[\frac{V_{OUT} + V_{DROP1}}{1 - hf_{SW}t_{OFF}(MIN)}\right] + V_{DROP2} - V_{DROP1}$$

where V<sub>DROP1</sub> is the sum of the parasitic voltage drops in the inductor discharge path, including synchronous rectifier, inductor, and PC board resistances; V<sub>DROP2</sub> is the sum of the resistances in the charging path, including high-side switch, inductor, and PC board resistances; and t<sub>OFF(MIN)</sub> is from the *Electrical Characteristics*. The absolute minimum input voltage is calculated with h = 1.

If the calculated V+(MIN) is greater than the required minimum input voltage, then reduce the operating frequency or add output capacitance to obtain an acceptable V<sub>SAG</sub>. If operation near dropout is anticipated, calculate V<sub>SAG</sub> to be sure of adequate transient response.

Dropout Design Example:

$$VOUT = 5$$

$f_{SW} = 600 \text{kHz}$   $t_{OFF(MIN)} = 250 \text{ns}$   $V_{DROP1} = V_{DROP2} = 100 \text{mV}$ h = 1.5

$$V_{\text{IN(MIN)}} = \left[\frac{5V + 100\text{mV}}{1 - 1.5(600\text{kHz})(250\text{ns})}\right] + 100\text{mV} - 100\text{mV} = 6.58\text{V}$$

Calculating again with h = 1 gives the absolute limit of dropout:

$$V_{\text{IN(MIN)}} = \left[\frac{5V + 100\text{mV}}{1 - (600\text{kHz})(250\text{ns})}\right] + 100\text{mV} - 100\text{mV} = 6V$$

Therefore,  $V_{IN}$  must be greater than 6V, even with very large output capacitance, and a practical input voltage with reasonable output capacitance would be 6.58V.

### Improving Noise Immunity

Applications where the MAX8529 must operate in noisy environments can typically adjust their controller's compensation to improve the system's noise immunity. In particular, high-frequency noise coupled into the feedback loop causes jittery duty cycles. One solution is to lower the crossover frequency (see the *Compensation* section).

### **PC Board Layout Guidelines**

Careful PC board layout is critical to achieve low switching losses and clean, stable operation. This is

especially true for dual converters where one channel can affect the other. Refer to the MAX8529 EV kit data sheet for a specific layout example.

If possible, mount all of the power components on the top side of the board with their ground terminals flush against one another. Follow these guidelines for good PC board layout:

- Isolate the power components on the top side from the analog components on the bottom side with a ground shield. Use a separate PGND plane under the OUT1 and OUT2 sides (referred to as PGND1 and PGND2). Avoid the introduction of AC currents into the PGND1 and PGND2 ground planes. Run the power-plane ground currents on the top side only.

- 2) Use a star ground connection on the power plane to minimize the crosstalk between OUT1 and OUT2.

- Keep the high-current paths short, especially at the ground terminals. This practice is essential for stable, jitter-free operation.

- Connect GND and PGND together close to the IC. Do not connect them together anywhere else. Carefully follow the grounding instructions under step 4 of the *Layout Procedure* section.

- Keep the power traces and load connections short. This practice is essential for high efficiency. Use thick copper PC boards (2oz vs. 1oz) to enhance full-load efficiency by 1% or more.

- 6) LX\_ and PGND connections to the synchronous rectifiers for current limiting must be made using Kelvin sense connections to guarantee the currentlimit accuracy. With 8-pin SO MOSFETs, this is best done by routing power to the MOSFETs from outside using the top copper layer, while connecting PGND and LX\_ underneath the 8-pin SO package.

- 7) When trade-offs in trace lengths must be made, allow the inductor-charging path to be made longer than the discharge path. Since the average input current is lower than the average output current in step-down converters, this minimizes the power dissipation and voltage drops caused by board resistance. For example, allow some extra distance between the input capacitors and the high-side MOSFET rather than to allow distance between the inductor and the low-side MOSFET or between the inductor and the output filter capacitor.

- 8) Ensure that the feedback connection to C<sub>OUT</sub> is short and direct.

- 9) Route high-speed switching nodes (BST\_, LX\_, DH\_, and DL\_) away from the sensitive analog areas (REF, COMP\_, ILIM\_, and FB\_). Use PGND1 and PGND2 as EMI shields to keep radiated noise away from the IC, feedback dividers, and analog bypass capacitors.

- 10) Make all pin-strap control input connections (ILIM\_, SYNC, and EN) to analog ground (GND) rather than power ground (PGND).

### **Layout Procedure**

- 1) Place the power components first, with ground terminals adjacent (N<sub>L</sub> source, C<sub>IN</sub>, and C<sub>OUT</sub>). Make all these connections on the top layer with wide, copper-filled areas (2oz copper recommended).

- 2) Mount the controller IC adjacent to the synchronous rectifier MOSFETs (NL\_), preferably on the back side in order to keep LX\_, PGND\_, and DL\_ traces short and wide. The DL\_ gate trace must be short and wide, measuring 50mils to 100mils wide if the low-side MOSFET is 1in from the controller IC.

- Group the gate-drive components (BST\_ diodes and capacitors, and V<sub>L</sub> bypass capacitor) together near the controller IC.

- 4) Make the DC-to-DC controller ground connections as follows:

- a) Create a small analog ground plane near the IC.

- b) Connect this plane to GND and use this plane for the ground connection for the reference (REF) V+ bypass capacitor, compensation components, feedback dividers, OSC resistor, and ILIM\_ resistors (if any).

- c) Connect GND and PGND together under the IC (this is the only connection between GND and PGND).

- 5) On the board's top side (power planes), make a star ground to minimize crosstalk between the two sides.

### **Buck-Boost**

The MAX8529 step-down regulator can be configured as a buck-boost (step-up) regulator with the addition of a MOSFET switch and an output diode (Figure 8). When LX is high, the inductor current increases with a slope of  $V_{IN}$

/ L. When LX is low, the inductor current decreases with a slope of  $(V_{OUT} + V_D)$  / L. The input and output currents are discontinuous, which allows the output voltage to be greater or less than the input voltage.

The output voltage is a function of the input voltage and the duty cycle:

$$V_{OUT} = \frac{D}{1-D} \times V_{IN}$$

Notice that the output voltage is increased by a factor of 1 / (1 - D) compared with a normal step-down regulator. The additional loop gain must be considered when designing the compensation circuit. Solving for D:

$$D_{MAX} = \frac{V_{OUT}}{V_{IN,MIN} + V_{OUT}}$$

and the maximum additional gain is:

$$G = \frac{1}{1 - D_{MAX}}$$

The open-loop gain must be reduced by a factor of G for stability at a given bandwidth compared with a normal step-down regulator. Alternatively, the unity-gain crossover frequency can be reduced by a factor of G when applying the compensation equations.

The output current is a fraction of the peak switch current and depends on the DC current in the inductor:

$$\begin{split} I_{OUT} &= (1 - D) \times \left( I_{L,DC} + \frac{1}{2} I_{L,RIPPLE} \right) \\ &\text{and} \\ I_{PK} &= I_{L,DC} + I_{L,RIPPLE} \\ \text{Choose L} &\approx \frac{V_{IN} \times (1 - D_{MAX}) \times D_{MAX}}{0.4 \times I_{OUT} \times f_{SW}} \end{split}$$

where fsw is the switching frequency.

Choose

$$C_{OUT} > \frac{I_{OUT} \times D_{MAX}}{V_{RIPPLE} \times f_{SW}}$$

where V<sub>RIPPLE</sub> is the maximum output ripple voltage and C<sub>OUT</sub> is a ceramic capacitor. Choose the output Schottky diode to be rated for I<sub>PK</sub> and V<sub>OUT</sub>. Similarly, choose the extra MOSFET to be rated for I<sub>PK</sub>, V<sub>GS,BR</sub> > V<sub>IN</sub>, and fast switching (< 50ns).

The buck-boost portion of the circuit shown in Figure 8 delivers 24V at 50mA with 70% efficiency. A pre+load resistor is used to ensure constant frequency operation over the entire load range.

Chip Information

TRANSISTOR COUNT: 6688 PROCESS: BICMOS

Figure 8. Buck-Boost Application

**MAX8529**

# **Package Information**

**MAX8529**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <u>www.maxim-ic.com/packages.</u>)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600