#### 查询IDT821034供应商

# QUAD PCM CODEC WITH PROGRAMMABLE GAIN

# IDT821034

# FEATURES:

- · 4 channel CODEC with on-chip digital filters

- Software Selectable A-law/malaw companding

- Programmable gain setting

- Automatic master clock frequency selection: 2.048MHz, 4.096 MHz or 8.192MHz

- Flexible PCM interface with up to 128 programmable time slots, data rate from 512 kbits/s to 8.192 Mbits/s

- 5 SLIC signaling pins per channel

- Flexible Serial Control Interface to microcontroller

- Software programmable timing modes

- TTL and CMOS compatible digital I/O

- Meets or exceeds ITU-T G.711 G.714 requirements

- +5V single power supply

- Low power consumption: 100mW Typ.

- Operating temperature range: -40 °C to +85 °C

- Packages available: 52 pin PQFP

# **DESCRIPTION:**

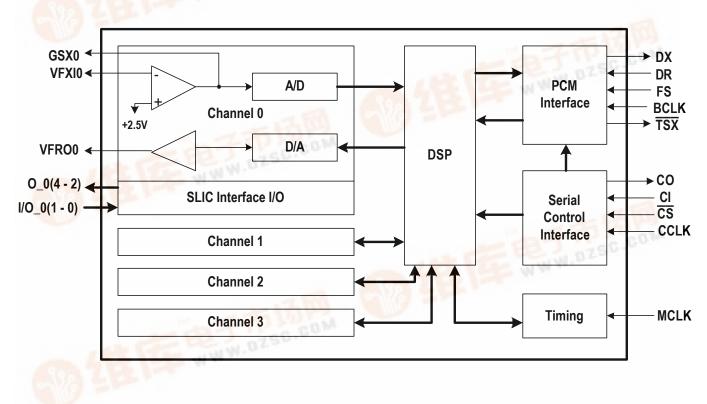

The IDT821034 is a single-chip, four channel PCM CODEC with onchip filters and programmable gain setting. This device provides both  $\mu$ -Law and A-Law companding digital-to-analog and analog-to-digital conversions based on ITU-T G.711 - G.714 specifications. The digital filters in IDT821034 provides the necessary transmit and receive filtering for voice telephone circuit to interface with time-division multiplexed systems. The IDT821034 has a flexible PCM interface with software selectable timing modes and independently programmable time slot for each transmit and receive channel. It also integrates the SLIC signaling functions through internal registers. The CODEC and SLIC control/status registers are accessed via the Serial Control Interface.

The IDT821034 can be used in digital telecommunication applications such as PBX, Central Office Switch, Digital Telephone and Integrated Voice/ Data Access Unit.

### MAY 13, 2003

# **FUNCTIONAL BLOCK DIAGRAM**

# **PIN CONFIGURATIONS**

# **PIN DESCRIPTION**

| Name  | Туре | Pin Number | Description                                                                                                                                     |

|-------|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| GNDA  |      | 46         | Analog Ground.                                                                                                                                  |

|       |      | 51         | All ground pins should be connected to the ground plane of the circuit board.                                                                   |

|       |      | 52         |                                                                                                                                                 |

|       |      | 40         |                                                                                                                                                 |

|       |      | 41         |                                                                                                                                                 |

| VDDA  |      | 47         | +5 V Analog Power Supply.                                                                                                                       |

|       |      | 45         | This pin should be bypassed to ground using 0.1µF capacitor. All power supply pins should be connected to the power plane of the circuit board. |

| VFRO3 | 0    | 3          | Voice Frequency Receiver Output.                                                                                                                |

| VFRO2 |      | 48         | This is the output of receive power amplifier. It can drive 2000 $\Omega$ (or greater) load.                                                    |

| VFRO1 |      | 44         |                                                                                                                                                 |

| VFRO0 |      | 37         |                                                                                                                                                 |

| GSX3  | 0    | 2          | Gain Setting Transmit Amplifier Output.                                                                                                         |

| GSX2  |      | 49         | This pin is the output of the gain setting amplifier, and the input to the differential transmit filter. It should be                           |

| GSX1  |      | 43         | connected to the corresponding VFXI pin through a resistive network to set the transmit gain. Refer to Figure                                   |

| GSX0  |      | 38         | 5 for details.                                                                                                                                  |

| VFXI3 | 1    | 1          | Voice Frequency Transmitter Input.                                                                                                              |

| VFXI2 |      | 50         | This pin is the input to the gain setting amplifier in the transmit path.                                                                       |

| VFXI1 |      | 42         |                                                                                                                                                 |

| VFXI0 |      | 39         |                                                                                                                                                 |

| O3_4  | 0    | 9          | SLIC Signaling Output for Channel 3.                                                                                                            |

| O3_3  |      | 10         |                                                                                                                                                 |

| O3 2  |      | 11         |                                                                                                                                                 |

| O2_4  |      | 4          | SLIC Signaling Output for Channel 2.                                                                                                            |

| O2_3  | 0    | 5          |                                                                                                                                                 |

| O2_2  |      | 6          |                                                                                                                                                 |

# INDUSTRIAL TEMPERATURE RANGE

# **PIN DESCRIPTION (CONTINUED)**

| Name             | Type | Pin Number | Description                                                                                                                                                                                                     |

|------------------|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01_4             |      | 35         | SLIC Signaling Output for Channel 1.                                                                                                                                                                            |

| 01_3             | 0    | 34         |                                                                                                                                                                                                                 |

| 01_2             |      | 33         |                                                                                                                                                                                                                 |

| O0_4             |      | 30         | SLIC Signaling Output for Channel 0.                                                                                                                                                                            |

| O0_3             | 0    | 29         |                                                                                                                                                                                                                 |

| O0 2             |      | 28         |                                                                                                                                                                                                                 |

| I/O3_1<br>I/O3_0 | I/O  | 12<br>13   | SLIC Signaling I/O for Channel 3.                                                                                                                                                                               |

| I/O2_1<br>I/O2_0 | I/O  | 7<br>8     | SLIC Signaling I/O for Channel 2.                                                                                                                                                                               |

| I/O1_1<br>I/O1_0 | I/O  | 32<br>31   | SLIC Signaling I/O for Channel 1.                                                                                                                                                                               |

| I/O0_1<br>I/O0_0 | I/O  | 27 26      | SLIC Signaling I/O for Channel 0.                                                                                                                                                                               |

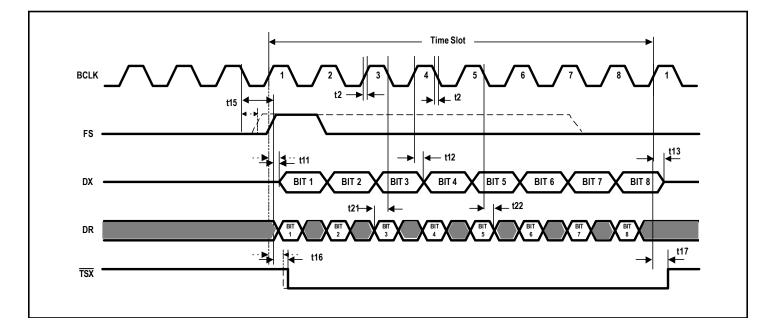

| DX               | 0    | 14         | Transmit PCM Data Output.<br>PCM data is shifted out of DX on rising edges of BCLK.                                                                                                                             |

| VDD              | -    | 15         | +5 V Digital Power Supply.<br>All power supply pins should be connected to the power plane of the circuit board.                                                                                                |

| DR               | 1    | 16         | Receive PCM Data Input.<br>PCM data is shifted into DR on falling edges of BCLK.                                                                                                                                |

| TSX              | 0    | 17         | Time Slot Indicator Output, Open Drain<br>This pin pulses low during the active time slot of each channel. A low level on this pin indicates active DX output.                                                  |

| FS               | I    | 18         | Frame Synchronization.<br>The FS pulse serves as the reference to time slots. The width of the FS pulse should be at least one BCLK cycle.                                                                      |

| MCLK             | I    | 19         | Master Clock.<br>Master Clock provides the clock for DSP. It can be 2.048 MHz, 4.096 MHz or 8.192 MHz. It must be<br>synchronous to FS.                                                                         |

| BCLK             | I    | 20         | Bit Clock.<br>Bit Clock shifts out PCM data on DX pin and shifts in PCM data on DR pin. The clock can vary from 512 kHz to 8.192 MHz at 64 kHz increment, depending on the time slot requirement of the system. |

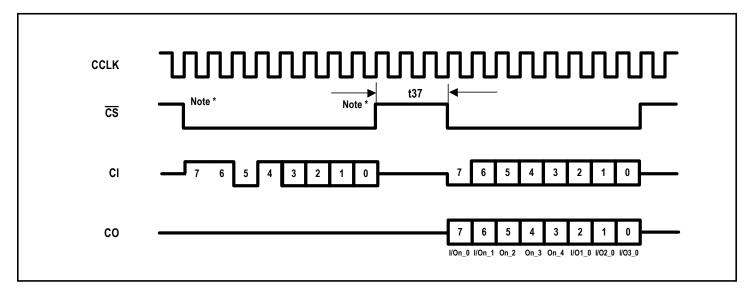

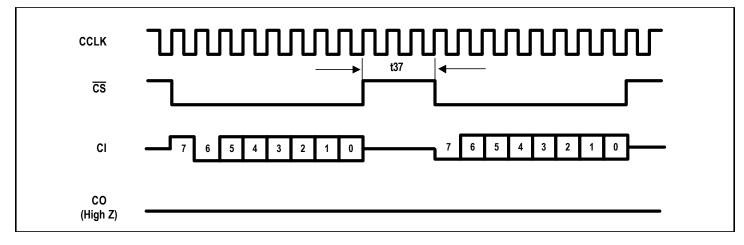

| CCLK             | I    | 21         | Serial Control Interface Clock.<br>This is the clock for Serial Control Interface. It can be up to 8.192 MHz.                                                                                                   |

| со               | 0    | 22         | Serial Control Interface Data Tri-State Output.<br>This pin is used to monitor SLIC working status. It is in high impedance state when CS is high.                                                              |

| СІ               | 1    | 23         | Serial Control Interface Data Input.<br>Data input on this pin can control both CODEC and SLIC.                                                                                                                 |

| <u>cs</u>        | I    | 24         | Chip Select.<br>A low level on this pin enables the Serial Control Interface.                                                                                                                                   |

| GND              |      | 25         | Ground.<br>All ground pins should be connected to the ground plane of the circuit board.                                                                                                                        |

| CNF              | 0    | 36         | <b>Capacitor For Noise Filter.</b><br>This pin should be connected to GNDA via a 0.1 μF capacitor.                                                                                                              |

### FUNCTIONAL DESCRIPTION

The IDT821034 contains four channel PCM CODEC with on chip digital filters. It provides the four-wire solution for the subscriber line circuitry in digital switches. The device converts analog voice signal into digital PCM samples, and converts digital PCM samples back to analog signal. Digital filters are used to bandlimit the voice signals during conversion.

The frequency of the master clock (MCLK) can be 2.048 MHz, 4.096 MHz or 8.192 MHz. Internal circuitry determines the master clock frequency automatically.

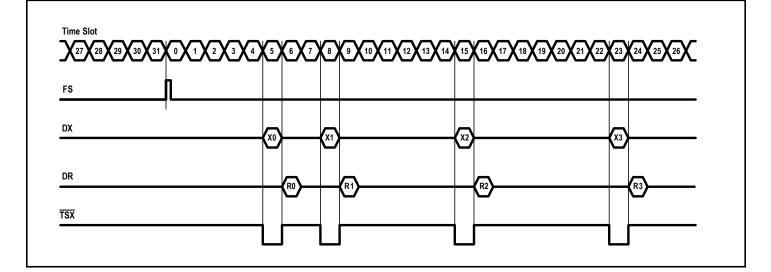

Four channels of serial PCM data are time multiplexed via two pins, DX and DR. The time slots of the four channels can be programmed dynamically. The control words can be written by a microcontroller via the Serial Control Interface. Dynamic time-slot assignment can accommodate 8 to 128 time slots corresponding to the bit clock (BCLK) frequency from 512 kHz to 8.192 MHz.

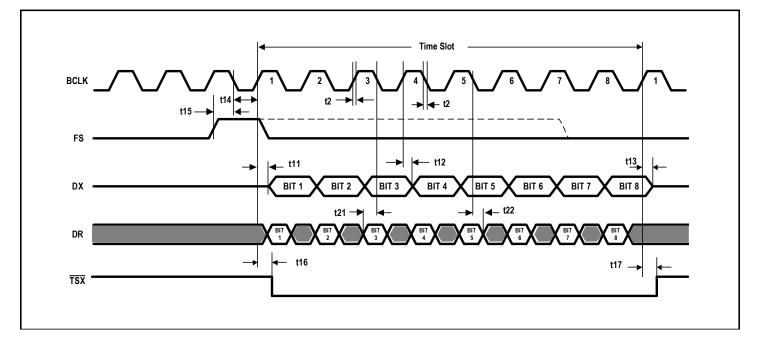

The IDT821034 offers two timing modes, delay mode and non-delay mode. Mode selection is done by programming the Configuration Register. The two modes are distinguished by time slot zero definition. In delay mode, the time slot zero is defined as starting on the first rising edge of BCLK after FS = '1' is detected by the falling edge of BCLK (Figure 7). While in non-delay mode, the time slot zero starts when both BCLK and FS are high (Figure 8).

The device provides a programmable interface to SLIC (Subscriber Line Interface Circuit). Each channel of the IDT821034 has three output pins and two I/O pins for SLIC signaling. These interface pins are mapped to internal registers and are accessed by the microcontroller via the Serial Control Interface. In this way, the IDT821034 provides high level of integration in line card design.

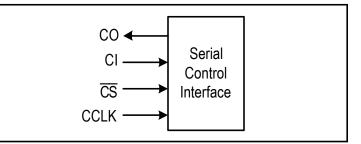

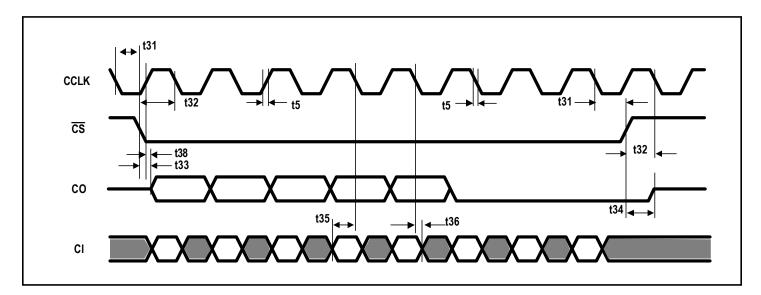

The Serial Control Interface of IDT821034 consists of four pins (CI, CO, CS and CCLK), as shown in Figure 1, for the communication to a microcontroller. Via this interface, the microcontroller can control the CODEC and SLIC working modes as well as monitor the SLIC status.

# **OPERATION CONTROL**

The following operation description applies to all four channels of the IDT821034.

#### **Initial State**

The IDT821034 has a built-in power on reset circuit. After initial power up, the device defaults to the following mode:

- 1. A-law is selected;

- 2. Delay mode is selected;

- 3. I/O pins of SLIC interface are set to input mode;

- 4. SLIC Control and Status Register bits are set to '0';

- 5. All four channels are placed in standby mode;

- All transmit and receive time slots are disabled with Time Slot Registers set to zero;

- 7. DX is set to high impedance state.

#### **Operating Modes**

There are two operating modes for each transmit or receive channel: standby mode and normal mode. When the IDT821034 is first powered on, standby mode is the default mode. Microcontroller can also set the device into this mode via the Serial Control Interface. In standby mode, the Serial Control Interface remains active to receive commands from the microcontroller. All other circuits are powered down with the analog outputs placed in high impedance state. All circuits which contain programmed information retain the data in this mode.

Each of the four channels in the IDT821034 can be in either normal mode or standby mode. The mode selection of each channel is done by the microcontroller via the Serial Control Interface. When in normal mode. each channel of the IDT821034 is able to transmit and receive both PCM and analog information. This is the operating mode when a telephone call is in progress.

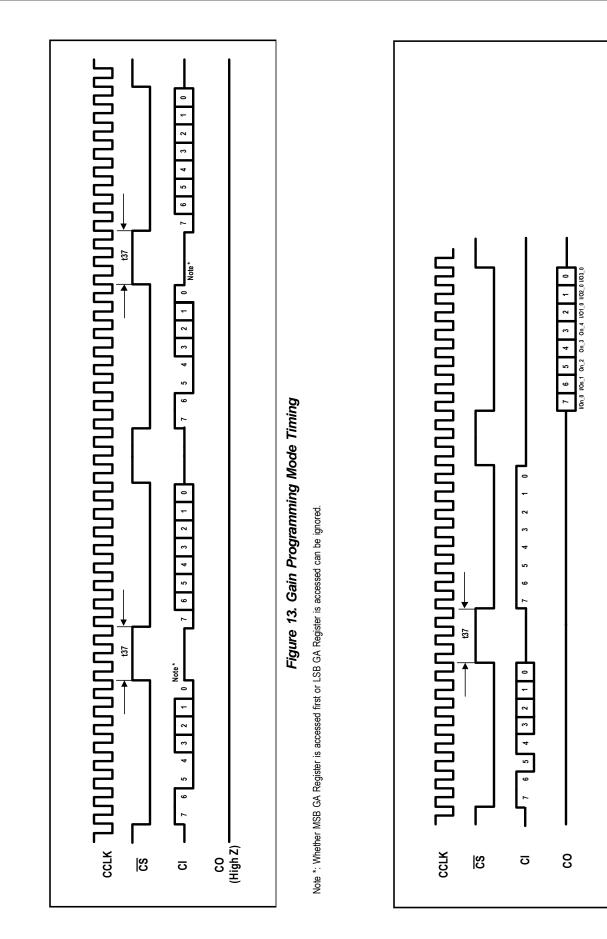

### **Gain Programming**

Transmit gain and receive gain of each channel in IDT821034 can be varied by programming DSP digital filter coefficients. Transmit gain can be varied within the range of -3 dB to +13 dB; while receive gain can be varied within the range of -13 dB to +3 dB. This function allows the IDT821034 to be used with SLICs of different gain requirement.

Gain programming coefficient can be written into IDT821034 via Serial Control Interface. The detailed operation will be covered in Serial Control Interface description. The gain programming coefficients should be calculated as:

Transmit: Coeff X = round [gain X0dB × gain X] Receive: Coeff\_R = round [gain\_R0dB × gain\_R] where:

gain\_X0dB = 1820; gain\_X is the target gain; Coeff\_X should be in the range of 0 to 8192. gain R0dB = 2506; gain R is the target gain; Coeff\_R should be in the range of 0 to 8192.

A gain programming coefficient is 14-bit wide and in binary format. The 7 Most Significant Bits of the coefficient is called GA\_MSB\_Transmit for transmit path, or is called GA MSB Receive for receive path; The 7 Least Significant Bits of the coefficient is called GA\_LSB\_ Transmit for transmit path, or is called GA\_LSB\_Receive for receive path.

An example is given below to clarify the calculation of the coefficient. To program a +3 dB gain in transmit path and a -3.5 dB gain in receive path:

| •           | Linear Code of +3 dB               | = 10 <sup>3/20</sup><br>= 1.412537545                                               |

|-------------|------------------------------------|-------------------------------------------------------------------------------------|

| r           | Coeff_X                            | = round (1820 × 1.412537545)<br>= 2571<br>= 0010100, 0001011<br>(in binary format ) |

|             | GA_MSB_Transmit<br>GA_LSB_Transmit | = 0010100<br>= 0001011                                                              |

| -           | Linear Code of -3.5 dB             | = 10 <sup>(-3.5/20)</sup><br>= 0.668343917                                          |

| :           | Coeff_R                            | = round (2506 × 0.668343917)<br>= 1675<br>= 0001101, 0001011<br>(in binary format)  |

| )<br>)<br>) | GA_MSB_Receive<br>GA_LSB_Receive   | = 0001101<br>= 0001011                                                              |

### SIGNAL PROCESSING

High performance oversampling Analog-to-Digital Converters (ADC) and Digital-to-Analog Converters (DAC) are used in the IDT821034 to provide the required conversion accuracy. The associated decimation and interpolation filters are realized with both dedicated hardware and Digital Signal Processor (DSP). The DSP also handles all other necessary functions such as PCM bandpass filtering and sample rate conversion.

### **Transmit Signal Processing**

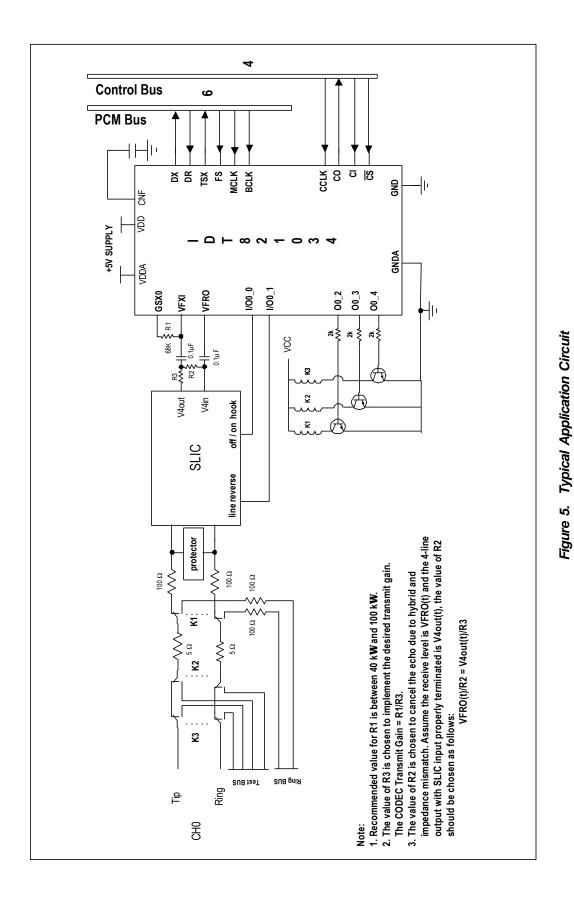

In the transmit path, the analog input signal is received with a gain setting amplifier. The signal gain is set by the resistive feedback network as shown in the application circuit (Figure 5). The output of the gain setting amplifier is connected internally to the input of the anti-alias filter for the oversampling ADC. The digital output of the oversampling ADC is decimated and sent to the DSP. The transmit filter is implemented in the DSP as a digital bandpass filter. The filtered signal is further decimated and compressed to PCM format.

### **Transmit PCM Interface**

The transmit PCM interface clocks the PCM data out of DX pin on rising edges of BCLK according to the time slot assignment. The frame sync (FS) pulse identifies the beginning of a transmit frame, or time slot zero. The time slots for all channels are referenced to FS. The IDT821034 contains user programmable Transmit Time Slot Register for each transmit channel. The register is 7 bits wide and can accommodate up to 128 time slots (corresponding to the maximum BCLK frequency of 8.192 MHz) in each frame. The PCM Data is transmitted serially on DX pin with the Most Significant Bit (MSB), or Bit 7, first.

When the device is first powered up, all transmit time slots are disabled with Transmit Time Slot Registers set to zero. DX pin remains in highimpedance state. To power up or power down each transmit channel, Configuration Register and the corresponding Time Slot Register must be programmed.

### **Receive Signal Processing**

In the receive path, the PCM code is received at the rate of 8,000 samples per second. The PCM code is expanded and sent to the DSP for interpolation and receive channel filtering function. The receive filter is implemented in the DSP as a digital lowpass filter. The filtered signal is then sent to an oversampling DAC. The DAC output is post-filtered and then delivered at VFRO pin by a power amplifier. The amplifier can drive resistive load higher than 2 k $\Omega$ .

### **Receive PCM Interface**

The receive PCM interface clocks the PCM data into DR pin on falling edges of BCLK according to the time slot assignment. The receive time slot definition and programming is similar to that of the transmit time slot. The IDT821034 contains a user programmable Receive Time Slot Register for each receive channel. The register is 7 bits wide and can accommodate up to 128 time slots (corresponding to the maximum BCLK frequency of 8.192 MHz) in each frame. The PCM Data is received serially on DR pin with the MSB (Bit 7) first.

When the device is first powered up, all receive time slots are disabled with Receive Time Slot Registers set to zero. Data on DR pin is ignored. To power up or power down each receive channel, Configuration Register and the corresponding Time Slot Register must be programmed.

### Serial Control Interface

A Serial Control Interface is provided for a microprocessor to access the control and status registers of IDT821034. The control registers include Configuration Register, Time Slot Registers, SLIC Control Registers and Gain Adjustment Registers. They are used to program the working modes of CODEC and SLIC. The status registers include SLIC Status Registers. They are used to monitor SLIC functions. All registers are 8 bits wide.

The Serial Control Interface consists of CO, CI,  $\overline{CS}$  and CCLK pins (see Figure 1). A microprocessor initiates a write or read cycle after low level is asserted on  $\overline{CS}$  pin. In the microprocessor write cycle, 8 bits of serial data on CI pin are shifted into the device at falling edges of CCLK. In the microprocessor read cycle, 8 bits of serial data are shifted out of the device on CO pin at rising edges of CCLK. At the end of each 8-bit transaction, the microprocessor sets  $\overline{CS}$  high to terminate the cycle. Multiple accesses to the device are separated by an idle state (high level) of  $\overline{CS}$ . The width of  $\overline{CS}$  high level is at least three CCLK cycles.

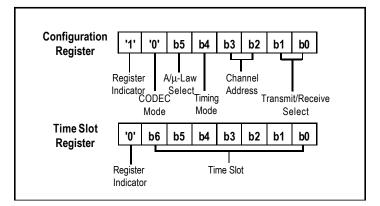

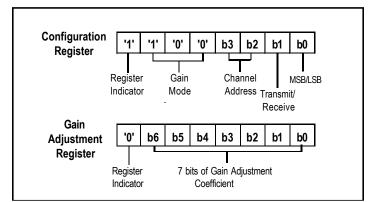

The IDT821034 has a Configuration Register. Its register bits are designated CR.7 - CR.0. The definition of the bits in Configuration Register is shown in Table 1. If the leading data bit on CI pin is '1' in a microprocessor write cycle, the 8-bit data on CI pin is latched into Configuration Register with MSB first.

There are eight Time Slot Registers for four transmit channels and four receive channels. The definition of the bits in Time Slot Register is shown in Table 2. Since PCM sample rate is 8k samples/sec and each sample is 8 bits wide, each time slot occupies 64 kbits/sec of data rate. The number of time slots in a frame is equal to the ratio of the bit clock frequency (BCLK) to 64 kHz. For the maximum BCLK frequency of 8.192 MHz, the number of time slots in a frame is 8.192MHz/64kHz, or 128. The minimum number of time slots (corresponding to the minimum BCLK frequency of 512 kHz) in a frame is 8. The relationship between frequently used BCLK frequencies and the number of time slots in a frame is shown in Table 3. Bit 6-0 in each Time Slot Register identify the time slot number (0 to 127) of the corresponding transmit or receive channel. Time Slot Registers can be accessed by specifying the transmit/ receive select (CR.1 and CR.0) and channel address (CR.3 and CR.2) in Configuration Register. If CR.6 = '0' and the leading data bit on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is latched into the selected Time Slot Register with MSB first.

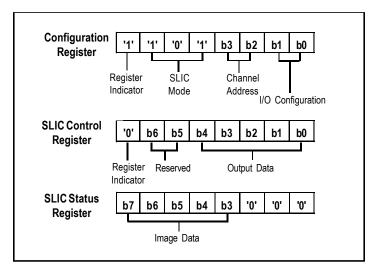

There are four SLIC Control Registers for four channel SLIC signaling control. The definition of the bits in a SLIC Control Register is shown in Table 4. SLIC Control Registers can be accessed by specifying the channel address (CR.3 and CR.2) in Configuration Register. If CR[6:4] = '101' and the leading data bit on Cl pin is '0' in a microprocessor write or read cycle, the 8-bit data on Cl pin is latched into the selected SLIC Control Register with MSB first.

There are four SLIC Status Registers for four channel SLIC monitoring. The bits in each SLIC Status Register are mapped to the SLIC signaling output and I/O pins of the corresponding channel as shown in Table 5. It should be noted that the last 3 bits of the SLIC Status Register are always mapped to I/O1\_0, I/O2\_0 and I/O3\_0. This feature allows a rapid read process of the SLIC status when Channel 0 is selected. The SLIC Status Registers can be accessed by specifying the channel address (CR.3 and CR.2) in the Configuration Register. If CR[6:4] = '101', as a result of the previous write to the Configuration Register, the subsequent microprocessor cycle is a read cycle. The content of the selected SLIC Status Register is shifted out of the device on CO pin with MSB first.

There are 16 Gain Adjustment Registers for both transmit and receive paths of four channels. For each path, there are two

corresponding 8-bit Gain Adjustment Registers: MSB GA Register, which stores the 7 Most Significant bits of gain adjustment coefficient; and LSB GA Register, which stores the 7 Least Significant bits of gain adjustment coefficient. All Gain Adjustment Registers start with '0'. Gain Adjustment Registers can be accessed by specifying the channel address (CR.3 and CR.2) in Configuration Register. If CR[6:4] = '100', CR.0 = '1' and the leading data bit on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is latched into the selected MSB GA Register with MSB first; If CR[6:4] = '100', CR.0 = '0' and the leading data bit on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is '0' in a microprocessor write cycle, the 8-bit data on CI pin is latched into the selected LSB GA Register with MSB first.

All microprocessor cycles are either write cycles or read cycles. In typical applications, the microprocessor will write control registers as ordered pairs for CODEC Mode programming (Figure 2), SLIC Mode programming (Figure 3), or Gain Mode programming (Figure 4). The first write in the pair is to Configuration Register. This is identified by a leading '1' on CI pin. If CR.6 = '0' after writing Configuration Register, the programming is for CODEC mode and the succeeding operation is a write cycle with a leading '0' on CI pin. The write is intended for the selected Time Slot Register. The timing diagram for CODEC Mode programming is shown in Figure 11. If CR.6 = '1' and CR.5 = '0' and CR.4 = '1' after writing Configuration Register, the programming is for SLIC control function and the succeeding operation is a read/write cycle. The write, also with a leading '0' on CI pin, is intended for the selected SLIC Control Register, while the simultaneous read is from the SLIC Status Register of the same channel. The timing diagram for SLIC Mode programming is shown in Figure 10. If CR.6 = '1', CR.5 = '0' and CR.4 = '0' after writing Configuration Register, the programming is for Gain adjustment function and the succeeding operation is a write cycle with a leading '0' on CI pin. The write is intended for the selected Gain Adjustment Register. The timing diagram for Gain Mode programming is shown in Figure 13.

Configuration Register, Time Slot Registers, SLIC Control Registers and Gain Adjustment Registers are write only registers while SLIC Status Registers are read only registers. Refer to Figure 12 for the detail timing of the Serial Control Interface.

An alternative method of receiving data from SLIC Status Register is designed for IDT821034. This procedure is initiated when a '1111-1110' command appears on CI. To read from the SLIC Status Registers when using this method, Configuration Register should be set to indicate the following operation is a SLIC programming, and then assert a '1111-1111' command on CI. The data from SLIC Status Registers will clock out of CO pin on CCLK rising edges when  $\overline{CS}$  is low. The timing diagram of this method is shown in Figure 14. When using this method, CO and CI pins can be connected together. Either CO or CI will be in high Z state, depending on the Serial Control Interface is in write cycle or read cycle. When a command of '1111-1101' appears on CI, the device will terminate this procedure.

Figure 1. Serial Control Interface Signals

Figure 2. Registers for CODEC Mode Programming

Figure 3. Registers for SLIC Mode Programming

Figure 4. Registers for Gain Mode Programming

# INDUSTRIAL TEMPERATURE RANGE

| Bit          | Name                                                          |                                            | Value                | Description                                                                                                                                                                                                                                          |

|--------------|---------------------------------------------------------------|--------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR.7         | Register Indicator                                            |                                            |                      | Always '1'                                                                                                                                                                                                                                           |

| CR.6<br>CR.5 | Mode Select 1<br>Mode Select 0                                |                                            |                      | μ-Law CODEC Mode (This is global setting for all channels.)<br>A-Law CODEC Mode (This is global setting for all channels.)<br>SLIC/Gain Mode<br>Reserved (This mode should not be programmed for normal operation.)                                  |

| CR.4         | CODEC Mode (CR.6 = '0')                                       | Timing Mode Select                         | 0<br>1               | Non-delay Mode (This is global setting for all channels.)<br>Delay Mode (This is global setting for all channels.)                                                                                                                                   |

| UK.4         | SLIC/Gain Mode (CR.6 = '1') SLIC/Gain Mode Select             |                                            | 0<br>1               | Gain Mode<br>SLIC Mode                                                                                                                                                                                                                               |

| CR.3<br>CR.2 |                                                               |                                            |                      | Select Channel 0 for CODEC or SLIC programming<br>Select Channel 1 for CODEC or SLIC programming<br>Select Channel 2 for CODEC or SLIC programming<br>Select Channel 3 for CODEC or SLIC programming                                                 |

|              | CODEC Mode (CR.6 = '0') Transmitter Select<br>Receiver Select |                                            | 00<br>01<br>10<br>11 | Channel power down<br>Channel power up with receive time slot assignment<br>Channel power up with transmit time slot assignment<br>Channel power up with both receive and transmit time slot assignment                                              |

| CR.1<br>CR.0 | SLIC Mode (CR.6 = '1', CR.4 = '1')                            | I/O_1 Configuration<br>I/O_0 Configuration | 00<br>01<br>10<br>11 | Configure I/O_1 as an output pin and I/O_0 as an output pin<br>Configure I/O_1 as an output pin and I/O_0 as an input pin<br>Configure I/O_1 as an input pin and I/O_0 as an output pin<br>Configure I/O_1 as an input pin and I/O_0 as an input pin |

|              |                                                               | CR.1: Transmit/Receive<br>Select           | 0<br>1               | Receive gain will be adjusted<br>Transmit gain will be adjusted                                                                                                                                                                                      |

|              | Gain Mode (CR.6 = '1', CR.4 = '0')<br>CR.0: MSB/LSB Select    |                                            | 0<br>1               | Indicates the following 8 bits contain the 7 Least Significant bits of gain adjustment coefficient<br>Indicates the following 8 bits contain the 7 Most Significant bits of gain adjustment coefficient                                              |

# Table 1. Description of Configuration Register

| Bit | Name               | Description                                                                         |

|-----|--------------------|-------------------------------------------------------------------------------------|

| 7   | Register Indicator | Always '0'                                                                          |

| 6   | Time Slot Bit 6    | Bit 6-0 indicate which time slot is selected for the transmit/receive channel. Time |

| 5   | Time Slot Bit 5    | Slot 0 is aligned to FS.                                                            |

| 4   | Time Slot Bit 4    | -                                                                                   |

| 3   | Time Slot Bit 3    |                                                                                     |

| 2   | Time Slot Bit 2    |                                                                                     |

| 1   | Time Slot Bit 1    |                                                                                     |

| 0   | Time Slot Bit 0    |                                                                                     |

| Table 2. | Definition | of | Time | Slot | Register |

|----------|------------|----|------|------|----------|

|----------|------------|----|------|------|----------|

| BCLK Frequency      | 512 kHz | 1.544 MHz | 2.048 MHz | 4.096 MHz | 8.192 MHz |

|---------------------|---------|-----------|-----------|-----------|-----------|

| Number of Time Slot | 8       | 24        | 32        | 64        | 128       |

Table 3. Relationship between BCLK Frequency and Time Slot Number

**INDUSTRIAL TEMPERATURE RANGE**

| Bit        | Name               | Description                                                                |  |  |  |  |

|------------|--------------------|----------------------------------------------------------------------------|--|--|--|--|

| 7          | Register Indicator | Always '0'                                                                 |  |  |  |  |

| 6          |                    | Reserved, always '0'                                                       |  |  |  |  |

| 5          |                    | Reserved, always '0'                                                       |  |  |  |  |

| 4          | O_4 Data           | Output data on O_4 pin of the selected channel                             |  |  |  |  |

| 3 O_3 Data |                    | Output data on O_3 pin of the selected channel                             |  |  |  |  |

| 2          | O_2 Data           | Output data on O_2 pin of the selected channel                             |  |  |  |  |

| 1          | I/O_1 Data         | Output data on I/O_1 pin (if defined as an output) of the selected channel |  |  |  |  |

| 0          | I/O _0 Data        | Output data on I/O_0 pin (if defined as an output) of the selected channel |  |  |  |  |

Table 4. Definition of SLIC Control Register

| Bit | Name                                           | Description                                    |  |  |  |  |  |

|-----|------------------------------------------------|------------------------------------------------|--|--|--|--|--|

| 7   | I/On_0 Image                                   | Mapped to I/On_0 pin of the selected channel n |  |  |  |  |  |

| 6   | I/On_1 Image                                   | Mapped to I/On_1 pin of the selected channel n |  |  |  |  |  |

| 5   | On_2 Image                                     | Mapped to On_2 pin of the selected channel n   |  |  |  |  |  |

| 4   | On_3 Image                                     | Mapped to On_3 pin of the selected channel n   |  |  |  |  |  |

| 3   | On_4 Image                                     | Mapped to On_4 pin of the selected channel n   |  |  |  |  |  |

| 2   | I/O1_0 Image                                   | Always mapped to the I/O1_0 pin                |  |  |  |  |  |

| 1   | 1 I/O2_0 Image Always mapped to the I/O2_0 pin |                                                |  |  |  |  |  |

| 0   | 0 I/O3_0 Image Always mapped to the I/O3_0 pin |                                                |  |  |  |  |  |

Table 5. Definition of SLIC Status Register

# APPLICATION NOTE

The IDT821034 is mainly used in line card application. Figure 5 shows a typical system with telephony line interface.

The IDT821034 offers not only encoding/decoding function, but also a signaling channel, which can simplify the circuit design of the control interface. In addition, the dynamic time slot assignment of IDT821034 reduces the hardware requirement for PCM interface. The device also supports 8.192 Mbps PCM data rate, which can increase the time slot density up to 128.

Signal to total distortion ratio (both  $STD_x$  and  $STD_R$ ) are guaranteed over -55 dBm0 to +3 dBm0 range with a specific gain setting (0 dB for both transmit path and receive path). Since there is a finite noise floor associated with the quantization effect of both data converters and digital filter coefficients, the overall signal to total distortion ratio of each path is a function of the gain setting. In system design, attention should be paid to the gain setting for the best signal to total distortion performance.

Generally, a channel gain of a line-card system is contributed by both SLIC and CODEC. In a system design using IDT821034, the SLIC gain should be taken into account to optimize the SNR. In the transmit path of IDT821034, there are two resistors (R1 and R3 in Figure 5) which enable the analog gain to be adjusted around 0 dB. Further gain adjustment can be obtained by programming the DSP filters. Since this adjustment is close to 0 dB, the SNR remains at the optimum value. In the receive path of IDT821034, analog gain adjustment is not available. Thus, the adjustment of CODEC gain will be performed only by programming the DSP filters. In this way, the SLIC gain should be such that the DSP gain is closest to 0 dB. This will maximize the achievable SNR in the overall system. For example, if the design target for receive path gain is -3.5 dB and -7 dB for local and long distance calls respectively, the recommended solution is to set SLIC gain at -3.5 dB. As a result, the gain of CODEC, which is adjusted by programming DSP coefficients, will be 0 dB and -3.5 dB.

# **ABSOLUTE MAXIMUM RATINGS**

| Rating                                            | Com'l & Ind'l | Unit |

|---------------------------------------------------|---------------|------|

| Power Supply Voltage                              | ≤ 6.5         | V    |

| Voltage on Any Pin with Respect to<br>Ground      | -0.5 to 5.5   | V    |

| Package Power Dissipation                         | ≤600          | mW   |

| Storage Temperature                               | -65 to +150   | °C   |

| Total SLIC Control pins output current per device |               |      |

| Source from VDD :<br>Sink from GND:               | 50<br>50      | mA   |

NOTE: Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **ELECTRICAL CHARACTERISTICS**

### **Digital Interface**

| Parameter | Description                            | Min       | Тур | Max | Units | Test Conditions                                                 |

|-----------|----------------------------------------|-----------|-----|-----|-------|-----------------------------------------------------------------|

| Vi∟       | Input Low Voltage                      |           |     | 0.8 | V     | All digital inputs                                              |

| Vih       | Input High Voltage                     | 2.0       |     |     | V     | All digital inputs                                              |

| Vol       | Output Low Voltage                     |           |     | 0.4 | V     | DX, TSX, CO, <b>L</b> = 14 mA                                   |

|           |                                        |           |     | 0.8 | V     | All other digital outputs, IL = 4 mA.                           |

|           |                                        |           |     | 0.2 | V     | All digital pins, I∟ = 1 mA.                                    |

| Vон       | Output High Voltage                    | VDD - 0.6 |     |     | V     | DX, CO, $H = -7$ mA.<br>All other digital outputs, $H = -4$ mA. |

|           |                                        | VDD - 0.2 |     |     | V     | All digital pins, IH = -1 mA                                    |

| lı        | Input Current                          | -10       |     | 10  | μД    | All digital inputs, GND <vin<vdd< td=""></vin<vdd<>             |

| loz       | Output Current in High-impedance State | -10       |     | 10  | μд    | DX                                                              |

| Cı        | Input Capacitance                      |           |     | 5   | pF    |                                                                 |

Note: The I/O\_n and O\_n outputs are resistive for less than a 0.8 V drop. Total current must not exceed absolute maximum ratings.

### **Power Dissipation**

| Parameter | Description       | Min | Тур | Max | Units | Test Conditions                                   |

|-----------|-------------------|-----|-----|-----|-------|---------------------------------------------------|

| IDD1      | Operating Current |     | 25  | 40  | mA    | All channels are active.                          |

| IDD0      | Standby Current   |     | 4   | 6   | mA    | All channels are powered down, with MCLK present. |

Note: Power measurements are made at MCLK = 4.096 MHz, outputs unloaded.

### INDUSTRIAL TEMPERATURE RANGE

# RECOMMENDED DC OPERATING CONDITIONS

| Parameter             | Min. | Тур. | Max. | Unit |

|-----------------------|------|------|------|------|

| Operating Temperature | -40  |      | +85  | Ο°   |

| Power Supply Voltage  | 4.75 |      | 5.25 | V    |

NOTE: MCLK: 2.048 MHz, 4.096 MHz or 8.192 MHz with tolerance of ± 50 ppm

INDUSTRIAL TEMPERATURE RANGE

### **Analog Interface**

| Parameter | Description                       | Min  | Тур | Max  | Units | Test Conditions                                     |

|-----------|-----------------------------------|------|-----|------|-------|-----------------------------------------------------|

| VFXI      | Input Voltage, VFXI               | 2.3  | 2.4 | 2.55 | V     |                                                     |

| VFR01     | Output Voltage, VFRO              | 2.25 | 2.4 | 2.6  | V     | Alternating ±zero $\mu$ -law PCM code applied to DR |

| VFR02     | Output Voltage Swing, VFRO        | 3.25 |     |      | Vp-р  | RL = 2000 Ω                                         |

| Rı        | Input Resistance, VFXI            | 2.0  |     |      | MΩ    | 0.25 V < VFXI < 4.75 V                              |

| Rg        | Load Resistance, GSX              | 10   |     |      | kΩ    |                                                     |

| Ro        | Output Resistance VFRO            |      |     | 20   | Ω     | 0 dBm0, 1020 Hz PCM code applied to DR.             |

| RL        | Load Resistance, VFRO             | 2000 |     |      | Ω     | External loading                                    |

|           | Input Leakage Current, VFXI       | -1.0 |     | 1.0  | μA    | 0.25 V < VFXI < VDD -0.25 V                         |

| lz        | Output Leakage Current, VFRO      | - 10 |     | 10   | μA    | Power down                                          |

| CG        | Load Capacitance, GSX             |      |     | 50   | pF    |                                                     |

| CL        | Load Capacitance, VFRO            |      |     | 100  | pF    | External loading                                    |

| Av        | DC Voltage Gain, VFXI to GSX      | 5000 |     |      |       |                                                     |

| fu        | Unity Gain Bandwidth, VFXI to GSX | 1    | 3   |      | MHz   |                                                     |

# **TRANSMISSION CHARACTERISTICS**

0 dBm0 is defined as 0.775 Vrms for A-law and 0.769 Vrms for µ-law, both for 600 W load. Unless otherwise noted, the analog input is a 0 dBm0, 1020 Hz sine wave; the input amplifier is set for unity gain. The digital input is a PCM bit stream equivalent to that obtained by passing a 0 dBm0, 1020 Hz sine wave through an ideal encoder. The output level is sin(x)/x-corrected.

### Absolute Gain

Gain Tracking

| Parameter | Description             | Тур   | Deviation | Units | Test Conditions                                                                                       |

|-----------|-------------------------|-------|-----------|-------|-------------------------------------------------------------------------------------------------------|

| Gxa       | Transmit Gain, Absolute | 0.00  | ±0.25     | dB    | Signal input of 0 dBm0, μ-law or A-law                                                                |

| GRA       | Receive Gain, Absolute  | -0.15 | ±0.25     | dB    | Measured relative to 0 dBm0, $\mu$ -law or A-law,<br>PCM input of 0 dBm0 1020 Hz , RL = 10 k $\Omega$ |

|                 |                        |       |     |      |       | i                                     |

|-----------------|------------------------|-------|-----|------|-------|---------------------------------------|

| Parameter       | Description            | Min   | Тур | Max  | Units | Test Conditions                       |

| GTx             | Transmit Gain Tracking |       |     |      |       | Tested by Sinusoidal Method, µ-law/A- |

|                 | +3 dBm0 to - 40 dBm0   | -0.10 |     | 0.10 | dB    | law                                   |

|                 | -40 dBm0 to -50 dBm0   | -0.25 |     | 0.50 | dB    |                                       |

|                 | -50 dBm0 to -55 dBm0   | -0.50 |     | 0.50 | dB    |                                       |

| GT <sub>R</sub> | Receive Gain Tracking  |       |     |      |       | Tested by Sinusoidal Method, µ-law/A- |

|                 | +3 dBm0 to - 40 dBm0   | -0.10 |     | 0.10 | dB    | law                                   |

|                 | -40 dBm0 to -50 dBm0   | -0.25 |     | 0.50 | dB    |                                       |

|                 | -50 dBm0 to -55 dBm0   | -0.50 |     | 0.50 | dB    |                                       |

### **Frequency Response**

| Parameter | Description                    | Min   | Тур | Max  | Units | Test Conditions |

|-----------|--------------------------------|-------|-----|------|-------|-----------------|

| Gxr       | Transmit Gain, Relative to GXA |       |     |      |       |                 |

|           | f = 50 Hz                      |       |     | -40  | dB    |                 |

|           | f = 60 Hz                      |       |     | -40  | dB    |                 |

|           | f = 300 Hz to 3400 Hz          | -0.15 |     | 0.15 | dB    |                 |

|           | f = 3600 Hz                    |       |     | -0.1 | dB    |                 |

|           | f = 4600 Hz and above          |       |     | -35  | dB    |                 |

| GRR       | Receive Gain, Relative to GRA  |       |     |      |       |                 |

|           | f below 300 Hz                 |       |     | 0    | dB    |                 |

|           | f = 300 Hz to 3400 Hz          | -0.15 |     | 0.15 | dB    |                 |

|           | f = 3600 Hz                    |       |     | -0.2 | dB    |                 |

|           | f = 4600 Hz and above          |       |     | -35  | dB    |                 |

# INDUSTRIAL TEMPERATURE RANGE

### **Group Delay**

| Parameter       | Description                                                                                                                         | Min | Тур | Max                     | Units                | Test Conditions |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------|----------------------|-----------------|

| Dxa             | Transmit Delay, Absolute *                                                                                                          |     |     | 340                     | μs                   |                 |

| Dxr             | Transmit Delay, Relative to 1800 Hz<br>f = 500 Hz – 600 Hz<br>f = 600 Hz –1000 Hz<br>f = 1000 Hz – 2600 Hz<br>f = 2600 Hz – 2800 Hz |     |     | 280<br>150<br>80<br>280 | μs<br>μs<br>μs<br>μs |                 |

| D <sub>RA</sub> | Receive Delay, Absolute *                                                                                                           |     |     | 260                     | μs                   |                 |

| D <sub>RR</sub> | Receive Delay, Relative to 1800 Hz<br>f = 500 Hz – 600 Hz<br>f = 600 Hz –1000 Hz<br>f = 1000 Hz – 2600 Hz<br>f = 2600 Hz – 2800 Hz  |     |     | 50<br>80<br>120<br>150  | μs<br>μs<br>μs<br>μs |                 |

Note\*: Minimum value in transmit and receive path.

### Distortion

| Parameter | Description                                                                                                                                     | Min                  | Typ* | Max | Units                | Test Conditions                                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-----|----------------------|------------------------------------------------------------------------------------------------------------|

| STDx      | Transmit Signal to Total Distortion Ratio<br>Input level = 0 dBm0<br>Input level = -30 dBm0<br>Input level = -40 dBm0<br>Input level = -45 dBm0 | 36<br>36<br>30<br>24 |      |     | dB<br>dB<br>dB<br>dB | ITU-T O.132<br>Sine Wave Method (C-message weighted<br>for μ-law; Psophometrically weighted for A-<br>law) |

| STDR      | Receive Signal to Total Distortion Ratio<br>Input level = 0 dBm0<br>Input level = -30 dBm0<br>Input level = -40 dBm0<br>Input level = -45 dBm0  | 36<br>36<br>30<br>24 |      |     | dB<br>dB<br>dB<br>dB | ITU-T O.132<br>Sine Wave Method (C-message weighted<br>for μ-law; Psophometrically weighted for A-<br>law) |

| SFDx      | Single Frequency Distortion, Transmit                                                                                                           |                      |      | -42 | dBm0                 | 200 Hz - 3400 Hz, 0 dBm0 input, output<br>any other single frequency ≤ 3400 Hz                             |

| SFDR      | Single Frequency Distortion, Receive                                                                                                            |                      |      | -42 | dBm0                 | 200 Hz - 3400 Hz, 0 dBm0 input, output<br>any other single frequency ≤ 3400 Hz                             |

| IMD       | Intermodulation Distortion                                                                                                                      |                      |      | -50 | dBm0                 | Four Tone Method                                                                                           |

### Noise

| Parameter | Description                                                                                                        | Min      | Тур | Max        | Units    | Test Conditions                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------|----------|-----|------------|----------|------------------------------------------------------------|

| Nxc       | Transmit Noise, C Message Weighted for µ-law                                                                       |          |     | 18         | dBrnC0   |                                                            |

| NXP       | Transmit Noise, P Message Weighted for A-law                                                                       |          |     | -68        | dBm0p    |                                                            |

| NRC       | Receive Noise, C Message Weighted for µ-law                                                                        |          |     | 12         | dBrnC0   |                                                            |

| NRP       | Receive Noise, P Message Weighted for A-law                                                                        |          |     | -78        | dBm0p    |                                                            |

| NRS       | Noise, Single Frequency<br>f = 0 kHz – 100 kHz                                                                     |          |     | -53        | dBm0     | VFXI = 0 Vrms, tested at VFRO                              |

| PSRX      | Power Supply Rejection Transmit<br>f = 300 Hz – 3.4 kHz<br>f = 3.4 kHz – 20 kHz                                    | 40<br>25 |     |            | dB<br>dB | VDD = 5.0 VDC + 100 mVrms                                  |

| PSRR      | Power Supply Rejection Receive<br>f = 300 Hz – 3.4 kHz<br>f = 3.4 kHz – 20 kHz                                     | 40<br>25 |     |            | dB<br>dB | PCM code is positive one LSB, VDD = 5.0<br>VDC + 100 mVrms |

| SOS       | Spurious Out-of-Band Signals at VFRO Relative to<br>Input PCM code applied:<br>4600 Hz – 20 kHz<br>20 kHz – 50 kHz |          |     | -40<br>-30 | dB<br>dB | 0 dBm0, 300 Hz – 3400 Hz input                             |

### INDUSTRIAL TEMPERATURE RANGE

#### Interchannel Crosstalk

| Parameter | Description                    | Min | Тур | Max | Units | Test Conditions                                                                                                |

|-----------|--------------------------------|-----|-----|-----|-------|----------------------------------------------------------------------------------------------------------------|

| XTx-r     | Transmit to Receive Crosstalk  |     | -85 | -78 | dB    | 300 Hz – 3400 Hz, 0 dBm0 signal into VFXI<br>of interfering channel. Idle PCM code into<br>channel under test. |

| XTR-X     | Receive to Transmit Crosstalk  |     | -85 | -80 | dB    | 300 Hz – 3400 Hz, 0 dBm0 PCM code into<br>interfering channel. VFXI = 0 Vrms for<br>channel under test.        |

| XTx-x     | Transmit to Transmit Crosstalk |     | -85 | -78 | dB    | 300 Hz – 3400 Hz, 0 dBm0 signal into VFXI<br>of interfering channel. VFXI = 0 Vrms for<br>channel under test.  |

| XTR-R     | Receive to Receive Crosstalk   |     | -85 | -80 | dB    | 300 Hz – 3400 Hz, 0 dBm0 PCM code into<br>interfering channel. Idle PCM code into<br>channel under test.       |

Note: Crosstalk into the transmit channels (VFXI) can be significantly affected by parasitic capacitive coupling from GSX and VFRO outputs. PCB layouts should be arranged to minimize these parasitics. The resistor value of Rf (from GSX to VFXI) should be kept as low as possible to minimize crosstalk. The limits given above are based on Rf < 200 kΩ.

#### Intrachannel Crosstalk

| Paran | neter       | Description                   | Min | Тур | Max | Units | Test Conditions                                                      |

|-------|-------------|-------------------------------|-----|-----|-----|-------|----------------------------------------------------------------------|

| ХТХ   | (-R         | Transmit to Receive Crosstalk |     | -80 | -70 | dB    | 300 Hz – 3400 Hz, 0 dBm0 signal into VFXI.<br>Idle PCM code into DR. |

| XTF   | <b>२-</b> Х | Receive to Transmit Crosstalk |     | -80 | -70 | dB    | 300 Hz – 3400 Hz, 0 dBm0 PCM code into<br>DR. VFXI = 0 Vrms.         |

Note: Crosstalk into the transmit channels (VFXI) can be significantly affected by parasitic capacitive coupling from GSX and VFRO outputs. PCB layouts should be arranged to minimize these parasitics. The resistor value of Rf (from GSX to VFXI) should be kept as low as possible to minimize crosstalk. The limits given above are based on Rf < 200 kΩ.

# INDUSTRIAL TEMPERATURE RANGE

# **TIMING CHARACTERISTICS**

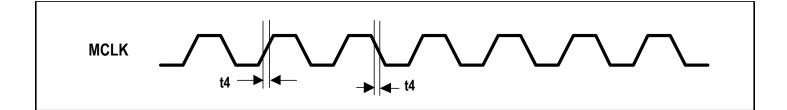

Clock

| Parameter | Description             | Min | Тур | Max | Units | Test Conditions                          |

|-----------|-------------------------|-----|-----|-----|-------|------------------------------------------|

| t1        | BCLK Duty Cycle         | 40  |     | 60  | %     | BCLK = 512 kHz to 8.192 MHz              |

| t2        | BCLK Rise and Fall Time |     |     | 15  | ns    | BCLK = 512 kHz to 8.192 MHz              |

| t3        | MCLK Duty Cycle         | 40  |     | 60  | %     | MCLK = 2.048 MHz, 4.096 MHz or 8.192 MHz |

| t4        | MCLK Rise and Fall Time |     |     | 15  | ns    | MCLK = 2.048 MHz, 4.096 MHz or 8.192 MHz |

| t5        | CCLK Rise and Fall Time |     |     | 15  | ns    | CCLK ≤ 8.192 MHz                         |

### Transmit

| Parameter | Description                | Min | Тур | Max | Units | Test Conditions |

|-----------|----------------------------|-----|-----|-----|-------|-----------------|

| t11       | Data Enabled Delay Time    |     |     | 25  | ns    | CLOAD = 100 pF  |

| t12       | Data Delay Time from BCLK  |     |     | 25  | ns    | CLOAD = 100 pF  |

| t13       | Data Float Delay Time      | 3   |     | 8   | ns    | CLOAD = 0 pF    |

| t14       | Frame sync Hold Time       | 25  |     |     | ns    |                 |

| t15       | Frame sync High Setup Time | 25  |     |     | ns    |                 |

| t16       | TSX Enable Delay Time      |     |     | 25  | ns    | CLOAD = 100 pF  |

| t17       | TSX Disable Delay Time     |     |     | 25  | ns    | CLOAD = 100 pF  |

| t21       | Receive Data Setup Time    | 30  |     |     | ns    |                 |

| t22       | Receive Data Hold Time     | 15  |     |     | ns    |                 |

Note: Timing parameter t12 is referenced to a high-impedance state.

Figure 6. MCLK Timing

Figure 7. Transmit and Receive Timing in Delay Mode

Figure 8. Transmit and Receive Timing in Non-Delay Mode

### INDUSTRIAL TEMPERATURE RANGE

Figure 9. Typical Frame Sync Timing (2 MHz Operation)

### Serial Control Interface Timing

| Parameter | Description                 | Min | Тур | Max | Units          | Test Conditions |

|-----------|-----------------------------|-----|-----|-----|----------------|-----------------|

| t31       | CS Hold Time                | 30  |     |     | ns             |                 |

| t32       | CS Setup Time               | 30  |     |     | ns             |                 |

| t33       | CS to CO Valid Delay Time   |     |     | 30  | ns             |                 |

| t34       | CO Float Delay Time         |     |     | 10  | ns             |                 |

| t35       | CI Setup Time               | 30  |     |     | ns             |                 |

| t36       | CI Hold Time                | 30  |     |     | ns             |                 |

| t37       | CS Idle Time                | 3   |     |     | cycles of CCLK |                 |

| t38       | CCLK to CO Valid Delay Time |     |     | 30  | ns             |                 |

### Figure 10. SLIC Programming Mode Timing

Figure 11. CODEC Programming Mode Timing

Figure 12. Serial Control Interface Timing

Figure 14. Timing Diagram of the Alternative Method to Read From SLIC Status Register

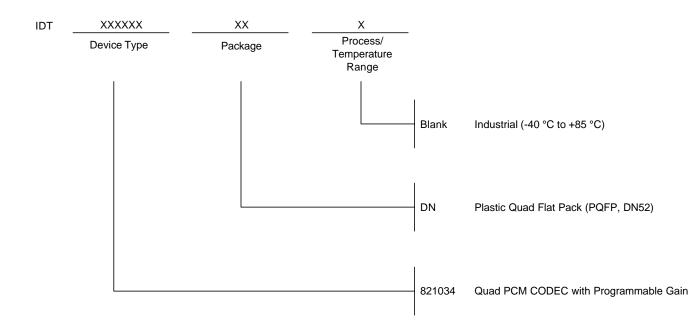

# **ORDERING INFORMATION**

# **Data Sheet Document History**

| 01/16/2002 | pgs. 1, 4-8, 10          |

|------------|--------------------------|

| 01/08/2003 | pgs. 1, 19               |

| 05/13/2003 | pgs. 2, 5, 8, 15, 16, 18 |

for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*

for Tech Support: 408-330-1753 email:telecomhelp@idt.com