查询LTC1484供应商 LTC1484供应商 LTC1484供应商 LTC1484供应商 LTC1484供应商

<sup>●业PCB打样</sup>INIアYM型中増増しEASE Final Electrical Specifications LTC1484

### Low Power EIA485 Transceiver with Receiver Fail-Safe

September 1998

### FEATURES

- No Damage or Latchup to ±15kV ESD (Human Body Model), IEC-1000-4-2 Level 4 Contact (±8kV) and Level 3 (±8kV) Air Gap Specifications

- Guaranteed High Receiver Output State for Floating, Shorted or Terminated Inputs with No Signal Present

- Drives Low Cost Residential Telephone Wires

- Low Power: I<sub>CC</sub> = 700µA Max with Driver Disabled

- I<sub>CC</sub> = 900µA Max for Driver Enable with No Load

- 20µA Max Quiescent Current in Shutdown Mode

- Single 5V Supply

- -7V to 12V Common Mode Range Permits ±7V Ground Difference Between Devices on the Data Line

- Power Up/Down Glitch-Free Driver Outputs

- Up to 32 Transceivers on the Bus

- Pin Compatible with the LTC485

- Available in 8-Lead **MSOP**, PDIP and SO Packages

## **APPLICATIONS**

- Battery-Powered EIA485/EIA422 Applications

- Low Power EIA485/EIA422 Transceiver

- Level Translator

# DESCRIPTION

The LTC<sup>®</sup>1484 is a low power EIA485 compatible transceiver. In receiver mode, it offers a fail-safe feature which guarantees a high receiver output state when the inputs are left open, shorted together or terminated with no signal present. No external components are required to ensure the high receiver output state.

Both driver and receiver feature three-state outputs with separate receiver and driver control pins. The driver outputs maintain high impedance over the entire common mode range when three-stated. Excessive power dissipation caused by bus contention or faults is prevented by a thermal shutdown circuit that forces the driver outputs into a high impedance state.

Enhanced ESD protection allows the LTC1484 to withstand  $\pm 15$ kV (human body model), IEC-1000-4-2 level 4 ( $\pm 8$ kV) contact and level 3 ( $\pm 8$ kV) air discharge ESD without latchup or damage.

The LTC1484 is fully specified over the commercial and industrial temperature ranges and is available in 8-lead MSOP, PDIP and SO packages.

∠, LTC and LT are registered trademarks of Linear Technology Corporation.

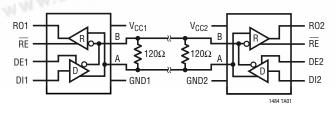

## TYPICAL APPLICATION

EIA485 Interface

## LTC1484

## ABSOLUTE MAXIMUM RATINGS

#### (Note 1)

| Supply Voltage (V <sub>CC</sub> )                           |

|-------------------------------------------------------------|

| Control Input Voltages $-0.3V$ to (V <sub>CC</sub> + 0.3V)  |

| Driver Input Voltage $-0.3V$ to $(V_{CC} + 0.3V)$           |

| Driver Output Voltages7V to 10V                             |

| Receiver Input Voltages (Driver Disabled)12V to 14V         |

| Receiver Output Voltage $-0.3V$ to (V <sub>CC</sub> + 0.3V) |

| Junction Temperature                  | 125°C                                                                |

|---------------------------------------|----------------------------------------------------------------------|

| Operating Temperature Range           |                                                                      |

| LTC1484C                              | $\dots 0^{\circ}C \le T_A \le 70^{\circ}C$                           |

| LTC14841                              | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$ |

| Storage Temperature Range             | 65°C to 150°C                                                        |

| Lead Temperature (Soldering, 10 sec). | 300°C                                                                |

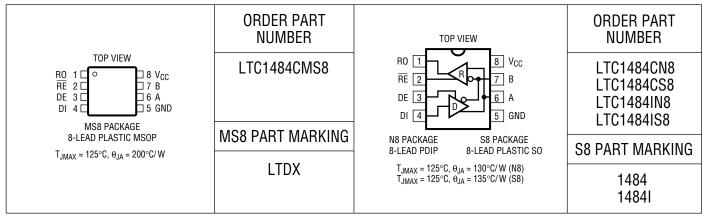

### PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

#### **ELECTRICAL CHARACTERISTICS** $V_{CC} = 5V \pm 5\%$ (Notes 2 and 3) unless otherwise noted.

| SYMBOL            | PARAMETER                                                                                    | CONDITIONS                                                                                                                    |   | MIN      | ТҮР | MAX             | UNITS       |

|-------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---|----------|-----|-----------------|-------------|

| V <sub>OD1</sub>  | Differential Driver Output Voltage (Unloaded)                                                | I <sub>OUT</sub> = 0                                                                                                          |   |          |     | V <sub>CC</sub> | V           |

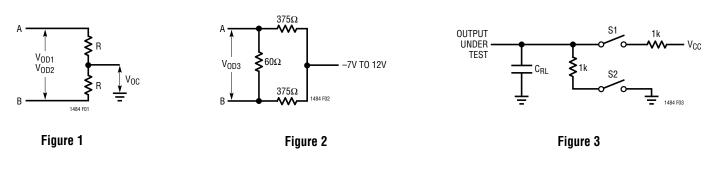

| V <sub>OD2</sub>  | Differential Driver Output Voltage (with Load)                                               | R = 50Ω (RS422)<br>R = 27Ω (RS485) Figure 1<br>R = 22Ω, Figure 1                                                              | • | 2<br>1.5 |     | 5               | V<br>V<br>V |

| V <sub>0D3</sub>  | Differential Driver Output Voltage<br>(with Common Mode)                                     | $V_{TST} = -7V$ to 12V, Figure 2                                                                                              | • | 1.5      |     | 5               | V           |

| $\Delta V_{0D}$   | Change in Magnitude of Driver Differential<br>Output Voltage for Complementary Output States | $R$ = 22 $\Omega$ , 27 $\Omega$ or $R$ = 50 $\Omega$ , Figure 1 $V_{TST}$ = -7V to 12V, Figure 2                              | • |          |     | 0.2             | V           |

| V <sub>OC</sub>   | Driver Common Mode Output Voltage                                                            | R = 22 $\Omega$ , 27 $\Omega$ or R = 50 $\Omega$ , Figure 1                                                                   |   |          |     | 3               | V           |

| $\Delta  V_{0C} $ | Change in Magnitude of Driver Common Mode<br>Output Voltage for Complementary Output States  | $R$ = 22 $\Omega,$ 27 $\Omega$ or $R$ = 50 $\Omega,$ Figure 1                                                                 | • |          |     | 0.2             | V           |

| V <sub>IH</sub>   | Input High Voltage                                                                           | DE, DI, RE                                                                                                                    |   | 2.0      |     |                 | V           |

| V <sub>IL</sub>   | Input Low Voltage                                                                            | DE, DI, RE                                                                                                                    |   |          |     | 0.8             | V           |

| I <sub>IN1</sub>  | Input Current                                                                                | DE, DI, RE                                                                                                                    |   |          |     | ±2              | μA          |

| I <sub>IN2</sub>  | Input Current (A, B)                                                                         | $ \begin{array}{l} DE = 0,  V_{CC} = 0   or   5V,  V_{IN} = 12V \\ DE = 0,  V_{CC} = 0   or   5V,  V_{IN} = -7V \end{array} $ | • |          |     | 1.0<br>-0.8     | mA<br>mA    |

| V <sub>TH</sub>   | Differential Input Threshold Voltage for Receiver                                            | $-7V \le V_{CM} \le 12V$ , DE = 0                                                                                             | • | -0.20    |     | -0.015          | V           |

## **ELECTRICAL CHARACTERISTICS** $v_{cc} = 5V \pm 5\%$ (Notes 2 and 3) unless otherwise noted.

| SYMBOL            | PARAMETER                                                      | CONDITIONS                                                                                           |   | MIN | ТҮР        | MAX        | UNITS    |

|-------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---|-----|------------|------------|----------|

| $\Delta V_{TH}$   | Receiver Input Hysteresis                                      | $V_{CM} = 0V, DE = 0$                                                                                | • |     | ±30        |            | mV       |

| V <sub>OH</sub>   | Receiver Output High Voltage                                   | $I_{OUT} = -4mA$ , $(V_A - V_B) = 200mV$                                                             | • | 3.5 |            |            | V        |

| V <sub>OL</sub>   | Receiver Output Low Voltage                                    | $I_{OUT} = 4mA$ , $(V_A - V_B) = -200mV$                                                             | • |     |            | 0.4        | V        |

| I <sub>0ZR</sub>  | Three-State (High Impedance) Output Current at Receiver        | $\label{eq:VCC} \begin{array}{l} V_{CC} = Max, \ 0.4V \leq V_{OUT} \leq 2.4V, \\ DE = 0 \end{array}$ | • |     |            | ±1         | μA       |

| R <sub>IN</sub>   | Receiver Input Resistance                                      | $-7V \le V_{CM} \le 12V$                                                                             | • | 12  | 22         |            | kΩ       |

| I <sub>CC</sub>   | Supply Current                                                 | No Load, Output Enabled (DE = $V_{CC}$ )<br>No Load, Output Disabled (DE = 0)                        | • |     | 600<br>400 | 900<br>700 | μA<br>μA |

| I <sub>SHDN</sub> | Supply Current in Shutdown Mode                                | $DE = 0, \overline{RE} = V_{CC}, DI = 0$                                                             | • |     | 10         | 20         | μA       |

| I <sub>OSD1</sub> | Driver Short-Circuit Current, V <sub>OUT</sub> = High (Note 4) | $-7V \le V_{OUT} \le 10V$                                                                            |   | 35  |            | 250        | mA       |

| I <sub>OSD2</sub> | Driver Short-Circuit Current, V <sub>OUT</sub> = Low (Note 4)  | $-7V \le V_{OUT} \le 10V$                                                                            |   | 35  |            | 250        | mA       |

| I <sub>OSR</sub>  | Receiver Short-Circuit Current                                 | $0V \le V_{OUT} \le V_{CC}$                                                                          | • | 7   |            | 85         | mA       |

### **SWITCHING CHARACTERISTICS**

| SYMBOL                          | PARAMETER                                        | CONDITIONS                                                                                                         |   | MIN | ТҮР  | MAX  | UNITS |

|---------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---|-----|------|------|-------|

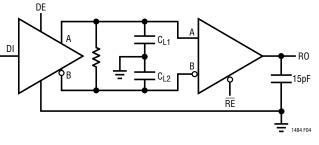

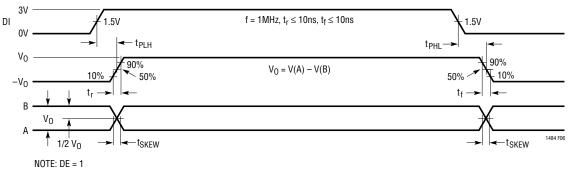

| t <sub>PLH</sub>                | Driver Input to Output                           | $R_{DIFF} = 54\Omega, C_{L1} = C_{L2} = 100 pF$<br>(Figures 4, 6)                                                  | • | 10  | 25   | 60   | ns    |

| t <sub>PHL</sub>                | Driver Input to Output                           | $R_{DIFF} = 54\Omega, C_{L1} = C_{L2} = 100pF$<br>(Figures 4, 6)                                                   | • | 10  | 25   | 60   | ns    |

| t <sub>SKEW</sub>               | Driver Output to Output                          | $\label{eq:RDIFF} \begin{array}{l} R_{DIFF} = 54\Omega, \ C_{L1} = C_{L2} = 100 pF \\ (Figures 4, 6) \end{array}$  | • |     | 5    | 10   | ns    |

| t <sub>r</sub> , t <sub>f</sub> | Driver Rise or Fall Time                         | $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100 pF$<br>(Figures 4, 6)                                               | • | 3   | 15   | 40   | ns    |

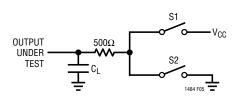

| t <sub>ZH</sub>                 | Driver Enable to Output High                     | C <sub>L</sub> = 100pF (Figures 5, 7) S2 Closed                                                                    | • |     | 40   | 70   | ns    |

| t <sub>ZL</sub>                 | Driver Enable to Output Low                      | C <sub>L</sub> = 100pF (Figures 5, 7) S1 Closed                                                                    | • |     | 40   | 100  | ns    |

| t <sub>LZ</sub>                 | Driver Disable Time from Low                     | $C_L = 15 pF$ (Figures 5, 7) S1 Closed                                                                             | • |     | 40   | 70   | ns    |

| t <sub>HZ</sub>                 | Driver Disable Time from High                    | $C_L = 15 pF$ (Figures 5, 7) S2 Closed                                                                             | • |     | 40   | 70   | ns    |

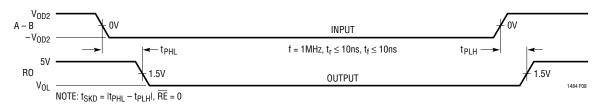

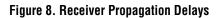

| t <sub>PLH</sub>                | Receiver Input to Output                         | $\label{eq:RDIFF} \begin{array}{l} R_{DIFF} = 54\Omega, \ C_{L1} = C_{L2} = 100 pF, \\ (Figures 4, 8) \end{array}$ | • | 30  | 140  | 200  | ns    |

| t <sub>PHL</sub>                | Receiver Input to Output                         | $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100 pF$ , (Figures 4, 8)                                                | • | 30  | 140  | 200  | ns    |

| t <sub>SKD</sub>                | $It_{PLH} - t_{PHL}I$ Differential Receiver Skew | $R_{DIFF} = 54\Omega, C_{L1} = C_{L2} = 100 pF,$<br>(Figures 4, 8)                                                 |   |     | 5    |      | ns    |

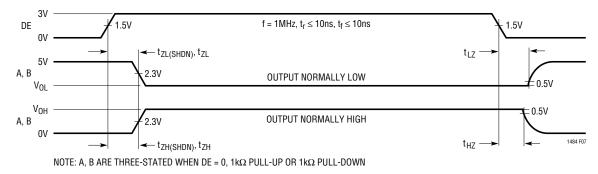

| t <sub>ZL</sub>                 | Receiver Enable to Output Low                    | C <sub>RL</sub> = 15pF (Figures 3, 9) S1 Closed                                                                    | • |     | 20   | 50   | ns    |

| t <sub>ZH</sub>                 | Receiver Enable to Output High                   | C <sub>RL</sub> = 15pF (Figures 3, 9) S2 Closed                                                                    | • |     | 20   | 50   | ns    |

| t <sub>LZ</sub>                 | Receiver Disable from Low                        | C <sub>RL</sub> = 15pF (Figures 3, 9) S1 Closed                                                                    | • |     | 20   | 50   | ns    |

| t <sub>HZ</sub>                 | Receiver Disable from High                       | C <sub>RL</sub> = 15pF (Figures 3, 9) S2 Closed                                                                    | • |     | 20   | 50   | ns    |

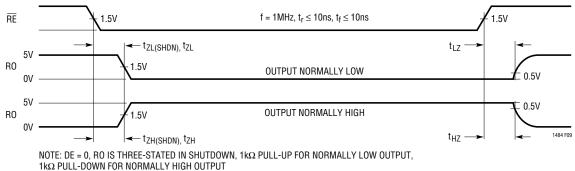

| t <sub>DZR</sub>                | Driver Enable to Receiver Valid                  | $R_{DIFF} = 54\Omega, C_{L1} = C_{L2} = 100 pF$<br>(Figures 4, 10)                                                 | • |     | 1600 | 3000 | ns    |

| f <sub>MAX</sub>                | Maximum Data Rate (Note 5)                       |                                                                                                                    | • | 4   | 5    |      | Mbps  |

| t <sub>SHDN</sub>               | Time to Shutdown (Note 6)                        | $DE = 0, \overline{RE}\uparrow$                                                                                    |   | 50  | 300  | 600  | ns    |

#### **SWITCHING CHARACTERISTICS** $V_{CC} = 5V \pm 5\%$ (Notes 2 and 3) unless otherwise noted.

| SYMBOL                | PARAMETER                                    | CONDITIONS                                         |   | MIN | ТҮР | MAX | UNITS |

|-----------------------|----------------------------------------------|----------------------------------------------------|---|-----|-----|-----|-------|

| t <sub>zh(shdn)</sub> | Driver Enable from Shutdown to Output High   | $C_L$ = 100pF (Figures 5, 7) S2 Closed,<br>DI = DE | • |     | 40  | 100 | ns    |

| t <sub>ZL(SHDN)</sub> | Driver Enable from Shutdown to Output Low    | $C_L = 100 pF$ (Figures 5, 7) S1 Closed,<br>DI = 0 | • |     | 40  | 100 | ns    |

| t <sub>zh(shdn)</sub> | Receiver Enable from Shutdown to Output High | $C_L = 15pF$ (Figures 3, 9) S2 Closed,<br>DE = 0   | • |     |     | 10  | μs    |

| t <sub>zl(shdn)</sub> | Receiver Enable from Shutdown to Output Low  | $C_L = 15pF$ (Figures 3, 9) S1 Closed,<br>DE = 0   | • |     |     | 10  | μs    |

The  $\bullet$  denotes specifications which apply over the full specified temperature range.

**Note 4:** For higher ambient temperatures, the part may enter thermal shutdown during short-circuit conditions.

**Note 6:** Time for  $I_{CC}$  to drop to  $I_{CC}/2$  when the receiver is disabled.

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: All typicals are given for  $V_{CC}$  = 5V and  $T_A$  = 25°C.

**Note 3:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground unless otherwise specified.

PIN FUNCTIONS

**R0 (Pin 1):** Receiver Output. If the receiver output is enabled ( $\overline{RE}$  low) and the part is not in shutdown, RO is high if (A – B) > V<sub>TH(MAX)</sub> and low if (A – B) < V<sub>TH(MIN)</sub>. RO is also high if the receiver inputs are open or shorted together, with or without a termination resistor.

**RE** (**Pin 2**): Receiver Output Enabled. A high on this pin three-states the receiver output (RO) and a low enables it.

**DE (Pin 3):** Driver Enable Input. DE = high enables the output of the driver with the driver outputs determined by the DI pin. DE = low forces the driver outputs into a high impedance state. The LTC1484 enters shutdown when both receiver and driver outputs are disabled ( $\overline{RE}$  is high and DE is low).

**DI (Pin 4):** Driver Input. When the driver outputs are enabled (DE high), DI high takes the A output high and the B output low. DI low takes the A output low and the B output high.

#### GND (Pin 5): Ground.

Note 5: Guaranteed by design.

**A (Pin 6):** Driver Output/Receiver Input. The input resistance is typically 22k when the driver is disabled (DE = 0). When the driver is enabled, the A output follows the logic level at the DI pin.

**B** (Pin 7): Driver Output/Receiver Input. The input resistance is typically 22k when the driver is disabled (DE = 0). When the driver is enabled, the B output is inverted from the logic level at the DI pin.

**V<sub>CC</sub> (Pin 8):** Positive Supply.  $4.75V \le V_{CC} \le 5.25V$ . A  $0.1\mu$ F bypass capacitor is recommended.

### FUNCTION TABLES

Note: Z = high impedance, X = don't care

#### Driver

| INPUTS |    |    | OUTI | PUTS |

|--------|----|----|------|------|

| RE     | DE | DI | В    | Α    |

| Х      | 1  | 1  | 0    | 1    |

| Х      | 1  | 0  | 1    | 0    |

| 0      | 0  | Х  | Z    | Z    |

| 1      | 0  | Х  | Ζ*   | Z*   |

Receiver

|    | OUTPUTS |                       |    |

|----|---------|-----------------------|----|

| RE | DE      | A – B                 | RO |

| 0  | 0       | ≥V <sub>TH(MAX)</sub> | 1  |

| 0  | 0       | ≤V <sub>TH(MIN)</sub> | 0  |

| 0  | 0       | Inputs Open           | 1  |

| 0  | 0       | Inputs Shorted        | 1  |

| 1  | Х       | Х                     | Z† |

<sup>†</sup>Shutdown mode for LTC1484 if DE = 0. Table valid with or without termination resistors.

#### **TEST CIRCUITS**

\*Shutdown mode for LTC1484

Figure 4

Figure 5

#### SWITCHING TIME WAVEFORMS

Figure 7. Driver Enable and Disable Timing

2 PULL-DUWN FOR NORMALLY HIGH OUTPUT

Figure 9. Receiver Enable and Shutdown Timing

#### SWITCHING TIME WAVEFORMS

### **APPLICATIONS INFORMATION**

#### Low Power Operation

The LTC1484 has a quiescent current of  $900\mu$ A max when the driver is enabled. With the driver in three-state, the supply current drops to  $700\mu$ A max. The difference in these supply currents is due to the additional current drawn by the internal 22k receiver input resistors when the driver is enabled. Under normal operating conditions, the additional current is overshadowed by the 50mA current drawn by the external termination resistor.

#### **Receiver Open-Circuit Fail-Safe**

Some encoding schemes require that the output of the receiver maintain a known state (usually a logic 1) when data transmission ends and all drivers on the line are forced into three-state. Earlier EIA485 receivers with a weak pull-up at the A input will give a high output only when the inputs are floated. When terminated or shorted together, the weak pull-up is easily defeated causing the receiver output to go low. External components are needed if a high receiver output is mandatory. The receiver of the LTC1484 has a fail-safe feature which guarantees the output to be in a logic 1 when the receiver inputs are left open or shorted together, regardless of whether the termination resistor is present or not.

In encoding schemes where the required known state is a low, external components are needed for the LTC1484 and other EIA485 parts.

Fail-safe is achieved by making the receiver trip points fall within the  $V_{TH(MIN)}$  to  $V_{TH(MAX)}$  range. When any of the listed receiver input conditions exist, the receiver inputs are effectively at OV and the receiver output goes high.

The receiver fail-safe mechanism is designed to reject fast common mode steps (–7V to 12V in 10ns) switching at 100kHz typ. This is achieved through an internal carrier detect circuit similar to the LTC1482. This circuit has built-in delays to prevent glitches while the input swings between  $\pm V_{TH(MAX)}$  levels. When all the drivers connected to the receiver inputs are three-stated, the internal carrier detect signal goes low to indicate that no differential signal is present. When any driver is taken out of three-state, the carrier detect signal takes 1.6µs typ (see t<sub>DZR</sub>) to detect the enabled driver. During this interval, the transceiver output (RO) is forced to the fail-safe high state. After 1.6µs, the receiver will respond normally to changes in driver output.

If the part is taken out of shutdown mode with the receiver inputs floating, the receiver output takes about 10 $\mu$ s to leave three-state. If the receiver inputs are actively driven to a high state, the outputs go high after about 5.5 $\mu$ s (see t<sub>ZL(SHDN</sub>)).

## **APPLICATIONS INFORMATION**

#### Shutdown Mode

The receiver output (RO) and the driver outputs (A, B) can be three-stated by taking the  $\overline{RE}$  and DE pins high and low respectively. Taking  $\overline{RE}$  high and DE low at the same time puts the LTC1484 into shutdown mode and I<sub>CC</sub> drops to 20µA max.

In some applications (see CDMA), the A and B lines are pulled to  $V_{CC}$  or GND through external resistors to force the line to a high or low state when all connected drivers are disabled. In shutdown, the supply current will be higher than  $20\mu$ A due to the additional current drawn through the external pull-up and the 22k input resistance of the LTC1484.

#### ESD Protection

The ESD performance of the LTC1484 A and B pins is characterized to meet  $\pm 15$ kV using the Human Body Model (100pF, 1.5k $\Omega$ ), IEC-1000-4-2 level ( $\pm 8$ kV) contact mode and IEC-1000-4-2 level 3 ( $\pm 8$ kV) air discharge mode.

This means that external voltage suppressors are not required in many applications when compared with parts that are only protected to  $\pm 2kV$ . Pins other than the A and B pins are protected to  $\pm 4.5kV$  typical per the Human Body Model.

When powered up, the LTC1484 does not latch up or sustain damage when the A and B pins are tested using any of the three conditions listed. The data during the ESD event may be corrupted, but after the event the LTC1484 continues to operate normally. The additional ESD protection at the A and B pins is important in applications where these pins are exposed to the external world via connections to sockets.

#### Fault Protection

When shorted to -7V or 10V at room temperature, the short-circuit current in the driver pins is limited by internal resistance or protection circuitry to 250mA. Over the industrial temperature range, the absolute maximum positive voltage at any driver pin should be limited to 10V to avoid damage to the driver pins. At higher ambient

temperatures, the rise in die temperature due to the short-circuit current may trip the thermal shutdown circuit.

When the driver is disabled, the receiver inputs can withstand the entire -7V to 12V EIA485 common mode range without damage.

The LTC1484 includes a thermal shutdown circuit which protects the part against prolonged shorts at the driver outputs. If a driver output is shorted to another output or to  $V_{CC}$ , the current will be limited to 250mA. If the die temperature rises above 150°C, the thermal shutdown circuit three-states the driver outputs to open the current path. When the die cools down to about 130°C, the driver outputs are taken out of three-state. If the short persists, the part will heat again and the cycle will repeat. This thermal oscillation occurs at about 10Hz and protects the part from excessive power dissipation. The average fault current drops as the driver cycles between active and three-state. When the short is removed, the part will return to normal operation.

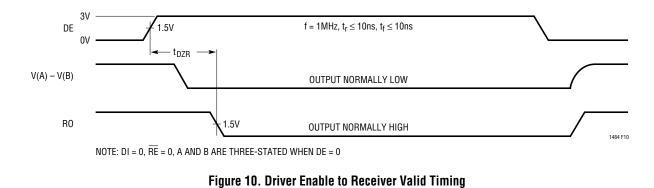

#### **Carrier Detect Multiple Access (CDMA) Application**

In normal half-duplex EIA485 systems, only one node can transmit at a time. If an idle node suddenly needs to gain access to the twisted pair whilst other communications are in progress, it must wait its turn. This delay is unacceptable in safety-related applications. A scheme known as Carrier Detect Multiple Access (CDMA) solves this problem by allowing any node to interrupt on-going communications.

Figure 11 shows four nodes in a typical CDMA communications system. In the absence of any active drivers, bias resistors (1.2k) force a "1" across the twisted pair. All drivers in the system are connected so that when enabled, they transmit a "0". This is accomplished by tying DI low and using DE as the driver data input. A "1" is transmitted by disabling the driver's "0" output and allowing the bias resistors to reestablish a "1" on the twisted pair.

Control over communications is achieved by asserting a "0" during the time an active transmitter is sending a "1". Any node that is transmitting data watches its own

#### **APPLICATIONS INFORMATION**

Figure 11. Transmit "0" CDMA Application

receiver output and expects to see perfect agreement between the two data streams. (Note that the driver inverts the data, so the transmitted and received data streams are actually opposites.) If the simultaneously transmitted and received data streams differ (usually detected by comparing RO and DE with an XOR), it signals the presence of a second, active driver. The first driver falls silent, and the second driver seizes control.

If the LTC1484 is connected as shown in Figure 11, the overhead of XORing the transmitted and received data in hardware or software is eliminated. DE and RE are connected together so the receiver is disabled and its output three-stated whenever a "0" is transmitted. A 1k pull-up ensures a "1" at the receiver output during this condition. The receiver is enabled when the driver is disabled. During this interval the receiver output should also be "1". Thus, under normal operation the receiver output is always "1". If a "0" is detected, it indicates the presence of a second active driver attempting to seize control of communications.

The maximum frequency at which the system in Figure 11 can operate is determined by the cable capacitance, the value of the 1.2k pull-up and pull-down resistors and receiver propagation delay. The external resistors take a longer time to pull the line to a "1" state due to higher source resistance compared to an active driver, thereby affecting the duty cycle of the receiver output at the far end of the line.

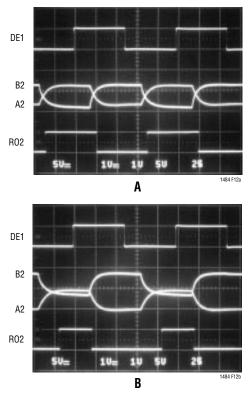

Figure 12a shows a 100kHz DE1 waveform for an LTC1484 driving a 1000-foot shielded twisted-pair (STP) cable and the A2, B2 and RO2 waveforms of a receiving LTC1484 at the far end of the cable. The propagation delay between DE1 of the driver and RO2 at the far end of the line is  $1.8\mu$ s at the rising edge and  $3.7\mu$ s at the falling edge of DE1. The

Figure 12. LTC1484 Driving a 1000 Foot STP Cable

## **APPLICATIONS INFORMATION**

longer delay for the falling edge is due to the larger voltage range the line must swing (typically > 2V compared to 370mV) before the receiver trips high again. The difference in delay affects the duty cycle of the received data and depends on cable capacitance. For a 1-foot STP cable, the delays drop to 0.13µs and 0.4µs. Using smaller valued pull-up and pull-down resistors to equalize the positive and negative voltage swings needed to trip the receivers will reduce the difference in delay and increase the maximum data rate. With  $220\Omega$  resistors, both rising and falling edge delays are 2.2 µs when driving a 1000-foot STP cable as shown in Figure 12b.

The fail-safe feature of the LTC1484 receiver allows a CDMA system to function without the A and B pull-up and pull-down resistors. However, if the resistors are left out, noise margin will be reduced to as low as 15mV and propagation delays will increase significantly. Operation in this mode is not recommended.

Since DE and RE are tied together, the part never shuts down. The receiver inputs are never floating (due to the external bias resistors) so that the  $t_{D7R}$  timing does not apply to this application. The whole system can be changed to actively transmit only a "1" by swapping the pull-up and pull-down resistors in Figure 11, shorting DI to  $V_{CC}$  and connecting the 1k resistor as a pull-down. In this configuration the driver is noninverting and the receiver output RO truly follows DE.

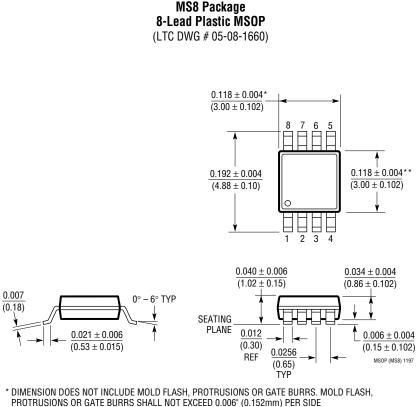

#### PACKAGE DESCRIPTION Dimensions in inches (millimeters), unless otherwise noted.

\* DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

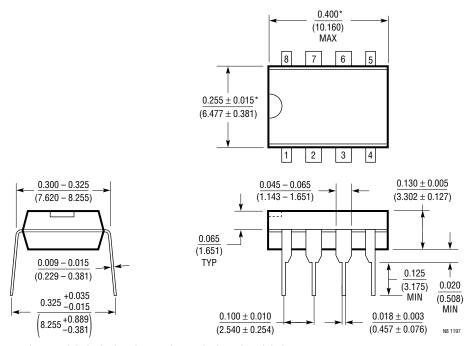

## **PACKAGE DESCRIPTION** Dimensions in inches (millimeters), unless otherwise noted.

N8 Package 8-Lead PDIP (Narrow 0.300) (LTC DWG # 05-08-1510)

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

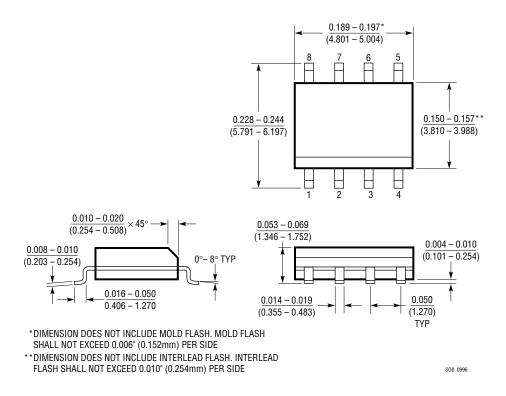

## **PACKAGE DESCRIPTION** Dimensions in inches (millimeters), unless otherwise noted.

S8 Package 8-Lead Plastic Small Outline (Narrow 0.150) (LTC DWG # 05-08-1610)

#### **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                              | COMMENTS                                                                    |

|-------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| LTC485      | 5V Low Power EIA485 Interface Transceiver                                | Low Power                                                                   |

| LTC1480     | 3.3V Ultralow Power EIA485 Transceiver with Shutdown                     | Lower Supply Voltage                                                        |

| LTC1481     | 5V Ultralow Power EIA485 Transceiver with Shutdown                       | Lowest Power                                                                |

| LTC1482     | 5V Low Power EIA485 Transceiver with Carrier Detect Output               | Low Power, High Output State When Inputs are Open,<br>Shorted or Terminated |

| LTC1483     | 5V Ultralow Power EIA485 Low EMI Transceiver with Shutdown               | Low EMI, Lowest Power                                                       |

| LTC1485     | 5V Differential Bus Transceiver                                          | Highest Speed                                                               |

| LTC1487     | 5V Ultralow Power EIA485 with Low EMI, Shutdown and High Input Impedance | Highest Input Impedance, Low EMI, Lowest Power                              |

| LTC1690     | 5V Differential Driver and Receiver Pair with Fail-Safe Receiver Output  | Low Power                                                                   |