# **ASSP**

# USB3.0-SATA Bridge LSI MB86C31

### DESCRIPTION

MB86C31 is USB3.0 external storage solution that complies with Universal Serial Bus 3.0 Specification, Revision 1.0, Universal Serial Bus Specification, Revision 2.0 and Serial ATA Specification Revision 2.6. MB86C31 integrates USB3.0 / USB2.0 / SATA Links and PHYs and 32bit RISC processor to respond to the requests from USB host.

This product offers four different lineups of MB86C311A and MB86C311B whose PKG are LQFP-64 and QFN-48. MB86C311A includes an encryption function and MB86C311B does not have an encryption function.

# APPLICATION

USB3.0 External storage

HDD, SSD, Blu-ray and DVD

# FEATURES

- SuperSpeed (5 Gbps) / high-speed (480 Mbps) / full-speed (12 Mbps)

Compliant to Universal Serial Bus 3.0 Specification, Revision 1.0

Compliant to Universal Serial Bus Specification, Revision 2.0

- UAS Protocol Transport

- Mass Storage Class Bulk-Only Transport

Compliant to Mass Storage Class Bulk-Only Transport, Revision 1.0

- NCQ function

- HID Class (Option)

- SATA Gen2i (3 Gbps) & Gen1i (1.5 Gbps)

Compliant to Serial ATA Specification Revision 2.6

- Supports both ATA and ATAPI device

- Supports Hot-plugging of ATA device

- Supports port multiplier device (Option)

- ATA command pass through function

- Supports over 2TB over HDD & 4K sector HDD

- An Integrated a high performance 32bit RISC MPU

- Several customized function, VID / PID and etc.

- An Integrated high speed encryption block

- IEEE1667 (Option)

- GPIO function including PWM: LQFP package 10 pins, QFN package 9 pins

- SPI for Serial Flash ROM & plural SPI devices

- Embedded SSCG for SuperSpeed USB

- One external crystal (25MHz)

- LQFP-64 & QFN-48 package

# • PIN ASSIGNMENTS(LQFP-64)

**TOP VIEW** RQ/SCEN\_X4/GPI0[8] U2\_EXT12K U2\_AVDP U2\_AVDB VBUS \SS 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 VSS 49 SCEN\_X1/GPIO[0] SCK/GPIO[1] SS\_TXM 50 31 SS\_TXP VDDE 51 30 SS\_VDN SD/NMSEL/GPIO[2] 52 29 NC 53 28 GPI0[3] SS\_RXM 54 GPIO[4] 27 SS\_RXP 55 26 SCEN X2/GPIO[5] 56 SS\_VDN VDDI NC 57 24 VSS NC SYSRST\_X 58 23 SS\_VDU SCEN\_X3/GPIO[6] 59 22 VSS GPI0[7] 60 21 VDDI SYS\_XO 61 20 TMODE[0] SYS\_XI 62 19 TMODE[1] VDDI 63 18 VDDE 64 17 VSS 15 2 10 11 12 13 14 16 ZX M TMODE[2] ST\_RXP 88

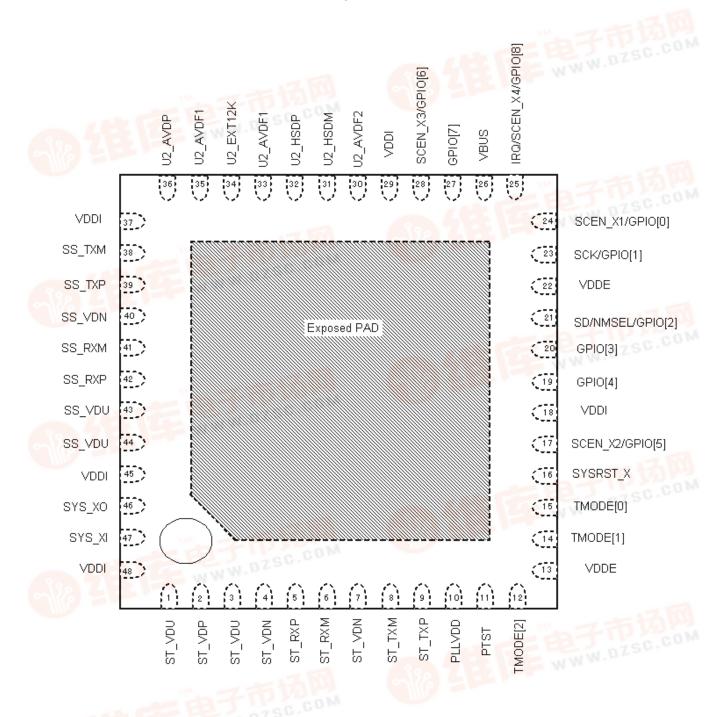

# • PIN ASSIGNMENTS(QFN - 48)

#### **TOP VIEW**

# PIN ASSIGNMENTS TABLE(LQFP-64)

| Pin No. | Pin name            | Pin No.  | Pin name                    | Pin No. | Pin name |

|---------|---------------------|----------|-----------------------------|---------|----------|

| 1       | VSS                 | 23       | SYSRST_X                    | 45      | VDDI     |

| 2       | ST_VDU              | 24       | VSS                         | 46      | VDDE 750 |

| 3       | ST_VDP              | 25       | VDDI                        | 47      | VDDI     |

| 4       | ST_VDU              | 26       | SCEN_X2<br>/GPIO[5]         | 48      | VSS      |

| 5       | ST_VDN              | 27       | GPIO[4]                     | 49      | VSS      |

| 6       | ST_RXP              | 28       | GPIO[3]                     | 50      | SS_TXM   |

| 7       | ST_RXM              | 29       | SD<br>/NMSEL<br>/GPIO[2]    | 51      | SS_TXP   |

| 8       | ST_VDN              | 30       | VDDE                        | 52      | SS_VDN   |

| 9       | ST_TXM              | 31       | SCK<br>/GPIO[1]             | 53      | NC       |

| 10      | ST_TXP              | 32       | SCEN_X1<br>/GPIO[0]         | 54      | SS_RXM   |

| 11      | VSS                 | 33       | IRQ<br>/SCEN_X4<br>/GPIO[8] | 55      | SS_RXP   |

| 12      | PLLVDD              | 34       | VBUS                        | 56      | SS_VDN   |

| 13      | VDDI                | 35       | VSS                         | 57      | NC       |

| 14      | VSS                 | 36       | U2_AVDF2                    | 58      | NC       |

| 15      | PTST                | 37       | U2_HSDM                     | 59      | SS_VDU   |

| 16      | TMODE_2             | 38       | U2_HSDP                     | 60      | VSS      |

| 17      | VDDE                | 39       | U2_AVDF1                    | 61      | SYS_XO   |

| 18      | TMODE_1             | 40       | U2_EXT12K                   | 62      | SYS_XI   |

| 19      | TMODE_0             | 41       | U2_AVDB                     | 63      | VDDI     |

| 20      | VDDI                | 42       | U2_AVDP                     | 64      | VSS      |

| 21      | GPIO_7              | 43       | VSS                         | 自計片     | WWW.     |

| 22      | SCEN_X3<br>/GPIO[6] | 50 44 ON | GPIO_9                      |         |          |

# PIN ASSIGNMENTS TABLE(QFN-48)

| Pin No. | Pin name | Pin No. | Pin name                    | Pin No. | Pin name  |

|---------|----------|---------|-----------------------------|---------|-----------|

| 1       | ST_VDU   | 17      | SCEN_X2<br>/GPIO[5]         | 33      | U2_AVDF1  |

| 2       | ST_VDP   | 18      | VDDI                        | 34      | U2_EXT12K |

| 3       | ST_VDU   | 19      | GPIO[4]                     | 35      | U2_AVDF1  |

| 4       | ST_VDN   | 20      | GPIO[3]                     | 36      | U2_AVDP   |

| 5       | ST_RXP   | 21      | SD<br>/NMSEL<br>/GPIO[2]    | 37      | VDDI      |

| 6       | ST_RXM   | 22      | VDDE                        | 38      | SS_TXM    |

| 7       | ST_VDN   | 23      | SCK<br>/GPIO[1]             | 39      | SS_TXP    |

| 8       | ST_TXM   | 24      | SCEN_X1<br>/GPIO[0]         | 40      | SS_VDN    |

| 9       | ST_TXP   | 25      | IRQ<br>/SCEN_X4<br>/GPIO[8] | 41      | SS_RXM    |

| 10      | PLLVDD   | 26      | VBUS                        | 42      | SS_RXP    |

| 11      | PTST     | 27      | GPIO[7]                     | 43      | SS_VDU    |

| 12      | TMODE[2] | 28      | SCEN_X3<br>/GPIO[6]         | 44      | SS_VDU    |

| 13      | VDDE     | 29      | VDDI                        | 45      | VDDI      |

| 14      | TMODE[1] | 30      | U2_AVDF2                    | 46      | SYS_XO    |

| 15      | TMODE[0] | 31      | U2_HSDM                     | 47      | SYS_XI    |

| 16      | SYSRST_X | 32      | U2_HSDP                     | 48      | VDDI      |

# • PIN DESCRIPTOIN(LQFP - 64)

# 1. System Interface of LQFP - 64

| - |          |     |        |       |              |                                 |  |  |  |  |  |

|---|----------|-----|--------|-------|--------------|---------------------------------|--|--|--|--|--|

|   | Pin name | I/O | Active | PU/PD | Pin<br>count | Function explanation            |  |  |  |  |  |

|   | SYS_XI   | Ι   | -      | -     | 1            | 25MHz crystal Input.            |  |  |  |  |  |

|   | SYS_XO   | Ю   | -      | -     | 1            | 25MHz crystal Input and output. |  |  |  |  |  |

|   | SYSRST_X |     | L      | PU    | 1            | System reset.                   |  |  |  |  |  |

# 2. USB3.0 Interface of LQFP - 64

| Pin name | I/O | Active | PU/PD | Pin<br>count | Function explanation                  |

|----------|-----|--------|-------|--------------|---------------------------------------|

| SS_TXP   | 0   | -      | -     | 1            | SuperSpeed TX+ (Differential signal). |

| SS_TXM   | 0   | -      | -     | 1            | SuperSpeed TX- (Differential signal). |

| SS_RXP   | Ι   | -      | -     | 1            | SuperSpeed RX+ (Differential signal). |

| SS_RXM   | Ι   | 107    | -7 :  | 1            | SuperSpeed RX- (Differential signal). |

| SS_VDN   | -   |        | 173   | 2            | 1.2V Analog power supply.             |

| SS_VDU   | -   | E-W    | MM-   | 1            | 1.2V Analog power supply for PLL.     |

# 3. USB2.0 Interface of LQFP - 64

| Pin name  | I/O | Active | PU/PD | Pin<br>count | Function explanation                                                         |

|-----------|-----|--------|-------|--------------|------------------------------------------------------------------------------|

| U2_EXT12K | 0   | 3      | WW.   | ,            | External resistance pin for internal fixed current circuit.12K $\Omega$ ±1%. |

| U2_HSDP   | 10  | -      | -     | 1            | USB D+.                                                                      |

| U2_HSDM   | Ю   | -      | -     | 1            | USB D                                                                        |

| U2_AVDP   | -   | 1      | -     | 1            | 1.2V Analog power supply for PLL.                                            |

| U2_AVDB   | -   | 1      | -     | 1            | 3.3V Analog power supply for USB driver receiver.                            |

| U2_AVDF1  | -   | -      | -     | _1_          | 3.37 Analog power supply for OSB driver receiver.                            |

| U2_AVDF2  | -   |        | 7-    | 1            | 1.2V Analog power supply for USB driver receiver.                            |

# 4. SATA Interface of LQFP - 64

|   | 11 07 (17 ( 111) |     |        |           |              |                                   |

|---|------------------|-----|--------|-----------|--------------|-----------------------------------|

| ° | Pin name         | I/O | Active | PU/PD     | Pin<br>count | Function explanation              |

|   | ST_TXP           | 0   | -      | -         | 1            | SATA TX+ (Differential signal).   |

|   | ST_TXM           | 0   | ı      | -         | 1            | SATA TX- (Differential signal).   |

|   | ST_RXP           | Ι   | -      | -         | 1            | SATA RX+ (Differential signal).   |

|   | ST_RXM           | Ι   | THE    | =-1       | 1            | SATA RX- (Differential signal).   |

|   | ST_VDP           | -   |        | 7. 10. 10 | 1716C        | 3.3V Analog power supply.         |

|   | ST_VDN           | -   | - W    | 40 -      | 2            | 1.2V Analog power supply.         |

|   | ST_VDU           | -   | -      | -         | 2            | Analog power supply for 1.2V PLL. |

查询MB86C31供应商 5. Peripheral Interface of LQFP - 64

| J. Penpi            | ioru | i iiitoi | iacc o | LQI          | 1 - 0-7                                                                                                                                                                                                                                                                                                    |

|---------------------|------|----------|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin name            | I/O  | Active   | PU/PD  | Pin<br>count | Function explanation                                                                                                                                                                                                                                                                                       |

| SCEN_X1/<br>GPIO[0] | Ю    | L        | -      | 1            | Serial Flash ROM chip enable or General Purpose IO port [0] including PWM.                                                                                                                                                                                                                                 |

| SCK/<br>GPIO[1]     | Ю    | -        | -      | 1            | Serial Flash ROM clock or General Purpose IO port [1] including PWM.                                                                                                                                                                                                                                       |

| SD                  |      |          |        |              | Serial Flash ROM data, selecting normal mode/maintenance mode or General Purpose IO port [2] including PWM*.                                                                                                                                                                                               |

| /NMSEL              | IO   | -        | PU     | 1            | 10. 7 E. E. WWW.                                                                                                                                                                                                                                                                                           |

| /GPIO[2]            |      | Thi      | 7      | Ti           | Note:<br>This pin must not be fixed to PD.                                                                                                                                                                                                                                                                 |

| GPIO[3]             | Ю    |          | PD     | 3750         | General Purpose IO port [3] including PWM.                                                                                                                                                                                                                                                                 |

| GPIO[4]             | 10   | - W      | PU     | 1            | General Purpose IO port [4] including PWM.                                                                                                                                                                                                                                                                 |

| SCEN_X2<br>GPIO[5]  | Ю    | -        | PU     | 1            | Serial Flash ROM chip enable for expansion or General Purpose IO port [5] including PWM.                                                                                                                                                                                                                   |

| SCEN_X3/<br>GPIO[6] | Ю    | -        | PU     | 1            | Serial Flash ROM chip enable for expansion or General Purpose IO port [6] including PWM.                                                                                                                                                                                                                   |

| GPIO[7]             | Ю    | -        | -      | 1            | General Purpose IO port [7] including PWM.                                                                                                                                                                                                                                                                 |

| IRQ/                | 184  | E W      | ww.    | ZSC          | External interruption inputting, Serial Flash ROM chip enable for expansion or General Purpose IO port [8] including PWM.  Note:                                                                                                                                                                           |

| SCEN_X4/<br>GPIO[8] | Ю    | - E      | PD PD  | 1            | When GPIO[8] is used as Serial Flash ROM chip enable, set pull-up resistor on the board. If MB86C31 is turned on without setting pull-up, data might collide. Because enable-signal is asserted by pull-down of internal IO.  Refer to VIH(minimum) of the SPI flash used about the pull-up resistor value |

| GPIO[9]             | Ю    | =- W     | PD     | 1            | General Purpose IO port [9] including PWM.                                                                                                                                                                                                                                                                 |

| VBUS                | I    | Н        | -      | 1            | VBUS monitor.                                                                                                                                                                                                                                                                                              |

# 6. MODE SELECT INTERFACE of LQFP - 64

| _ |          |     |        |       |              | , ,                             |

|---|----------|-----|--------|-------|--------------|---------------------------------|

|   | Pin name | I/O | Active | PU/PD | Pin<br>count | Function explanation            |

|   | PTST     | -1  | Н      | PD    | 176°C        | "No connect". or "connect to 0" |

|   | TMODE[0] | T   | - W    | PU    | 1            | connect to 1 *                  |

|   | TMODE[1] | I   | -      | PD    | 1            | connect to 0.*                  |

|   | TMODE[2] | I   | -      | PD    | 1            | "No connect". or "connect to 0" |

<sup>\*:</sup> Note that TMODE[1] should be connected to 0 and TMODE[0] should be connected to 1.

# 7. POWER/GND of LQFP - 64

|   | 7.1 OWENCIND OF EQTT = 04 |     |        |       |              |                                      |  |  |  |  |  |  |

|---|---------------------------|-----|--------|-------|--------------|--------------------------------------|--|--|--|--|--|--|

| I | Pin name                  | I/O | Active | PU/PD | Pin<br>count | Function explanation                 |  |  |  |  |  |  |

|   | PLLVDD                    | ı   | -      | -     | 1            | 1.2V Analog power supply for PLL.    |  |  |  |  |  |  |

| ı | VDDE                      | -   | -      | -     | 3            | 3.3V power supply for external IO.   |  |  |  |  |  |  |

|   | VDDI                      | -   | -      | -     | 6            | 1.2V power supply for Internal core. |  |  |  |  |  |  |

|   | VSS                       | -   | -      | -     | 10           | GND.                                 |  |  |  |  |  |  |

# 8. OTHERS of LQFP - 64

| _ | <u> </u> |     |        |       |              |                      |

|---|----------|-----|--------|-------|--------------|----------------------|

|   | Pin name | I/O | Active | PU/PD | Pin<br>count | Function explanation |

|   | NC       | _   | -      | -     | 3            | No connect.          |

# • PIN DESCRIPTOIN(QFN - 48)

# 1. System Interface of QFN - 48

|   | Pin name | I/O | Active | PU/PD | Pin<br>count | Function explanation            |

|---|----------|-----|--------|-------|--------------|---------------------------------|

| I | SYS_XI   | Ι   | -      | -     | 1            | 25MHz crystal Input.            |

|   | SYS_XO   | Ю   | -      | -     | 1            | 25MHz crystal Input and output. |

| I | SYSRST_X | -   | L      | PU    | _1           | System reset.                   |

# 2. USB3.0 Interface of QFN - 48

| Pin name | I/O | Active | PU/PD | Pin<br>count | Function explanation                  |

|----------|-----|--------|-------|--------------|---------------------------------------|

| SS_TXP   | 0   | -      | -     | 1            | SuperSpeed TX+ (Differential signal). |

| SS_TXM   | 0   | -      | -     | 1            | SuperSpeed TX- (Differential signal). |

| SS_RXP   | Ι   | -      | -     | 1            | SuperSpeed RX+ (Differential signal). |

| SS_RXM   | П   | 107    | -7:   | 1            | SuperSpeed RX- (Differential signal). |

| SS_VDN   | -   |        | 173   | 150          | 1.2V Analog power supply.             |

| SS_VDU   | -   | E-W    | MM-   | 2            | 1.2V Analog power supply for PLL.     |

# 3. USB2.0 Interface of QFN - 48

| Pin name  | I/O | Active | PU/PD  | Pin<br>count | Function explanation                                                         |  |  |  |  |

|-----------|-----|--------|--------|--------------|------------------------------------------------------------------------------|--|--|--|--|

| U2_EXT12K | 0   | - 1    | F      | -            | External resistance pin for internal fixed current circuit.12K $\Omega$ ±1%. |  |  |  |  |

| U2_HSDP   | 10  | - 111  | 1.18 W | 171          | USB D+.                                                                      |  |  |  |  |

| U2_HSDM   | 10  |        | -      | 1            | USB D                                                                        |  |  |  |  |

| U2_AVDP   | -   | -      | -      | 1            | 1.2V Analog power supply for PLL.                                            |  |  |  |  |

| U2_AVDF1  | -   | -      | -      | 2            | .3V Analog power supply for USB driver receiver.                             |  |  |  |  |

| U2_AVDF2  | -   | -      | -      | 1            | 1.2V Analog power supply for USB driver receiver.                            |  |  |  |  |

# 4. SATA Interface of QFN - 48

|   | Pin name | I/O | Active     | PU/PD | Pin<br>count | Function explanation              |

|---|----------|-----|------------|-------|--------------|-----------------------------------|

|   | ST_TXP   | 0   | - "        | -     | 1            | SATA TX+ (Differential signal).   |

|   | ST_TXM   | 0   | -          | -     | 1            | SATA TX- (Differential signal).   |

|   | ST_RXP   | _   | -          | -     | 1            | SATA RX+ (Differential signal).   |

|   | ST_RXM   | _   | 1          | 1     | 1            | SATA RX- (Differential signal).   |

|   | ST_VDP   |     | ı          | ı     | 1            | 3.3V Analog power supply.         |

|   | ST_VDN   | 1   | χ=         | -27   | 2            | 1.2V Analog power supply.         |

| I | ST_VDU   | -   | <b>3</b> B |       | 2            | Analog power supply for 1.2V PLL. |

查询MB86C31供应商 5 Peripheral Interface of QFN - 48

|   | 5. Penpheral interrace of QFN - 48 |     |        |       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---|------------------------------------|-----|--------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|   | Pin name                           | I/O | Active | PU/PD | Pin<br>count |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|   | SCEN_X1/<br>GPIO[0]                | Ю   | L      | -     | 1            | Serial Flash ROM chip enable or General Purpose IO port [0] including PWM.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|   | SCK/<br>GPIO[1]                    | Ю   | ı      | -     | 1            | Serial Flash ROM clock or General Purpose IO port [1] including PWM.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|   | SD<br>/NMSEL<br>/GPIO[2]           | Ю   | 113    | PU    | 1            | Serial Flash ROM data, selecting normal mode/maintenance mode or General Purpose IO port [2] including PWM.  Note: This pin must not be fixed to PD.                                                                                                                                                                                                                                                                                          |  |  |  |

|   | GPIO[3]                            | Ю   |        | PD    | 375C         | General Purpose IO port [3] including PWM.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ٩ | GPIO[4]                            | Ю   | _ W    | PU    | 1            | General Purpose IO port [4] including PWM.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|   | SCEN_X2<br>GPIO[5]                 | Ю   | 1      | PU    | 1            | Serial Flash ROM chip enable for expansion or General Purpose IO port [5] including PWM.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|   | SCEN_X3/<br>GPIO[6]                | Ю   | 1      | PU    | 1            | Serial Flash ROM chip enable for expansion or General Purpose IO port [6] including PWM.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|   | GPIO[7]                            | Ю   | ı      | -     | 1            | General Purpose IO port [7] including PWM.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|   | IRQ/<br>SCEN_X4/<br>GPIO[8]        | Ю   | 世3     | PD    | To ZSO       | External interruption inputting, Serial Flash ROM chip enable for expansion or General Purpose IO port [8] including PWM*.  Note: When GPIO[8] is used as Serial Flash ROM chip enable, set pull-up resistor on the board. If MB86C31 is turned on without setting pull-up, data might collide. Because enable-signal is asserted by pull-down of internal IO.  Refer to VIH(minimum) of the SPI flash used about the pull-up resistor value. |  |  |  |

|   | VBUS                               | -   | Н      | 7.7   | ·7150        | VBUS monitor.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

# 6. MODE SELECT INTERFACE of QFN - 48

| Pin name | I/O     | Active   | PU/PD | Pin<br>count | Function explanation            |

|----------|---------|----------|-------|--------------|---------------------------------|

| PTST     | Ι       | Н        | PD    | 1            | "No connect". or "connect to 0" |

| TMODE[0] | Ι       | (-)      | PU    | 1            | connect to 1 *                  |

| TMODE[1] | $\perp$ | <u> </u> | PD    | 750          | connect to 0.*                  |

| TMODE[2] |         | W        | PD    | 1            | "No connect". or "connect to 0" |

<sup>\*:</sup> Note that TMODE[1] should be connected to 0 and TMODE[0] should be connected to 1.

# 7. POWER/GND of QFN - 48

| Pin name    | I/O | Active | PU/PD | Pin<br>count | Function explanation                 |

|-------------|-----|--------|-------|--------------|--------------------------------------|

| PLLVDD      | -   | = w    | LWW.  | 1            | 1.2V Analog power supply for PLL.    |

| VDDE        | 7   | -      | -     | 2            | 3.3V power supply for external IO.   |

| VDDI        |     | -      | -     | 5            | 1.2V power supply for Internal core. |

| Exposed PAD | -   | -      | ı     | 1            | GND.                                 |

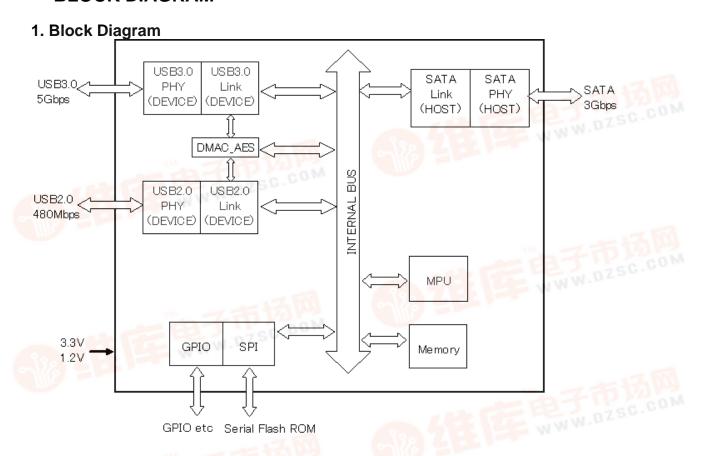

# **BLOCK DIAGRAM**

### 2. USB3.0 PHY

PHY layer of USB3.0. It transfers the data between host and USB3.0 LINK.

#### 3. **USB3.0 LINK**

Link layer of USB3.0. It transfers the data between USB3.0 PHY and Internal bus.

#### 4. USB2.0 PHY

PHY layer of USB2.0. It transfers the data between host and USB2.0 LINK.

# **5. USB2.0 LINK**

Link layer of USB2.0. It transfers the data between USB2.0\_PHY and Initial bus.

# 6. SATA PHY

PHY layer of SATA. It transfers the data between external SATA device and SATA\_LINK. WWW.DZSC.COM

#### 7. SATA LINK

Link layer of SATA. It transfers the data between SATA PHY and Internal bus.

### 8. DMAC AES

A DMA controller with high speed encryption engine. The AES encryption hardware encrypts and decrypts the data if you select to use the MB86C311A. XTS-AES are supported.

: 128bit + 128bit / 256bit + 256bit Key length

Throughput : ≥300 MB/s

### 9. MPU

High performance ARM TM 32bit RISC processor, Cortex-M3TM.

\*: ARM and Cortex-M3 are the trademark of ARM Limited in the EU and other countries.

### 10. MEMORY

Internal RAM used by firmware which is connected with the local bus.

#### 11. SPI

Interface for Serial Flash ROM. Supports ROM devices complied with SPI standard. The firmware and the configuration data are stored in Serial Flash ROM.

#### 12. GPIOs

General Purpose I/O that can be used for the LED control and the switch, etc. All GPIOs have PWM function and it is pssible to set arbitrary Duty.

Cycle time of PWM

MIN: 53nsec MAX: 114sec

### ELECTRICAL SPECIFICATION

1. Absolute maximum rating

| boolate maxima      | iii raaiiig          |      |                                               |       |

|---------------------|----------------------|------|-----------------------------------------------|-------|

| Item                | Sign                 | F    | Unit                                          |       |

| item                | Sign                 | min  | max                                           | Offic |

| Power-supply        | 1.2V power supply *1 | -0.5 | 1.8                                           | V     |

| voltage             | 3.3V power supply *2 | -0.5 | 4.6                                           | V     |

| Input voltage       | FFF VI III           | -0.5 | 3.3 V power supply voltage + 0.5 V ( ≤ 4.6 V) | V     |

| Output voltage      | VO                   | -0.5 | 3.3 V power supply voltage + 0.5 V (≤ 4.6 V)  | V     |

| Storage temperature | Tst                  | -55  | +125                                          | °C    |

<sup>\*1:</sup> SS\_VDN, SS\_VDU, U2\_AVDP, U2\_AVDF2, ST\_VDN, ST\_VDU, PLLVDD, VDDI

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

2. Recommended operating conditions

| Parameter                | sign              | min 🦱 | typ | max | unit |

|--------------------------|-------------------|-------|-----|-----|------|

| Internal Power           | 1.2V power supply | 1.1   | 1.2 | 1.3 | ٧    |

| I/O Power                | 3.3V power supply | 3.0   | 3.3 | 3.6 | ٧    |

| Operating<br>Temperature | Та                | 0     | -   | 70  | °C   |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

<sup>\*2:</sup> U2\_AVDB, U2\_AVDF1, ST\_VDP, VDDE

# 3. DC SPECIFICATION

| 3. DC SPECIFICATION                                 |      |                      |          | Value              |          |       |     |

|-----------------------------------------------------|------|----------------------|----------|--------------------|----------|-------|-----|

|                                                     | Sym  | Power supply         |          | Unit               |          |       |     |

| Parameter                                           | bol  | . e.ve. eapp.y       | Min      | Тур                | Max      | z KW  |     |

| A & costinuo ti cuo                                 |      | 1.2 V power supply - |          | 230                | 320      | mA    |     |

| At activation                                       |      | 3.3 V power supply   | 8004/51  | 7 W                | 9        | mA    |     |

| When USB2.0 is used                                 | 市    | 1.2 V power supply   | 166      | 270                | 360      | mA    |     |

| When OSB2.0 is used                                 | V.DZ | 3.3 V power supply   | -        | 26                 | 39       | ША    |     |

| When USB2.0 is used                                 |      | 1.2 V power supply   | -        | 230                | 320      | mA    |     |

| suspend state                                       |      | 3.3 V power supply   | -        | 7                  | 9        | ША    |     |

| When USB3.0 is used                                 |      | 1.2 V power supply   | - 4H     | 300                | 440      | mA    |     |

| (U0 state)                                          | IDD  | 3.3 V power supply   | WE ALL   | 7                  | 9        |       |     |

| USB3.0                                              |      | 1.2 V power supply   | -        | 250                | 360      | mA    |     |

| U1 state                                            |      | 3.3 V power supply   | -        | 7                  | 9        |       |     |

| USB3.0                                              |      |                      |          | 1.2 V power supply | 100 4/1  | 170 W | 240 |

| U2 state                                            | 市    | 3.3 V power supply   | MB -I-   | 7                  | 9        | MA    |     |

| USB3.0                                              | J.BZ | 1.2 V power supply   | -        | 150                | 210      | ^     |     |

| U3 state                                            |      | 3.3 V power supply   | -        | 7                  | 9        | mA    |     |

| Input High Voltage                                  | VIH  | -                    | 2.1      | - H                | VDDE+0.3 | V     |     |

| Input Low Voltage                                   | Vil  | - 4                  | -0.3     | W                  | 0.7      | V     |     |

| Output High Voltage 3.3 V output current = - 0.1 mA | Voh  | 场的<br>COM            | VDDE-0.2 | -                  | VDDE     | V     |     |

| Output Low Voltage 3.3 V output current = 0.1 mA    | Vol  | 50.0                 | 0        | -                  | 0.2      | ٧     |     |

| Pull-up / Pull-down resistance<br>(GPIO)            | RUP  | -                    | 15       | 33                 | 70       | kΩ    |     |

| Input Leak Current<br>(GPIO)                        | II   | -                    | -10      | 存电                 | 10,50    | μA    |     |

| Input Capacitor<br>(GPIO)                           | Cin  | 摄图- 。                | 18814=   | 10                 | 16       | pF    |     |

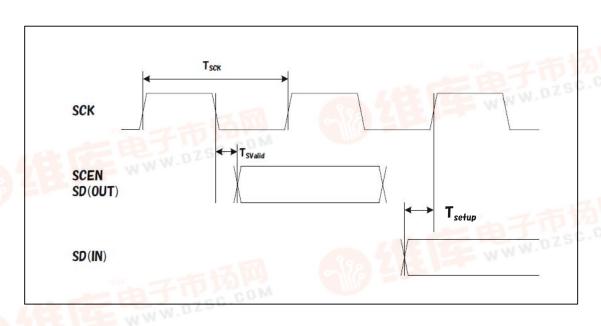

# 4.SPI interface AC specification

| Parameter           | Min. | Max. | Unit | Description                                             |

|---------------------|------|------|------|---------------------------------------------------------|

| T <sub>SCK</sub>    | 53.3 | WW.  | ns   | SCK cycle time                                          |

| T <sub>SValid</sub> | -1.5 | 0.5  | ns   | SCK negative edge to data valid time for SCEN, SD (OUT) |

| T <sub>Setup</sub>  | 13.5 | -    | ns   | Required input setup time to SCK for SD (IN)            |

C=25pF

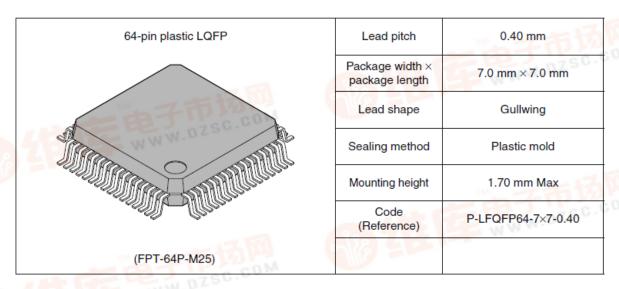

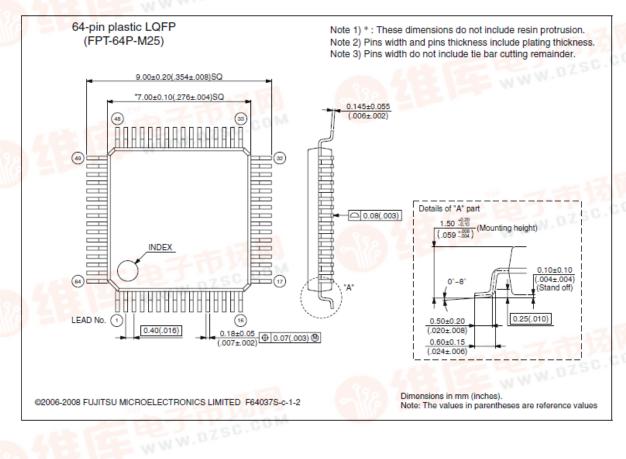

### ORDERING INFORMATION

| Part number      | Package                              | Encryption function |  |

|------------------|--------------------------------------|---------------------|--|

| MB86C311APMC-GE1 | 64-pin Plastic LQFP<br>(FPT-64P-M25) | supported           |  |

| MB86C311BPMC-GE1 | 64-pin Plastic LQFP<br>(FPT-64P-M25) | Non supported       |  |

| MB86C311AWQN-GE1 | 48-pin Plastic QFN                   | supported           |  |

| MB86C311BWQN-GE1 | 48-pin Plastic QFN                   | Non supported       |  |

# POWER SUPPLY CIRCUIT

#### 1. DISPLAY CONDENSER

Between power supply and GND, we recommend you to connect 4-8Chip laminated ceramic capacitor respectively. You arrange the chip laminated ceramic capacitor as much as possible near LSI. Between power supply and GND, we recommend you connect tantalum capacitor or electrolytic capacitor of about 10uF respectively.

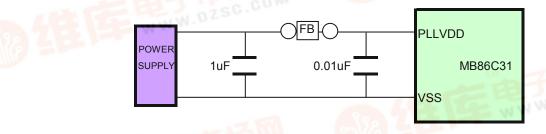

### 2. PLL POWER SUPPLY WIRING

We recommend less noise than 100 mVpp for the power supply of PLL.

The figure below shows the example for reducing the noise, where FB indicates a ferrite bead inductor and the values are reference values.

LIMITED 2010 ALL RIGHTS RESERVED

# ABOUT TURNING ON THE POWER SUPPLY

### 1. Initialization reset

You must put power-on reset to SYSRST\_X when you turn on the power supply. Moreover, please put SYSRST\_X into the state of Low until the input clock is steady.

Set up time is 100 usec. So, negate SYSRST\_X after waiting 100 usec.

### 2. Irregular output

There is a possibility that the output terminal becomes irregular until an internal power supply is steady whenpower supply is turned on.

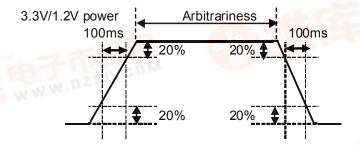

3. Turning on/off the power supply

| item             |                         | Regulator                              | Pin                  | min   | Max | unit |

|------------------|-------------------------|----------------------------------------|----------------------|-------|-----|------|

| Turning on/ off  |                         | Digital power supply for external IO   | VDDE                 | 4     | 100 | ms   |

| the power        | 3.3V<br>Power           | SATA 3.3V analog power supply          | ST_VDP               | 15.37 | 100 | ms   |

| supply           | supply                  | USB2.0 3.3V analog power supply        | U2_AVDF1,<br>U2_AVDB | -     | 100 | ms   |

| NO HILL          | 1.2V<br>Power<br>supply | Analog power supply for PLL            | PLLVDD               | -     | 100 | ms   |

| Turning on/off   |                         | Digital power supply for internal core | VDDI                 |       | 100 | ms   |

| the power supply |                         | SATA 1.2V analog<br>power supply       | ST_VD,<br>ST_VDU     | 1531  | 100 | ms   |

| зирру            |                         | USB3.0 1.2V analog power supply        | SS_VDN、<br>SS_VDU    | -     | 100 | ms   |

|                  |                         | USB2.0 1.2V analog power supply        | U2_AVDF2,<br>U2_AVDP | -     | 100 | ms   |

Turning on/off the power supply

LIMITED 2010 ALL RIGHTS RESERVED

### 4. Note of turning on/ off the power supply

We recommend the following order for turning on/off the power supply.

turning on: 1.2V power source  $\rightarrow$  3.3V source  $\rightarrow$  signal turning of: signal  $\rightarrow$  3.3V power source  $\rightarrow$  1.2Vpower Source

Input the signal after the input clock and the power supply stabilizes.

### 5. Note of PLL power supply

Power supply (PLLVDD, U2\_AVDP) for analog PLL must not rise more than VDDI when you turn on/off the power supply.

### 6. Normal mode / Maintenance mode

Select either maintenance mode or normal mode with GPIO[2] under the below conditions at power on.

- (1) Normal mode: GPIO[2] is High

- (2) Maintenance mode: GPIO[2] keeps low for 1 to 5 seconds, then turns High.

- (3) Error: Others

- \*: The maintenance mode is the mode used for the farm wear debug, and is normally unnecessary. See the USERS MANUAL for details on the Maintenance mode.

# RoHS COMPLIANCE INFORMATION OF LEAD (Pb) FREE VERSION

The LSI products of Fujitsu Microelectronics with "E1" are compliant with RoHS Directive, and has observed the standard of lead, cadmium, mercury, hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE).

A product whose part number has trailing characters "E1" is RoHS compliant.

# Notes when board is designed

### 1. Common notes of differential signal

- 1. Please shorten the wiring of D + /D to cable connector as much as possible.

- 2. Please adjacently wire D + and D . Please keep constantly the line-space and stroke width from the edge to the edge.

- 3. Please make wiring a big R bend of 45° or less. 90° bend is a prohibition.

- 4. Please make shields and avoid other signals which are adjoining for avoiding crosstalk noise from the same layer.

- 5. Please avoid Via. Because, Via is one of the reasons for reflection.

# 2. USB2.0

- Wire the same length for below lines. Suppress the tolerance to 1.5 mm or less. Make them to equal length as much as possible without making them to the meander wiring.

U2 HSDP and U2 HSDM

- 2. It is necessary to take the impedance match of the wiring for the board. Each impedance property is as follows. USB2.0 impedance property: Differential impedance :  $90 \Omega \pm 7\%$ .

- :Single ended impedance:  $45 \Omega \pm 7\%$  (reference).

- 3. The efficiency of a common mode chalk filter depends on an external condition. It may be effective or not effective. Beforehand, we recommend that you design the board which can be inserted and non-inserted common mode chalk filter.

#### 3. USB3.0

1. Wire the same length for below lines. Suppress the tolerance to 1.0 mm or less. Make them to equal length as much as possible without making them to the meander wiring.

SS\_TXP and SS\_TXM

SS\_RXP and SS\_RXM

2. It is necessary to take the impedance match of the wiring for the board.

Each impedance property is as follows.

USB3.0 impedance property: Differential impedance : 90  $\Omega \pm 7\%$ .

: Single ended impedance: 45  $\Omega$  ± 7% (reference).

3. Using a common mode chalk filter is depending to an external condition. It might be effective or not effective. Beforehand, we recommend that you design the board which can be inserted and non-inserted common mode chalk filter.

### 4. SATA

1. Wire the same length for below lines. Suppress the tolerance to 1.0 mm or less. Make them to equal length as much as possible without making them to the meander wiring.

ST\_TXP and ST\_TXM ST\_RXP and ST\_RXM

2. It is necessary to take the impedance match of the wiring for the board. Each impedance property is as follows.

SATA impedance property: Differential impedance : 100  $\Omega \pm 7\%$ .

: Common mode impedance: 35  $\Omega$  ± 7% (reference).

# 5. U2\_EXT12K

- 1. U2\_EXT12K connects GND (VSS) through the external resistance element 12 k $\Omega$ .

- 2. Arrange resistive element External 12 k $\Omega$  near the terminal. Shorten wiring from the pin to resistance as much as possible.

- 3. Use the resistive element External 12 k $\Omega$  whose precision is 12 k $\Omega$  ± 1%.

- 4. When cross talk noise is propagated to U2\_EXT12K, the influence appears in all operations for USB2.0. We forbid other signal wires are adjacent to wiring from U2\_EXT12K to resistive element External 12 k $\Omega$ . We forbid other signal wires cross to wiring from U2\_EXT12K to resistive element External 12 k $\Omega$ .

- It is a prohibition that two or more kinds cross the wiring, even if it is GND and power supply.

- 5. To intercept the noise from other signal wires, it is recommended to shield all sides by the GND.

- 6. Adjust the capacity added to the U2\_EXT12K to 10 pF or less. The value is including parasitic capacitance of wiring with the board and PKG.

- 7. Suppress the amount of the noise in the U2\_EXT12K pin to 50 mV or less by the peak to peak.

- 8. Measure the noise amount under the below conditions for measuring the noise of U2\_EXT12K pin.Location of measurement: pin and GND. Or, it is the vicinity of both ends of resistive element External 12  $k\Omega$ .

Input resistance: 1 M $\Omega$  or more. Input capacitance: 1 pF or less.

Band: 1.5 GHz or more.

# 6. About crystal

- 1. We recommend accuracy of the crystal is 50 ppm or less.

- 2. Influences from other signal wirings such as cross talk noise on crystal oscillator will affect the operation, for example jitter would occur. Countermeasures are necessary such that distance from the signal wire is to be ensured on board or crystal is to be shielded with the stable power supply line.

- 3. The best circuit constant changes by the specification and the ambient surrounding (parasitic capacitance etc. of an external substrate) of the crystal. We recommend you request the investigation (matching investigation) to crystal manufacturer about optimization of circuit constant by product substrate.

### 7. About power supply / GND

- 1. We recommend you make U2\_AVDF1, U2\_AVDF2, U2\_AVDB, and U2\_AVDP to be power supplies which are the exclusive uses of them. We recommend being separated from other power supplies.

- 2. We recommend you make ST\_VDN, ST\_VDP, and ST\_VDU to be power supplies which are the exclusive uses of them. We recommend being separated from other power supplies.

- 3. We recommend you make SS\_VDN, and SS\_VDU to be power supplies which are the exclusive uses of them. We recommend being separated from other power supplies.

- 4. We recommend you make PLLVDD to be power supplies which are the exclusive uses of them. We recommend being separated from other power supplies.

- 5. There is an influence in operation and the characteristic when the noise is caused in a power supply or an analog GND. Please widen the area to the pattern of the power supply and the GND as much aspossible. Especially, please make the GND low impedance. For example, you make the GND to be a plane.

- 6. We recommend the change of an analogue system power supply and a GND are 30 mV or less.

# PACKAGE

# 1. LQFP Package

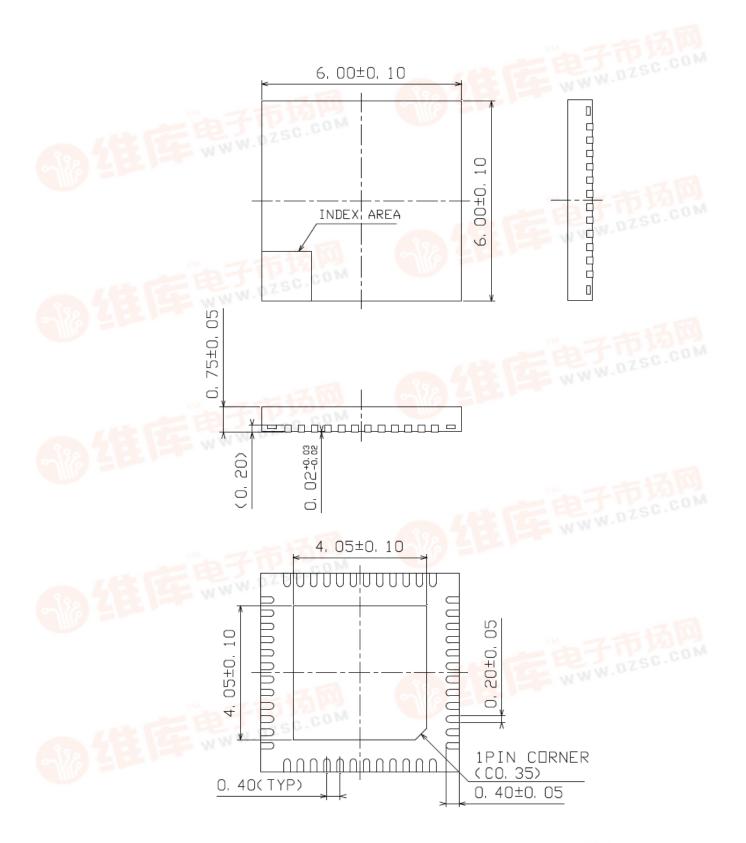

# 查询MB86C31供应商 2. QFN - 48 Package

Specifications are subject to change without notice. For further information please contact each office.

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

All rights reserved, Copyright © FUJITSU SEMICONDUCTOR LIMITED 2010