# **FMS7401/7401L** Digital Power Controller

# **General Description**

The FMS7401/7401L is a family of Digital Power Controllers designed for applications requiring ease of digital based control over analog based implementations. The FMS7401/ 7401L family is an ideal solution to implement ballast control, motor control and battery management functions. This family integrates a wide variety of analog blocks with an 8-bit microcontroller core to offer a complementary feature set with high performance, low power and small size in a single chip.

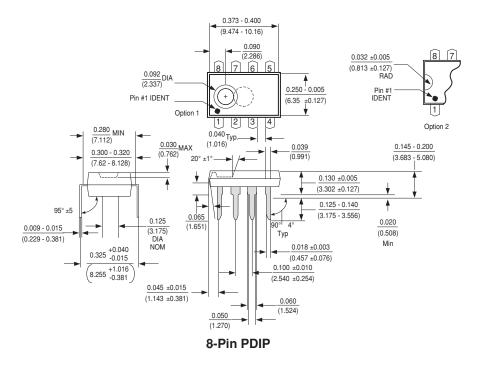

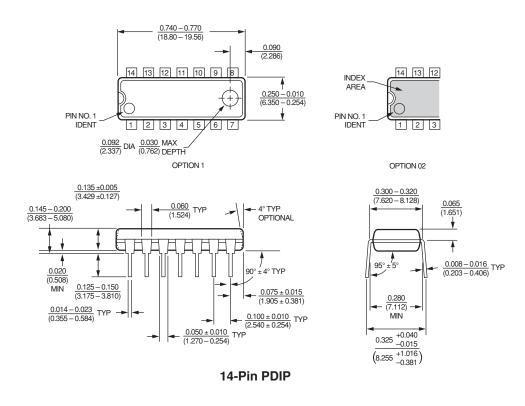

The FMS7401/7401L family is fabricated using CMOS technology and is fully static. This offers significant power savings. This family is available in both 8-pin and 14-pin PDIP packages. SOIC and TSSOP packages are available upon request.

The FMS7401L is intended for applications using a supply voltage in the 2.7V to 3.6V range, while the FMS7401 is suited for applications that use a supply voltage in the 10V to 13.5V range.

# Features

- 8-bit Microcontroller Core

- 1K bytes on-board code EEPROM

- 64 bytes data EEPROM

- 64 bytes SRAM

- Watchdog Reset

- Multi-input Wakeup on all general purpose I/O pins

- Fast 12-bit PWM timer with dead time control and halfbridge output drive

- Input Capture Mode

- 5-Ch 8-bit Analog-to-Digital Converter

- 20 µS conversion time

- Sample and Hold

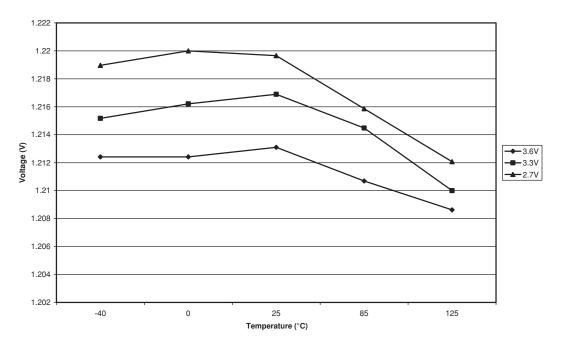

- Internal Voltage Reference (1.21V)

- Gated Auto-sampling Mode

- Auto-zero Amplifier (gain 16)

- Uncommitted Amplifier

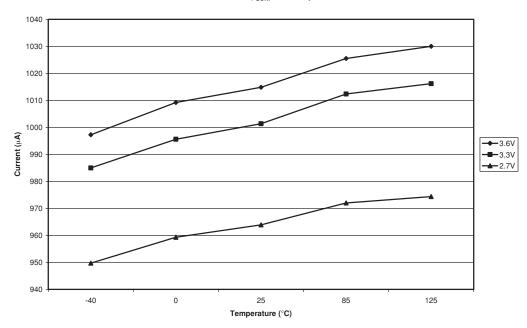

- Internal Current Source Generator (1mA)

- On-chip Oscillator

- No external components

- 1µs instruction cycle time

- On-chip Power-on Reset

- Programmable read and write disable functions

- Memory Mapped I/O

- Programmable Comparator (63 Levels)

- Brown-out Reset

- · Software selectable I/O option

- · Push-pull outputs with tri-state option

- Weak pull-up or high impedance inputs

- Fully static CMOS

- Power Saving Halt Mode

FMS7401L (< 1.3μA @ 3.3V)</li>

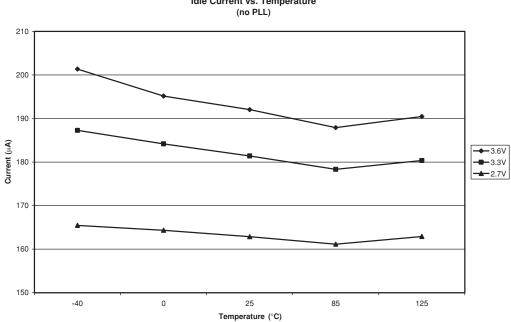

- Power Saving Idle Mode – FMS7401L (< 180μA @ 3.3V)

- Single supply operation - 10V - 13.5V (FMS7401)\*

- -2.7V 3.6V (FMS7401L)

- 40 years data retention

- 100,000 data changes

- 8-/14-pin PDIP, SOIC, and TSSOP packages

- In-circuit programming

- Fast Page-write Programming Mode

|          |                | Program | Data Me | mory (bytes) |     |           |  |

|----------|----------------|---------|---------|--------------|-----|-----------|--|

| Device   | Supply Voltage |         |         | Data EEPROM  | I/O | Pin Count |  |

| FMS7401L | 2.7V – 3.6V    | 1K      | 64      | 64           | 6   | 8         |  |

| FMS7401L | 2.7V - 3.6V    | 1K      | 64      | 64           | 8   | 14        |  |

| FMS7401* | 10V – 13.5V    | 1K      | 64      | 64           | 8   | 14        |  |

Contact your local Fairchild Sales Representative for FMS7401 availability.

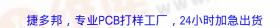

# **Block Diagram**

Figure 1. FMS7401/7401L Block and Connection Diagram

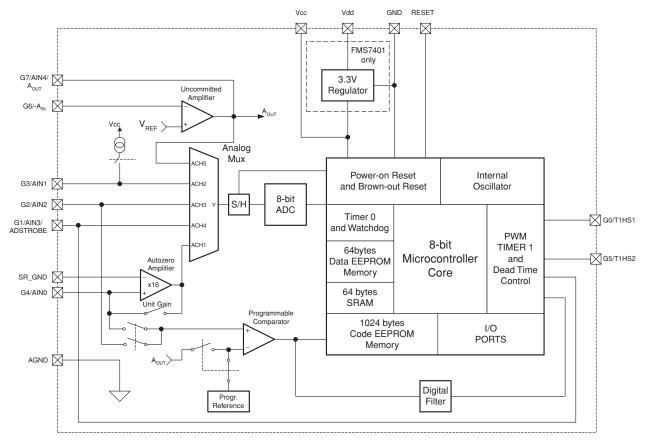

# **Pin Configurations**

FMS7401/7401L 14-Pin PDIP/SOIC/TSSOP

# FMS7401/7401L Pin Definitions

|              | Pin Numbe | r      |                     |                                                                                                                                                                        |  |

|--------------|-----------|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8-           | Pin       | 14-Pin |                     |                                                                                                                                                                        |  |

| PDIP<br>SOIC |           |        |                     | Pin Function Description                                                                                                                                               |  |

| 1            | 3         | 1      | G4/AIN0             | General purpose I/O port (bit 4 of the I/O configuration registers).                                                                                                   |  |

|              |           |        |                     | AIN0 analog input of the ADC (autozero amplifier's positive terminal).                                                                                                 |  |

|              |           |        |                     | Programmable Comparator non-inverting input, if COMPSEL=0.                                                                                                             |  |

| 2            | 4         | 3      | GND                 | Digital ground pin.                                                                                                                                                    |  |

| 3            | 5         | 6      | G2/AIN2             | General purpose I/O port (bit 2 of the I/O configuration registers).                                                                                                   |  |

|              |           |        |                     | AIN2 analog input of the ADC.                                                                                                                                          |  |

|              |           |        |                     | Programmable Comparator non-inverting input, if COMPSEL=1.                                                                                                             |  |

| 4            | 6         | 7      | G1/AIN3/            | General purpose I/O port (bit 1 of the I/O configuration registers).                                                                                                   |  |

|              |           |        | ADSTROBE            | AIN3 analog input of the ADC.                                                                                                                                          |  |

|              |           |        |                     | External digital clock input.                                                                                                                                          |  |

|              |           |        |                     | PWM Timer 1's ADSTROBE output.                                                                                                                                         |  |

| 5            | 7         | 9      | G3/AIN1             | General purpose I/O port (bit 3 of the I/O configuration registers).                                                                                                   |  |

|              |           |        |                     | AIN1 analog input of the ADC.                                                                                                                                          |  |

|              |           |        |                     | Internal current source generator pin.                                                                                                                                 |  |

| 6            | 8         | 10     | G0/                 | General purpose I/O port (bit 0 of the I/O configuration registers).                                                                                                   |  |

|              |           |        | T1HS1               | PWM Timer 1's T1HS1 output.                                                                                                                                            |  |

| 7            | 1         | 12     | G5/                 | General purpose I/O port (bit 5 of the I/O configuration registers).                                                                                                   |  |

|              |           |        | T1HS2               | PWM Timer 1's T1HS2 output.                                                                                                                                            |  |

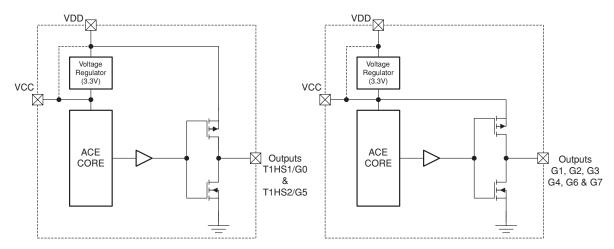

| 8            | 2         | 14     | VCC                 | Supply voltage input for the FMS7401L. In the FMS7401, Vcc is the regulated output.                                                                                    |  |

| -            | -         | 2      | SR_GND              | AIN0 analog input of the ADC (autozero amplifier's negative terminal). SR_GND is internally connected to GND in the 8-pin FMS7401L.                                    |  |

| _            | _         | 4      | G6/-A <sub>IN</sub> | General purpose I/O port (bit 6 of the I/O configuration registers).                                                                                                   |  |

|              |           |        |                     | Uncommitted amplifier negative analog input.                                                                                                                           |  |

| _            | _         | 5      | G7/AIN4/            | General purpose I/O port (bit 7 of the I/O configuration registers).                                                                                                   |  |

|              |           |        | A <sub>OUT</sub>    | AIN4 analog input of the ADC.                                                                                                                                          |  |

|              |           |        |                     | Uncommitted amplifier analog output.                                                                                                                                   |  |

| -            | -         | 8      | AGND                | Analog ground for the FMS7401. In the FMS7401L, AGND is internally connected to GND. Externally, AGND should be left unconnected or connected to GND.                  |  |

| _            | -         | 11     | RESET               | Active low external reset input.                                                                                                                                       |  |

| -            | -         | 13     | VDD                 | High voltage supply input for the FMS7401. In the FMS7401L, VCC is internally connected to VDD. Externally, VDD should either be left unconnected or connected to VCC. |  |

# **Table of Contents**

| <b>FMS7401/7401L</b>                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Description       1         Features       1         Block Diagram       2         Pin Configurations       2         FMS7401/7401L Pin Definitions       3                                                                                                                                                                 |

| <u>1 Reset Circuit</u>                                                                                                                                                                                                                                                                                                              |

| 1.1 FMS7401L Power-on Reset Circuit         8           1.2 FMS7401L External Reset         8           1.3 FMS7401L Brown-out Reset Circuit         8                                                                                                                                                                              |

| <u>2 Clock Circuit</u>                                                                                                                                                                                                                                                                                                              |

| <u>2.1 PLL</u>                                                                                                                                                                                                                                                                                                                      |

| <u>3 Power Saving Modes</u>                                                                                                                                                                                                                                                                                                         |

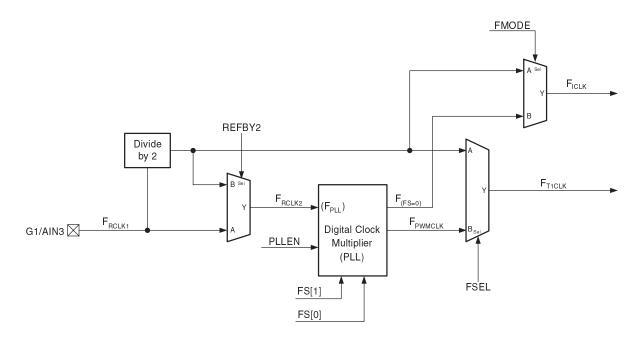

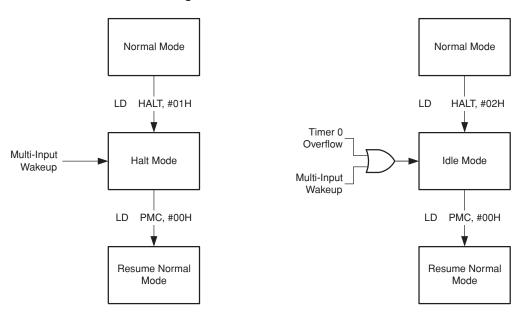

| 3.1 Halt Mode       13         3.1.1 PLL Steps for Halt Mode       13         3.2 Idle Mode       14         3.2.1 PLL Steps for Idle Mode       14                                                                                                                                                                                 |

| <u>4 ADC Circuit</u>                                                                                                                                                                                                                                                                                                                |

| 4.1 ADC Circuit Configuration164.1.1 ADCNTRL1 Register174.1.2 ADCNTRL2 Register194.2 ADC Conversion Modes214.2.1 Analog Input Voltage and its 8-bit Digital Result224.2.2 ADC Gated Auto-sampling Mode224.2.3 ADC Conversion Clock Configuration224.3 Autozero Amplifier234.4 Uncommitted Amplifier234.5 Current Source Generator23 |

| <u>5 Programmable Comparator Circuit</u>                                                                                                                                                                                                                                                                                            |

| 5.1 Programmable Comparator's Voltage Threshold Levels (VLOOP=0)255.2 Hardware Voltage and Current Loop Control (VLOOP=1)285.3 Digital Delay Filter with PWMOFF Output30                                                                                                                                                            |

| <u>6 PWM Timer 1 Circuit</u>                                                                                                                                                                                                                                                                                                        |

| 6.1 PWM Timer 1 Configuration Registers       32         6.1.1 PSCALE Register and Timer 1 Clock Configuration       32         6.1.2 PWM Cycle Configuration Registers       34         6.1.3 Timer 1 Control Register       35         6.2 Pulse Width Modulation (PWM) Mode       37         6.3 Input Capture Mode       40     |

| <u>7 Timer 0 Circuit</u>                                                                                                                                                                                                                                                                                                            |

| 7.1 Idle Timer                                                                                                                                                                                                                                                                                                                      |

| <u>8 I/O Ports</u>                                                                                                                                                                                                                                                                                                                  |

| <u>8.1 I/O Registers</u>                                                                                                                                                                                                                                                                                                            |

| <u>9 Multi-input Wakeup Circuit</u>                                                                                                                                                                                                                                                                                                 |

| 9.1 MIW Configuration Registers                                                                                                                                                                                                                                                                                                     |

# PRODUCT SPECIFICATION

#### FMS7401/7401L

| <b><u>10 8-Bit Microcontroller Core</u></b>    |

|------------------------------------------------|

| <u>10.1 Core Registers</u>                     |

| <u>10.1.1 Accumulator (A)</u>                  |

| <u>10.1.2 X-Pointer (X)</u>                    |

| <u>10.1.3 Program Counter (PC)</u>             |

| <u>10.1.4 Stack Pointer (SP)</u>               |

| <u>10.1.5 Status Register (SR)</u>             |

| 10.1.6 Interrupt Handling                      |

| <u>10.2 Addressing Modes</u>                   |

| <u>11 Device Memory</u>                        |

| 11.1 Initialization Registers                  |

| <u>11.2 Memory Map</u>                         |

| <u>12 In-circuit Programming Specification</u> |

| 12.1 Programming Mode Interface                |

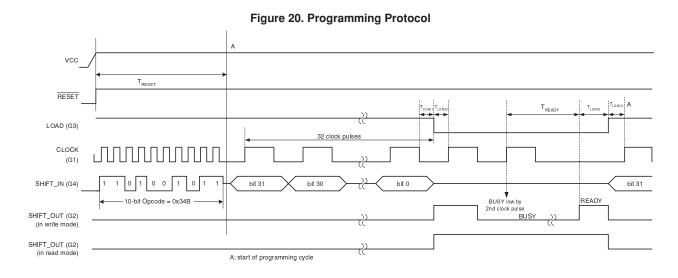

| 12.2 Programming Protocol                      |

| <u>12.2.1 Byte Write Sequence</u>              |

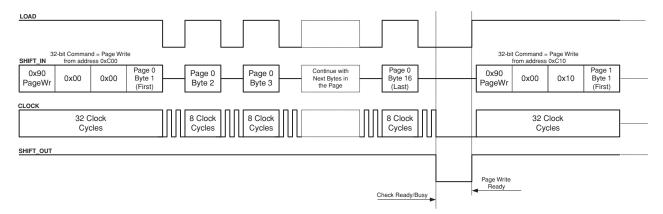

| <u>12.2.2 Page Write Sequence</u>              |

| <u>12.2.3 Byte Read Sequence</u>               |

| 12.2.4 Program Memory Erase                    |

| <u>13 Electrical Characteristics</u>           |

| <u>13.1 FMS7401L (2.7V to 3.6V)</u>            |

| Ordering Information                           |

| Physical Dimensions                            |

# List of Figures

| Figure 1.                                                                                                                                                                          | FMS7401/7401L Block and Connection Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .2                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

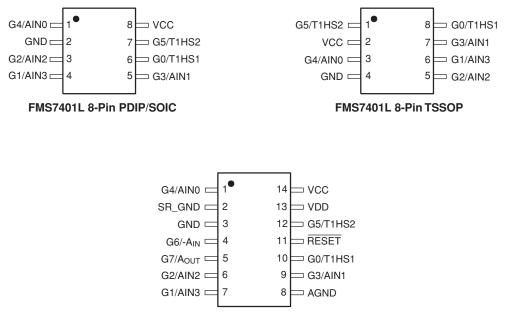

| Figure 2.                                                                                                                                                                          | BOR and POR Circuit Relationship Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .9                                                                                                                                                         |

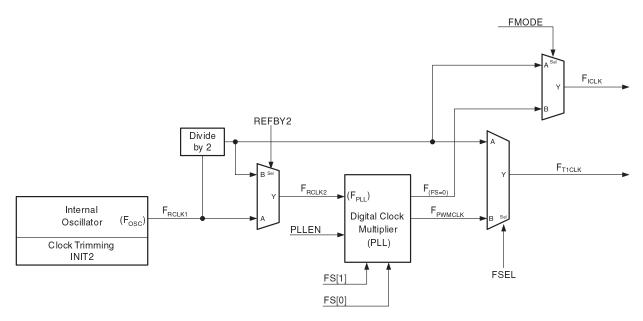

| Figure 3.                                                                                                                                                                          | Internal Clock Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                                                                                                                         |

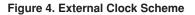

| Figure 4.                                                                                                                                                                          | External Clock Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12                                                                                                                                                         |

| Figure 5.                                                                                                                                                                          | Recommended Halt/Idle Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

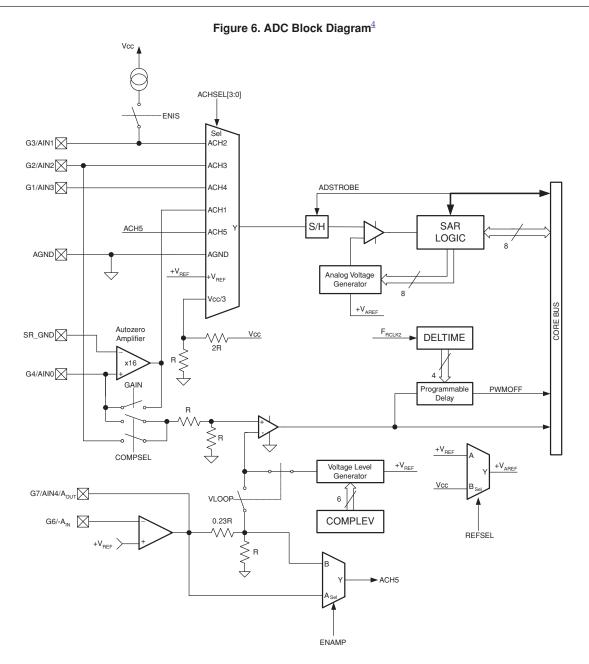

| Figure 6.                                                                                                                                                                          | ADC Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

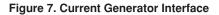

| Figure 7.                                                                                                                                                                          | Current Generator Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |

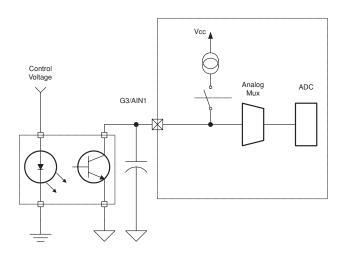

| Figure 8.                                                                                                                                                                          | <u>Programmable Comparator Block Diagram (VLOOP = 0)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26                                                                                                                                                         |

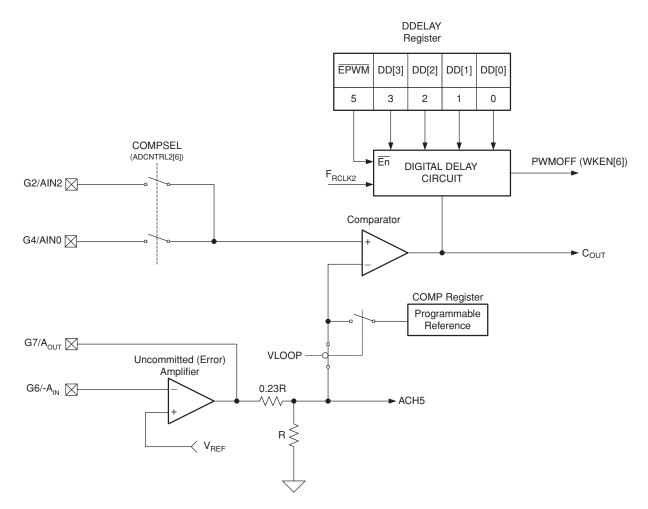

| Figure 9.                                                                                                                                                                          | <u>Programmable Comparator Block Diagram (VLOOP = 1)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                                                                                                                         |

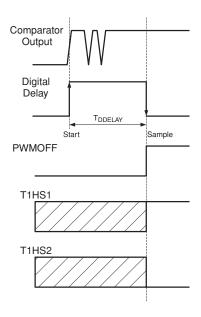

| Figure 10.                                                                                                                                                                         | Digital Delay Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31                                                                                                                                                         |

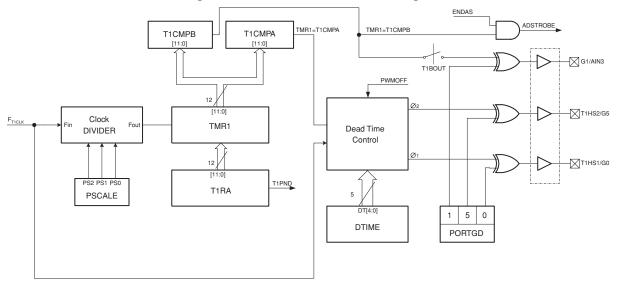

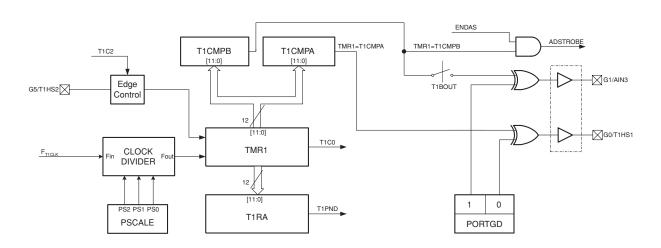

| Figure 11.                                                                                                                                                                         | Timer 1's PWM Mode Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39                                                                                                                                                         |

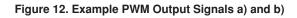

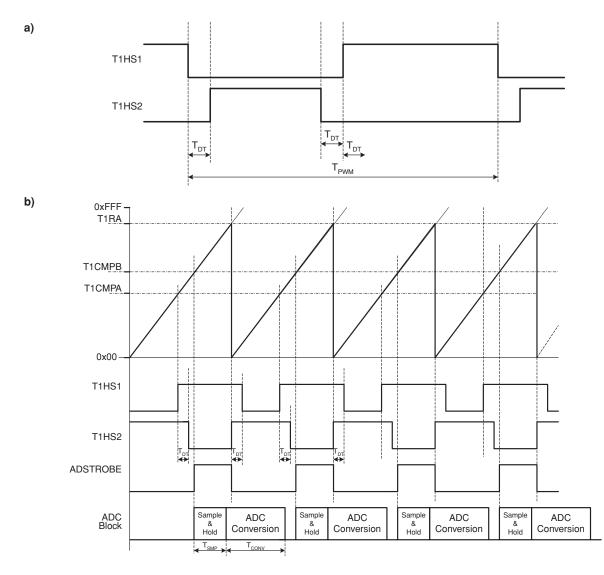

| Figure 12.                                                                                                                                                                         | Example PWM Output Signals a) and b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39                                                                                                                                                         |

| Figure 13.                                                                                                                                                                         | Timer 1's Input Capture Mode Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                                                                                                                         |

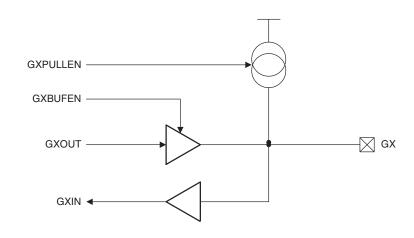

| Figure 14.                                                                                                                                                                         | PORTGD Logic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                            |

| Figure 15.                                                                                                                                                                         | Output Port Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43                                                                                                                                                         |

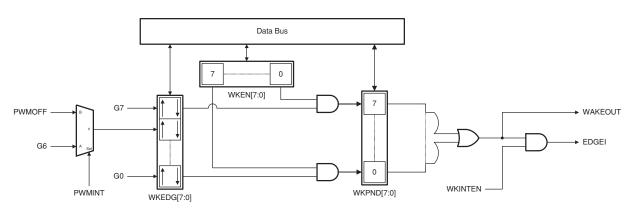

| Figure 16.                                                                                                                                                                         | Multi-input Wakeup (MIW) Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                                                                                                                                                         |

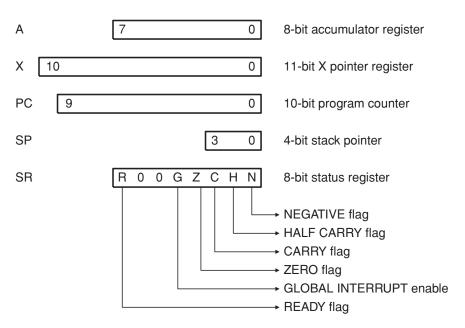

| Figure 17.                                                                                                                                                                         | Core Program Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47                                                                                                                                                         |

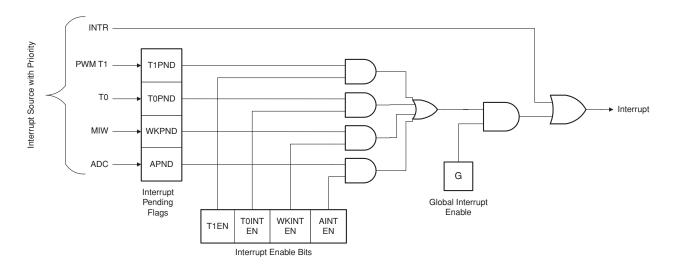

| Figure 18.                                                                                                                                                                         | Basic Interrupt Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50                                                                                                                                                         |

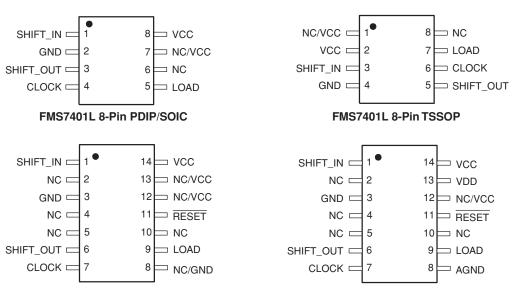

| Figure 19.                                                                                                                                                                         | Programming Mode Pin Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                                                                         |

| Figure 20.                                                                                                                                                                         | Programming Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63                                                                                                                                                         |

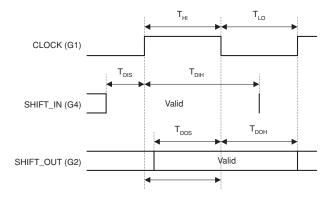

| Figure 21.                                                                                                                                                                         | Serial Data Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                                                                                                         |

| Figure 22.                                                                                                                                                                         | Page Mode Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                                                                                                         |

|                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                            |

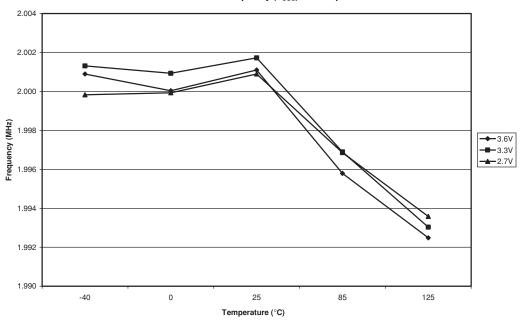

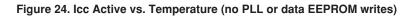

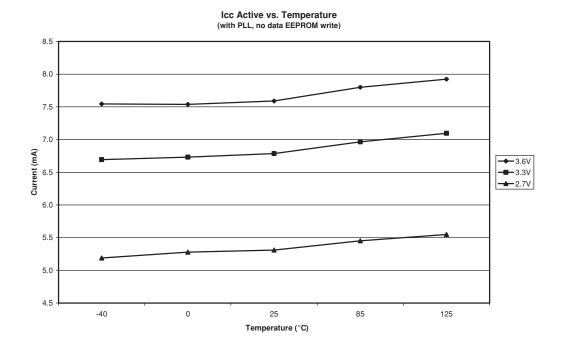

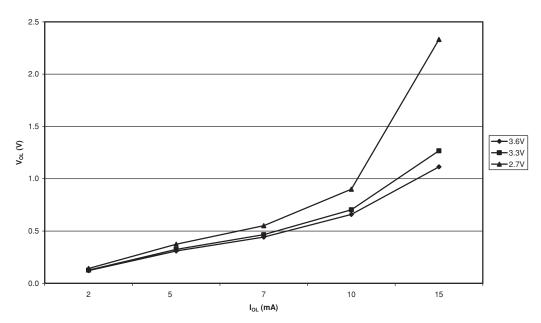

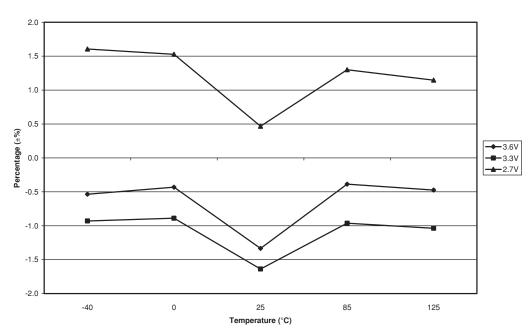

| Figure 23.                                                                                                                                                                         | Internal Oscillator Frequency (Fosc) vs. Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                            |