# Ultra Fast FET-Input Operational Amplifier

## LH0032 / LH0032C

#### **FEATURES**

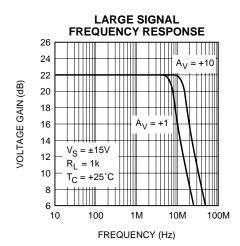

- 500V/µs Slew Rate

- 70MHz Bandwidth

- $10^{12}\Omega$  Input Impedance

- As Low as 2mV Max Input Offset Voltage

- FET Input

- Offset Null with Single Pot

- No Compensation for Gains Above 50

- Peak Output Current to 100mA

#### **GENERAL DESCRIPTION**

The LH0032 is a FET input, high slew rate amplifier capable of driving up to 100mA current.

With wide bandwidth, high slew rate, high input impedance and high current drive capability, LH0032 is an ideal choice for many applications that includes high speed integrator, video amplifier, summing amplifier, high speed D/A converters, etc.

#### **ORDERING INFORMATION**

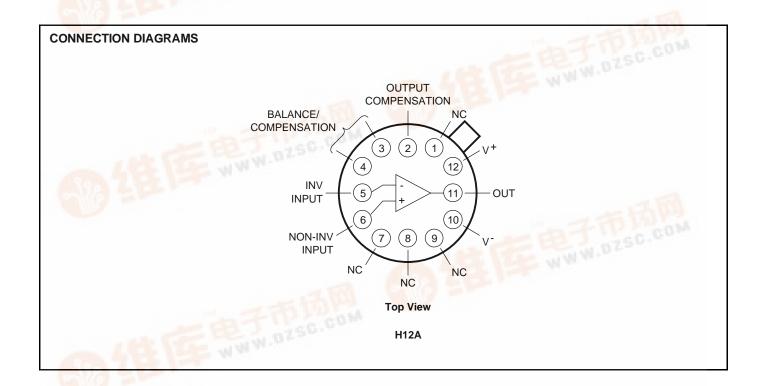

| Part     | Package            | Temperature Range |  |  |  |

|----------|--------------------|-------------------|--|--|--|

| LH0032G  | H12A (TO8-12 Lead) | -55°C to +125°C   |  |  |  |

| LH0032CG | H12A (TO8-12 Lead) | -25°C to +85°C    |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>S</sub> ±18V                                 | Operating Temperature Range, T <sub>A</sub>          |

|---------------------------------------------------------------------|------------------------------------------------------|

| Input Voltage, V <sub>IN</sub>                                      | LH0032G55°C to +125°C                                |

| Differential Input Voltage ±30V or± 2V <sub>S</sub>                 | LH0032CG25°C to +85°C                                |

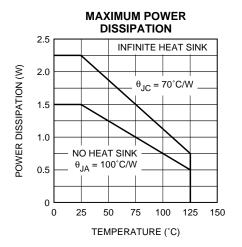

| Power Dissipation, PD                                               | Operating Junction Temperature, T <sub>J</sub> 175°C |

| $T_A = 25^{\circ}C$                                                 | Storage Temperature Range65°C to +150°C              |

| $T_C = 25^{\circ}C.$ 2.2W, derate $70^{\circ}C/W$ to $125^{\circ}C$ | Lead Temp. (Soldering, 10 seconds)                   |

## **DC ELECTRICAL CHARACTERISTICS** $V_S = \pm 15 V$ , $T_{MIN} \le T_A \le T_{MAX}$ unless otherwise noted (Note 1) $(T_A = T_j)$

| SYMBOL                      | PARAMETER                       | LH0032 |       | LH0032C         |     |     | UNITS          | TEST CONDITIONS |                                                       |                                                                               |

|-----------------------------|---------------------------------|--------|-------|-----------------|-----|-----|----------------|-----------------|-------------------------------------------------------|-------------------------------------------------------------------------------|

| STWIBOL                     | TANAMETEN                       | MIN    | TYP   | MAX             | MIN | TYP | MAX            | ONITS           | TEST CONDITIONS                                       |                                                                               |

| Vos                         | Input Offset Voltage            |        | 2     | 5<br>10         |     | 2   | 15<br>20       | mV              |                                                       | $T_A = T_J = 25^{\circ}C \text{ (Note 3)}$                                    |

| ΔVOS/ΔT                     | Average Offset Voltage Drift    |        | 15    | 50              |     | 15  | 50             | μV/°C           |                                                       | (Note 4)                                                                      |

| los                         | Input Offset Current            |        |       | 25<br>250<br>25 |     |     | 50<br>500<br>5 | pA<br>pA<br>nA  | V <sub>IN</sub> = 0                                   | $T_{J} = 25^{\circ}C \text{ (Note 2)}$ $T_{A} = 25^{\circ}C \text{ (Note 3)}$ |

| I <sub>B</sub>              | Input Bias Current              |        |       | 100<br>1<br>50  |     |     | 500<br>5<br>15 | pA<br>nA<br>nA  |                                                       | T <sub>J</sub> = 25°C (Note 2)<br>T <sub>A</sub> = 25°C (Note 3)              |

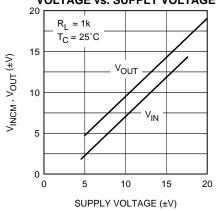

| VINCM                       | Input Voltage Range             | ±10    | ±12   |                 | ±10 | ±12 |                | V               | Note 6                                                |                                                                               |

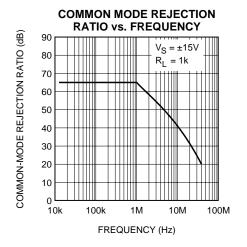

| CMRR                        | Common Mode Rejection<br>Ratio  | 50     | 60    |                 | 50  | 60  |                | dB              | $\Delta V_{IN} = \pm 10 V$                            |                                                                               |

|                             |                                 | 60     | 70    |                 | 60  | 70  |                | dB              | $V_0 = \pm 10V$ , $f = 1kHz$                          | $T_J = 25^{\circ}C$                                                           |

| AvoL Open-Loop Voltage Gain |                                 | 57     |       |                 | 57  |     |                |                 | $R_{L} = 1k\Omega$ (Note 7)                           |                                                                               |

| Vo                          | Output Voltage Swing            | ±10    | ±13.5 |                 | ±10 | ±13 |                | V               | $R_L = 1k\Omega$                                      |                                                                               |

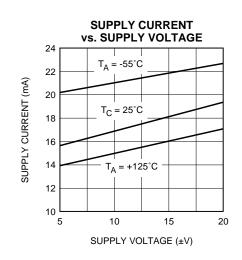

| Is                          | Power Supply Current            |        | 18    | 20              |     | 20  | 22             | mA              | T <sub>A</sub> = 25°C,<br>I <sub>O</sub> = 0 (Note 3) |                                                                               |

| PSRR                        | Power Supply Rejection<br>Ratio | 50     | 60    |                 | 50  | 60  |                | dB              | ΔV <sub>S</sub> = 10V<br>(±5 to ±15V)                 |                                                                               |

#### AC ELECTRICAL CHARACTERISTICS $V_S = \pm 15V$ , $R_L = 1k\Omega$ , $T_J = 25^{\circ}C$ (Note 5)

| SYMBOL         | PARAMETER                            | MIN | TYP | MAX | UNITS | CONDITIONS                        |                        |

|----------------|--------------------------------------|-----|-----|-----|-------|-----------------------------------|------------------------|

| S <sub>R</sub> | Slew Rate                            | 350 | 500 |     | V/µs  | A <sub>V</sub> = +1               |                        |

| ts             | Settling Time to 1% of Final Value   |     | 100 |     |       | Av = -1                           | ΔV <sub>IN</sub> = 20V |

| ts             | Settling Time to 0.1% of Final Value |     | 300 |     | ns    | Ay = -1                           |                        |

| t <sub>R</sub> | Small Signal Rise Time               |     | 8   | 20  |       | $A_V = +1$ , $\Delta V_{IN} = 1V$ |                        |

| t <sub>D</sub> | Small Signal Delay Time              |     | 10  | 25  |       | $AV = +1$ , $\Delta V   N = 1$    |                        |

**Note 1.** LH0032G/CG are 100% production tested as specified at 25°C, Specifications at temperature extremes are verified by testing, periodic characterization, or correlation.

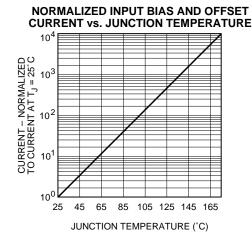

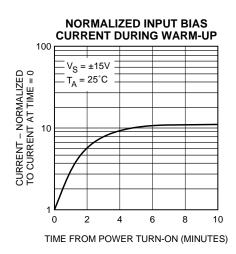

**Note 2.** Specification is at  $25^{\circ}$ C junction temperature due to requirements of high-speed automatic testing. Actual values at operating temperature will exceed the value at  $T_J = 25^{\circ}$ C. When supply voltages are  $\pm 15$ V, no-load operating junction temperature may rise  $40-60^{\circ}$ C above ambient, and more under load conditions. Accordingly,  $V_{OS}$  may change one to several mV, and  $I_B$  and  $I_{OS}$  will change significantly during warm-up. Refer to  $I_B$  and  $I_{OS}$  vs. temperature graph for expected values.

Note 3. Measured in still air 7 minutes after application of power. Guaranteed thru correlated automatic pulse testing.

Note 4.  $\Delta V_{OS}/\Delta T$  is the average value calculated from measurements at 25°C and  $T_{MAX}$ , specifications at temperature are verified by testing, periodic characterization, or correlation.

Note 5. Not 100% production tested; verified by testing, periodic characterization, or correlation.

Note 6. Guaranteed by CMRR test condition.

**Note 7.** Guaranteed thru correlated pulse testing at  $T_j = 25^{\circ}C$ .

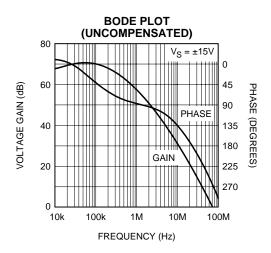

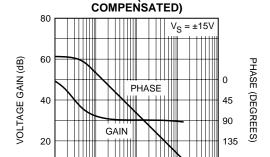

#### TYPICAL PERFORMANCE CHARACTERISTICS

# INPUT VOLTAGE RANGE AND OUTPUT VOLTAGE vs. SUPPLY VOLTAGE

1M

FREQUENCY (Hz)

10M

100M

0

10k

100k

**BODE PLOT (UNITY GAIN**

#### TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

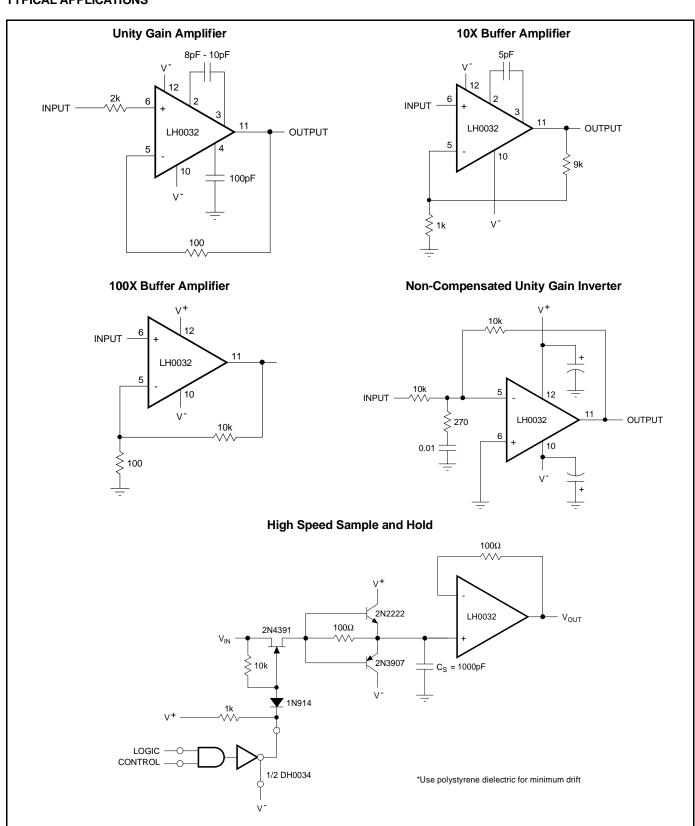

#### **TYPICAL APPLICATIONS**

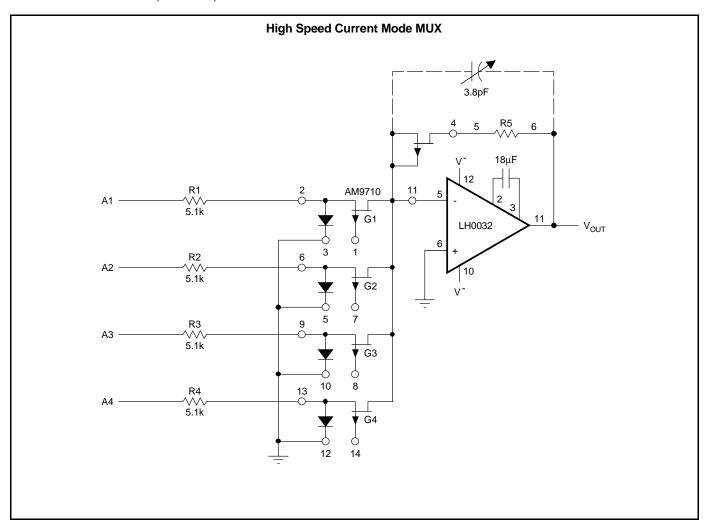

#### **TYPICAL APPLICATIONS** (Continued)

#### **APPLICATION INFORMATION:**

#### **Power Supply Decoupling**

The LH0032, like most high speed circuits, is sensitive to layout and stray capacitance. Power supplies should be bypassed as near to pins 10 and 12 as practicable with low inductance capacitors such as  $0.01\mu F$  disc ceramics. Compensation components should also be located close to the appropriate pins to minimize stray reactances.

#### **Input Current**

Because the input devices are FETs, the input bias current may be expected to double for each  $11^{\circ}\text{C}$  junction temperature rise. This characteristic is plotted in the typical performance characteristics graphs. The device will self-heat due to internal power dissipation after application of power thus raising the FET junction temperature  $40\text{-}60^{\circ}\text{C}$  above free-air ambient temperature when supplies are  $\pm 15\text{V}$ . The device temperature will stabilize within 5-10 minutes after application of power, and the input bias currents measured at that time will be indicative of normal operating currents. An

additional rise would occur as power is delivered to a load due to additional internal power dissipation.

There is an additional effect on input bias current as the input voltage is changed. The effect, common to all FETs, is an avalanche-like increase in gate current as the FET gate-to-drain voltage is increased above a critical value depending on FET geometry and doping levels. This effect will be noted as the input voltage of the LH0032 is taken below ground potential when the supplies are  $\pm 15 \text{V}$ . All of the effects described here may be minimized by operating the device with  $\text{V}_{\text{S}} \leq \pm 15 \text{V}$ .

These effects are indicated in the typical performance curves.

#### **Input Capacitance**

The input capacitance to the LH0032/LH0032C is typically 5pF and thus may form a significant time constant with high value resistors. For optimum performance, the input

capacitance to the inverting input should be compensated by a small capacitor across the feedback resistor. The value is strongly dependent on layout and closed loop gain, but will typically be in the neighborhood of several picofarads.

In the non-inverting configuration, it may be advantageous to bootstrap the case and/or a guard conductor to the inverting input. This serves both to divert leakage currents away from the non-inverting input and to reduce the effective input capacitance. A unity gain follower so treated will have an input capacitance under a picofarad.

#### Compensation

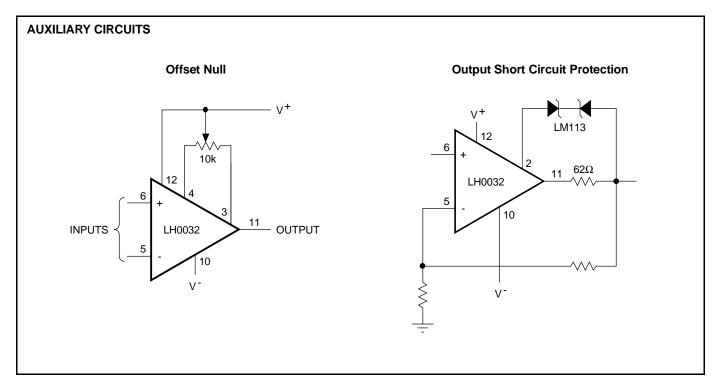

Two compensation schemes may be used, depending on the designer's specific needs.

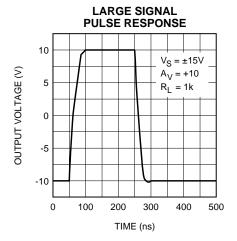

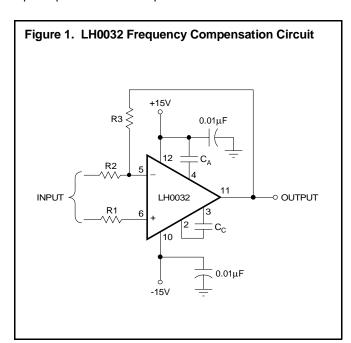

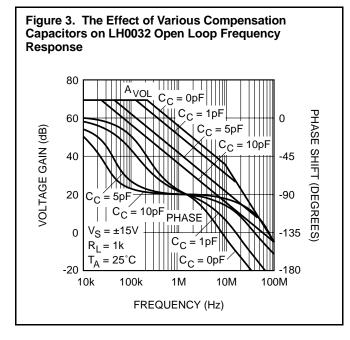

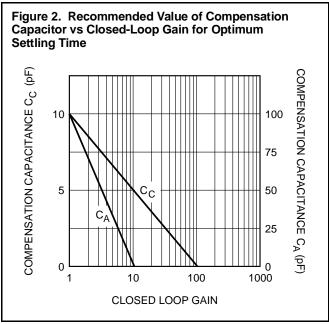

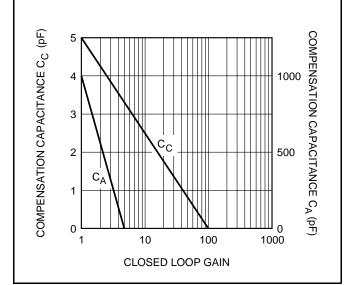

The first technique is shown in *Figure 1*. It offers the best 0.1% settling time for a  $\pm 10V$  square wave input. The compensation capacitors  $C_C$  and  $C_A$  should be selected from *Figure 2* for various closed-loop gains. *Figure 3* shows how the LH0032 frequency response is modified for different value compensation capacitors.

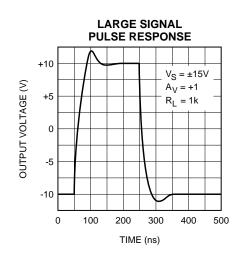

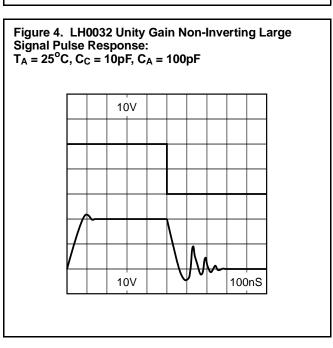

Although this approach offers the shortest settling time, the falling edge exhibits overshoot up to 30% lasting 200 to 300ns. *Figure 4* shows the typical pulse response.

If obtaining minimum ringing at the falling edge is the primary objective, a slight modification to the above is recommended. It is based on the same circuit as that of *Figure 1*.

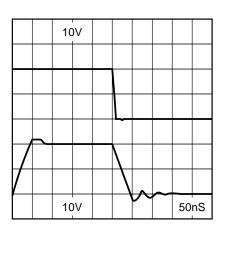

The values of the unity gain compensation capacitors  $C_C$  and  $C_A$  should be modified to 5pF and 1000pF, respectively. *Figure 5* shows the suitable capacitance to use for various closed-loop gains. The resulting unity gain pulse response

Figure 5. Recommended Value of Compensation

Capacitor vs Closed-Loop Gain for Optimum Slew Rate

Figure 6. LH0032 Unity Gain Non-Inverting Large

Signal Pulse Response:  $C_C = 5pF$ ,  $C_A = 1000pF$

waveform is shown in *Figure 6*. The settling time to 1% final value is actually superior to the first method of compensation. However, the LH0032 suffers slow settling thereafter to 0.1% accuracy at the falling edge, and nearly four times as much at the rising edge, compared to the previous scheme. Note, however, that the falling edge ringing is considerably reduced. Furthermore, the slew rate is consistently superior using this compensation because of the smaller value of Miller capacitance  $C_{\rm C}$  required.

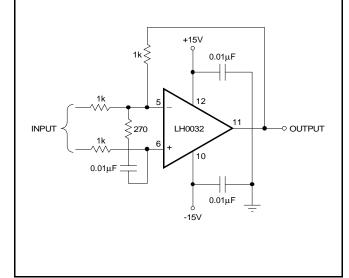

The second compensation scheme works well with both inverting or non-inverting modes. Figure 7 shows the circuit schematic, in which a 270ohm resistor and a  $0.01\mu F$  capacitor are shunted across the inputs of the device. This lag compensation introduces a zero in the loop modifying the response such that adequate phase margin is preserved at unity gain crossover frequency. Note that the circuit requires no additional compensation.

#### **Heat Sinking**

While the LH0032 is specified for operation without any explicit heat sink, internal power dissipation does cause a significant temperature rise. Improved bias current performance can thus be obtained by limiting this temperature rise with a small heat sink such as the Thermalloy No. 2241 or equivalent. The case of the device has no internal connection, so it may be electrically connected to the sink if this is advantageous. However, that this will affect the stray capacitance to all pins and may thus require adjustment of circuit compensation values.

Figure 7. LH0032 Non-Compensated Unity Gain Compensation