4-Channel Voltage Output 15 MHz, Input Bandwidth, 8-Bit Multiplying DACs with 3-Wire Serial Digital Port and Independent References

### **FEATURES**

- Independent References

- 4 Independent 2-Quadrant Multiplying 8-Bit DACs

- Dual Positive (+10 V and +5 V) Supplies or Dual (+5 V) Supplies Capability

- **High Speed:**

- 12.5 MHz Digital Clock Rate

- V<sub>REF to</sub> V<sub>OUT</sub> Settling Time: 150ns to 8-bit

- **Voltage Reference Input Bandwidth:** 15 MHz

- Low Power: 80mW

- Low AC Voltage Reference Feedthrough

- **Excellent Channel-to-Channel Isolation**

- DNL =  $\pm 0.5$  LSB, INL =  $\pm 1$  LSB (typ)

- DACs Matched to  $\pm 0.5\%$  (typ)

- **Very Low Noise**

- Low Harmonic Distortion: 0.25% typical with  $V_{REF} = 1 V p-p @ 1 MHz$

- V<sub>RFF</sub>/2 Output Preset Level

- Latch-Up Free

- **ESD Protection: 2000 V Minimum**

#### **APPLICATIONS**

- Direct High-Frequency Automatic Gain Control

- Video AGC & CCD Level AGC

- Convergence Adjustment for High-Resolution Monitors (Workstations)

#### **GENERAL DESCRIPTION**

The MP7652 is ideal for digital gain control of high frequency analog signals such as video, composite video, CCD and others. The device includes 4-channels of high speed, wide bandwidth, two quadrant multiplying, 8-bit accurate digital-toanalog converter. It includes an output drive buffer per channel capable of driving a ±1mA (typ) load. DNL of better than ±0.5 LSB is achieved with a channel-to-channel matching of typically 0.5%. Stability, matching, and precision of the DACs are achieved by using MPS' thin film technology. Also, excellent channel-to-channel isolation is achieved with EXAR's BiCMOS process which cannot be achieved using a typical CMOS technology.

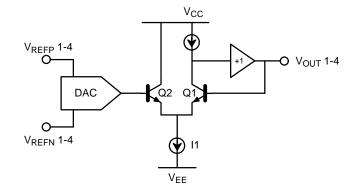

An open loop architecture (patent pending) provides wide

small signal bandwidth from V<sub>REF</sub> to output up to 15 MHz (typ), fast output settling time of 150 ns, and excellent V<sub>REF</sub> feedthrough isolation. The bottom of each DAC reference string is brought out separately for totally isolated operation. In addition, low distortion in the order of 0.25% with a 1 V p-p, 1 MHz signal is achieved.

The combination of a constant input Z and the ability to vary V<sub>REFN</sub> within V<sub>CC</sub> -1.8 and V<sub>EE</sub> +1.5 V allows flexibility for optimum system design.

The MP7652 is fabricated on a junction isolated, high speed BiCMOS (BiCMOS IV<sup>TM</sup>) process with thin film resistors. This process enables precision high speed analog/digital (mixedmode) circuits to be fabricated on the same chip.

## ORDERING INFORMATION

| INFORMATION WWW.DZSG.COM                                             |              |          |            |              |              |  |  |  |

|----------------------------------------------------------------------|--------------|----------|------------|--------------|--------------|--|--|--|

| PackageTemperatureINLDNLGain ErrorTypeRangePart No.(LSB)(LSB)(% FSR) |              |          |            |              |              |  |  |  |

| SOIC                                                                 | -40 to +85°C | MP7652AS | <u>+</u> 1 | <u>+</u> 0.5 | <u>+</u> 1.5 |  |  |  |

| Plastic Dip                                                          | –40 to +85°C | MP7652AN | <u>+</u> 1 | <u>+</u> 0.5 | <u>+</u> 1.5 |  |  |  |

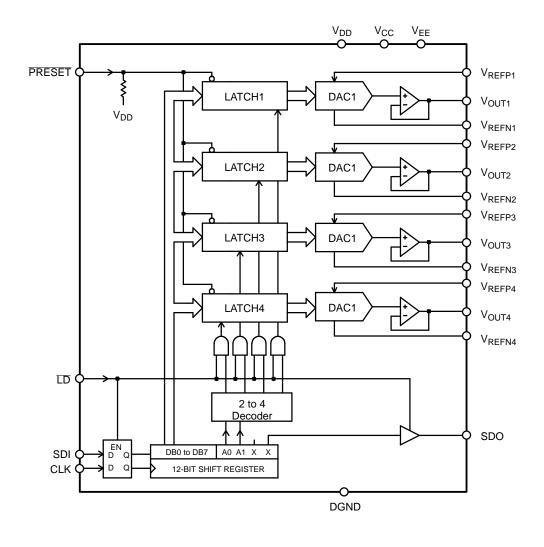

### SIMPLIFIED BLOCK DIAGRAM

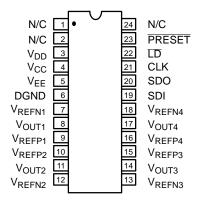

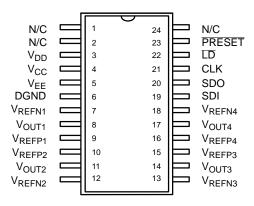

# **PIN CONFIGURATIONS**

24 Pin SOIC (Jedec, 0.300") S24

# **PIN OUT DEFINITIONS**

| PIN NO. | NAME               | DESCRIPTION                    |

|---------|--------------------|--------------------------------|

| 1       | N/C                | No Connection                  |

| 2       | N/C                | No Connection                  |

| 3       | $V_{DD}$           | Digital Positive Supply        |

| 4       | V <sub>CC</sub>    | Analog Positive Supply         |

| 5       | $V_{EE}$           | Analog Negative Supply         |

| 6       | DGND               | Digital Ground                 |

| 7       | V <sub>REFN1</sub> | DAC 1 Negative Reference Input |

| 8       | V <sub>OUT1</sub>  | DAC 1 Output                   |

| 9       | $V_{REFP1}$        | DAC 1 Positive Reference Input |

| 10      | $V_{REFP2}$        | DAC 2 Positive Reference Input |

| 11      | $V_{OUT2}$         | DAC 2 Output                   |

| 12      | $V_{REFN2}$        | DAC 2 Negative Reference Input |

| 13      | $V_{REFN3}$        | DAC 3 Negative Reference Input |

|         |                    |                                |

| PIN NO. | NAME              | DESCRIPTION                                                                                                 |

|---------|-------------------|-------------------------------------------------------------------------------------------------------------|

| 14      | V <sub>OUT3</sub> | DAC 3 Output                                                                                                |

| 15      | $V_{REFP3}$       | DAC 3 Positive Reference Input                                                                              |

| 16      | $V_{REFP4}$       | DAC 4 Positive Reference Input                                                                              |

| 17      | $V_{OUT4}$        | DAC 4 Output                                                                                                |

| 18      | $V_{REFN4}$       | DAC 4 Negative Reference Input                                                                              |

| 19      | SDI               | Serial Data and Address Input                                                                               |

| 20      | SDO               | Serial Data Output                                                                                          |

| 21      | CLK               | Shift Register Clock Input                                                                                  |

| 22      | LD                | Load Data to Selected DAC                                                                                   |

| 23      | PRESET            | Preset all DACs to 1/2 ( $V_{REF} - V_{REFN}$ ). PRESET is internally connected to $V_{DD}$ through 300 kΩ. |

| 24      | N/C               | No Connection                                                                                               |

# **ELECTRICAL CHARACTERISTICS TABLE FOR DUAL SUPPLIES**

Unless Otherwise Noted:  $V_{DD}$  = 5 V,  $V_{CC}$  = +5 V,  $V_{EE}$  = -5 V,  $V_{REFP}$  = 3 V and -3 V, T = 25°C, Output Load = Open, DGND= $V_{REFN}$  = 0 V

|                                                                                                                                             |                                                                         |                           | 25°C                                         |                            |                                         |                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------|----------------------------------------------|----------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                                                                                   | Symbol                                                                  | Min                       | Тур                                          | Max                        | Units                                   | Test Conditions/Comments                                                                                                                        |

| DC CHARACTERISTICS                                                                                                                          |                                                                         |                           |                                              |                            |                                         |                                                                                                                                                 |

| Resolution (All Grades) Differential Non-Linearity Integral Non-Linearity Monotonicity Gain Error Zero Scale Offset Output Drive Capability | N<br>DNL<br>INL<br>GE<br>Z <sub>OFS</sub>                               | 8                         | Guaranteed<br>±1                             | ±0.8<br>±1<br>±1.5<br>±50  | Bits<br>LSB<br>LSB<br>% FSR<br>mV<br>mA | FSR = Full Scale Range <sup>1</sup>                                                                                                             |

| REFERENCE/INV INPUTS                                                                                                                        |                                                                         |                           |                                              |                            |                                         |                                                                                                                                                 |

| Impedance of V <sub>REF</sub> Voltage Range V <sub>REFN</sub> DC Voltage Range                                                              | REF<br>V <sub>R</sub><br>INV Pos.<br>INV Neg.                           | 6<br>V <sub>EE</sub> +1.5 | V <sub>O</sub><br>V <sub>EE</sub> <u>+</u> 1 | 18<br>V <sub>CC</sub> –1.8 | kΩ<br>V<br>V<br>V                       | $V_{REFP}$ Max Swing is $V_{REFN}$ $\pm 3$ $V$                                                                                                  |

| DYNAMIC<br>CHARACTERISTICS <sup>2</sup>                                                                                                     |                                                                         |                           |                                              |                            |                                         | $R_L = 5 \text{ k}\Omega$ , $C_L = 20 \text{ pF}$                                                                                               |

| Input to Output Bandwidth Input to Output Settling Time <sup>6</sup> Small Signal Voltage Reference Input to Output Bandwidth               | ft <sub>r</sub>                                                         |                           | 15<br>150<br>15                              |                            | MHz<br>ns<br>MHz                        | $V_{REFP}$ =1.6 Vp–p, $R_L$ =5k $\Omega$ , to $V_{EE}$ $V_{REFP}$ =1.6 Vp–p, $R_L$ =5k $\Omega$ , to $V_{EE}$ $V_{OUT}$ =50mV p-p above code 16 |

| Small Signal Voltage Reference                                                                                                              | ft <sub>r</sub>                                                         |                           | 15                                           |                            | MHz                                     | V <sub>OUT</sub> =50mV p-p for all codes                                                                                                        |

| Input to Output Bandwidth Voltage Settling from V <sub>REF</sub> to V <sub>DAC</sub> Out                                                    | t <sub>sr</sub>                                                         |                           | 275                                          |                            | ns                                      | $V_{REFP}$ =0 to $V_{REFP}$ = 3V Step <sup>6</sup> to 1 LSB                                                                                     |

| Voltage Settling from Digital Code to V <sub>DAC</sub> Out                                                                                  | t <sub>sd</sub>                                                         |                           | 275                                          |                            | ns                                      | ZS to FS to 1 LSB                                                                                                                               |

| V <sub>REF</sub> Feedthrough Group Delay Harmonic Distortion Channel-to-Channel Crosstalk Digital Feedthrough Power Supply Rejection Ratio  | F <sub>DT</sub><br>GD<br>T <sub>HD</sub><br>C <sub>T</sub><br>Q<br>PSRR |                           | TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>±0.5      |                            | dB<br>ns<br>%<br>dB<br>nVs<br>%/%       | Codes=0 @ 1 MHz $V_{REFP}$ =1MHz Sine 3V p-p @ 1 MHz, single channel  CLK to $V_{OUT}$ $\Delta V$ = $\pm 5\%$                                   |

| POWER CONSUMPTION                                                                                                                           |                                                                         |                           |                                              |                            |                                         |                                                                                                                                                 |

| Positive Supply Current Negative Supply Current Power Dissipation                                                                           | I <sub>CC</sub><br>I <sub>EE</sub><br>P <sub>DISS</sub>                 |                           | 12<br>12<br>80                               |                            | mA<br>mA<br>mW                          | $V_{REFP} = 0 V$ $V_{REFP} = 0 V$ $V_{REFP} = 0 V$ , Codes = all 1                                                                              |

| DIGITAL INPUT<br>CHACTERISTICS                                                                                                              |                                                                         |                           |                                              |                            |                                         |                                                                                                                                                 |

| Logic High <sup>3</sup> Logic Low <sup>3</sup> Input Current Input Capacitance <sup>2</sup>                                                 | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>L</sub><br>C <sub>L</sub>  | 2.4                       |                                              | 0.8<br>±10<br>8            | V<br>V<br>μA<br>pF                      |                                                                                                                                                 |

#### **ELECTRICAL CHARACTERISTICS TABLE**

|                                                  |                                   |     | 25°C |     |       |            |

|--------------------------------------------------|-----------------------------------|-----|------|-----|-------|------------|

| Description                                      | Symbol                            | Min | Тур  | Max | Units | Conditions |

| DIGITAL TIMING<br>SPECIFICATIONS <sup>2, 4</sup> |                                   |     |      |     |       |            |

| Input Clock Pulse Width                          | t <sub>CH</sub> , t <sub>CL</sub> | 60  |      |     | ns    |            |

| Data Setup Time                                  | $t_{DS}$                          | 70  |      |     | ns    |            |

| Data Hold Time                                   | $t_{DH}$                          | 0   |      |     | ns    |            |

| CLK to SDO Propagation Delay                     | $t_{PD}$                          |     |      | 150 | ns    |            |

| DAC Register Load Pulse Width                    | $t_{LD}$                          | 100 |      |     | ns    |            |

| PRESET Pulse Width                               | $t_{PR}$                          | 50  |      |     | ns    |            |

| Clock Edge to Load Rising Edge                   | t <sub>CKLD1</sub>                | 100 |      |     | ns    |            |

| Clock Edge to Load Falling Edge                  | t <sub>CKLD2</sub>                | 0   |      |     | ns    |            |

| Load Falling Edge to SDO  Tri-state Enable       | t <sub>HZ1</sub>                  | 80  |      |     | ns    |            |

| Load Rising Edge to SDO Tri-state Disable        | t <sub>HZ2</sub>                  | 40  |      |     | ns    |            |

| Load Falling Edge to CLK Disable                 | t <sub>LDCK1</sub>                | 30  |      |     | ns    |            |

| Load Rising Edge to CLK Enable                   | t <sub>LDCK2</sub>                | 60  |      |     | ns    |            |

| LD Set-up Time with Respect                      | t <sub>LDSU</sub>                 | 20  |      |     | ns    |            |

| to CLK                                           |                                   |     |      |     |       |            |

#### **NOTES**

- Full Scale Range (FSR) is 3V.

- <sup>2</sup> Guaranteed but not production tested.

- Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

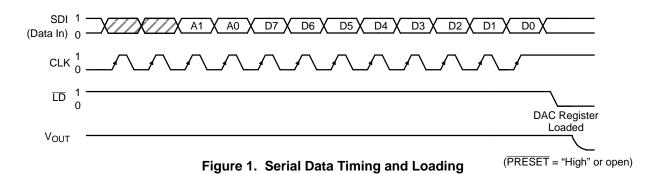

- 4 See Figures 1 and 2.

- For reference input pulse:  $t_R = t_F \ge 100 \text{ ns.}$

#### Specifications are subject to change without notice

# ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2</sup>

| V <sub>CC</sub> to V <sub>REFN</sub> +6.5 V                                   | Maximum Junction Temperature −65°C to 150°C |

|-------------------------------------------------------------------------------|---------------------------------------------|

| V <sub>EE</sub> to V <sub>REFN</sub> 6.5 V<br>V <sub>CC</sub> to DGND +13.0 V | Storage Temperature                         |

| V <sub>EE</sub> to DGND                                                       | Lead Temperature (Soldering, 10 sec) +300°C |

| V <sub>REFP</sub> 1-4 to DGND, V <sub>REFN</sub>                              | Package Power Dissipation Rating @ 75°C     |

| Operating Temperature Range                                                   | PDIP, SOIC 1000mW                           |

| Extended Industrial40°C to +85°C                                              | Derates above 75°C 6mW/°C                   |

|                                                                               |                                             |

#### NOTES:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps.

Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. All inputs have protection diodes which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

SDI  $\frac{1}{0}$ SDI  $\frac{1}{0}$ SDO  $\frac{1}{0}$ CLK  $\frac{1}{0}$ TD  $\frac{1}{0}$ VOUT  $\frac{1}{0}$   $\frac{1}{0$

Figure 2. Detail Serial Data Input Timing

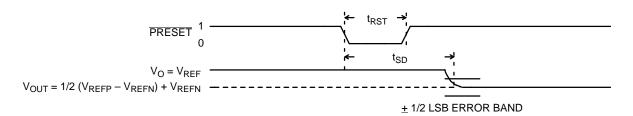

Figure 3. PRESET Operation

#### THEORY OF OPERATION

The MP7652 is a 4-channel multiplying D/A converter that incorporates a novel open loop architecture invented by MPS. The design produces the widest bandwidth, fastest settling time, most constant group delay, and a very low noise operation compared to the conventional R-2R based architectures (given an equal technology platform). This device is particularly useful in applications where analog multipliers are used to perform the gain adjustment function for high frequency analog signal conditioning. Analog multipliers produce much higher noise and. This design allows for digital control of gain with constant and very low noise for all gain settings.

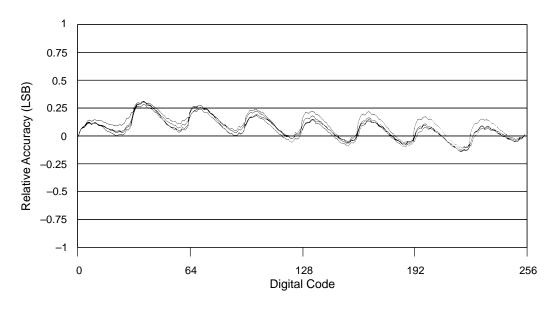

## **Linearity Characteristics**

Each DAC achieves DNL  $\leq$  ±0.5 LSB (typ), INL  $\leq$  ±1 LSB (typ), and gain error  $\leq$  ±1.5%. Since all 4 channel D/A converters are fabricated on the same IC, the linearity matching and gain matching of ±0.5% (typ) is achieved.

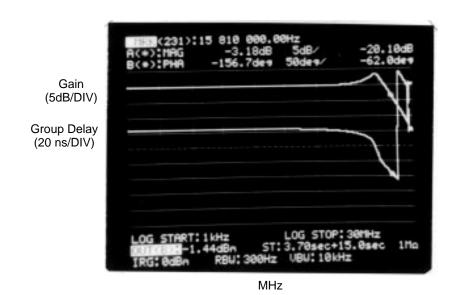

#### **AC and Low Noise Performance**

The novel subranging architecture delivers a 15 MHz (type) -3 dB bandwidth. A constant group delay of 70 ns (typ) is achieved to frequencies up to 8 MHz. Analog output settling time for a code change of FS to ZS and ZS to FS with  $V_{REFP}=3$  V, is typically 150 ns (with  $R_L=5$  k to  $V_{EE}$ ). Also, with all codes set to FS (all 1s) and a  $V_{REFP}=3$  V step, the analog output will settle to 8 bits in less than 110 ns (typ). Note that the AC performance specifications also match to between all 4 channels. The above AC and transient performance is achieved with each channel consuming only 20 mW (typ) with 10 V p-p supplies.

#### **Serial Port**

MP7652 is equipped with a serial data 3-wire standard  $\mu$ -processor logic interface to reduce pin count, package size, and board wire (space). This interface consists of  $\overline{LD}$  which controls the transfer of data to the selected DAC channel, SDI (serial data/address input), CLK (shift register clock) and SDO (serial data output). When the  $\overline{LD}$  signal is high, CLK signal loads the digital input bits (SDI) into the 12-bit shift register. The  $\overline{LD}$  signal going low loads this data into the selected DAC. The  $\overline{LD}$  signal

going low also disables the serial data input (SDI), output (SDO tri-stated) and the CLK input. This design tremendously reduces digital noise, and glitch transients into the DACs due to free running CLK and SDI. Also, tri-stating the SDO output with  $\overline{\text{LD}}$  signal would allow read back of pre-stored digital data of the selected package using one SDO wire for all DAC ICs on the board. When the PRESET signal is low, the output of all DACs are 1/2 of ( $V_{\text{REFP}} + V_{\text{REFN}}$ ), regardless of any digital inputs. Note that  $V_{\text{REFP}}$  is referenced to  $V_{\text{REFN}}$ .

# Power Supplies and Voltage Reference DC Voltage Ranges

For the single supply operation,  $V_{CC}$  = +10 V,  $V_{DD}$  = +5 V, and  $V_{EE}$  = DGND = 0 V. The  $V_O$  1-4 and  $V_{REFP}$  1-4 range would be  $V_{CC}$  -1.8 V (10 - 1.8 = 8.2 V) to  $V_{EE}$  +1.5 V (0 + 1.5 = 1.5 V).  $V_{REFN}$  is the equivalent of AGND for this DAC. In this mode  $V_{REFN}$  can be set at  $(V_{CC} + V_{EE})/2 = (10 + 0)/2 = 5$  V.  $V_{REFN}$  1-4 DC range can also be set from  $V_{EE}$  +1.5 = 1.5 V to  $V_{CC}$  - 1.5 = 8.2 V. Refer to *Table 2*. for the relationship equations.

For the dual supply operation,  $V_{CC}$  = +5,  $V_{DD}$  = +5, and  $V_{EE}$  = -5 V. The  $V_{OUT}$  1-4 and  $V_{REFP}$  1-4 range would be  $V_{CC}$  -1.8 V (-1.8 = 3.2 V) to  $V_{EE}$  +1.5 V (-5 + 1.5 = -3.5 V). In this mode  $V_{REFN}$  can be set to  $(V_{CC} + V_{EE})/2$  = (5 - 5)/2 = 0 V. Similarly,  $V_{REFN}$  1-4 DC range can be set from  $V_{EE}$  +1.5 V = 3.5 V to  $V_{CC}$  -1.8 = +3.2 V. Refer to *Table 2*. for the relationship equations.

Figure 4. Simplified Block Diagram

| Inputs |         |        |          | Inte<br>Add |        | Output                            |                                                                    |

|--------|---------|--------|----------|-------------|--------|-----------------------------------|--------------------------------------------------------------------|

| PRESET | SDI     | CLK    | LD       | <b>A</b> 1  | A0     | SDO                               | Operation                                                          |

| 0      | Х       | Х      | Х        | Х           | Х      | Х                                 | Preset all DACs to<br>1/2 (V <sub>REFP</sub> + V <sub>REFN</sub> ) |

| 1      | Data In | 0→1    | 1        | Х           | Χ      | Last bit of shift reg.            | Shift data in and out                                              |

| 1 1    | X<br>X  | X<br>X | 0<br>0→1 | 0           | 0<br>0 | Hi-Z<br>Last bit<br>of shift reg. | DAC 1 Transparent<br>DAC 1 Latched                                 |

| 1<br>1 | X<br>X  | X<br>X | 0<br>0→1 | 0           | 1<br>1 | Hi-Z<br>Last bit<br>of shift reg. | DAC 2 Transparent<br>DAC 2 Latched                                 |

| 1 1    | X<br>X  | X<br>X | 0<br>0→1 | 1<br>1      | 0      | Hi-Z<br>Last bit<br>of shift reg. | DAC 3 Transparent<br>DAC 3 Latched                                 |

| 1<br>1 | X<br>X  | X<br>X | 0<br>0→1 | 1           | 1<br>1 | Hi-Z<br>Last bit<br>of shift reg. | DAC 4 Transparent<br>DAC 4 Latched                                 |

Table 1. Digital Function Truth Table Serial In/Serial Out

| D7<br>MSB | D6 | D5 | D4 | D3 | D2 | D1 | D0<br>LSB | DAC Output Voltage V <sub>OUTi</sub> = V <sub>REFNi</sub> + (V <sub>REFPi</sub> - V <sub>REFNi</sub> ) ( D/256 ) |

|-----------|----|----|----|----|----|----|-----------|------------------------------------------------------------------------------------------------------------------|

| 0         | 0  | 0  | 0  | 0  | 0  | 0  | 0         | V <sub>REFN</sub>                                                                                                |

| 0         | 0  | 0  | 0  | 0  | 0  | 0  | 1         | $(V_{REFP} - V_{REFN}) \left( \frac{1}{256} \right) + V_{REFN}$                                                  |

|           |    |    |    |    |    |    |           |                                                                                                                  |

| 1         | 1  | 1  | 1  | 1  | 1  | 1  | 0         | $(V_{REFP} - V_{REFN}) (\frac{254}{256}) + V_{REFN}$                                                             |

| 1         | 1  | 1  | 1  | 1  | 1  | 1  | 1         | (V <sub>REFP</sub> – V <sub>REFN</sub> ) ( 255/256 ) + V <sub>REFN</sub>                                         |

Table 2. DAC Transfer Function Analog Output vs. Digital Code

# **OPERATION WITH DUAL POSITIVE POWER SUPPLIES**

For the dual positive supplies operation,  $V_{CC} = +10 \text{ V}$ ,  $V_{DD} = 5 \text{ V}$ ,  $V_{EE} = 0 \text{ V}$  and analog output zero level is to be referenced to  $(V_{CC} + V_{EE})/2$  by setting the AGND pin to 5 V.

#### MICROPROCESSOR INTERFACE

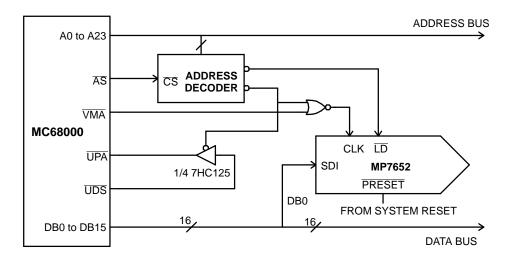

Figure 5. MC68000 Interface (Simplified Diagram)

#### NOTES:

- 1. Execute consecutive memory write instructions while manipulating the data between WRITEs so that each WRITE presents the next bit

- The serial data loading is triggered by the CLK pulse which is asserted by a decoded memory WRITE location 2000, R/W, and 02. A WRITE to address 4000 transfers data from the input shift register to the DAC register.

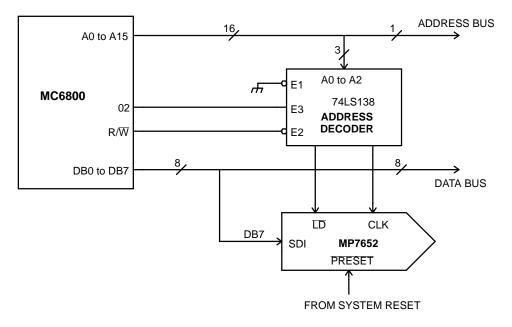

Figure 6. MC6800 Interface (Simplified Diagram)

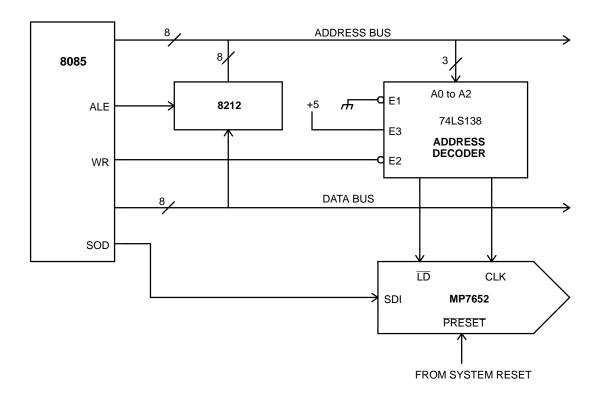

Figure 7. 8085 Interface (Simplified Diagram)

#### NOTES

- 1. Clock generated by  $\overline{\text{WR}}$  and decoding address 8000

- Data is clocked into the DAC shift register by executing memory write instructions. the clock input is generated by decoding address 8000 and WR. Data is then loaded into the DAC register with a memory write instruction to address 4000.

- 3. Serial data must be present in the right justified format in registers H & L of the microprocessor.

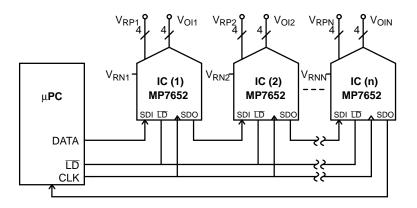

Figure 8. Simplified Diagram Configuration A

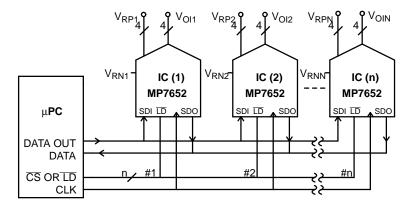

Figure 9. Simplified Diagram Configuration B

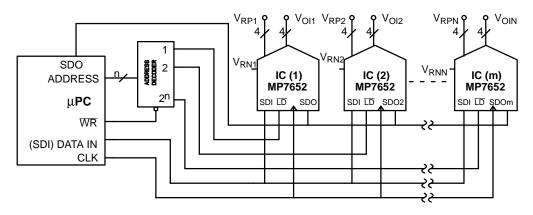

Figure 10. Simplified Diagram Configuration C

Graph 1. Relative Accuracy vs. Digital Code DACs 1 to 4

Graph 2. Typical Gain and Group Delay vs. Frequency (with 5K Resistor Across Output to  $V_{\text{EE}}$ )

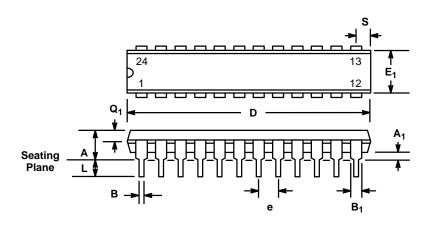

# 24 LEAD PLASTIC DUAL-IN-LINE (300 MIL PDIP) NN24

|                    | INC   | HES    | MILLIN | METERS |

|--------------------|-------|--------|--------|--------|

| SYMBOL             | MIN   | MAX    | MIN    | MAX    |

| А                  |       | 0.200  |        | 5.08   |

| A <sub>1</sub>     | 0.015 | _      | 0.38   |        |

| В                  | 0.014 | 0.023  | 0.356  | 0.584  |

| B <sub>1</sub> (1) | 0.038 | 0.065  | 0.965  | 1.65   |

| С                  | 0.008 | 0.015  | 0.203  | 0.381  |

| D                  | 1.16  | 1.280  | 29.46  | 32.51  |

| Е                  | 0.295 | 0.325  | 7.49   | 8.26   |

| E <sub>1</sub>     | 0.220 | 0.310  | 5.59   | 7.87   |

| е                  | 0.10  | 00 BSC | 2.5    | 4 BSC  |

| L                  | 0.115 | 0.150  | 2.92   | 3.81   |

| α                  | 0°    | 15°    | 0°     | 15°    |

| Q <sub>1</sub>     | 0.055 | 0.070  | 1.40   | 1.78   |

| S                  | 0.028 | 0.098  | 0.711  | 2.49   |

Note: (1) The minimum limit for dimensions B1 may be  $0.023^{\circ}$  (0.58 mm) for all four corner leads only.

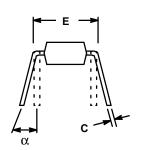

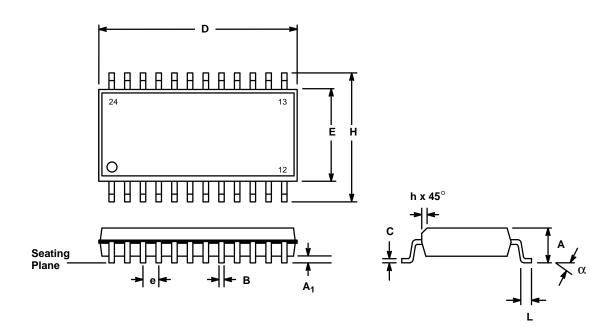

# 24 LEAD SMALL OUTLINE (300 MIL JEDEC SOIC) S24

|        | INC    | CHES   | MILLIN | METERS |

|--------|--------|--------|--------|--------|

| SYMBOL | MIN    | MAX    | MIN    | MAX    |

| А      | 0.097  | 0.104  | 2.464  | 2.642  |

| A1     | 0.0050 | 0.0115 | 0.127  | 0.292  |

| В      | 0.014  | 0.019  | 0.356  | 0.483  |

| С      | 0.0091 | 0.0125 | 0.231  | 0.318  |

| D      | 0.602  | 0.612  | 15.29  | 15.54  |

| Е      | 0.292  | 0.299  | 7.42   | 7.59   |

| е      | 0.0    | 50 BSC | 1.2    | 7 BSC  |

| Н      | 0.400  | 0.410  | 10.16  | 10.41  |

| h      | 0.010  | 0.016  | 0.254  | 0.406  |

| L      | 0.016  | 0.035  | 0.406  | 0.889  |

| α      | 0°     | 8°     | 0°     | 8°     |

# **Notes**

## NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contains here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1995 EXAR Corporation Datasheet April 1995

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

**T⊕M**<sup>™</sup>