### DEC 3 1990

#### **Philips Components**

|               | Data sheet            |

|---------------|-----------------------|

| status        | Product specification |

| date of issue | October 1990          |

|               |                       |

|               |                       |

# PCA82C200 Stand-alone CAN-controller

### **1.0 FEATURES**

- Multi-master architecture

- Interfaces with a large variety of microcontrollers (Intel, Motorola or Intel and Motorola compatible)

- Bus access priority (determined by the message identifier)

- 2032 message identifiers

- · Guaranteed latency time for high priority messages

- Powerful error handling capability

- Data length from 0 to 8 bytes

- Configurable bus interface

- Programmable clock output

- Multicast and Broadcast message facility

- Non destructive bit-wise arbitration

- Non-return-to-zero (NRZ) coding/decoding with bitstuffing

- Programmable transfer rate (up to 1 Mbit/s)

- · Programmable output driver configuration

- Suitable for use in a wide range of networks including the SAE networks Class A, B and C

### 2.0 GENERAL DESCRIPTION

The PCA82C200 is a highly integrated stand-alone controller for the controller area network (CAN) used within automotive and general industrial environments. The PCA82C200 contains all necessary features required to implement a high performance communication protocol. The PCA82C200 with a simple bus line connection performs all the functions of the physical and data-link layers. The application layer of an Electronic Control Unit (ECU) is provided by a microcontroller, to which the PCA82C200 provides a versatile interface. The use of the PCA82C200 in an automotive or general industrial environment, results in a reduced wiring harness and an enhanced diagnostic and supervisory capability.

### **3.0 ORDERING INFORMATION**

| EXTENDED                 |          | PACKA        | GE                 |                   |

|--------------------------|----------|--------------|--------------------|-------------------|

| TYPE NUMBER              | PINS     | PIN POSITION | MATERIAL           | CODE              |

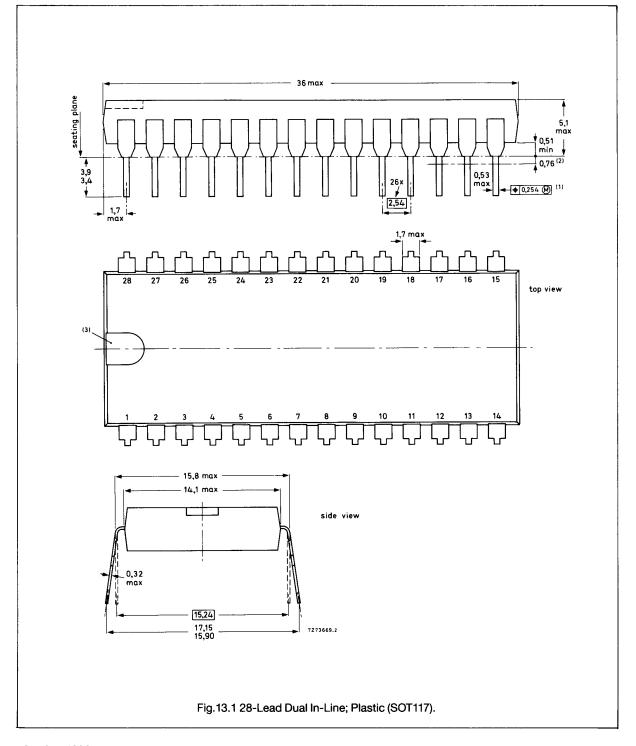

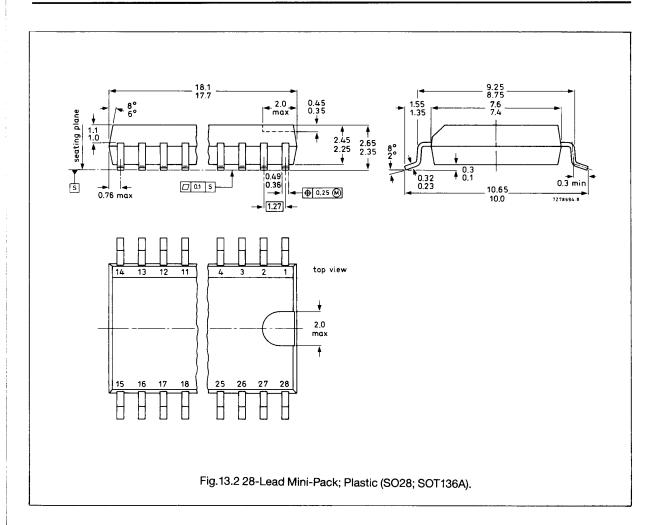

| PCA82C200P<br>PCA82C200T | 28<br>28 | DIL<br>SO28  | plastic<br>plastic | SOT117<br>SOT136A |

# **Philips Components**

### CONTENTS

| 1.0    | FEATURES                         |

|--------|----------------------------------|

| 2.0    | GENERAL DESCRIPTION              |

| 3.0    | ORDERING INFORMATION             |

| 4.0    | PINNING INFORMATION              |

| 4.1    | Pinning                          |

| 5.0    | DEVELOPMENT SUPPORT AND TOOLS    |

| 5.1    | The PCA82C200 evaluation board   |

| 5.2    | Advanced support                 |

| 6.0    | FUNCTIONAL DESCRIPTION           |

| 6.1    | Interface Management Logic (IML) |

| 6.2    | Transmit Buffer (TBF)            |

| 6.3    | Receive Buffers (RBF0 and RBF1)  |

| 6.4    | Bit Stream Processor (BSP)       |

| 6.5    | Bit Timing Logic (BTL)           |

| 6.6    | Transceiver Control Logic (TCL)  |

| 6.7    | Error Management Logic (EML)     |

| 6.8    | Controller Interface Logic (CIL) |

| 7.0    | CONTROL SEGMENT AND MESSAGE      |

|        | BUFFER DESCRIPTION               |

| 7.1    | Address allocation               |

| 7.2    | Control Segment layout           |

| 7.2.1  | Control Register (CR)            |

| 7.2.2  | Command Register (CMR)           |

| 7.2.3  | Status Register (SR)             |

| 7.2.4  | Interrupt Register (IR)          |

| 7.2.5  | Acceptance Code Register (ACR)   |

| 7.2.6  | Acceptance Mask Register (AMR)   |

| 7.2.7  | Bus Timing Register 0 (BTR 0)    |

| 7.2.8  | Bus Timing Register 1 (BTR 1)    |

| 7.2.9  | Output Control Register (OCR)    |

| 7.2.10 | Test Register (TR)               |

| 7.3    | Transmit Buffer layout           |

| 7.3.1  | Descriptor                       |

| 7.3.2  | Data Field                       |

| 7.4    | Receive Buffer layout            |

| 7.5    | Clock Divider Register (CDR)     |

### Product specification

## PCA82C200

| 8.0   | BUS TIMING/SYNCHRONIZATION          |

|-------|-------------------------------------|

| 8.1   | Bit timing                          |

| 8.1.1 | Synchronization Segment (SYNCSEG)   |

| 8.1.2 | Time Segment 1 (TSEG1)              |

| 8.1.3 | Time Segment 2 (TSEG2)              |

| 8.1.4 | Synchronization Jump Width (SJW)    |

| 8.1.5 | Propagation delay time              |

| 8.1.6 | Bit timing restrictions             |

| 8.2   | Synchronization                     |

| 8.2.1 | Hard synchronization                |

| 8.2.2 | Resynchronization                   |

| 8.2.3 | Synchronization rules               |

| 9.0   | COMMUNICATION PROTOCOL              |

| 9.1   | Frame types                         |

| 9.1.1 | Bit representation                  |

| 9.2   | Data Frame                          |

| 9.2.1 | Start-of-Frame                      |

| 9.2.2 | Arbitration Field                   |

| 9.2.3 | Control Field                       |

| 9.2.4 | Data Field                          |

| 9.2.5 | Cyclic Redundancy Check (CRC) Field |

| 9.2.6 | Acknowledge Field                   |

| 9.2.7 | End-of-Frame Field                  |

| 9.3   | Remote Frame                        |

| 9.4   | Error Frame                         |

| 9.4.1 | Error Flag                          |

| 9.4.2 | Error Delimiter                     |

| 9.5   | Overload Frame                      |

| 9.5.1 | Overload Flag                       |

| 9.5.2 | Overload Delimiter                  |

| 9.6   | Inter-Frame Space                   |

| 9.6.1 | Intermission Field                  |

| 9.6.2 | Bus-Idle                            |

| 9.7   | Bus organization                    |

| 9.7.1 | Bus access                          |

| 9.7.2 | Arbitration                         |

| 9.7.3 | Coding/decoding                     |

| 9.7.4 | Error signalling                    |

| 9.7.5 | Overload signalling                 |

| 9.8   | Error detection                     |

9.8.1 Bit Error

### PCA82C200

| 9.8.2  | Stuff Error                                 |

|--------|---------------------------------------------|

| 9.8.3  | CRC Error                                   |

| 9.8.4  | Form Error                                  |

| 9.8.5  | Acknowledgement error                       |

| 9.8.6  | Error detection by an Error Flag of another |

|        | PCA82C200                                   |

| 9.8.7  | Error detection capabilities                |

| 9.9    | Error confinement (definitions)             |

| 9.9.1  | Bus-Off                                     |

| 9.9.2  | Acknowledge (ACK)                           |

| 9.9.3  | Error-Active                                |

| 9.9.4  | Error-Passive                               |

| 9.9.5  | Suspend Transmission                        |

| 9.9.6  | Start-up                                    |

| 9.10   | Aims of error confinement                   |

| 9.10.1 | Distinction of short and long lasting       |

|        | disturbances                                |

| 9.10.2 | Detection and localization of hardware      |

|        | disturbances and defects                    |

| 9.10.3 | Error confinement                           |

| 10.0   | LIMITING VALUES                             |

### 11.0 DC CHARACTERISTICS

### 12.0 AC CHARACTERISTICS

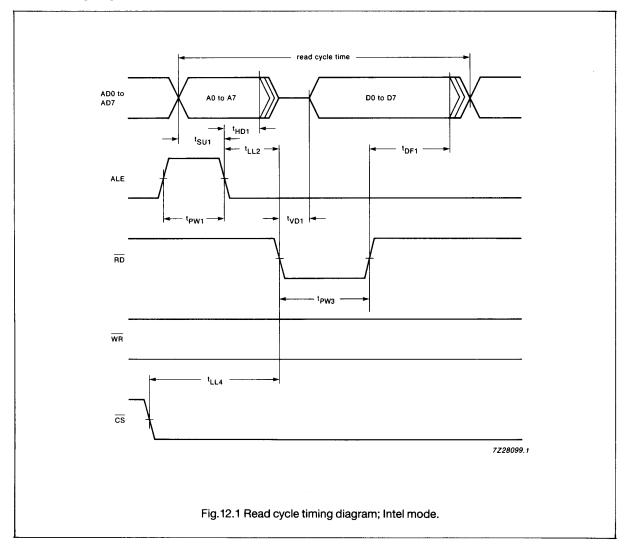

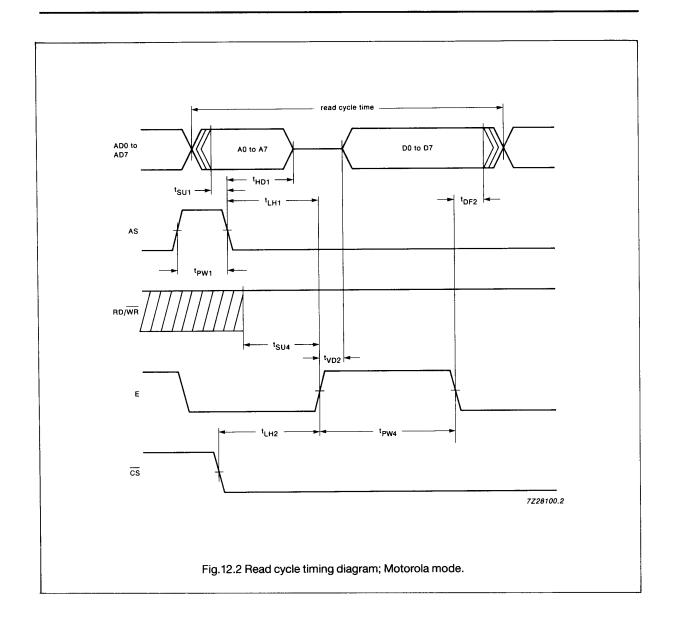

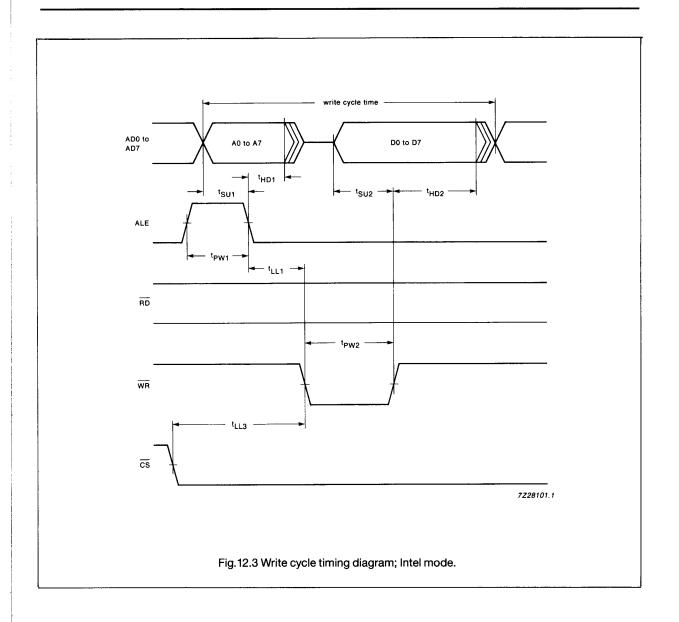

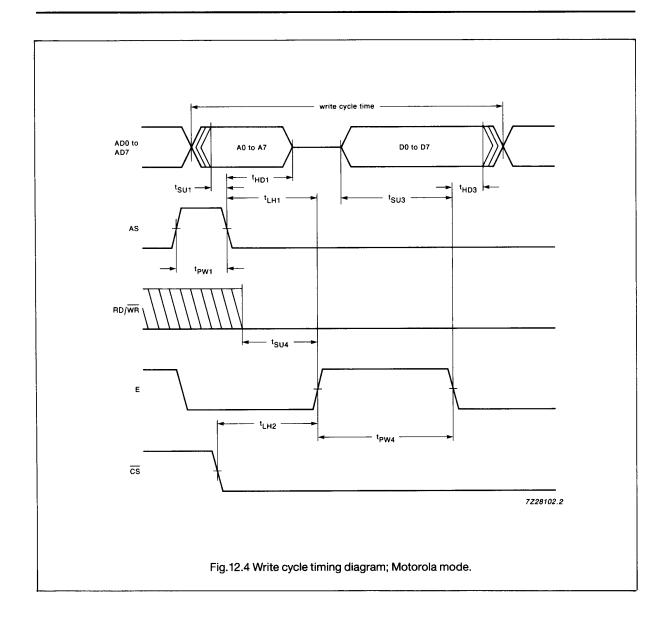

- 12.1 AC timing diagrams

- 12.2 Additional AC information

- 13.0 PACKAGE INFORMATION

### 14.0 SOLDERING INFORMATION

- 14.1 Soldering plastic dual in-line packages

- 14.2 Soldering plastic mini-packs

### 15.0 DEFINITIONS

## PCA82C200

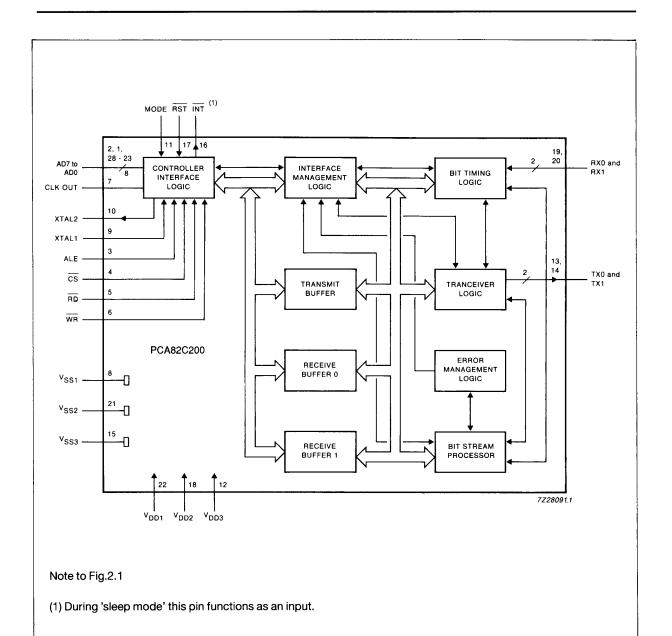

Fig.2.1 Block diagram.

I

## PCA82C200

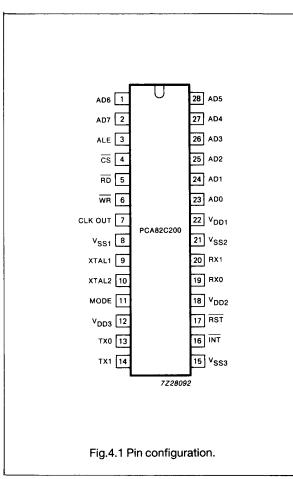

**4.0 PINNING INFORMATION**

## PCA82C200

| SYMBOL            | PIN           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AD7 - AD0         | 2, 1, 28 - 23 | Multiplexed address/data bus.                                                                                                                                                                                                                                                                                                                            |  |

| ALE               | 3             | ALE signal (Intel mode) or AS input signal (Motorola mode).                                                                                                                                                                                                                                                                                              |  |

| CS                | 4             | Chip select input, low level allows access to the PCA82C200.                                                                                                                                                                                                                                                                                             |  |

| RD                | 5             | RD signal (Intel mode) or E enable signal (Motorola mode) from the microcontroller.                                                                                                                                                                                                                                                                      |  |

| WR                | 6             | WR signal (Intel mode) or RD/WR signal (Motorola mode) from the microcontroller.                                                                                                                                                                                                                                                                         |  |

| CLK OUT           | 7             | Clock output signal produced by the PCA82C200 for the microcontroller. The clock signal is derived from the built-in oscillator, via the programmable divider (see section 7.5). This output is capable of driving one CMOS or NMOS load.                                                                                                                |  |

| V <sub>SS1</sub>  | 8             | Ground potential for the logic circuits.                                                                                                                                                                                                                                                                                                                 |  |

| XTAL1<br>(note 1) | 9             | Input to the oscillator's amplifier. External oscillator signal is input via this pin.                                                                                                                                                                                                                                                                   |  |

| XTAL2<br>(note 2) | 10            | Output from the oscillator's amplifier. Output must be left open when an external oscillator signal is used.                                                                                                                                                                                                                                             |  |

| MODE              | 11            | Mode select input: connected to $V_{DD}$ selects Intel mode; connected to $V_{SS}$ selects Motorola mode.                                                                                                                                                                                                                                                |  |

| V <sub>DD3</sub>  | 12            | 5 V power supply for the output driver.                                                                                                                                                                                                                                                                                                                  |  |

| TX0               | 13            | Output from the output-driver 0 to the physical bus-line.                                                                                                                                                                                                                                                                                                |  |

| TX1               | 14            | Output from the output-driver 1 to the physical bus-line.                                                                                                                                                                                                                                                                                                |  |

| V <sub>SS3</sub>  | 15            | Ground potential for the output driver.                                                                                                                                                                                                                                                                                                                  |  |

| INT               | 16            | Interrupt output, used to interrupt the microcontroller (see section 7.2.4). INT is active if the Interrupt Register contains a logic HIGH bit (present). INT is an open drain output and is designed to be a wired-OR with other INT outputs within the system. A LOW level on this pin will reactivate the IC from the sleep mode (see section 7.2.2). |  |

| RST               | 17            | Reset input, used to reset the CAN interface (LOW level). Automatic power-ON reset can be obtained by connecting $\overrightarrow{RST}$ via a capacitor to V <sub>SS</sub> and via a resistor to V <sub>DD</sub> (e.g. C = 1 $\mu$ F; R = 50 k $\Omega$ ).                                                                                               |  |

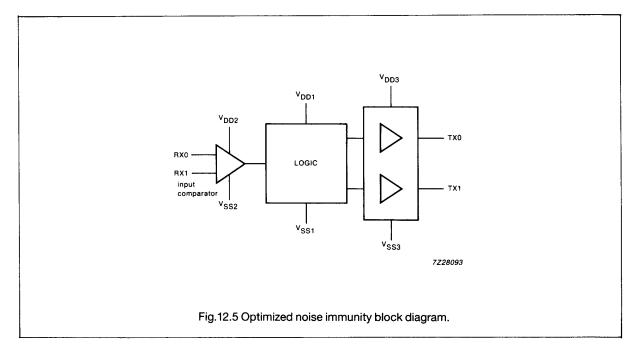

| V <sub>DD2</sub>  | 18            | 5 V power supply for the input comparator.                                                                                                                                                                                                                                                                                                               |  |

| RX0 - RX1         | 19, 20        | Input from the physical bus-line to the input comparator of the PCA82C200. A dominant level will wake-up the PCA82C200. A recessive level is read if RX0 is higher than RX1 and vice versa for the dominant level.                                                                                                                                       |  |

| V <sub>SS2</sub>  | 21            | Ground potential for the input comparator.                                                                                                                                                                                                                                                                                                               |  |

| V <sub>DD1</sub>  | 22            | 5 V power supply for the logic circuits.                                                                                                                                                                                                                                                                                                                 |  |

### Note

1. XTAL1 and XTAL2 pins should be connected to  $V_{SS}$  via 15  $\mu F$  capacitors.

## PCA82C200

#### 5.0 DEVELOPMENT SUPPORT AND TOOLS

#### 5.1 The PCA82C200 evaluation board

Philips offers powerful support during the design and test stages of CAN networks, working closely with customers to develop their systems. The "Philips Stand-alone CAN Controller (PSCC) Evaluation Board" is a versatile tool being a ready-to-use hardware and software module, very similar to a real CAN module. Since a 5 V power supply is provided, the board can be used in any vehicle without modification. An RS232 interface allows a terminal or a PC with terminal-emulation software to be connected to the board. The board comprises:

- a PCA82C200 CAN bus-controller

- a PCA80C552 microcontroller with up to 32K x 8 bits external RAM and EPROM

- a 5 V power supply with protection against car battery disturbances

- two different physical CAN bus interfaces (selectable)

- an RS232 interface

- · demonstration hardware

- a wrap field for customer-specific circuitry

The software provided with the board supports in learning about CAN and assists in prototyping (e.g. in-vehicle) networks. It provides:

- demonstration software (automatically startable)

- the menu-driven software comprises:

- a facility to alter the contents of the PCA82C200 registers

- a bus monitor to receive messages from the CAN bus and to display them on a terminal

- a download facility for the user's application software

With these facilities the board is a basis for prototype modules; using entirely your own software, the board can be used as a custom, debugged and proven hardware module.

### 5.2 Advanced support

For further development support, Philips subcontractor I+ME offers a complete set of development tools including:

- a CAN simulator; CAN/Net Sim

- an emulator; CAN/Net Emu

- a network analyzer; CAN/Net Anal

- I+ME can be contacted through the following address:

I+ME GmbH Ferdinandstrasse 15 D-3340 Wolfenbuettel West Germany.

#### **6.0 FUNCTIONAL DESCRIPTION**

The PCA82C200 contains all necessary hardware for a high performance serial network communication (see Fig.2.1). The PCA82C200 controls the communication flow through the area network using the CAN-protocol. The PCA82C200 meets the following automotive requirements:

- short message length

- · guaranteed latency time for urgent messages

- bus access priority, determined by the message identifier

- · powerful error handling capability

- configuration flexibility to allow area network expansion.

The latency time defines the period between the initiation (Transmission Request) and the start of the transmission on the bus. Latency time is dependent on a variety of bus related conditions. In the case of a message being transmitted on the bus and one distortion the latency time can be up to 149 bit times (worst case). For more information see application note on 'Bit Timing'.

#### 6.1 Interface Management Logic (IML)

The IML interprets commands from the microcontroller, allocates the message buffers (TBF, RBF0 and RBF1) and provides interrupts and status information to the microcontroller.

### 6.2 Transmit Buffer (TBF)

The TBF is a 10 byte memory into which the microcontroller writes messages which are to be transmitted over the CAN network.

## PCA82C200

#### 6.3 Receive Buffers (RBF0 and RBF1)

The RBF0 and RBF1 are each 10 byte memories which are alternatively used to store messages received from the CAN network. The CPU can process one message while another is being received.

#### 6.4 Bit Stream Processor (BSP)

The BSP is a sequencer, controlling the data stream between the transmit buffer, receive buffers (parallel data) and the CAN bus (serial data).

#### 6.5 Bit Timing Logic (BTL)

The BTL synchronizes the PCA82C200 to the bitstream on the CAN bus.

#### 6.6 Transceiver Control Logic (TCL)

The TCL controls the output driver.

#### 6.7 Error Management Logic (EML)

The EML performs the error confinement according to the CAN protocol.

#### 6.8 Controller Interface Logic (CIL)

The CIL is the interface to the external microcontroller. The PCA82C200 can directly interface with a variety of microcontrollers.

#### 7.0 CONTROL SEGMENT AND MESSAGE BUFFER DESCRIPTION

The PCA82C200 appears to a microcontroller as a memory-mapped I/O device due to the on-chip RAM, guaranteeing the independent operation of both devices.

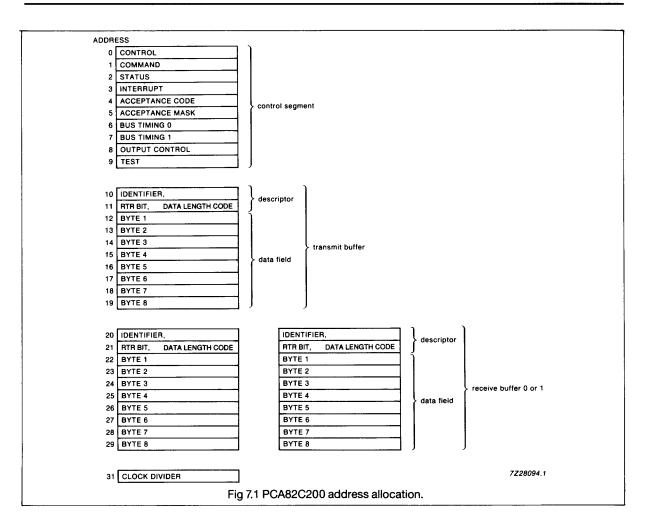

#### 7.1 Address allocation

The address area of the PCA82C200 consists of the Control Segment and the message buffers. The Control Segment is programmed during an initialization download in order to configure communication parameters (e.g. bit timing). Communication over the CAN-bus is also controlled via this segment by the microcontroller. During initialization the CLOCK OUT signal may be programmed to a value determined by the microcontroller (see Fig.2.1). A message which is to be transmitted, must be written to the Transmit Buffer. After a successful reception the microcontroller may read the message from the Receive Buffer and then release it for further use.

### 7.2 Control Segment layout

The exchange of status, control and command signals between the microcontroller and the PCA82C200 is performed in the control segment. The layout of this segment is shown in Fig 7.1. After an initial down-load, the contents of the Acceptance Code Register, the Acceptance Mask Register and Bus Timing Registers 0 and 1, should not be changed. These registers may only be accessed when the Reset Request bit in the Control Register, is set HIGH (see section 7.2.1).

| DESCRIPTION                   |              |               |              |                 |                         |                          |                     |                       |                        |

|-------------------------------|--------------|---------------|--------------|-----------------|-------------------------|--------------------------|---------------------|-----------------------|------------------------|

|                               | AU-<br>DRESS | 7 (MSB)       | 9            | 5               | 4                       | e                        | 8                   | -                     | 0 (LSB)                |

| <b>Control Segment</b>        |              |               |              |                 |                         |                          |                     |                       |                        |

| Control Register              | 0            | Test Mode     | Synch        | reserved        | Overrun                 | Error                    | Transmit            | Receive               | Reset Request          |

| )                             |              |               |              |                 | Interrupt               | Interrupt                | Interrupt<br>Enable | Interrupt<br>Enable   |                        |

| Command                       | +            | reserved      | reserved     | reserved        | Goto Sleep              | Clear                    | Release             | Abort                 | Transmission           |

| Register                      | _            |               |              |                 |                         | Overrun                  | Receive<br>Buffer   | Transmission          | Request                |

| Status Register               | 2            | Bus Status    | Error        | Transmit        | Receive                 | Transmission             | Transmit            | Data Overrun          | Receive Buffer         |

|                               |              |               | Status       | Status          | Status                  | Complete                 | Burrer<br>Access    |                       | olalus                 |

| Interrupt Register            | e            | reserved      | reserved     | reserved        | Wake-Up                 | Overrun                  | Error               | Transmit              | Receive Interrupt      |

| Acceptance Code               | 4            | AC.7          | AC.6         | AC.5            | AC.4                    | Interrupt<br>AC.3        | AC.2                | AC.1                  | AC.0                   |

| Register<br>Accentance Mask   | Ľ            | AM 7          | AM6          | AM 5            | AM 4                    | AM 3                     | AM.2                | AM.1                  | AM.0                   |

| Redister                      | >            |               |              | 2               |                         | )                        |                     |                       |                        |

| Bus Timing                    | 9            | SJW.1         | SJW.0        | BRP.5           | BRP.4                   | BRP.3                    | BRP.2               | BRP.1                 | BRP.0                  |

| Hegister 0<br>Bus Timing      | 7            | SAM           | TSEG2.2      | TSEG2.1         | TESG2.0                 | TSEG1.3                  | TSEG1.2             | TSEG1.1               | TSEG1.0                |

| Register 1                    | c            |               | FINE CO      |                 |                         | OCTNO                    |                     | OCMODE1               | OCMODED                |

|                               | 0            |               |              |                 | 200                     |                          |                     |                       |                        |

| Test Register<br>(see note 1) | 6            | reserved      | reserved     | Map<br>Internal | Connect<br>BX Buiffer 0 | Connect TX<br>Buffer CPU | Access<br>Internal  | Normal RAM<br>Connect | Float Output<br>Driver |

| (1 201 22)                    |              |               |              | Register        | CPU                     |                          | Bus                 |                       |                        |

| <b>Transmit Buffer</b>        |              |               |              |                 |                         |                          |                     |                       |                        |

| Identifier<br>RTR data length | 95           | ID.10<br>ID.2 | 1D.9         | 1D.8            | ID.7<br>RTR             | ID.6<br>DLC.3            | ID.5<br>DLC.2       | ID.4<br>DLC.1         | ID.3<br>DLC.0          |

| code<br>bytes 1 - 8           | 12 - 19      | Data          | Data         | Data            | Data                    | Data                     | Data                | Data                  | Data                   |

| Receive Buffer 0/1            |              |               |              |                 |                         |                          |                     |                       |                        |

| Identifier<br>RTR data length | 20<br>21     | ID.10<br>ID.2 | 1D.9<br>1D.1 | 1D.8<br>1D.0    | ID.7<br>RTR             | ID.6<br>DLC.3            | ID.5<br>DLC.2       | ID.4<br>DLC.1         | ID.3<br>DLC.0          |

| code<br>bytes 1 - 8           | 22 - 29      | Data          | Data         | Data            | Data                    | Data                     | Data                | Data                  | Data                   |

| Clock Divider                 | 31           | reserved      | reserved     | reserved        | reserved                | reserved                 | CD.2                | CD.1                  | CD.0                   |

**Philips Components**

## Stand-alone CAN-controller

# PCA82C200

Notes to Table 7.1

The Test Register is used for production testing only.

Register 30 is not implemented.

## Product specification

## PCA82C200

### 7.2.1 CONTROL REGISTER (CR)

The contents of the Control Register are used to change the behaviour of the PCA82C200. Control bits may be set or reset by the attached microcontroller which uses the Control Register as a read/write memory.

### Table 7.2 Control Register bits.

|      | CR     | : ADDRESS 0               |

|------|--------|---------------------------|

| BIT  | SYMBOL | FUNCTION                  |

| CR.7 | TM     | Test Mode                 |

| CR.6 | S      | Synch                     |

| CR.5 | -      | Reserved                  |

| CR.4 | OIE    | Overrun Interrupt Enable  |

| CR.3 | EIE    | Error Interrupt Énable    |

| CR.2 | TIE    | Transmit Interrupt Enable |

| CR.1 | RIE    | Receive Interrupt Enable  |

| CR.0 | RR     | Reset Request             |

### PCA82C200

Table 7.4 Effects of setting the Reset Request bit HIGH (present).

| TYPE      | BIŢ                                                                                                                                                                | EFFECT                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control   | Test Mode                                                                                                                                                          | LOW (disabled)                                                                                                                                          |

| Command   | Goto Sleep<br>Clear Overrun Status<br>Release Receive Buffer<br>Abort Transmission<br>Transmission Request                                                         | LOW (wake-up)<br>HIGH (clear)<br>HIGH (released)<br>LOW (absent)<br>LOW (absent)                                                                        |

| Status    | Bus Status<br>Error Status<br>Transmit Status<br>Receive Status<br>Transmission Complete Status<br>Transmit Buffer Access<br>Data Overrun<br>Receive Buffer Status | LOW (bus-ON), see note 1<br>LOW (no error), see note 1<br>LOW (idle)<br>LOW (idle)<br>HIGH (complete)<br>HIGH (released)<br>LOW (absent)<br>LOW (empty) |

| Interrupt | Overrun Interrupt<br>Transmit Interrupt<br>Receive Interrupt                                                                                                       | LOW (reset)<br>LOW (reset)<br>LOW (reset)                                                                                                               |

### Note to Table 7.4

1. Only after an external power-up reset; see note 5 to Table 7.8.

#### 7.2.2 COMMAND REGISTER (CMR)

A command bit initiates an action within the transfer layer of the PCA82C200. The Command Register appears to the microcontroller as a write only memory. If a read access is performed to this address the byte  $1111111_b$  is returned.

### Table 7.5 Command Register bits.

|       | СМ     | R : ADDRESS 1          |

|-------|--------|------------------------|

| BIT   | SYMBOL | FUNCTION               |

| CMR.7 | -      | Reserved               |

| CMR.6 | -      | Reserved               |

| CMR.5 | -      | Reserved               |

| CMR.4 | GTS    | Goto Sleep             |

| CMR.3 | COS    | Clear Overrun Status   |

| CMR.2 | RRB    | Release Receive Buffer |

| CMR.1 | AT     | Abort Transmission     |

| CMR.0 | TR     | Transmission Request   |

## PCA82C200

| Table 7.6 Description of | the Command | Register hits  |

|--------------------------|-------------|----------------|

| Table 1.0 Description of | the Command | negister bits. |

| CONTROL BIT                     | VALUE                              | COMMENTS                                                                                                                                                                                                                 |

|---------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmission Request (note 1)   | HIGH (present)<br>LOW (absent)     | A message shall be transmitted.<br>No action.                                                                                                                                                                            |

| Abort Transmission (note 2)     | HIGH (present)<br>LOW (absent)     | If not already in progress, a pending Transmission Request<br>is cancelled.<br>No action.                                                                                                                                |

| Release Receive Buffer (note 3) | HIGH (released)<br>LOW (no action) | The Receive Buffer attached to the microcontroller is released.<br>No action.                                                                                                                                            |

| Clear Overrun (note 4)          | HIGH (clear)<br>LOW (no action)    | The Data Overrun status bit is set to LOW (see section 7.2.3).<br>No action.                                                                                                                                             |

| Goto Sleep (note 5)             | HIGH (sleep)                       | The PCA82C200 enters sleep mode, if the INT = HIGH (no interrupt signal from the PCA82C200 to the microcontroller pending or external source pending) and there is no bus activity.<br>The PCA82C200 functions normally. |

### Notes to Table 7.6

- If the Transmission Request bit was set HIGH in a previous command, it cannot be cancelled by setting the Transmission Request bit LOW (absent). Cancellation of the requested transmission may be performed by setting the Abort Transmission bit HIGH (present).

- 2. The Abort Transmission bit is used when the microcontroller requires the suspension of the previously requested transmission, for example to transmit an urgent message. A transmission already in progress is not stopped. In order to determine if the original message had been transmitted successfully, or aborted, the Transmission Complete status bit should be checked after the Transmit Buffer Access bit has been set HIGH (released) or a Transmit Interrupt has been generated (see section 7.2.4).

- After reading the contents of the Receive Buffer (RBF0 or RBF1) the microcontroller must release this buffer by setting the Release Receive Buffer bit HIGH (released). This may result in another message becoming immediately available.

- 4. This command bit is used to acknowledge the Data Overrun condition signalled by the Data Overrun status bit. It may be given or set at the same time as a Release Receive Buffer command bit.

5. The PCA82C200 will enter sleep mode, if Goto Sleep is set HIGH (sleep), there is no bus activity and INT = HIGH (inactive). After sleep mode is set, the CLK OUT signal continues until at least 15 bit times have passed. The PCA82C200 will wake up when one of the three previously mentioned conditions is negated: after Goto Sleep is set LOW (wake up), there is bus activity or INT is driven LOW (active). On wake up, the oscillator is started and a Wake-Up Interrupt (see section 7.2.4) is generated. A PCA82C200 which is sleeping and then awoken by bus activity will not be able to receive this message until it detects a Bus-Free signal (see section 9.9.6).

#### 7.2.3 STATUS REGISTER (SR)

The contents of the Status Register reflect the status of the PCA82C200 bus controller. The Status Register appears to the microcontroller as a read only memory.

### Table 7.7 Status Register bits.

| SR : ADDRESS 2 |        |                              |  |  |  |  |

|----------------|--------|------------------------------|--|--|--|--|

| BIT            | SYMBOL | FUNCTION                     |  |  |  |  |

| SR.7           | BS     | Bus Status                   |  |  |  |  |

| SR.6           | ES     | Error Status                 |  |  |  |  |

| SR.5           | TS     | Transmit Status              |  |  |  |  |

| SR.4           | RS     | Receive Status               |  |  |  |  |

| SR.3           | TCS    | Transmission Complete Status |  |  |  |  |

| SR.2           | TBS    | Transmit Buffer Status       |  |  |  |  |

| SR.1           | DO     | Data Overrun                 |  |  |  |  |

| SR.0           | RBS    | Receive Buffer Status        |  |  |  |  |

## PCA82C200

| STATUS BIT                            | VALUE                          | COMMENTS                                                                                                                                                                         |

|---------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Buffer Status (note 1)        | HIGH (full)<br>LOW (empty)     | This bit is set when a new message is available.<br>No message has become available since the last<br>Release Receive Buffer command bit was set.                                |

| Data Overrun (note 2)                 | HIGH (overrun)<br>LOW (absent) | This bit is set HIGH (Overrun), when both Receive<br>Buffers are full and the first byte of another<br>message should be stored.<br>No data overrun has occurred since the Clear |

|                                       |                                | Overrun command was given.                                                                                                                                                       |

| Transmit Buffer Access(note 3)        | HIGH (released)                | The microcontroller may write a message into the TBF.                                                                                                                            |

|                                       | LOW (locked)                   | The microcontroller cannot access the Transmit<br>Buffer. A message is either waiting for transmission<br>or is in the process of being transmitted.                             |

| Transmission Complete Status (note 3) | HIGH (complete)                | Last requested transmission has been successfully completed.                                                                                                                     |

|                                       | LOW (incomplete)               | Previously requested transmission is not yet completed.                                                                                                                          |

| Receive Status (note 4)               | HIGH (receive)<br>LOW (idle)   | The PCA82C200 is receiving a message.<br>No message is received.                                                                                                                 |

| Transmit Status (note 4)              | HIGH (transmit)<br>LOW (idle)  | The PCA82C200 is transmitting a message.<br>No message is transmitted.                                                                                                           |

| Error Status                          | HIGH (error)<br>LOW (ok)       | At least one of the Error Counters (see 9.10.3) has<br>reached the microcontroller Warning Limit.<br>Both Error Counters have not reached the Warning<br>Limit.                  |

| Bus Status (note 5)                   | HIGH (Bus-Off)<br>LOW (Bus-On) | The PCA82C200 is not involved in bus activities.<br>The PCA82C200 is involved in bus activities                                                                                  |

#### Table 7.8 Description of the Status Register bits.

#### Notes to Table 7.8

- If the command bit Release Receive Buffer is set HIGH (released) by the microcontroller, the Receive Buffer Status bit is set LOW (empty) by IML. When a new message is stored in any of the receive buffers, the Receive Buffer Status bit is set HIGH (full) again.

- If Data Overrun = HIGH (Overrun) is detected, the currently received message is dropped.

A transmitted message, granted acceptance, is also stored in a Receive Buffer. This occurs because it is not known if the PCA82C200 will lose arbitration and so become a receiver of the message. If no receive buffer is available, Data Overrun is signalled.

- If the microcontroller tries to write to the Transmit Buffer when the Transmit Buffer Access bit is LOW (locked), the written bytes will not be accepted and will be lost without this being signalled.

The Transmission Complete Status bit is set LOW (incomplete) whenever the Transmission Request bit is set HIGH (present). If an Abort Transmission command is issued, the Transmit Buffer will be released. If the message, which was requested and then aborted, was not transmitted, the Transmission Complete Status bit will remain LOW.

- 4. If both the Receive Status and Transmit Status bits are LOW (idle) the CAN-bus is idle.

- 5. When the Bus Status bit is set HIGH (Bus-Off), the PCA82C200 will set the Reset Request bit HIGH (present). It will stay in this state until the microcontroller sets the Reset Request bit LOW (absent). Once this is completed the PCA82C200 will wait the minimum protocol-defined time (128 occurrences of the Bus-Free signal) before setting the Bus Status bit LOW (Bus-On), the Error Status bit LOW (OK) and resetting the Error Counters.

## PCA82C200

7.2.4 INTERRUPT REGISTER (IR)

The Interrupt Register allows the identification of an interrupt source. When one or more bits of this register are set, the  $\overline{INT}$  pin is activated. All bits are reset by the PCA82C200 after this register is read by the microcontroller. This register appears to the microcontroller as a read only memory.

#### Table 7.9 Interrupt Register bits.

| IR : ADDRESS 3 |        |                    |  |  |  |

|----------------|--------|--------------------|--|--|--|

| BIT            | SYMBOL | FUNCTION           |  |  |  |

| IR.7           | -      | Reserved           |  |  |  |

| IR.6           | -      | Reserved           |  |  |  |

| IR.5           | -      | Reserved           |  |  |  |

| IR.4           | WUI    | Wake-Up Interrupt  |  |  |  |

| IR.3           | 01     | Overrun Interrupt  |  |  |  |

| IR.2           | EI     | Error Interrupt    |  |  |  |

| IR.1           | TI     | Transmit Interrupt |  |  |  |

| IR.0           | RI     | Receive Interrupt  |  |  |  |

#### Table 7.10 Description of the Interrupt Register bits.

| INTERRUPT BIT              | VALUE                     | COMMENTS                                                                                                                                                                                                                                                                                                         |

|----------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Interrupt (note 1) | HIGH (set)<br>LOW (reset) | This bit is set when a new message is available in the Receive<br>Buffer and the Receive Interrupt Enable bit is HIGH (enabled).<br>Receive Interrupt bit is automatically reset by a read access of<br>Interrupt Register by the microcontroller.                                                               |

| Transmit Interrupt         | HIGH (set)<br>LOW (reset) | This bit is set whenever the Transmit Buffer Access is set<br>HIGH(released) and Transmit Interrupt Enable is set HIGH<br>(enabled).<br>Transmit Interrupt bit will be reset after a read access of the<br>Interrupt Register by the microcontroller.                                                            |

| Error Interrupt            | HIGH (set)<br>LOW (reset) | This bit is set on a change of either the Error Status or Bus Status<br>bits (see section 7.2.3) if the Error Interrupt Enable is set HIGH<br>(enabled).<br>the Error Interrupt bit is reset by a read access of the Interrupt<br>Register by the microcontroller.                                               |

| Wake-Up Interrupt          | HIGH (set)<br>LOW (reset) | The Wake-Up Interrupt bit is set HIGH, when the sleep mode is left<br>(see 7.2.2).<br>Wake-Up Interrupt bit is reset by a read access of Interrupt<br>Register by the microcontroller.                                                                                                                           |

| Overrun Interrupt (note 2) | HIGH (set)<br>LOW (reset) | This bit is set HIGH, if both Receive Buffers contain a message and<br>the first byte of another message should be stored (passed<br>acceptance), and the Overrun Interrupt Enable is set HIGH<br>(enabled).<br>Overrun Interrupt bit is reset by a read access of Interrupt Register<br>by the microcontroller. |

### Notes to Table 7.10

- 1. Receive Interrupt bit (if enabled) and Receive Buffer Status bit (see section 7.2.3) are set at the same time.

- 2. Overrun Interrupt bit (if enabled) and Data Overrun bit (see section 7.2.3) are set at the same time.

## PCA82C200

#### 7.2.5 ACCEPTANCE CODE REGISTER (ACR)

The Acceptance Code Register is part of the acceptance filter of the PCA82C200. This register can be accessed (read/write), if the Reset Request bit is set HIGH (present). When a message is received which passes the acceptance test and if there is an empty Receive Buffer, then the respective Descriptor and Data Field (see Fig 7.1) are sequentially stored in this empty buffer. In the case that there is no empty Receive Buffer, the Data Overrun bit is set HIGH (overrun), see sections 7.2.3 and 7.2.4. When the complete message has been correctly received the following occurs:

- the Receive Buffer Status bit is set HIGH (full)

- if the Receive Interrupt Enable bit is set HIGH (enabled), the Receive Interrupt is set HIGH (set).

The Acceptance Code bits (AC.7 - AC.0) and the eight most significant bits of the message's Identifier (ID.10 - ID.3) must be equal to those bit positions which are marked relevant by the Acceptance Mask bits (AM.7 - AM.0). If the following equation is satisfied, acceptance is given:

[(ID.10 .. ID.3)EQUAL(AC.7 .. AC.0)]OR (AM.7 .. AM.0) = 1111 1111<sub>b</sub>

Table 7.11 Acceptance Code Register bits.

|      | ACR : ADDRESS 4 |      |      |      |      |      |      |

|------|-----------------|------|------|------|------|------|------|

| 7    | 6               | 5    | 4    | 3    | 2    | 1    | 0    |

| AC.7 | AC.6            | AC.5 | AC.4 | AC.3 | AC.2 | AC.1 | AC.0 |

During transmission of a message which passes the acceptance test, the message is also written to its own Receive Buffer. If no Receive Buffer is available Data Overrun is signalled because it is not known at the start of a message whether the PCA82C200 will lose arbitration and so become a receiver of the message.

Table 7.13 Description of the Acceptance Mask Register bits.

| ACCEPTANCE MASK BIT | VALUE | COMMENTS                                                           |

|---------------------|-------|--------------------------------------------------------------------|

| AM.7 to AM.0        | HIGH  | This bit position is 'don't care' for the acceptance of a message. |

|                     | LOW   | This bit position is 'relevant' for acceptance filtering.          |

### 7.2.6 ACCEPTANCE MASK REGISTER (AMR)

The Acceptance Mask Register is part of the acceptance filter of the PCA82C200. This register can be accessed (read/write) if the Reset Request bit is set HIGH (present). The Acceptance Mask Register qualifies which of the corresponding bits of the acceptance code are 'relevant' or 'do not care' for acceptance filtering.

#### Table 7.12 Acceptance Mask Register bits.

|                 | AMR : ADDRESS 5 |      |      |      |      |      |      |      |

|-----------------|-----------------|------|------|------|------|------|------|------|

| 7 6 5 4 3 2 1 0 |                 |      |      |      |      | 0    |      |      |

|                 | AM.7            | AM.6 | AM.5 | AM.4 | AM.3 | AM.2 | AM.1 | AM.0 |

### PCA82C200

7.2.7 BUS TIMING REGISTER 0 (BTR 0)

The contents of Bus Timing Register 0 defines the values of the Baud Rate Prescaler (BRP) and the Synchronization Jump Width (SJW). This register can be accessed (read/ write) if the Reset Request bit is set HIGH (present).

Table 7.14 Bus Timing Register 0 bits.

|       | BTR 0 : ADDRESS 6 |       |       |       |       |       |       |

|-------|-------------------|-------|-------|-------|-------|-------|-------|

| 7     | 6                 | 5     | 4     | 3     | 2     | 1     | 0     |

| SJW.1 | SJW.0             | BRP.5 | BRP.4 | BRP.3 | BRP.2 | BRP.1 | BRP.0 |

#### Baud Rate Prescaler (BRP)

The period of the system clock  $t_{SCL}$  is programmable and determines the individual bit timing. The system clock is calculated using the following equation:

$t_{SCL} = 2t_{CLK}(32BRP.5 + 16BRP.4 + 8BRP.3 + 4BRP.2 + 2BRP.1 + BRP.0 + 1)$

$t_{CLK}$  = time period of the PCA82C200 oscillator.

#### Synchronization Jump Width (SJW)

To compensate for phase shifts between clock oscillators of different bus controllers, any bus controller must resynchronize on any relevant signal edge of the current transmission. The synchronization jump width defines the maximum number of clock cycles a bit period may be shortened or lengthened by one resynchronization:

$t_{SJW} = t_{SCL}(2SJW.1 + SJW.0 + 1)$

For further information on bus timing see sections 7.2.8 and 8.0.

#### Table 7.15 Bus Timing Register 1 bits.

|     | BTR 1 : ADDRESS 7 |         |         |         |         |         |         |

|-----|-------------------|---------|---------|---------|---------|---------|---------|

| 7   | 7 6 5 4 3 2 1 0   |         |         |         |         |         | 0       |

| SAM | TSEG2.2           | TSEG2.1 | TSEG2.0 | TSEG1.3 | TSEG1.2 | TSEG1.1 | TSEG1.0 |

### 7.2.8 BUS TIMING REGISTER 1 (BTR 1)

The contents of Bus Timing Register 1 defines the length of the bit period, the location of the sample point and the number of samples to be taken at each sample point. This register may be accessed (read/write) if the Reset Request bit is set HIGH (present).

#### Sampling (SAM)

#### Table 7.16 Selection of sampling

| BIT | VALUE | COMMENTS                 |

|-----|-------|--------------------------|

| SAM | HIGH  | Three samples are taken. |

|     | LOW   | The bus is sampled once. |

SAM = logic 0 is recommended for high speed buses (SAE class C), while SAM = logic 1 is recommended for slow/medium speed buses (class A and B) where filtering of spikes on the bus-line is beneficial (see section 8.1.6).

### Time Segment 1 (TSEG1) and Time Segment 2 (TSEG2)

TSEG1 and TSEG2 determine the number of clock cycles per bit period and the location of the sample point:

t<sub>TSEG1</sub> = t<sub>SCL</sub>(8TSEG1.3 + 4TSEG1.2 + 2TSEG1.1 + TSEG1.0 + 1)

$t_{TSEG2} = t_{SCL}(4TSEG2.2 + 2TSEG2.1 + TSEG2.0 + 1)$

For further information on bus timing see sections 7.2.7 and 8.0.

### PCA82C200

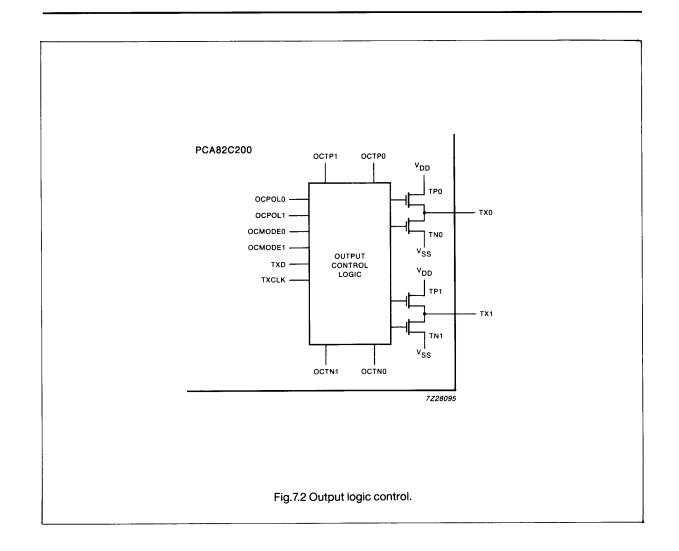

7.2.9 OUTPUT CONTROL REGISTER (OCR)

The Output Control Register allows, under software control, the set-up of different output driver configurations. This register may be accessed (read/write) if the Reset Request bit is set HIGH (present).

If the PCA82C200 is in the sleep mode (Goto Sleep = HIGH) a recessive level is output on the TX0 and TX1 pins. If the PCA82C200 is in the reset state (Reset Request = HIGH) the output drivers are floating.

## Test Output Mode

For the TX0 pin this is the same as in Normal Output Mode. To measure the delay time of the transmitter and receiver this mode connects the output of the input comparator (COMP OUT) with the input of the output driver TX1. This mode is used for production testing only.

Table 7.17 Output Control Register bits.

| OCR : ADDRESS 8 |                                                       |  |  |  |   |  |  |

|-----------------|-------------------------------------------------------|--|--|--|---|--|--|

| 7 6 5 4 3 2 1 0 |                                                       |  |  |  | 0 |  |  |

| OCTP1           | OCTP1 OCTN1 OCPOL1 OCTP0 OCTN0 OCPOL0 OCMODE1 OCMODE0 |  |  |  |   |  |  |

#### Normal Output Mode

In Normal Output Mode the bit sequence (TXD) is sent via TX0 and TX1. The voltage levels on the output driver pins TX1 and TX0 depend on both the driver characteristic programmed by OCTPx, OCTNx (float, pull-up, pull-down, push-pull) and the output polarity programmed by OCPOLX.

#### Clock Output Mode

For the TX0 pin this is the same as in Normal Output Mode. However, the data stream to TX1 is replaced by the transmit clock (TXCLK). The rising edge of the transmit clock (non inverted) marks the beginning of a bit period. The clock pulse width is  $t_{SCL}$ .

#### Bi-phase Output Mode

In contrast to Normal Output Mode the bit representation is time variant and toggled. If the bus controllers are galvanically decoupled from the bus-line by a transformer, the bit stream is not allowed to contain a DC component. This is achieved by the following scheme. During recessive bits all outputs are deactivated (3-state). Dominant bits are sent alternatingly on TX0 and TX1, i.e. the first dominant bit is sent on TX0, the second is sent on TX1, and the third one is sent on TX0 again, etc.

## PCA82C200

The following two tables, Table 7.18 and Table 7.19, show the relationship between the bits of the Output Control Register and the two serial output pins TX0 and TX1 of the PCA82C200, connected to the serial bus (see Fig.2.1).

Table 7.18 Description of the Output Mode bits.

| OCMODE1 | OCMODE0 | DESCRIPTION                                                   |

|---------|---------|---------------------------------------------------------------|

| 1       | 0       | Normal Output Mode; TX0, TX1: bit sequence (TXD; note 1).     |

| 1       | 1       | Clock Output Mode; TX0: bit sequence, TX1: bus clock (TXCLK). |

| 0       | 0       | Bi-phase Output Mode                                          |

| 0       | 1       | Test Output Mode; TX0: bit sequence, TX1: COMP OUT            |

### Note to Table 7.18

1. TXD is the data bit to be transmitted.

Table 7.19 Output pin set-up.

| DRIVE     | OCTPx | OCTNx | OCPOLx | TXD | TPx | TNx | TXx   |

|-----------|-------|-------|--------|-----|-----|-----|-------|

| Float     | 0     | 0     | 0      | 0   | Off | Off | float |

|           | 0     | 0     | 0      | 1   | Off | Off | float |

|           | 0     | 0     | 1      | 0   | Off | Off | float |

|           | 0     | 0     | 1      | 1   | Off | Off | float |

| Pull-down | 0     | 1     | 0      | 0   | Off | On  | LOW   |

|           | 0     | 1     | 0      | 1   | Off | Off | float |

|           | l o   | 1     | 1      | 0   | Off | Off | float |

|           | 0     | 1     | 1      | 1   | Off | On  | LOW   |

| Pull-up   | 1     | 0     | 0      | 0   | Off | Off | float |

| •         | 1     | 0     | 0      | 1   | On  | Off | HIGH  |

|           | 1     | 0     | 1      | 0   | On  | Off | HIGH  |

|           | 1     | 0     | 1      | 1   | Off | Off | float |

| Push/Puli | 1     | 1     | 0      | 0   | Off | On  | LOW   |

|           | 1     | 1     | 0      | 1   | On  | Off | HIGH  |

|           | 1     | 1     | 1      | 0   | On  | Off | HIGH  |

|           | 1     | 1     | 1      | 1   | Off | On  | LOW   |

#### Notes to Table 7.19

- 1. TPx is the on-chip output transistor x, connected to V<sub>DD</sub>; x = 0 or 1.

- TNx is the on-chip output transistor x, connected to V<sub>SS</sub>; x = 0 or 1.

- TXx is the serial output level on pin TX0 or TX1. It is required that the output level on the CAN bus is dominant with TXD = 0 and recessive with TXD = 1 (see section 9.1.1)

#### 7.2.10 TEST REGISTER (TR)

The Test Register is used for production testing only.

### PCA82C200

#### 7.3 Transmit Buffer layout

The global layout of the Transmit Buffer is shown in Fig.7.1. This buffer serves to store a message from the microcontroller to be transmitted by the PCA82C200. It is subdivided into Descriptor and Data Field. The Transmit Buffer can be written to and read from by the microcontroller (see note 1 to Table 7.3).

7.3.1 DESCRIPTOR

### Table 7.20 Descriptor Byte 1 (DSCR1).

| DSCR1 : ADDRESS 10 |      |      |      |      |      |      |      |

|--------------------|------|------|------|------|------|------|------|

| 7                  | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| ID.10              | ID.9 | ID.8 | ID.7 | ID.6 | ID.5 | ID.4 | ID.3 |

### Table 7.21 Descriptor Byte 2 (DSCR2).

| DSCR2 : ADDRESS 11 |      |      |     |       |       |       |       |

|--------------------|------|------|-----|-------|-------|-------|-------|

| 7                  | 6    | 5    | 4   | 3     | 2     | 1     | 0     |

| ID.2               | ID.1 | ID.0 | RTR | DLC.3 | DLC.2 | DLC.1 | DLC.0 |

#### Identifier (ID)

The Identifier consists of 11 bits (ID.10 to ID.0). ID.10 is the most significant bit, which is transmitted first on the bus during the arbitration process. The Identifier acts as the message's name, used in a receiver for acceptance filtering, and also determines the bus access priority during the arbitration process. The lower the binary value of the Identifier the higher the priority. This is due to the larger number of leading dominant bits during arbitration (see section 5).

#### Remote Transmission Request bit (RTR)

#### Table 7.22 Description of the RTR bit.

| BIT | VALUE       | COMMENTS                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| RTR | HIGH<br>LOW | Remote Frame will be transmitted<br>by the PCA82C200<br>Data Frame will be transmitted by<br>the PCA82C200. |

### Data Length Code (DLC)

The number of bytes (Data Byte Count) in the Data Field of a message is coded by the Data Length Code. At the start

of a Remote Frame transmission the Data Length Code is not considered due to the RTR bit being HIGH (remote). This forces the number of transmitted/received data bytes to be 0. Nevertheless, the Data Length Code must be specified correctly to avoid bus errors, if two CANcontrollers start a Remote Frame transmission simultaneously.

The range of the Data Byte Count is 0 to 8 bytes and coded as follows:

Data Byte Count = 8DLC.3 + 4DLC.2 + 2DLC.1 + DLC.0

For reasons of compatibility no Data Byte Counts other than 0 to 8 should be used.

#### 7.3.2 DATA FIELD

The number of transferred data bytes is determined by the Data Length Code. The first bit transmitted is the most significant bit of data byte 1 at address 12.

#### 7.4 Receive Buffer layout

The layout of the Receive Buffer and the individual bytes correspond to the definitions given for the Transmit Buffer layout, except that the addresses start at 20 instead of 10 (see Fig 7.1).

#### 7.5 Clock Divider Register (CDR)

The Clock Divider Register controls the CLK OUT frequency for the microcontroller (see Fig.2.1). It can be written to or read by the microcontroller. The default state of the register is divided by 12 for Motorola mode and divided by 2 for Intel mode. Values from 0 to 7 may be written into this register and will result in the CLK OUT frequencies shown in Table 7.24.

#### Table 7.23 Clock Divider Register bits.

| CDR : ADDRESS 31 |   |   |   |   |      |      |      |

|------------------|---|---|---|---|------|------|------|

| 7                | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

| -                | - | - | - | - | CD.2 | CD.1 | CD.0 |

Bits CDR.7 to CDR.3 are reserved.

October 1990

#### Table 7.24 CLK OUT frequency selection.

| CD.2 | CD.1 | CD.0 | CLK OUT FREQUENCY    |

|------|------|------|----------------------|

| 0    | 0    | 0    | f <sub>CLK</sub> /2  |

| 0    | 0    | 1    | fclk/4               |

| 0    | 1    | 0    | f <sub>CLK</sub> /6  |

| 0    | 1    | 1    | f <sub>CLK</sub> /8  |

| 1    | 0    | 0    | f <sub>CLK</sub> /10 |

| 1    | 0    | 1    | f <sub>CLK</sub> /12 |

| 1    | 1    | 0    | f <sub>CLK</sub> /14 |

| 1    | 1    | 1    | fCLK                 |

Note: f<sub>CLK</sub> is the frequency of the oscillator

#### 8.0 BUS TIMING/SYNCHRONIZATION

The Bus Timing Logic (BTL) monitors the serial bus-line via the on-chip input comparator and performs the following functions (see section 2):

- · monitors the serial bus-line level

- adjusts the sample point, within a bit period (programmable)

- samples the bus-line level using majority logic (programmable, 1 or 3 samples)

- Synchronization to the bit stream:

- Hard synchronization at the start of a message

- Resynchronization during transfer of a message.

The configuration of the BTL is performed during the initialization of the PCA82C200. The BTL uses the following three registers:

- Control register (Synch)

- Bus Timing Register 0

- Bus Timing Register 1.

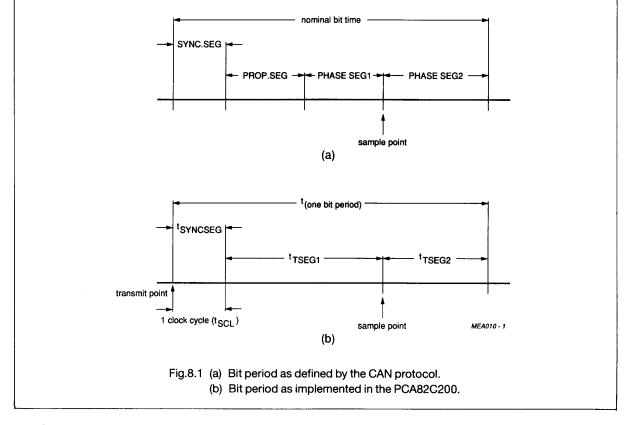

#### 8.1 Bit timing

A bit period is built up from a number of system clock cycles ( $t_{SCL}$ ), see section 7.2.7. One bit period is the result of the addition of the programmable segments TSEG1 and TSEG2 and the general segment SYNCSEG (see sections 7.2.7 to 7.2.8.).

### PCA82C200

#### 8.1.1 SYNCHRONIZATION SEGMENT (SYNCSEG)

The incoming edge of a bit is expected during this state; this state corresponds to one system clock cycle  $(1 \times t_{SCL})$ .

#### 8.1.2 TIME SEGMENT 1 (TSEG1)

This segment determines the location of the sampling point within a bit period, which is at the end of TSEG1. TSEG1 is programmable from 1 to 16 system clock cycles (see section 7.2.8).

The correct location of the sample point is essential for the correct functioning of a transmission. The following points must be taken into consideration:

- A Start-Of-Frame (see section 9.2.1) causes all PCA82C200's to perform a 'hard synchronization' (see section 8.2.1) on the first recessive-to-dominant edge. During arbitration, however, several PCA82C200's may simultaneously transmit. Therefore it may require twice the sum of bus-line, input comparator and the output driver delay times until the bus is stable. This is the propagation delay which must be taken into consideration.

- To avoid sampling at an incorrect position, it is necessary to include an additional synchronization buffer on both sides of the sample point. The main reasons for incorrect sampling are:

- incorrect synchronization due to spikes on the busline

- slight variations in the oscillator frequency of each PCA82C200 in the network, which results in a phase error.

#### 8.1.3 TIME SEGMENT 2 (TSEG2)

This time segment provides:

- additional time at the sample point for calculation of the subsequent bit levels (e.g. arbitration)

- synchronization buffer at right side of the sample point (see section 8.1.2).

TSEG2 is programmable from 1 to 8 system clock cycles (see section 7.2.8).

#### 8.1.4 SYNCHRONIZATION JUMP WIDTH (SJW)

SJW defines the maximum number of clock cycles (t<sub>SCL</sub>) a bit period may be reduced or increased by one resynchronization. SJW is programmable from 1 to 4 system clock cycles (see section 7.2.7).

### 8.1.5 PROPAGATION DELAY TIME (tprop).

The propagation delay time is calculated by summing the maximum propagation delay times of the physical bus, the input comparator and the output driver. The resulting sum is multiplied by 2 and then rounded up to the nearest multiple of  $t_{SCL}$ .

tprop = 2 x (physical bus delay + input comparator delay + output driver delay)

#### 8.1.6 BIT TIMING RESTRICTIONS

Restrictions on the configuration of the bit timing are based on internal processing. The restrictions are:

- t<sub>TSEG2</sub> ≥ 2t<sub>SCL</sub>

- t<sub>TSEG2</sub> ≥ t<sub>SJW</sub>

- tTSEG1 ≥ tTSEG2

- t<sub>TSEG1</sub> ≥ t<sub>SJW</sub> + t<sub>prop</sub>

The three sample mode (SAM = 1) has the effect of introducing a delay of one system clock cycle on the busline. This must be taken into account for the correct calculation of TSEG1 and TSEG2:

- $t_{TSEG1} \ge t_{SJW} + t_{prop} + t_{SCL}$

- t<sub>TSEG2</sub> ≥ 3t<sub>SCL</sub>

#### 8.2 Synchronization

Synchronization is performed by a state machine which compares the incoming edge with its actual bit timing and adapts the bit timing by hard synchronization or resynchronization.

#### 8.2.1 HARD SYNCHRONIZATION

This type of synchronization occurs only at the beginning of a message. The PCA82C200 synchronizes on the first incoming recessive-to-dominant edge of a message (being the leading edge of a message's Start-Of-Frame bit; see section 8.1).

October 1990

## PCA82C200

#### 8.2.2 RESYNCHRONIZATION

Resynchronization occurs during the transmission of a message's bit stream to compensate for:

- variations in individual PCA82C200 oscillator frequencies

- changes introduced by switching from one transmitter to another (e.g. during arbitration).

As a result of resynchronization either  $t_{TSEG1}$  may be increased by up to a maximum of  $t_{SJW}$  or  $t_{TSEG2}$  may be decreased by up to a maximum of  $t_{SJW}$ :

- $t_{TSEG1} \leq t_{SCL}((TSEG1 + 1) + (SJW + 1))$

- $t_{TSEG2} \ge t_{SCL}((TSEG2 + 1) (SJW + 1))$

Note: TSEG1, TSEG2 and SJW are the programmed numerical values.

The phase error (e) of an edge is given by the position of the edge relative to SYNCSEG, measured in system clock cycles ( $t_{SCL}$ ). The value of the phase error is defined as:

- e = 0, if the edge occurs within SYNCSEG

- e > 0, if the edge occurs within TSEG1

- e < 0, if the edge occurs within TSEG2.

The effect of resynchronization is:

- the same as that of a hard synchronization, if the magnitude of the phase error (e) is less or equal to the programmed value of t<sub>SJW</sub> (see section 7.2.7)

- to increase a bit period by the amount of t<sub>SJW</sub>, if the phase error is positive and the magnitude of the phase error is larger than t<sub>SJW</sub>.

- to decrease a bit period by the amount of t<sub>SJW</sub>, if the phase error is negative and the magnitude of the phase error is larger than t<sub>SJW</sub>.

#### 8.2.3 SYNCHRONIZATION RULES

The synchronization rules are as follows:

- only one synchronization within one bit time is used.

- an edge is used for synchronization only if the value detected at the previous sample point differs from the bus value immediately after the edge

- hard synchronization is performed whenever there is a

recessive-to-dominant edge during Bus-Idle (see section 8)

- all other edges (recessive-to-dominant and optionally dominant-to-recessive edges if the Synch bit is set HIGH; see section 7.2.1) which are candidates for resynchronization will be used with the following exception:

- A transmitting PCA82C200 will not perform a resynchronization as a result of a recessive-todominant edge with positive phase error, if only these edges are used for resynchronization. This ensures that the delay times of the output driver and input comparator do not cause a permanent increase in the bit time.

#### 9.0 COMMUNICATION PROTOCOL

#### 9.1 Frame types

The PCA82C200 bus controller supports the four different CAN protocol frame types for communication:

- Data Frame, to transfer data

- Remote Frame, request for data

- Error Frame, globally signal a (locally) detected error condition

- Overload Frame, to extend delay time of subsequent frames

#### 9.1.1 BIT REPRESENTATION

There are two logical bit representations used in the CAN protocol:

- A recessive bit on the bus-line appears only if all connected PCA82C200's send a recessive bit at that moment

- Dominant bits always overwrite recessive bits i.e. the resulting bit level on the bus-line is dominant.

### PCA82C200

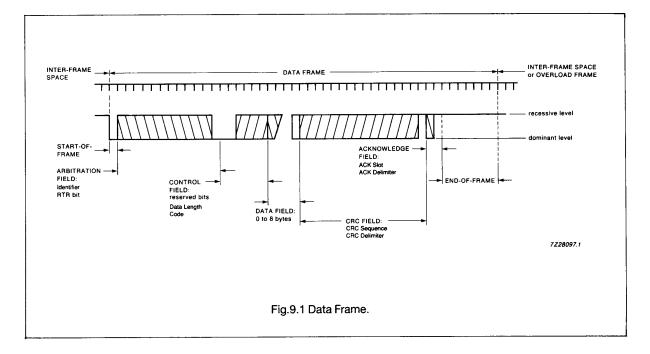

### 9.2. Data Frame

A Data Frame carries data from a transmitting PCA82C200 to one or more receiving PCA82C200's. A Data Frame is composed of seven different bit-fields:

- Start-Of-Frame

- Arbitration Field

- Control Field

- · Data Field (may have a length of zero)

- CRC Field

- Acknowledge Field

- End-Of-Frame.

#### 9.2.1 START-OF-FRAME BIT

Signals the start of a Data Frame or Remote Frame. It consists of a single dominant bit used for hard synchronization of a PCA82C200 in receive mode.

#### 9.2.2 ARBITRATION FIELD

Consists of the message Identifier and the RTR bit (see section 7.3.1). In the event of simultaneous message transmissions by two or more PCA82C200's the bus access conflict is solved by bit-wise arbitration, which is active during the transmission of the Arbitration Field.

#### Identifier

This 11-bit field is used to provide information about the message, as well as the bus access priority. It is transmitted in the order ID.10 to ID.0 (LSB). The situation that the seven most significant bits (ID.10 to ID.4) are all recessive must not occur.

An Identifier does not define which particular PCA82C200 will receive the frame, as a CAN based communication network does not discriminate between a point-to-point, multicast or broadcast communication.

## PCA82C200

#### Remote Transmission Request bit (RTR)

A PCA82C200, acting as a receiver for certain information may initiate the transmission of the respective data by transmitting a Remote Frame to the network, addressing the data source via the Identifier and setting the RTR bit HIGH (remote; recessive bus level). If the data source simultaneously transmits a Data Frame containing the requested data, it uses the same Identifier. No bus access conflict occurs due to the RTR bit being set LOW (data; dominant bus level) in the Data Frame.

#### 9.2.3 CONTROL FIELD

This field consists of six bits. It includes two reserved bits (for future expansions of the CAN-protocol), transmitted with a dominant bus level, and is followed by the Data Length Code (4 bits). The number of bytes in the (destuffed; number of data bytes to be transmitted/ received) Data Field is indicated by the Data Length Code. Admissible values of the Data Length Code and hence the number of bytes in the (destuffed) Data Field, are 0 to 8. A logic 0 (logic 1) in the Data Length Code is transmitted as a dominant (recessive) bus level, respectively.

#### 9.2.4 DATA FIELD

The data, stored within the Data Field of the Transmit Buffer, are transmitted according to the Data Length Code. Conversely, data of a received Data Frame will be stored in the Data Field of a Receive Buffer. Data is stored byte-wise both for transmission by the microcontroller and on reception by the PCA82C200. The most significant bit of the first data byte (lowest address) is transmitted/received first.

#### 9.2.5 CYCLIC REDUNDANCY CODE FIELD (CRC)

The CRC Field consists of the CRC Sequence (15 bits) and the CRC Delimiter (1 recessive bit). The Cyclic Redundancy Code (CRC) encloses the destuffed bit stream of the Start-Of-Frame, Arbitration Field, Control Field, Data Field and CRC Sequence. The most significant bit of the CRC Sequence is transmitted/ received first. This frame check sequence, implemented in the PCA82C200, is derived from a cyclic redundancy code best suited for frames with a total bit count of less than 127 bits, see section 9.8.3. With Start-Of-Frame (dominant bit) included in the code word, any rotation of the code word can be detected by the absence of the CRC Delimiter (recessive bit).

#### 9.2.6 ACKNOWLEDGE FIELD (ACK)

The Acknowledge Field consists of two bits, the Acknowledge Slot and the Acknowledge Delimiter, which are transmitted with a recessive level by the transmitter of the Data Frame. All PCA82C200's having received the matching CRC Sequence, report this by overwriting the transmitter's recessive bit in the Acknowledge Slot with a dominant bit (see section 9.9.2). Thereby a transmitter, still monitoring the bus level recognizes that at least one receiver within the network has received a complete and correct message (i.e. no error was found). The Acknowledge Delimiter (recessive bit) is the second bit of the Acknowledge Field. As a result, the Acknowledge Slot is surrounded by two recessive bits: the CRC Delimiter and the Acknowledge Delimiter.

All nodes within a CAN network may use all the information coming to the network by the PCA82C200's (shared memory concept). Therefore, acknowledgement and error handling are defined to provide all information in a consistent way throughout this shared memory. Hence, there is no reason to discriminate different receivers of a message in the acknowledge field. If a node is disconnected from the network due to bus failure, this particular node is no longer part of the shared memory. To identify a "lost node" additional and application specific precautions are required.

#### 9.2.7 END-OF-FRAME

Each Data Frame or Remote Frame is delimited by the End-Of-Frame bit sequence which consists of seven recessive bits (exceeds the bit stuff width by two bits). Using this method a receiver detects the end of a frame independent of a previous transmission error because the receiver expects all bits up to the end of the CRC sequence to be coded by the method of bit-stuffing (see section 9.7.3 Coding/Decoding). The bit-stuffing logic is deactivated during the End-Of-Frame sequence.

## PCA82C200

#### 9.3 Remote Frame

A PCA82C200, acting as a receiver for certain information may initiate the transmission of the respective data by transmitting a Remote Frame to the network, addressing the data source via the Identifier and setting the RTR bit HIGH (remote; recessive bus level). The Remote Frame is similar to the Data Frame with the following exceptions:

- RTR bit is set HIGH

- Data Length Code is ignored.

- no Data Field contained.

Note that the Data Length Code value should be the same as for the corresponding Data Frame (although this is ignored for a Remote Frame).

A Remote Frame is composed of six different bit fields:

- Start-Of-Frame

- Arbitration Field

- Control Field

- CRC-Field

- Acknowledge Field

- End-Of-Frame.

See section 9.2 for a more detailed explanation of the Remote Frame bit fields.

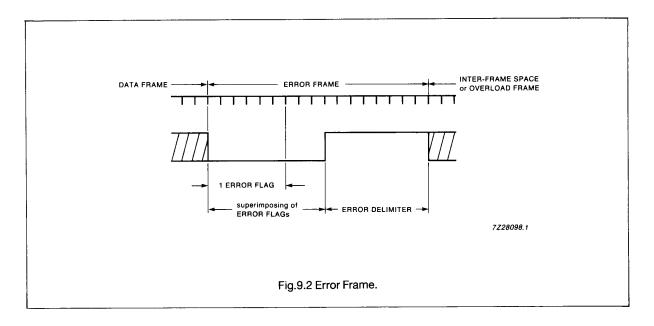

#### 9.4 Error Frame

The Error Frame consists of two different fields. The first field is accomplished by the superimposing of Error Flags contributed from different PCA82C200s. The second field is the Error Delimiter (see Fig.9.2).

#### 9.4.1 ERROR FLAG

There are two forms of an Error Flag:

- Active Error Flag, consists of six consecutive dominant bits

- Passive Error Flag, consists of six consecutive recessive bits unless it is overwritten by dominant bits from other PCA82C200's.

An error-active PCA82C200 (see section 9.9) detecting an error condition signals this by transmission of an Active Error Flag. This Error Flag's form violates the bit-stuffing law (see section 9.7.3) applied to all fields, from Start-Of-

Frame to CRC Delimiter, or destroys the fixed form of the fields Acknowledge Field or End-Of-Frame (see Fig 9.1). Consequently, all other PCA82C200's detect an error condition and start transmission of an Error Flag. Therefore the sequence of dominant bits, which can be monitored on the bus, results from a superposition of different Error Flags transmitted by individual PCA82C200's. The total length of this sequence varies between six (min) and twelve (max) bits.