## 查询S2100供应商

## **Contents**

| Features                         | . 1 |

|----------------------------------|-----|

| Applications                     | . 1 |

| Pin Assignment                   | . 1 |

| Block Diagram                    | . 1 |

| Terminal Description             | . 2 |

| Mode Table                       | . 2 |

| Absolute Maximum Ratings         | . 2 |

| Recommended Operating Conditions | . 2 |

| DC Electrical Characteristics    | . 3 |

| AC Electrical Characteristics    | . 3 |

| Read Mode Operation              | . 4 |

| Counter Hold Mode Operation      | . 4 |

| Program Mode Operation           | . 5 |

| Input Priority                   | . 6 |

| Notes                            | . 6 |

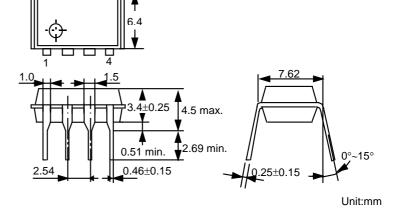

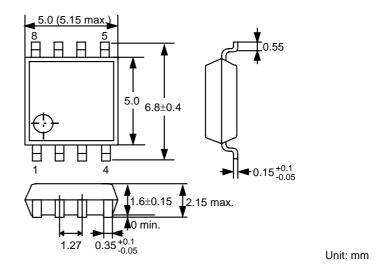

| Dimensions                       | . 7 |

| Characteristics                  | 8   |

range. Data can be read serially by clock pulses from address address 64. All the addresses are initialized at "H" so writing in can be done only once.

### **■** Features

- Low standby current (0.3 μA max., V<sub>DD</sub>=1.5 V)

- Wide operating voltage range

### ■ Applications

- Pager ID ROM

- Cordless telephone

- Security equipment

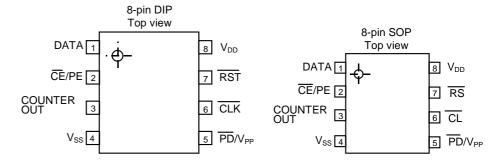

### ■ Pin Assignment

Figure 1

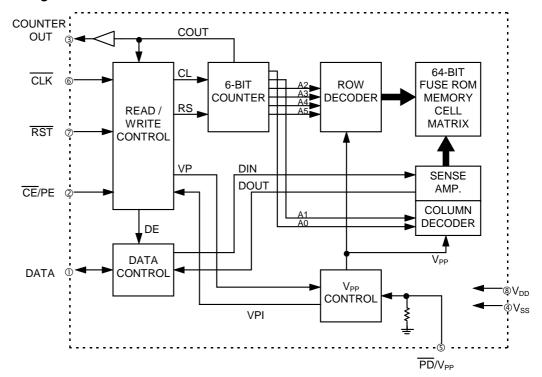

## **■** Block Diagram

Figure 2

| 2 | CE/PE                           | Mode select terminal           | (Refer to operation mode table)                                                                                         |

|---|---------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 3 | COUNTER<br>OUT                  | Counter output terminal        | 6-bit counter; 64th bit detection output terminal                                                                       |

| 4 | $V_{SS}$                        | Negative power supply terminal | Normally, connected to GND.                                                                                             |

| 5 | P <sub>D</sub> /V <sub>PP</sub> | Program voltage input terminal | Input terminal of writing voltage to FUSE memory at 21 V. (Refer to operation mode table.) Pull-down resistor built in. |

| 6 | CLK                             | Clock input terminal           | Clock input terminal of 6-bit counter. Operates at the falling edge.                                                    |

| 7 | RST                             | Reset input terminal           | Reset input terminal of 6-bit counter. Operates at "L".                                                                 |

| 8 | $V_{DD}$                        | Positive power supply terminal | Normally, connected to +1.1 to +5.5 V.                                                                                  |

## ■ Mode Table

Table 2

| Terminal<br>Read | CE/PE                                        | $\overline{P}_D/V_{PP}$ | DP CLK RST       |                  | DATA           |  |

|------------------|----------------------------------------------|-------------------------|------------------|------------------|----------------|--|

| Read             | $V_{SS}$                                     | $V_{SS}$                | Input possible   | Input possible   | Data output    |  |

| Counter hold     | Counter hold V <sub>DD</sub> V <sub>SS</sub> |                         | Input impossible | Input impossible | High impedance |  |

| Program          | $V_{DD}$                                     | $V_{PP}$                | Input impossible | Input impossible | Data input     |  |

# ■ Absolute Maximum Ratings

Table 3

| 14.5.0                                        |                   |                                |      |  |  |

|-----------------------------------------------|-------------------|--------------------------------|------|--|--|

| Parameter                                     | Symbol            | Ratings                        | Unit |  |  |

| Power supply voltage                          | $V_{DD}$          | -0.3 to +6.5                   | V    |  |  |

| P <sub>D</sub> /V <sub>PP</sub> input voltage | $V_{PP}$          | -0.3 to 26                     | V    |  |  |

| Input voltage                                 | $V_{IN}$          | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 | V    |  |  |

| Output voltage                                | V <sub>OUT</sub>  | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 | V    |  |  |

| Storage temperature under bias                | $V_{\text{bias}}$ | -30 to +85                     | °C   |  |  |

| Storage temperature                           | $V_{stg}$         | -40 to +125                    | °C   |  |  |

# ■ Recommended Operating Conditions

Table 4

| Parameter                 | Symbol             | Conditions                           | Min.                 | Тур. | Max.     | Unit |

|---------------------------|--------------------|--------------------------------------|----------------------|------|----------|------|

| Dawar awarb walta sa      | .,                 | Ta=25°C, Read, t <sub>CH</sub> =15μs | 1.1                  | 1.5  | 5.5      | V    |

| Power supply voltage      | $V_{DD}$           | Ta=25°C, Write                       | 4.5                  | 5.0  | 5.5      | V    |

| Llieb level innut veltage | ge V <sub>IH</sub> | Ta=25°C, Read                        | V <sub>DD</sub> -0.3 |      | $V_{DD}$ | V    |

| High level input voltage  |                    | Ta=25°C, Write                       | V <sub>DD</sub> -0.3 |      | $V_{DD}$ | V    |

| Low level input voltage   | M                  | Ta=25°C, Read                        | -0.3                 |      | 0.3      | V    |

|                           | $V_{IL}$           | Ta=25°C, Write                       | -0.3                 |      | 0.5      | V    |

| Operating temperature     | $V_{opr}$          |                                      | -20                  |      | 70       | °C   |

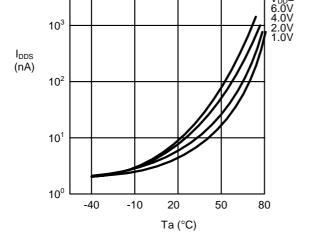

| Consumption                                   |                  |                                                                                                                            |      |     |     |    |

|-----------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------|------|-----|-----|----|

| Standby current consumption                   | I <sub>DDS</sub> | $V_{DD}$ =1.5 V, $\overline{RS}$ T= $V_{DD}$<br>$\overline{CLK}$ = $V_{DD}$ , $\overline{CE}$ / $\overline{PE}$ = $V_{SS}$ | _    |     | 0.3 | μА |

| P <sub>D</sub> /V <sub>PP</sub> input voltage | $V_{PP}$         |                                                                                                                            | 20   | 21  | 22  | V  |

| P <sub>D</sub> /V <sub>PP</sub> input current | I <sub>PP</sub>  |                                                                                                                            | _    | _   | 150 | mA |

|                                               | I <sub>OH</sub>  | V <sub>DD</sub> =1.1 to 5.5 V, V <sub>OH</sub> =V <sub>DD</sub> -0.3 V                                                     | -300 | _   | _   | μΑ |

| Output current                                | I <sub>OL</sub>  | V <sub>DD</sub> =1.1 to 5.5 V, V <sub>OH</sub> =0.3 V                                                                      | 300  | _   | _   | μΑ |

| Pull-down resistance                          | $R_D$            | V <sub>DD</sub> =1.5 V                                                                                                     | 0.1  | 0.2 | 0.4 | МΩ |

## ■ AC Electrical Characteristics

## 1. Read mode

Table 6

(Ta=25°C, V<sub>DD</sub>=1.5 V)

| Parameter                | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------------|------------------|------|------|------|------|

| RST hold time            | t <sub>RH</sub>  | 5.0  | _    | _    | μS   |

| Read cycle time          | t <sub>RC</sub>  | 2.0  | _    | _    | μS   |

| CLK hold time            | t <sub>CH</sub>  | 5.0  | _    | _    | μS   |

| Access time              | t <sub>ACC</sub> |      | _    | 5.0  | μS   |

| CE/PE setup time         | t <sub>CES</sub> | 2.0  | _    | _    | μS   |

| RST setup time           | t <sub>RS</sub>  | 5.0  | _    | _    | μS   |

| CLK setup time           | t <sub>CS</sub>  | 5.0  | _    | _    | μS   |

| CE access time           | t <sub>CE</sub>  | _    | _    | 5.0  | μS   |

| Output disable time      | t <sub>WZ</sub>  |      | _    | 500  | ns   |

| CLK and RST inhibit time | t <sub>CRI</sub> |      | _    | 500  | ns   |

Load: 60 pF

## 2. Write mode

Table 7

(Ta=25°C, Vpp=5.0 V, Vpp=21 V)

|                            |                  | (Ta: | =25°C, V <sub>D</sub> | <sub>D</sub> =5.0 V, V | V <sub>PP</sub> =Z1 V) |

|----------------------------|------------------|------|-----------------------|------------------------|------------------------|

| Parameter                  | Symbol           | Min. | Тур.                  | Max.                   | Unit                   |

| CE-data setup time         | t <sub>CDS</sub> | 0.5  | _                     | _                      | μs                     |

| Data setup time            | t <sub>DS</sub>  | 0.5  | _                     | _                      | μS                     |

| Data hold time             | t <sub>DH</sub>  | 0    | _                     | _                      | μS                     |

| CE-data hold time          | t <sub>CDH</sub> | 2.0  | _                     | _                      | μS                     |

| V <sub>PP</sub> rise time  | t <sub>r</sub>   | 20   | _                     | _                      | μS                     |

| Program pulse width        | t <sub>PW</sub>  | 8.0  | _                     | _                      | ms                     |

| V <sub>PP</sub> rise slope | $\Delta V_{PP}$  | _    | _                     | 4                      | V/μs                   |

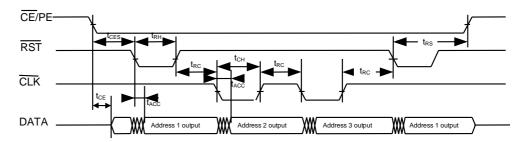

read by the RST pulse.

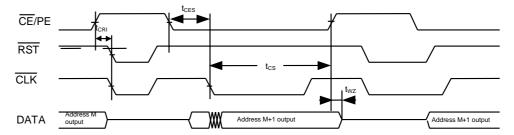

Figure 3 Read mode timing

- \*1 When both the CLK and RST terminals are at "H" level.

- When the RST terminal is at "L" level, the latch is transparent and the data is recognized by the rising of the RST pulse.

- Data read by the CLK pulse is latched at its rising.

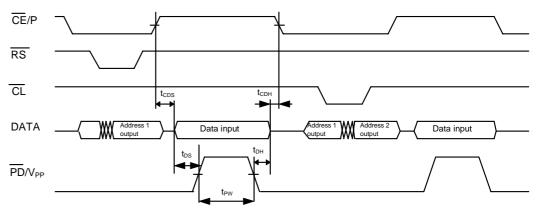

### **■ Counter Hold Mode Operation**

By setting the CE/PE terminal to "H" level, the S-2100R enters the counter hold mode and the DATA terminal becomes high impedance.

In counter hold mode, the  $\overline{\text{CLK}}$  and  $\overline{\text{RST}}$  pulses which fall while the  $\overline{\text{CE}}/\text{PE}$  terminal is at "H" level are recognized to be invalid and there is no change in counter and data output. When the  $\overline{\text{CE}}/\text{PE}$  terminal is set to "L" level again, it returns to the condition in which it was before the counter hold mode.

Figure 4 Counter hold mode timing

\*4 When both the CLK and RST terminals are at "H" level.

be written into the selected address only office.

If you coutinue writing from address 1 to 64, the output of the COUNTER OUT terminal goes to "H" level, just like in the read and no more  $\overline{\text{CLK}}$  pulses or writing pulses in program mode can be accepted.

Figure 5 Program mode timing

- \*5 In program mode, operate at VDD=5.0 V to assure reliability of the data writing.

- The selection of addresses is possible only in read mode. Address 1 is selected by RST pulses and writing proc sequentially from address 1 by CLK pulse.

- All the memories are initially at "H" level, so writing into "L" can be done. When data is at "H" level, writing voltage can be supplied to the memory.

- Address 1 is selected again by the RST pulse. The addresses which are not written to "L" level are at "H" level, so w "L" level in these addresses is possible.

If the  $\overline{\text{CLK}}$  and  $\overline{\text{RST}}$  pulses which are input in the counter hold mode are still at "L" level after setting the  $\overline{\text{CE}}/\text{PE}$  terminal to "L" level, these  $\overline{\text{CLK}}$  and  $\overline{\text{RST}}$  terminals are ignored. The mode shifts to read mode and data which is held before the shift is output at the DATA terminal. \*11

In program mode, inputting the DATA terminal before the  $\overline{\text{CE}}/\text{PE}$  terminal goes to "H" level is prohibited. Also, charging the writing voltage from the  $P_D/V_{PP}$  terminal is prohibited when the  $\overline{\text{CE}}/\text{PE}$  terminal is at "L" level. In program mode, input to the DATA terminal muse be decided before charging the writing voltage. \*12

- \*9 Input of the CLK and RST pulses is not recognized as valid unless both pulses are input at "H" level.

- \*10 The counter hold mode is entered when reading of the CLK and RST pulses has been finished and DATA output has been stabilized .

- \*11 No more CLK or RST pulses are accepted unless both the CLK and RST terminals are at "H" level.

- \*12 If data input is changed while writing voltage is supplied, the S-2100R does not accept the changed data.

#### ■ Notes

Memory should not be accessed for at least 10  $\mu s$  after voltage is supplied and goes to  $V_{DD}$ .

2. 8-pin SOP

Figure 6

Figure 7

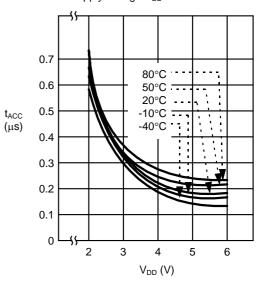

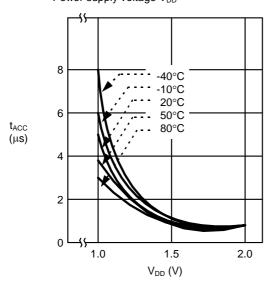

2. Access time  $t_{ACC}$ Power supply voltage  $V_{DD}$

3. Access time  $t_{ACC}$ -Power supply voltage  $V_{DD}$