#### 查询TPS2070供应商

## 捷多邦,专业PCB打样工厂,24小町**PPS207**0, TPS2071 FOUR-PORT USB HUB POWER CONTROLLERS

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

- Complete USB Hub Power Solution

- Meets USB Specifications 1.1 and 2.0

- Independent Thermal and Short-Circuit Protection

- 3.3-V Regulator for USB Hub Controller

- Overcurrent Logic Outputs

- 4.5-V to 5.5-V Operating Range

- CMOS- and TTL-Compatible Enable Inputs

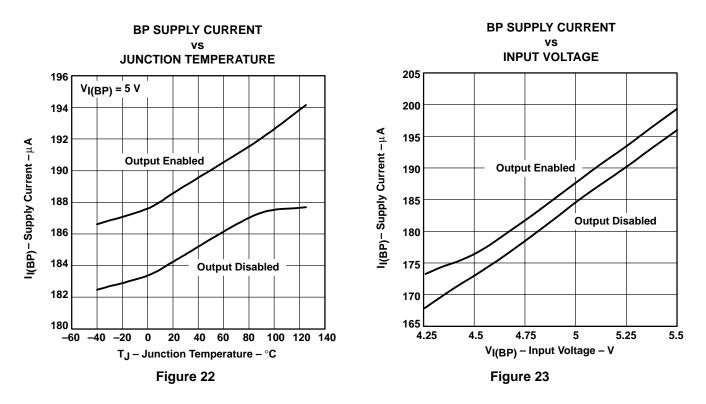

- 185 μA Bus-Power Supply Current

- Available in 32-Pin HTSSOP PowerPAD<sup>™</sup>

- –40°C to 85°C Ambient Temperature Range

#### description

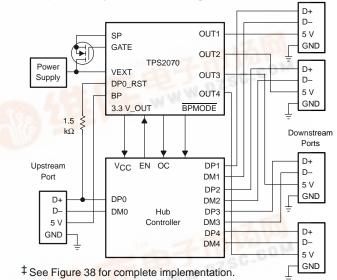

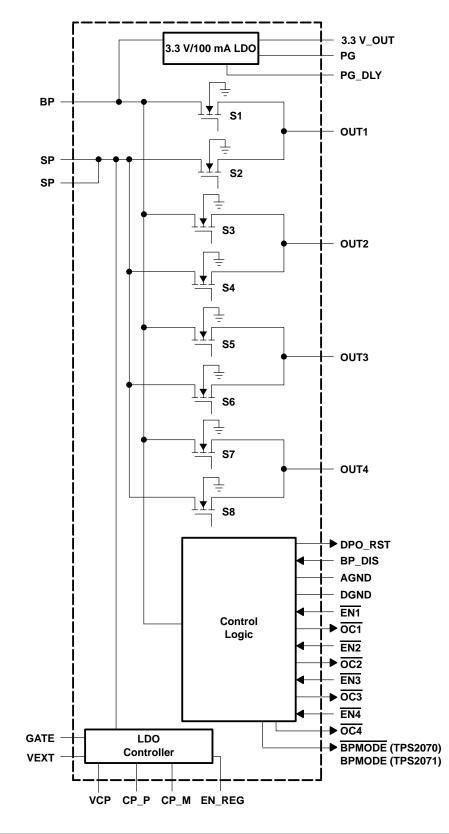

The TPS2070 and TPS2071 provide a complete USB hub power solution by incorporating four major functions: current-limited power switches for four ports, a 3.3-V 100-mA regulator, a 5-V regulator controller for self power, and a DP0 line control to signal attach/detach of the hub.

These devices are designed to meet bus-powered and self-powered hub requirements. These devices are also designed for hybrid hub implementations and allow for automatic switching from self-powered mode to bus-powered mode if loss of self-power is experienced (can be disabled by applying a logic high to BP\_DIS).

Each port has a current-limited  $107 \text{-m}\Omega$  Nchannel MOSFET high-side power switch for 500 mA self-powered operation. Each port also has a current-limited 560-m $\Omega$  N-channel MOS-FET high-side power switch for 100-mA bus-powered operation. All the N-channel MOSFETs are designed without parasitic diodes, preventing current backflow into the inputs.

For applications not requiring a 5-V regulator controller, use the TPS2074 or TPS2075 device.

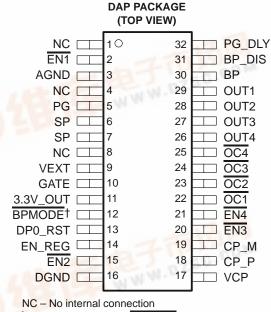

<sup>†</sup> Pin 12 is active low (BPMODE) for TPS2070 and active high (BPMODE) for TPS2071.

#### simplified hybrid-hub diagram<sup>‡</sup>

|               | GEELOIN                                   | SH GOIDE         |             |                           |           |  |  |  |  |

|---------------|-------------------------------------------|------------------|-------------|---------------------------|-----------|--|--|--|--|

| т.            | USB HUB POWER CONTROLLERS                 | PACKAGED DEVICES |             |                           |           |  |  |  |  |

| A'            | USB HUB POWER CONTROLLERS                 | PIN COUNT        | BPMODE      | HTSSOP (DAP) <sup>†</sup> | SSOP (DB) |  |  |  |  |

|               | Four port with internal I DO controller   | 22               | Active low  | TPS2070DAP                | —         |  |  |  |  |

| 40°C to 95°C  | C to 85°C                                 | Active high      | TPS2071DAP  | —                         |           |  |  |  |  |

| -40 C 10 85 C | Four-port without internal LDO controller | 24               | Active low  | —                         | TPS2074DB |  |  |  |  |

|               | Four-port without internal LDO controller | ∠4               | Active high | _                         | TPS2075DB |  |  |  |  |

SELECTION GUIDE

The DAP package is available taped and reeled. Add an R suffix to the device type (e.g., TPS2070DAPR).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SLVS287A – SEPTEMBER 2000 – REVISED FEBRUARY 2001

## functional block diagram

TEXAS

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

| TERM                | INAL |       |                                                                                                                                                             |  |  |  |  |

|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                | NO.  | - 1/0 | DESCRIPTION                                                                                                                                                 |  |  |  |  |

| NC                  | 1    |       | No internal connection                                                                                                                                      |  |  |  |  |

| EN1                 | 2    | 1     | Active-low enable for OUT1                                                                                                                                  |  |  |  |  |

| AGND                | 3    |       | Analog ground                                                                                                                                               |  |  |  |  |

| NC                  | 4    |       | No internal connection                                                                                                                                      |  |  |  |  |

| PG                  | 5    | 0     | Logic output, power good                                                                                                                                    |  |  |  |  |

| SP                  | 6    | 1     | Self-power voltage input, connects to local power supply                                                                                                    |  |  |  |  |

| SP                  | 7    | 1     | Self-power voltage input, connects to local power supply                                                                                                    |  |  |  |  |

| NC                  | 8    |       | No internal connection                                                                                                                                      |  |  |  |  |

| VEXT                | 9    | 1     | Input voltage for the external voltage regulator                                                                                                            |  |  |  |  |

| GATE                | 10   | 0     | Output gate drive for an external N-channel MOSFET                                                                                                          |  |  |  |  |

| 3.3V_OUT            | 11   | 0     | 3.3-V internal voltage regulator output                                                                                                                     |  |  |  |  |

| BPMODE <sup>†</sup> | 12   | 0     | A logic signal that indicates if the outputs source from the bus-powered supply. BPMODE (TPS2070) or BPMODE (TPS2071) can be used to signal hub controller. |  |  |  |  |

| DP0_RST             | 13   | 0     | Connects to DP signal from upstream hub/host through an external 1.5-k $\Omega$ resistor                                                                    |  |  |  |  |

| EN_REG              | 14   | 1     | Active-high enable, enables external voltage regulator. Connect to BP or GND                                                                                |  |  |  |  |

| EN2                 | 15   | 1     | Active-low enable for OUT2                                                                                                                                  |  |  |  |  |

| DGND                | 16   |       | Digital ground                                                                                                                                              |  |  |  |  |

| VCP                 | 17   |       | Charge-pump output, source for an external voltage-regulator driver. Recommend $0.1-\mu F$ capacitor to DGND.                                               |  |  |  |  |

| CP_P                | 18   |       | Charge-pump-capacitor connection from CP_M. Recommend 0.01-µF between CP_P and CP_M.                                                                        |  |  |  |  |

| CP_M                | 19   |       | Charge-pump-capacitor connection from CP_P. Recommend 0.01-µ between CP_P and CP_M.                                                                         |  |  |  |  |

| EN3                 | 20   | 1     | Active-low enable for OUT3                                                                                                                                  |  |  |  |  |

| EN4                 | 21   | 1     | Active-low enable for OUT4                                                                                                                                  |  |  |  |  |

| OC1                 | 22   | 0     | Logic output, overcurrent response for OUT1                                                                                                                 |  |  |  |  |

| OC2                 | 23   | 0     | Logic output, overcurrent response for OUT2                                                                                                                 |  |  |  |  |

| OC3                 | 24   | 0     | Logic output, overcurrent response for OUT3                                                                                                                 |  |  |  |  |

| OC4                 | 25   | 0     | Logic output, overcurrent response for OUT4                                                                                                                 |  |  |  |  |

| OUT4                | 26   | 0     | Power switch output for downstream ports                                                                                                                    |  |  |  |  |

| OUT3                | 27   | 0     | Power switch output for downstream ports                                                                                                                    |  |  |  |  |

| OUT2                | 28   | 0     | Power switch output for downstream ports                                                                                                                    |  |  |  |  |

| OUT1                | 29   | 0     | Power switch output for downstream ports                                                                                                                    |  |  |  |  |

| BP                  | 30   | 1     | Bus power voltage input, connect to VBUS                                                                                                                    |  |  |  |  |

| BP_DIS              | 31   | I     | Active-high logic input, disables autoswitch to bus power when self power is disconnected. Connect to BP or GND                                             |  |  |  |  |

| PG_DLY <sup>‡</sup> | 32   | 1     | Adjusts the PG time delay with a capacitor to ground. Adjust the pulsewidth to fit the application.                                                         |  |  |  |  |

<sup>†</sup> Pin 12 is active low for TPS2070 and active high for TPS2071. <sup>‡</sup> Use the following formula to calculate the capacitance needed;  $C = (desired pulsewidth \times 3 \times 10^{-6})/1.22$

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## detailed description

#### BP

The bus-powered supply input (BP) serves as the source for the internal 3.3-V LDO and for all logic functions in the device. In bus-powered mode, BP also serves as the source for all the outputs (OUTx). If BP is below the undervoltage threshold, all power switches will turn off and the LDO will be disabled. BP must be connected to a voltage source in order for the device to operate.

#### SP

The self-powered supply input (SP) serves as the source for all the outputs (OUTx) in self-powered mode. The enable logic for the SP switches requires that BP be connected to a voltage source.

## OUT1, OUT2, OUT2, OUT4

OUTx are the outputs of the integrated power switches.

## 3.3V\_OUT

The internal 3.3-V LDO output can be used to supply up to 100 mA current to low-power functions, such as hub controllers.

## VEXT

VEXT is used to generate a 5-V source for the SP input by using the internal LDO controller and an external N-channel MOSFET. This pin connects to a 6-V to 9-V power supply and to the drain of the MOSFET if the external LDO is needed.

#### GATE

GATE is the output of the 5-V LDO controller and connects to the gate of the external MOSFET.

## EN\_REG

The active-high input, EN\_REG, is used to enable the 5-V regulator controller. EN\_REG is compatible with TTL and CMOS logic levels.

## DP0\_RST

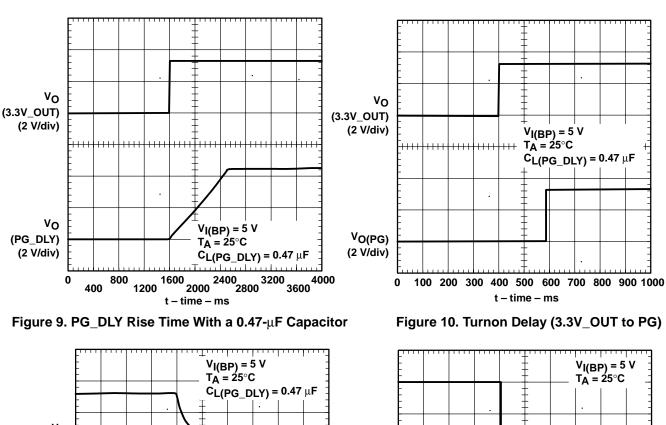

DP0\_RST functions as a hub reset when a 1.5-k $\Omega$  resistor is connected between DP0\_RST and the upstream DP0 data line in a hub system. To provide a clean attach signal on DP0 data line, the DP0\_RST output goes low momentarily (because of the upstream pulldown resistor) to discharge any parasitic charge on the cable, then goes to 3-state and finally outputs a high signal. The low and Hi-Z pulse widths are adjustable using a capacitor between PG\_DLY and ground, and are approximately 50% of the power-good time delay. Detachment is signaled by a Hi-Z on DP0\_RST. Both DP0\_RST and PG will transition high at the same time.

## Power Good (PG)

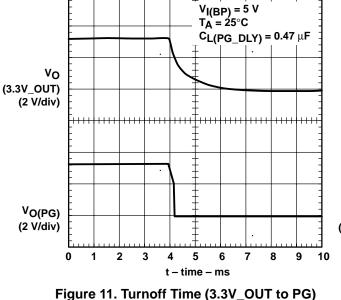

The power good (PG) function serves as a reset for a USB hub controller. PG is asserted low when the output voltage on the internal voltage regulator is below a fixed threshold. A time delay to ensure a stable output voltage before PG goes high is adjustable using a small-value ceramic capacitor from PG\_DLY to ground.

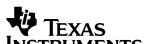

## PG\_DLY

$PG_DLY$  connects to an external capacitor to adjust the time delay for PG and DP0\_RST. For USB applications, a 0.1- $\mu$ F capacitor is recommended, however, reference the USB Hub Controller data sheet to determine the needed pulsewidth criteria.

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## detailed description (continued)

#### **BP\_DIS**

BP\_DIS is used to enable or disable the autoswitching function between bus-powered mode and self-powered mode. When BP\_DIS is connected low and the voltage on SP is greater than the undervoltage-lockout (UVLO) threshold, the device will switch to self-powered operation automatically; if the SP voltage falls lower than the UVLO threshold, the device will switch to bus-powered operation. When BP\_DIS is connected high, the autoswitching function is disabled and the device will not autoswitch to bus-powered operation if the SP voltage is below the UVLO threshold.

#### **BPMODE** or **BPMODE**

BPMODE (TPS2070) or BPMODE (TPS2071) is an output that signals when the device is in bus-powered mode. The logic state is set according to the voltages on BP, SP, and BP\_DIS. For the TPS2070, BPMODE outputs a low signal to indicate bus-powered mode or a high signal to indicate self-powered mode. For the TPS2071, BPMODE outputs a high signal to indicate bus-powered mode or a low signal to indicate self-powered mode. This output can be used to inform a USB hub controller to configure for bus-powered mode or self-powered mode.

## $\overline{\text{OC1}}, \overline{\text{OC2}}, \overline{\text{OC3}}, \overline{\text{OC4}}$

OCx is an output signal that is asserted (active low) when an overcurrent or overtemperature condition is encountered for the corresponding channel. OCx will remain asserted until the overcurrent or overtemperature condition is removed.

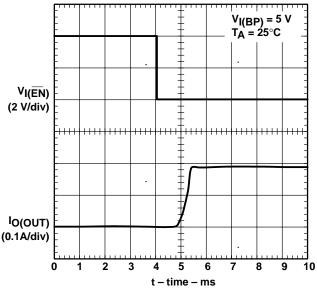

#### <u>EN1</u>, <u>EN2</u>, <u>EN3</u>, <u>EN4</u>,

The active-low logic input ENx enables or disables the power switches in the device. The enable input is compatible with both TTL and CMOS logic levels. The switches will not turn on until 3.3V\_OUT is above the PG threshold.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Input voltage range: VI(BP)    | , $V_{I(SP)}$ , $V_{I(\overline{ENx})}$ , $V_{I(EN\_REG)}$ , $V_{I(BP\_DIS)}$ | $\ldots$ –0.3 V to 6 V                    |

|--------------------------------|-------------------------------------------------------------------------------|-------------------------------------------|

| VI(VE)                         | (T) · · · · · · · · · · · · · · · · · · ·                                     | $\ldots$ –0.3 V to 10 V                   |

| Output voltage range: VO(C     | DUTx) ·····                                                                   | $\ldots$ –0.3 V to 6 V                    |

| V <sub>O(3</sub>               | .3V_OUT), VO(PG_DLY), VO(OCx), VO(BPMODE),                                    |                                           |

| VOC                            | PO_RST), VO(PG) · · · · · · · · · · · · · · · · · · ·                         | –0.3 V to V <sub>O (3.3V_OUT)</sub> 0.3 V |

| Void                           | GATE), VO(CP_M), VO(CP_P), VO(VCP) ·····                                      | –0.3 V to 15 V                            |

| Continuous output current:     | I <sub>O(OUTx)</sub>                                                          | internally limited                        |

|                                | I <sub>O(3.3V_OUT)</sub>                                                      | internally limited                        |

| Maximum output current:        |                                                                               | ±30 mA                                    |

|                                | IO(BPMODE) or IO(BPMODE), IO(DP0_RST), IO(PO                                  | G), I <sub>O(OCx)</sub> ±10 mA            |

|                                | I <sub>O(GATE)</sub> , sourcing                                               | 700 μΑ                                    |

|                                | I <sub>O(GATE)</sub> , sinking                                                | –2.2 mA                                   |

| Continuous total power diss    | ipation                                                                       |                                           |

| Operating virtual junction ter | mperature range, T <sub>J</sub>                                               | –40°C to 125°C                            |

| Storage temperature range,     | T <sub>stg</sub>                                                              | –65°C to 150°C                            |

| Lead temperature soldering     | 1,6 mm (1/16 inch) from case for 10 seconds                                   | 260°C                                     |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup> All voltages are with respect to GND.

SLVS287A – SEPTEMBER 2000 – REVISED FEBRUARY 2001

| DISSIPATION RATING TABLE |                                    |                                                |                                       |                                       |  |  |  |  |  |  |

|--------------------------|------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|--|--|--|--|--|--|

| PACKAGE                  | $T_A \le 25^{\circ}C$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |  |  |  |  |  |  |

| 32-DAP                   | 1162.8 mW                          | 11.6 mW/°C                                     | 639.5 mW                              | 465.1 mW                              |  |  |  |  |  |  |

| 32-DAP <sup>†</sup>      | 4255.3 mW                          | 42.5 mW/°C                                     | 2340.4 mW                             | 1702.1 mW                             |  |  |  |  |  |  |

<sup>†</sup> Using PowerPAD as heatsink.

#### recommended operating conditions

|                                 |                                           | MIN | MAX | UNIT |

|---------------------------------|-------------------------------------------|-----|-----|------|

|                                 | V <sub>I(BP)</sub>                        | 4.5 | 5.5 |      |

|                                 | VI(SP)                                    | 0   | 5.5 |      |

| Input voltage                   | VI(VEXT)                                  | 0   | 9   | v    |

| input voltage                   | VI(BP_DIS)                                | 0   | 5.5 | v    |

|                                 | VI(ENx)                                   | 0   | 5.5 |      |

|                                 | VI(EN_REG)                                | 0   | 5.5 |      |

|                                 | BP to OUTx (per switch)                   |     | 100 |      |

| Continuous output current, IO   | SP to OUTx (per switch)                   |     | 500 | mA   |

|                                 | BP to 3.3V_OUT                            |     | 100 |      |

| Operating virtual junction temp | perating virtual junction temperature, TJ |     |     |      |

# electrical characteristics over recommended operating junction temperature range, 4.5 V $\leq$ V<sub>I(BP)</sub> $\leq$ 5.5 V, 4.85 V $\leq$ V<sub>I(SP)</sub> $\leq$ 5.5 V, 6 V $\leq$ V<sub>I(VEXT)</sub> $\leq$ 9 V, ENx = 0 V, EN\_REG = 0 V, BP\_DIS = 0 V (unless otherwise noted)

#### input current

|                    | PARAMETER                                      | TEST CONDITIONS                                             | it .                      | MIN | TYP | MAX | UNIT |

|--------------------|------------------------------------------------|-------------------------------------------------------------|---------------------------|-----|-----|-----|------|

|                    |                                                |                                                             | V <sub>I(SP)</sub> = Hi-Z |     | 185 | 240 |      |

|                    | Input current at BP, switches<br>disabled      | No load on OUTx and $3.3V_OUT$ ,<br>ENx = $V_{I(BP)}$       | $V_{I(SP)} = 0 V$         |     | 185 | 240 | μΑ   |

| lupp)              |                                                |                                                             | $V_{I(SP)} = 5 V$         |     | 175 | 210 |      |

| li(BP)             |                                                |                                                             | V <sub>I(SP)</sub> = Hi-Z |     | 185 | 240 |      |

|                    | Input current at BP, switches<br>enabled       | No load on OUTx and $3.3V_OUT$ ,<br>ENx = 0 V               | $V_{I(SP)} = 0 V$         |     | 185 | 240 | μA   |

|                    |                                                |                                                             | $V_{I(SP)} = 5 V$         |     | 175 | 210 |      |

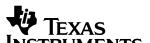

|                    | Input current at SP, switches disabled         | $\frac{No}{ENx} = V_{I}(SP)$                                | V <sub>I(BP)</sub> = Hi-Z |     | 90  | 115 | -    |

|                    |                                                |                                                             | $V_{I(BP)} = 0 V$         |     | 90  | 115 |      |

|                    |                                                |                                                             | $V_{I(BP)} = 5 V$         |     | 115 | 140 |      |

| <sup>I</sup> I(SP) |                                                |                                                             | V <sub>I(BP)</sub> = Hi-Z |     | 90  | 115 |      |

|                    | Input current at SP, switches<br>enabled       | No load on OUTx and $3.3V_OUT$ ,<br>ENx = 0V                | $V_{I(BP)} = 0 V$         |     | 90  | 115 | μA   |

|                    |                                                |                                                             | $V_{I(BP)} = 5 V$         |     | 115 | 140 |      |

|                    | Input current at VEXT, LDO controller disabled |                                                             |                           |     | 200 | 360 | μΑ   |

| l(VEXT)            | Input current, at VEXT, LDO controller enabled | $V_{I(EN\_REG)} = 5 V,$<br>$VI(BP) = 5 V, V_{I(SP)} = Hi-Z$ |                           |     |     | 10  | mA   |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## electrical characteristics over recommended operating junction temperature range, 4.5 V $\leq$ V<sub>I(BP)</sub> $\leq$ 5.5 V, 4.85 V $\leq$ V<sub>I(SP)</sub> $\leq$ 5.5 V, 6 V $\leq$ V<sub>I(VEXT)</sub> $\leq$ 9 V, ENx = 0 V, EN\_REG = 0 V, BP\_DIS = 0 V (unless otherwise noted) (continued)

#### power switches

| P.                      | ARAMETER                                               |        | TEST CONDITIONS                                                                                                                                                                |                       | MIN TYP |     |     | UNIT  |

|-------------------------|--------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------|-----|-----|-------|

|                         | Static                                                 | SP to  | V <sub>I(SP)</sub> = V <sub>I(BP)</sub> = 5 V, I <sub>Ox</sub> = 0.5 A                                                                                                         | T <sub>A</sub> = 25°C |         | 107 |     |       |

| (DC(an)                 | drain-source                                           | OUTx   |                                                                                                                                                                                | T <sub>A</sub> = 70°C |         | 125 | 160 | mΩ    |

| <sup>r</sup> DS(on)     | on-state                                               | BP to  | V <sub>I(BP)</sub> = 4.5 V, V <sub>I(SP)</sub> = Open, I <sub>OX</sub> = 0.1 A                                                                                                 | T <sub>A</sub> = 25°C |         | 560 |     | 11122 |

|                         | resistance                                             | OUTx   | $v_{1(BP)} = 4.0 v_{1}^{2}$ $v_{1(SP)} = 00000000000000000000000000000000000$                                                                                                  | T <sub>A</sub> = 70°C |         | 630 | 900 |       |

|                         |                                                        |        | $\overline{\text{ENx}} = \text{V}_{I(\text{BP})} = 5.5 \text{ V},  \text{V}_{I(\text{SP})} = \text{Hi-Z},$ OUTx connected to ground, $ \text{V}_{I(\text{VIN})} = \text{Hi-Z}$ | TJ = 25°C             |         | 0.5 | 10  |       |

|                         | Leakage current at<br>x) OUTx (no load on<br>3.3V_OUT) |        | $\overline{ENx} = V_{I(BP)} = V_{I(SP)} = 5.5 V,$<br>OUTx connected to ground, $V_{I(EXT)} = Hi-Z$                                                                             | TJ = 25°C             |         | 0.5 | 10  |       |

| l <sub>lkg</sub> (OUTx) |                                                        |        | $\overline{ENx} = V_{I(BP)} = Hi-Z \text{ or } 0 \text{ V},$<br>$V_{I(VEXT)} = V_{I(SP)} = V_{I(OUTx)} = 5.5 \text{ V}$                                                        | T <sub>J</sub> = 25°C |         | 0.5 | 10  | μA    |

|                         |                                                        |        | $\overline{ENx} = V_{I(BP)} = V_{I(SP)} = Hi-Z \text{ or } 0 \text{ V},$<br>$V_{I(VEXT)} = V_{I(OUTx)} = 5.5 \text{ V}$                                                        | T <sub>J</sub> = 25°C |         | 0.5 | 10  |       |

|                         |                                                        |        | $\overline{ENx} = V_{I(BP)} = V_{I(SP)} = V_{I(VEXT)} = Hi-Z \text{ or } 0 \text{ V},$<br>$V_{I(OUTx)} = 5.5 \text{ V}$                                                        | T <sub>J</sub> = 25°C |         | 0.5 | 10  |       |

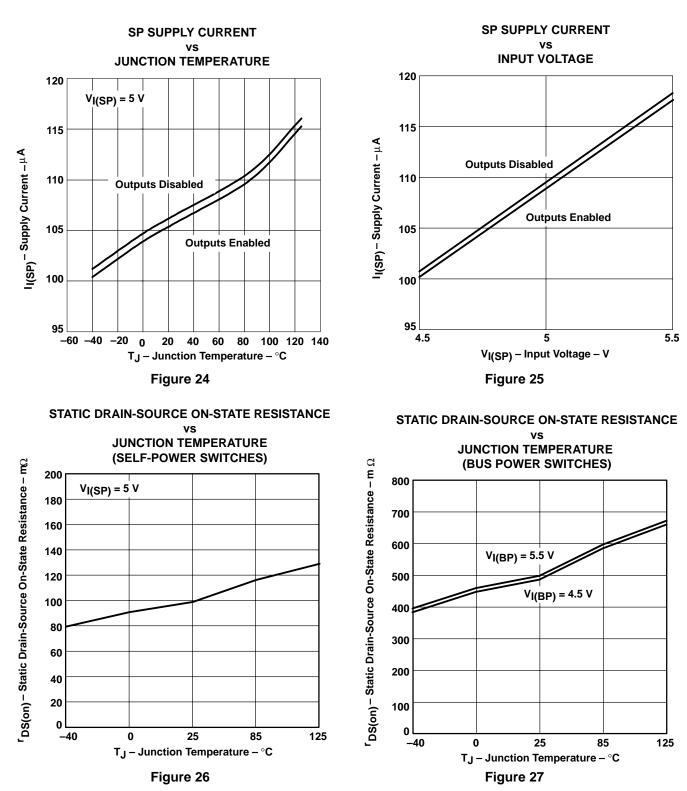

|                         |                                                        | urront | $V_{I}(BP) = V_{I}(SP) = 5 V$ , OUTx connected to GND,<br>Device enabled into short circuit                                                                                    |                       | 0.6     | 0.9 | 1.2 |       |

|                         | Short-circuit current<br>(per output)†                 |        | $V_{I(BP)} = 5 V, V_{I(SP)} = open,$<br>OUTx connected to GND, device enabled into short circuit                                                                               |                       | 0.12    | 0.2 | 0.3 | A     |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

## input signals (ENx, EN\_REG, BP\_DIS)

|      | PARAM                    | TEST CONDITIONS | MIN                  | TYP                | MAX | UNIT |     |    |

|------|--------------------------|-----------------|----------------------|--------------------|-----|------|-----|----|

| VIH  | High-level input voltage |                 |                      |                    | 2   |      |     | V  |

| VIL  | Low-level input voltage  |                 |                      |                    |     |      | 0.8 | v  |

|      |                          | Pullup          | ENx (active low)     | $V_{I(ENx)} = 0 V$ |     |      | 5   |    |

| li I | Input current            | Pulldown        | EN_REG (active high) | VI(EN_REG) = 5 V   |     |      | 5   | μA |

|      |                          | FulldOWN        | BP_DIS (active high) | VI(BP_DIS) = 5 V   |     |      | 5   |    |

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## electrical characteristics over recommended operating junction temperature range, 4.5 V $\leq$ V<sub>I(BP)</sub> $\leq$ 5.5 V, 4.85 V $\leq$ V<sub>I(SP)</sub> $\leq$ 5.5 V, 6 V $\leq$ V<sub>I(VEXT)</sub> $\leq$ 9 V, ENx = 0 V, EN\_REG = 0 V, BP\_DIS = 0 V (unless otherwise noted) (continued)

## output signals (BPMODE or BPMODE, OCx, DPO\_RST)

|                    | PARAMETER                                        |                                                                                                                                                   | TEST CON                                                                                                                                          | IDITIONS                                   | MIN | TYP   | MAX | UNIT |

|--------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----|-------|-----|------|

|                    |                                                  | BPMODE                                                                                                                                            | $\begin{array}{l} 4.25 \; V \leq V_{I(BP)} \leq 5.5 \; V, \\ 4.5 \; V \leq V_{I(SP)} \leq 5.5 \; V \end{array}$                                   |                                            | 2.4 |       |     | v    |

| ∨он                | High-level output                                | BPMODE                                                                                                                                            | $4.25 V \le V_{I(BP)} \le 5.5 V$ ,<br>$V_{I(SP)} < 4 V$                                                                                           |                                            | 2.4 |       |     |      |

|                    | voltage                                          | OCx                                                                                                                                               | $4.25 \text{ V} \le \text{V}_{I(BP)} \le 5.5 \text{ V},$<br>$\text{V}_{I(ENx)} = 3.3 \text{ V or Hi-Z}$                                           | I <sub>O</sub> = 2 mA                      | 2.4 |       |     |      |

|                    |                                                  |                                                                                                                                                   | 2.4                                                                                                                                               |                                            |     |       |     |      |

|                    | Low-level output voltage                         | BPMODE                                                                                                                                            | $\begin{array}{l} 4.25 \ \mbox{V} \leq \mbox{V}_{I(BP)} \leq 5.5 \ \mbox{V}, \\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                             | I <sub>O</sub> = 3.2 mA                    |     |       | 0.4 |      |

| V <sub>OL</sub>    |                                                  | BPMODE                                                                                                                                            | $\begin{array}{l} 4.25 \text{ V} \leq \text{V}_{I(BP)} \leq 5.5 \text{ V}, \\ 4.5 \text{ V} \leq \text{V}_{I(SP)} \leq 5.5 \text{ V} \end{array}$ | 10 = 3.2 IIIA                              |     |       | 0.4 | V    |

|                    |                                                  | OCx                                                                                                                                               | 4.25 V $\leq$ V <sub>I(BP)</sub> $\leq$ 5.5 V, OUTx = 0 V                                                                                         | $I_{O(\overline{OC})} = 3.2 \text{ mA}$    |     |       | 0.4 |      |

|                    | Minimum input voltago at                         | BB for low lovel                                                                                                                                  | I <sub>O</sub> = 300 μA,                                                                                                                          | V <sub>O(</sub> BPMODE) <sup>≤</sup> 0.4 V |     |       | 1.5 |      |

| V <sub>I(BP)</sub> | Minimum input voltage at BP for low-level output | I <sub>O</sub> = 300 μA,<br>V <sub>I(SP)</sub> = 5 V                                                                                              | VO(BPMODE) <sup>≤</sup> 0.4 V,                                                                                                                    |                                            |     | 1.5 V | V   |      |

| l <sub>lkg</sub>   | Hi-Z leakage current at D                        | $ \begin{array}{l} 0 \ V \leq V_{I}(DPO\_RST) \leq 3.3 \ V, \ V_{I}(SP) = 0 \ V, \\ V_{I}(BP) = 5.5 \ V, \ V_{I}(PG\_DLY) = 0.9 \ V \end{array} $ |                                                                                                                                                   | V, $V_{I}(SP) = 0 V$ ,<br>Y) = 0.9 V       | -5  |       | 5   | μA   |

| <sup>t</sup> d     | Overcurrent response del<br>(see Note 1)         | ay time                                                                                                                                           |                                                                                                                                                   |                                            | 1   |       | 10  | ms   |

NOTE 1: Specified by design, not tested in production.

#### undervoltage lockout (SP, BP, VEXT)

|                  | PARAMETER                       | TEST CONDITIONS | MIN                       | TYP  | MAX | UNIT |    |  |

|------------------|---------------------------------|-----------------|---------------------------|------|-----|------|----|--|

|                  |                                 | SP              |                           |      |     | 4.5  |    |  |

|                  | Start threshold                 | BP              | V <sub>I(SP)</sub> = Hi-Z |      |     | 4.25 | V  |  |

|                  |                                 | VEXT            |                           |      |     | 3    |    |  |

|                  |                                 | SP              |                           | 4    |     |      |    |  |

|                  | Stop threshold                  | BP              |                           | 3.75 |     |      | V  |  |

|                  |                                 | VEXT            |                           | 2.50 |     |      |    |  |

|                  |                                 | SP              |                           | 300  |     |      | mV |  |

| V <sub>hys</sub> | Hysteresis voltage (see Note 1) | BP              |                           | 300  |     |      |    |  |

|                  |                                 | VEXT            |                           | 150  |     |      |    |  |

NOTE 1: Specified by design, not tested in production.

SLVS287A – SEPTEMBER 2000 – REVISED FEBRUARY 2001

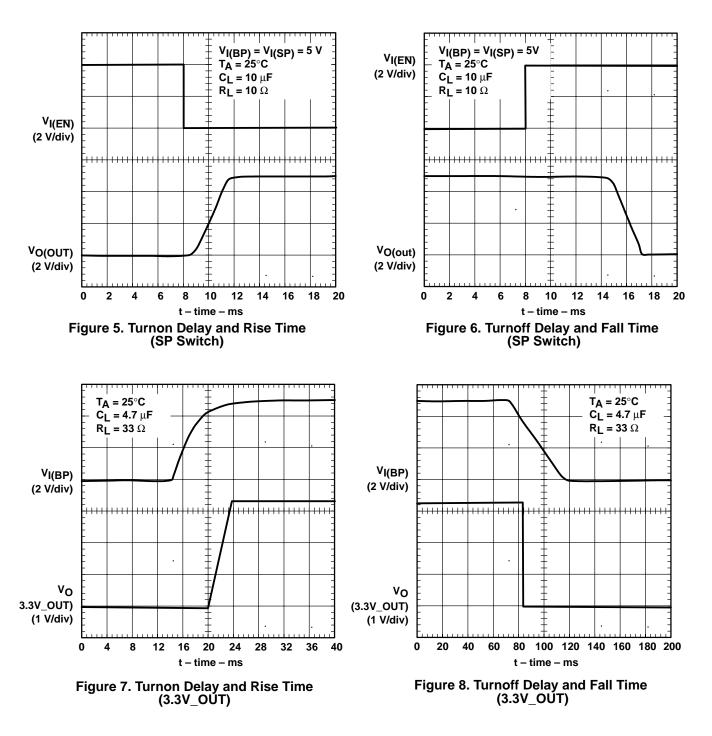

# electrical characteristics over recommended operating junction temperature range, 4.5 V $\leq$ V<sub>I(BP)</sub> $\leq$ 5.5 V, 4.85 V $\leq$ V<sub>I(SP)</sub> $\leq$ 5.5 V, 6 V $\leq$ V<sub>I(VEXT)</sub> $\leq$ 9 V, ENx = 0 V, EN\_REG = 0 V, BP\_DIS = 0 V, C<sub>L(3.3V\_OUT)</sub> = 10 $\mu$ F (unless otherwise noted)

#### internal voltage regulator

|                  | PARAMETER                                  | TEST CONDITIONS                                                                                                        | MIN  | TYP  | MAX  | UNIT |

|------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VO               | Output voltage, dc                         | $V_{I(BP)} = 4.25 V \text{ to } 5.5 V$ , $I_{O} = 5 \text{ mA to } 100 \text{ mA}$                                     | 3.2  | 3.3  | 3.4  | V    |

|                  | Dropout voltage                            | I <sub>O</sub> = 100 mA                                                                                                |      | 0.6  |      | V    |

|                  | Line regulation                            | $V_{I(BP)} = 4.25 V \text{ to } 5.25 V, I_O = 5 \text{ mA}$                                                            |      |      | 0.1  | %/v  |

|                  | Load regulation                            | $V_{I(BP)} = 4.25 \text{ V},$ $I_{O} = 5 \text{ mA to } 100 \text{ mA}$                                                |      |      | 0.6% |      |

| los              | Short-circuit current limit <sup>†</sup>   | VI(BP) = 4.25 V, 3.3V_OUT connected to GND                                                                             | 0.12 | 0.2  | 0.3  | А    |

|                  | Pulldown transistor at 3.3V_OUTPUT         | V <sub>I(3.3V_OUT)</sub> = 3.3 V                                                                                       |      |      |      | mA   |

|                  | (see Note 1)                               | V <sub>I(3.3V_OUT)</sub> = 1 V                                                                                         | 5    |      |      | IIIA |

| PSRR             | Power-supply ripple rejection (see Note 1) | F = 1 kHz, C <sub>L(3.3V_OUT)</sub> = 4.7 μF,<br>ESR = 0.25 Ω, I <sub>O</sub> = 5 mA,<br>V <sub>I(BP)PP</sub> = 100 mV | 40   |      |      | dB   |

|                  | Low-level trip threshold voltage at PG     |                                                                                                                        | 2.88 | 2.94 | 3    | V    |

| V <sub>hys</sub> | Hysteresis voltage at PG (see Note 1)      |                                                                                                                        | 50   |      | 100  | mV   |

| Vон              | High-level output voltage at PG            | $4.25 \text{ V} \le \text{V}_{I(BP)} \le 5.25 \text{ V},  I_{O} = 2 \text{ mA}$                                        | 2.4  |      |      | V    |

| Vol              | Low-level output voltage at PG             | $4.25 \text{ V} \le \text{V}_{I(BP)} \le 5.25 \text{ V}, \text{ I}_{O} = 3.2 \text{ mA}$                               |      |      | 0.4  | V    |

| V <sub>ref</sub> | Reference voltage at PG_DLY                |                                                                                                                        |      | 1.22 |      | V    |

|                  | Charge current at PG_DLY                   |                                                                                                                        |      | 3    |      | uA   |

| t <sub>d</sub>   | Delay time at PG (see Notes 1 and 2)       | C <sub>L(PG_DLY)</sub> = 0.47 μF                                                                                       |      | 190  |      | ms   |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately. NOTES: 1. Specified by design, not tested in production.

2. The PG delay time (t<sub>d</sub>) is calculated using the PG\_DLY reference voltage and charge current:

$t_{d} = \frac{C_{L(PG\_DLY)} \times V_{ref}}{Charge \ Current}$

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## electrical characteristics over recommended operating junction temperature range, 4.5 V $\leq$ V<sub>I(BP)</sub> $\leq$ 5.5 V, 4.85 V $\leq$ V<sub>I(SP)</sub> $\leq$ 5.5 V, 6 V $\leq$ V<sub>I(VEXT)</sub> $\leq$ 9 V, ENx = 0 V, EN\_REG = 3.3 V, BP\_DIS = 0 V, C<sub>L(SP)</sub> = 220 $\mu$ F (unless otherwise noted)

#### voltage regulator controller

|                                                                    | PARAMETER                         |            | TEST CONDITIONS                                                                  | MIN  | TYP | MAX  | UNIT |

|--------------------------------------------------------------------|-----------------------------------|------------|----------------------------------------------------------------------------------|------|-----|------|------|

| V <sub>O(CP)</sub>                                                 | CP) Output voltage, charge pump   |            | $V_{I}(VEXT) = 6 V$ , $I_{O}(VCP) = 5 mA$<br>$C(CP_P) = 10 nF$ , $C(VCP)=100 nF$ | 10   |     |      | V    |

| f <sub>osc</sub>                                                   | Oscillator frequency (see Note 1) |            | 6 V $\leq$ VI(VEXT) $\leq$ 9 V, IO(VCP) = 5 mA, VO(VCP)= 10 V                    |      | 850 |      | kHz  |

|                                                                    |                                   |            | VI(VCP) = 9 V, VO(GATE) = 7.5 V,<br>VI(SP) = 4.5 V                               | 500  |     |      | μΑ   |

|                                                                    | Gate drive current Sinking        | Sinking    | VI(VCP) = 9 V, VO(GATE) = 5.5 V,<br>VI(SP) = 5.5 V                               | 1.5  |     |      | mA   |

|                                                                    | Open-loop gain (see Note 1)       |            | $V_{I(VEXT)} = 6 V, 0.5 V \le V_{O(GATE)} \le 9 V$                               |      | 80  |      | dB   |

| Reference voltage at V <sub>I(SP)</sub> , using external regulator |                                   |            | VI(VEXT) = 6 V to 9 V, IRLZ24N FET                                               | 4.90 | 5.1 | 5.25 | V    |

|                                                                    | Gate clamp voltage                | Gate to SP |                                                                                  | 10   |     | V    |      |

NOTE 1: Specified by design, not tested in production.

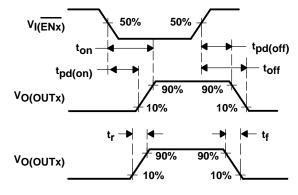

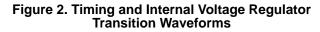

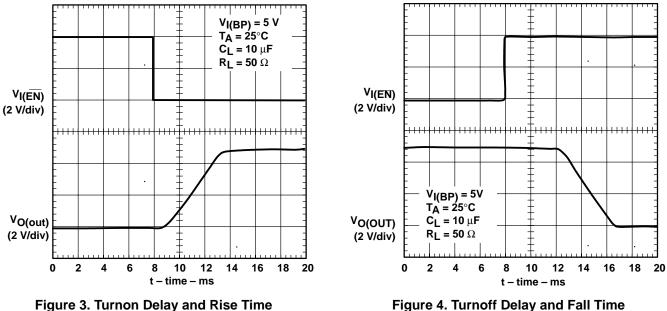

## power switch timing requirements

|                  | PARAMETER                      |                      | TEST CONDITIONS <sup>†</sup>                                                                                                                  | MIN TYP MAX | UNIT |  |

|------------------|--------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|--|

| t <sub>on</sub>  | Turnon time (see Note 1)       | BP to OUTx<br>switch | $ \begin{array}{l} V_{I(BP)} = 5 \; V, \; V_{I(SP)} = open,  T_{A} = 25^\circ C, \\ C_{L} = 100 \; \muF,  R_{L} = 50 \; \Omega \end{array} $  | 4.5         |      |  |

|                  |                                | SP to OUTx switch    | $ \begin{array}{l} V_{I}(SP) = V_{I}(BP) = 5 \ V,  T_{A} = 25^\circ C, \\ C_{L} = 100 \ \muF,  R_{L} = 10 \ \Omega \end{array} $              | 4.5         | ms   |  |

| <sup>t</sup> off | Turnoff time (see Note 1)      | BP to OUTx switch    | $ \begin{array}{l} V_{I(BP)} = 5 \; V, \; V_{I(SP)} = open,  T_{A} = 25^\circ C, \\ C_{L} = 100 \; \muF,  R_{L} = 50 \; \Omega \end{array} $  | 15          |      |  |

|                  |                                | SP to OUTx switch    | $ \begin{array}{l} V_{I}(SP) = V_{I}(BP) = 5 \; V,  T_{A} = 25^{\circ}C, \\ C_{L} = 100 \; \muF,  R_{L} = 10 \; \Omega \end{array} $          | 10          | ms   |  |

| tr               | Rise time, output (see Note 1) | BP to OUTx switch    | $ \begin{array}{l} V_{I(BP)} = 5 \; V, \; V_{I(SP)} = open,  T_{A} = 25^{\circ}C, \\ C_{L} = 100 \; \muF,  R_{L} = 50 \; \Omega \end{array} $ | 4           | ms   |  |

|                  |                                | SP to OUTx switch    | $ \begin{array}{l} V_{I}(SP) = V_{I}(BP) = 5 \; V,  T_{A} = 25^{\circ}C, \\ C_{L} = 100 \; \muF,  R_{L} = 10 \; \Omega \end{array} $          | 3           |      |  |

| t <sub>f</sub>   | Fall time, output (see Note 1) | BP to OUTx switch    | $ \begin{array}{l} V_{I(BP)} = 5 \; V, \; V_{I(SP)} = open,  T_{A} = 25^{\circ}C, \\ C_{L} = 100 \; \muF,  R_{L} = 50 \; \Omega \end{array} $ | 10          | ms   |  |

|                  |                                | SP to OUTx switch    |                                                                                                                                               | 3           |      |  |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately. NOTE 1. Specified by design, not tested in production.

## thermal shutdown

|    |                  | MIN    | TYP | MAX | UNIT |    |

|----|------------------|--------|-----|-----|------|----|

| ТJ | Thermal shutdown | First  | 140 |     |      | °C |

|    |                  | Second |     | 150 |      | C  |

|    | Hysteresis       | First  |     | 15  |      | °C |

|    |                  | Second |     | 25  |      | U  |

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

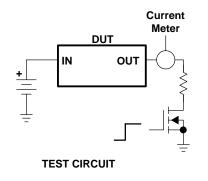

## PARAMETER MEASUREMENT INFORMATION

(BP Switch)

TIMING

(BP Switch)

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

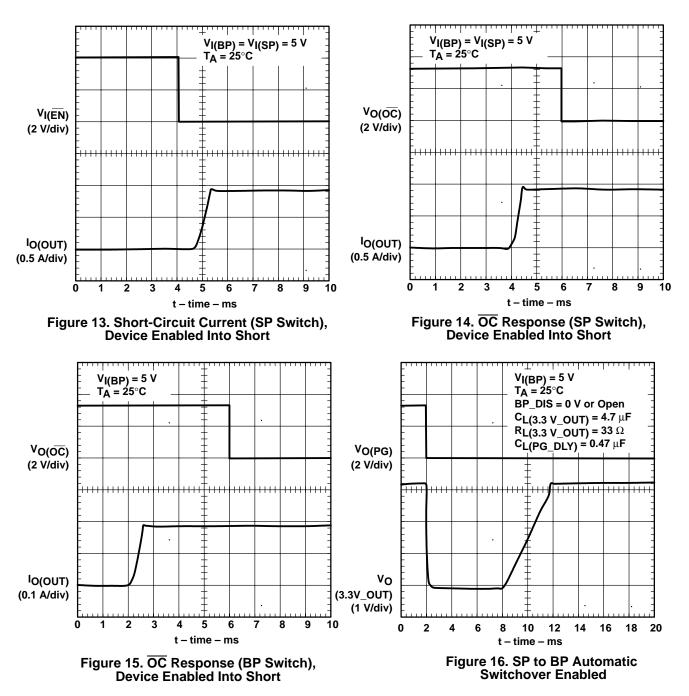

Figure 12. Short-Circuit Current (BP Switch), Device Enabled Into Short

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## PARAMETER MEASUREMENT INFORMATION

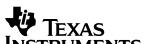

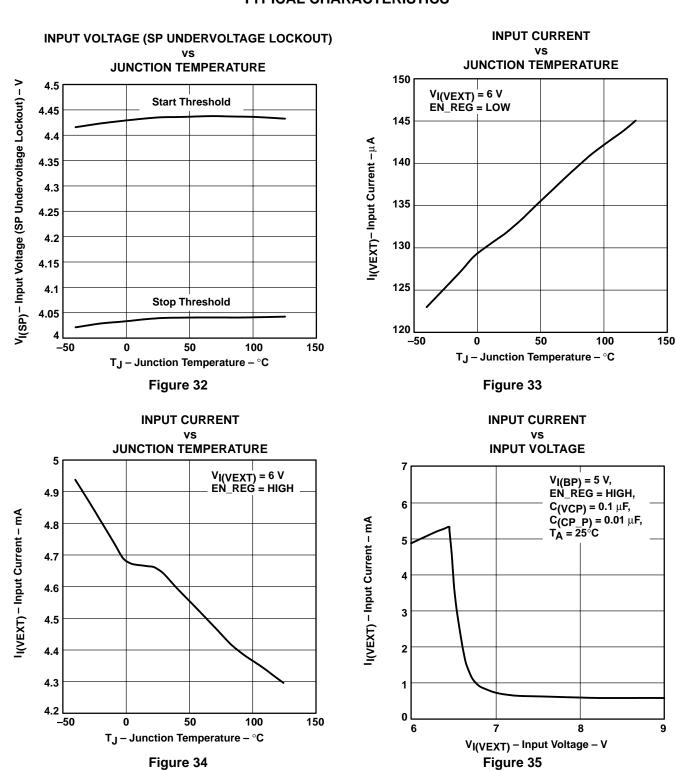

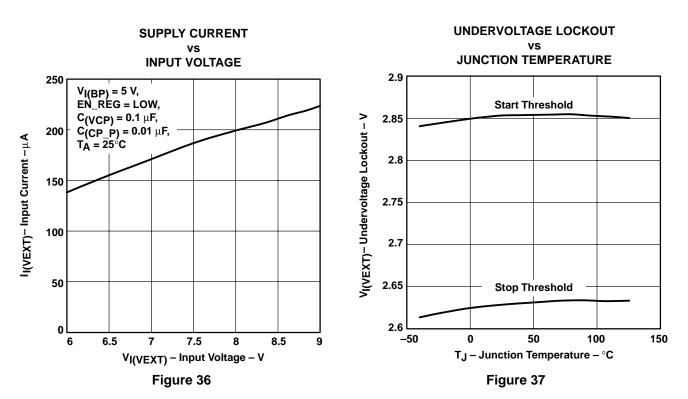

**TYPICAL CHARACTERISTICS**

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

**TYPICAL CHARACTERISTICS**

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

**TYPICAL CHARACTERISTICS**

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

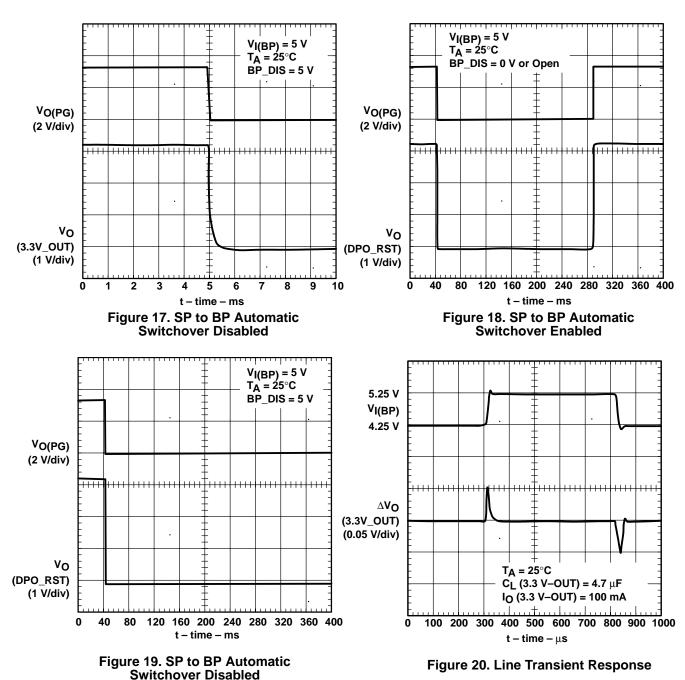

## TYPICAL CHARACTERISTICS

## **APPLICATION INFORMATION**

## external capacitor requirements

A 0.1- $\mu$ F ceramic bypass capacitor and a 10- $\mu$ F bulk capacitor between BP and AGND, close to the device, are recommended. Similarly, a 0.1- $\mu$ F ceramic and a 68- $\mu$ F bulk capacitor, from SP to AGND, and from VEXT to AGND if an external 5-V LDO is required, are recommended because of much higher current in the self-powered mode.

From each of the outputs (OUTx) to ground, a 33- $\mu$ F or higher valued bulk capacitor is recommended when the output load is heavy. This precaution reduces power-supply transients. Additionally, bypassing the outputs with a 0.1- $\mu$ F ceramic capacitor improves the immunity of the device to short-circuit transients.

An output capacitor connected between 3.3V\_OUT and GND is required to stabilize the internal control loop. The internal LDO is designed for a capacitor range of 4.7  $\mu$ F to 33  $\mu$ F with an ESR of 0.2  $\Omega$  to 10  $\Omega$ . Solid tantalum-electrolytic, aluminum-electrolytic and multilayer ceramic capacitors are all suitable.

Ceramic capacitors have different types of dielectric material, each exhibiting different temperature and voltage variations. The most common types are X5R, X7R, Y5U, Z5U, and NPO. The NPO type ceramic capacitors are generally the most stable over temperature. However, the X5R and X7R are also relatively stable over temperature (with the X7R being the more stable of the two) and are therefore acceptable for use. The Y5U and Z5U types provide high capacitance in a small geometry, but exhibit large variations over temperature. For this reason, the Y5U and Z5U are not generally recommended.

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## **APPLICATION INFORMATION**

#### external capacitor requirements (continued)

A transient condition occurs because of a sudden increase in output current. The output capacitor reduces the transient effect by providing the additional current needed by the load. Depending on the current demand at the output, a voltage drop will occur across the internal resistance, ESR, of the capacitor. Using a low ESR capacitor will help minimize this voltage drop. A larger capacitor will also reduce the voltage drop by supplying the current demand for a longer time, versus that provided by a smaller capacitor.

#### overcurrent

An internal sense FET checks for overcurrent conditions. Unlike current-sense resistors, sense FETs do not increase the series resistance of the current path. When an overcurrent condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Complete shutdown occurs only if the fault is present long enough to activate thermal limiting.

Three possible overload conditions can occur. In the first condition, the output has been shorted before the device is enabled or before BP and SP have been applied. The TPS2070 and TPS2071 sense the short and immediately switch into a constant-current output.

In the second condition, the short occurs while the device is enabled. At the instant the short occurs, very high currents may flow for a very short time before the current-limit circuit can react. After the current-limit circuit has tripped (reached the overcurrent trip threshold), the device switches into constant-current mode.

In the third condition, the load has been gradually increased beyond the recommended operating current. The current is permitted to rise until the current-limit threshold is reached or until the thermal limit of the device is exceeded. The TPS2070 and TPS2071 are capable of delivering current up to the current-limit threshold without damaging the device. Once the threshold has been reached, the device switches into its constant-current mode.

## **OC** response

The OCx output is asserted (active low) when an overcurrent or overtemperature condition is encountered and will remain asserted until the overcurrent or overtemperature condition is removed. Connecting a heavy capacitive load to an enabled device can cause momentary false overcurrent reporting from the inrush current flowing through the device and charging the downstream capacitor. The TPS2070 and TPS2071 are designed to reduce false overcurrent reporting by implementing an internal deglitch circuit. This circuit eliminates the need for an external filter, which requires extra components. Also, using low-ESR electrolytic capacitors on the outputs can reduce erroneous overcurrent reporting by providing a low-impedance energy source to lower the inrush current flow through the device during hot-plug events. The OCx outputs are logic outputs thereby requiring no pullup or pulldown resistors.

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## **APPLICATION INFORMATION**

## power dissipation and junction temperature

The major source of power dissipation for the TPS2070 and TPS2071 comes from the internal voltage regulator and the N-channel MOSFETs. Checking the power dissipation and junction temperature is always a good design practice. Begin by determining the  $r_{DS(on)}$  of the N-channel MOSFET according to the input voltage and operating temperature. As an initial estimate, use the highest operating ambient temperature of interest and read  $r_{DS(on)}$  from the graphs shown under the typical characteristics section of this data sheet. Using this value, the power dissipation per switch can be calculated by:

$$P_D = r_{DS(on)} \times I^2$$

Multiply this number by four to get the total power dissipation coming from the N-channel MOSFETs.

The power dissipation for the internal voltage regulator is calculated using:

$$\mathsf{P}_{\mathsf{D}} = \left(\mathsf{V}_{\mathsf{I}(\mathsf{BP})} - \mathsf{V}_{\mathsf{O}(\mathsf{min})}\right) \times \mathsf{I}_{\mathsf{O}(\mathsf{OUT})}$$

The total power dissipation for the device becomes:

$$P_{D(total)} = P_{D(voltage regulator)} + (4 \times P_{D(switch)})$$

Finally, calculate the junction temperature:

$$\mathsf{T}_{\mathsf{J}} = \mathsf{P}_{\mathsf{D}} \times \mathsf{R}_{\mathsf{\theta}\mathsf{J}\mathsf{A}} + \mathsf{T}_{\mathsf{A}}$$

Where:

$$T_A$$

= ambient temperature °C

$R_{\theta JA}$  = Thermal resistance °C/W, equal to inverting of derating factor found on the power dissipation table in this data sheet.

Compare the calculated junction temperature with the initial estimate. If they do not agree within a few degrees, repeat the calculation, using the calculated value as the new estimate. Two or three iterations are generally sufficient to get a reasonable answer.

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## **APPLICATION INFORMATION**

#### thermal protection

Thermal protection prevents damage to the IC when heavy-overload or short-circuit faults are present for extended periods. The faults force the TPS2070 and TPS2071 into constant-current mode at first, which causes the voltage across the high-side switch to increase; under short-circuit conditions, the voltage across the switch is equal to the input voltage. The increased dissipation causes the junction temperature to rise to high levels.

The protection circuit senses the junction temperature of the switch and shuts it off. Hysteresis is built into the thermal sense circuit, and after the device has cooled approximately 20 degrees the switch turns back on. The switch continues to cycle in this manner until the load fault or input power is removed.

The TPS2070 and TPS2071 implement a dual thermal trip to allow fully independent operation of the power distribution switches. In an overcurrent or short-circuit condition the junction temperature rises. Once the die temperature rises to approximately 140°C, the internal thermal-sense circuitry determines which power switch is in an overcurrent condition and turns only that power switch off, thus isolating the fault without interrupting operation of the adjacent power switch. If the die temperature exceeds the first thermal trip point of 140°C and reaches 150°C, the device turns off. The OC output is asserted (active low) when overtemperature or overcurrent occurs.

## undervoltage lockout (UVLO)

An undervoltage lockout ensures that the device (LDO and switches) is in the off state at power up. The UVLO will also keep the device from being turned on until the power supply has reached the start threshold (see undervoltage lockout table), even if the switches are enabled. The UVLO will activate whenever the input voltage falls below the stop threshold as defined in the undervoltage lockout table. This facilitates the design of hot-insertion systems where it is not possible to turn off the power switches before input power is removed. Upon reinsertion, the power switches will be turned on with a controlled rise time to reduce EMI and voltage overshoots.

#### self-power to bus-power or bus-power to self-power transition

An autoswitching function between bus-powered mode and self-powered mode is a feature of the TPS2070 and TPS2071. When this feature is enabled (BP\_DIS is inactive) and SP is removed or applied, a transition will be initiated. The transition sequence begins with the internal LDO being turned off and its external capacitance discharged. Any enabled switches are also turned off and the external capacitors discharged. Once the LDO and switch outputs are low, the internal logic will turn the LDO back on. This entire sequence occurs whenever power to the SP input is removed or applied, regardless of the source of power, i.e., an external power supply or the use of the external regulator.

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## **APPLICATION INFORMATION**

## universal serial bus (USB) applications

The universal serial bus (USB 1.1) interface is a 12-Mb/s, 1.5-Mb/s, or 480 Mb/s (USB 2.0), multiplexed serial bus designed for low-to-medium bandwidth PC peripherals (e.g., keyboards, printers, scanners, and mice). The four-wire USB interface is conceived for dynamic attach-detach (hot plug-unplug) of peripherals. Two lines are provided for differential data, and two lines are provided for 5-V power distribution.

USB data is a 3.3-V-level signal, but power is distributed at 5 V to allow for voltage drops in cases where power is distributed through more than one hub or across long cables. Each function must provide its own regulated 3.3 V from the 5-V input or its own internal power supply.

The USB specification defines the following five classes of devices, each differentiated by power-consumption requirements:

- Hosts/self-powered hubs (SPH)

- Bus-powered hubs (BPH)

- Low-power, bus-powered functions

- High-power, bus-powered functions

- Self-powered functions

Self-powered and bus-powered hubs distribute data and power to downstream functions. The TPS2070 and TPS2071 can provide power-distribution solutions for hybrid hubs that need switching between BPH and SPH according to power availability and application requirements.

## **USB** power-distribution requirements

USB can be implemented in several ways, and, regardless of the type of USB device being developed, several power-distribution features must be implemented.

- Hosts/self-powered hubs must:

- Current-limit downstream ports

- Report overcurrent conditions on USB V<sub>BUS</sub>

- Output 5.25 V to 4.75 at 500 mA

- Bus-powered hubs must:

- Enable/disable power to downstream ports

- Power up at <100 mA</li>

- Limit inrush current (<44  $\Omega$  and 10  $\mu$ F)

- Output 5.25 V to 4.4 at 100 mA

- Not send power back upstream

- Functions must:

- Limit inrush currents

- Power up at <100 mA</li>

- Not send power back upstream (SP functions)

The feature set of the TPS2070 and TPS2071 allows them to meet each of these requirements. The integrated current-limiting and overcurrent reporting is required by hosts and self-powered hubs. The logic-level enable and controlled rise times meet the needs of both input and output ports on hubs, as well as the input ports for bus-powered functions

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## **APPLICATION INFORMATION**

## **USB** hybrid hub

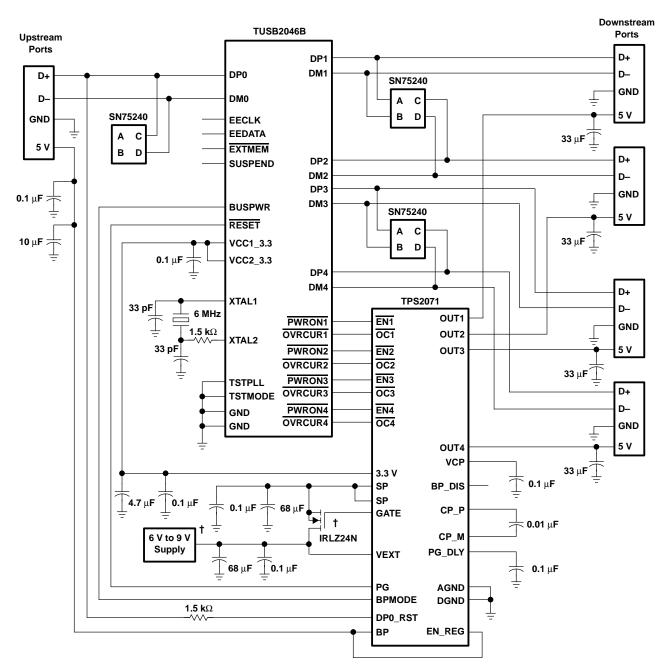

A USB hybrid hub can be simply implemented using the TPS2071 USB power controller and a TUSB2046 USB hub controller as shown in Figure 38. The TPS2071 USB power controller provides all the power needs to the four downstream ports and meets all the USB power specifications for both self-powered hubs and bus-powered hubs. The power controllers integrated 3.3-V LDO is used to provide power for the hub controller and any other local functions (e.g. transient suppressor SN75240), which saves board space and cost. The TPS2071 also provides the hub controller with a power good (PG) signal that connects to the RESET input of the hub controller to automatically reinitialize the hub when switching between self-powered mode and bus-powered mode whenever the self-power supply is connected or disconnected. The amount of time in which the hub controller is kept in a reset state is controlled by a capacitor connected between the PG\_DLY pin of the power controller and ground.

By using an external N-channel MOSFET and the TPS2071 internal voltage-regulator controller, a regulated 5-V self-powered source can be generated from an input voltage range of 6 V to 9 V (see Figure 38). In this configuration, the internal voltage regulator controller is enabled by connecting the EN\_REG input to the BP input. Using the internal voltage regulator controller also requires connecting a 0.01  $\mu$ F capacitor between CP\_P and CP\_M of the TPS2071 power controller. Also, a 0.1- $\mu$ F capacitor is needed between VCP of the power controller and ground.

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## **APPLICATION INFORMATION**

<sup>†</sup> This hybrid hub can also be implemented by connecting a 5-V power supply to the SP input of the TPS2071 and eliminating the external FET. However, this type of implementation is best suited for the TPS2074/75 (refer to the TPS2074, TPS2075 data sheet for details).

Figure 38. USB Hybrid Hub Using TPS2071 Power Controller and TUSB2046 Hub Controller

PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

SLVS287A - SEPTEMBER 2000 - REVISED FEBRUARY 2001

## **MECHANICAL DATA**

DAP (R-PDSO-G\*\*) 38 PINS SHOWN

0,30 0,65  $\Phi$ 0,13 M 0,19 38 20 **Thermal Pad** (see Note D) 6,20 8,40 NOM 7,80 0,15 NOM  $\cap$ Gage Plane Π 1 19 0.25 0°-8° 0,75 0,50 Seating Plane 0,15 1,20 MAX 0,10  $\frown$ 0,05 PINS \*\* 28 30 32 38 DIM A MAX 9,80 11,10 11,10 12,60 A MIN 9,60 10,90 10,90 12,40 4073257/A 07/97

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

## PACKAGE OPTION ADDENDUM

18-Oct-2005

## **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| TPS2070DAP       | ACTIVE                | HTSSOP          | DAP                | 32   | 46             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| TPS2071DAP       | ACTIVE                | HTSSOP          | DAP                | 32   | 46             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| TPS2071DAPR      | ACTIVE                | HTSSOP          | DAP                | 32   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| TPS2071DAPRG4    | ACTIVE                | HTSSOP          | DAP                | 32   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

#### Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated