SLUS232B - DECEMBER 19, 2002 - REVISED OCTOBER 2007

# **LOAD SHARE CONTROLLER**

#### **FEATURES**

- 2.7-V to 20-V Operation

- 8-Pin Package

- Requires Minimum Number of External Components

- Compatible with Existing Power Supply Designs Incorporating Remote Output Voltage Sensin

- Differential Share Bus

- Precision Current Sense Amplifier (40 Gain)

- UVLO (Undervoltage Lockout) Circuitry

- User Programmable Share Loop Compensation

### **APPLICATIONS**

Paralelled Power Supplies

#### DESCRIPTION

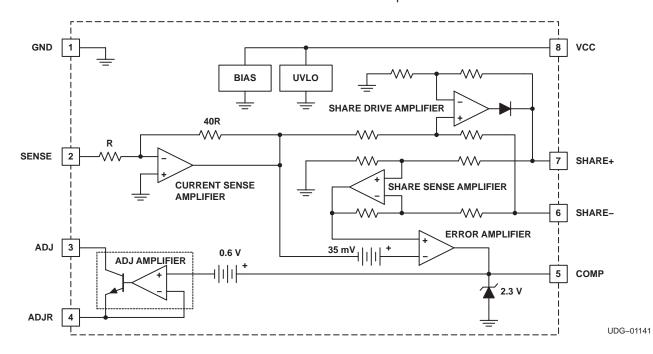

The UC3902 load share controller is an 8-pin device that balances the current drawn from independent, paralleled power supplies. Load sharing is accomplished by adjusting each supplies' output current to a level proportional to the voltage on a share bus.

The master power supply, which is automatically designated as the supply that regulates to the highest voltage, drives the share bus with a voltage proportional to its output current. The UC3902 trims the output voltage of the other paralleled supplies so that they each support their share of the load current. Typically, each supply is designed for the same current level although that is not necessary for use with the UC3902. By appropriately scaling the current sense resistor, supplies with different output current capability can be paralleled with each supply providing the same percentage of their output current capability for a particular load.

### **DESCRIPTION** (continued)

A differential line is used for the share bus to maximize noise immunity and accommodate different voltage drops in each power converter's ground return line. Trimming of each converter's output voltage is accomplished by injecting a small current into the output voltage sense line, which requires a small resistance (typically 20  $\Omega$  to 100  $\Omega$ ) to be inserted.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

|                                       |                                     | UC2902<br>UC3902 | UNIT |  |

|---------------------------------------|-------------------------------------|------------------|------|--|

|                                       | VCC, ADJ                            | -0.3 to 20       |      |  |

| Lamest coefficient man was M          | SENSE                               | -5 to 5          | .,   |  |

| Input voltage range, V <sub>I</sub>   | ADJR, COMP                          | -0.3 to 4        | \ \  |  |

|                                       | SHARE-, SHARE+                      | -0.3 to 10       | ]    |  |

| Output current, IO                    | SHARE+                              | -100 mA to 10 mA | mA   |  |

|                                       | ADJ                                 | –1 mA to 30 mA   | mA   |  |

| Operating free-air temperate          | ure range, Тд                       | -40 to 100       |      |  |

| Junction temperature range            | , TJ                                | -55 to 105       | ]    |  |

| Storage temperature, T <sub>Stg</sub> |                                     | -65 to 150       | °C   |  |

| Lead temperature 1,6 mm (             | 1/16 inch) from case for 10 seconds | 300              |      |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. Voltages are with respect to GND. Currents are positive into, and negative out of the specified terminal.

#### RECOMMENDED OPERATING CONDITIONS

|                                                | MIN | MAX | UNIT |

|------------------------------------------------|-----|-----|------|

| Supply voltage, V <sub>CC</sub>                | 4   | 10  | V    |

| Operating junction temperature, T <sub>J</sub> |     | 85  | °C   |

## **ELECTRICAL CHARACTERISTICS**

$T_J = -40^{\circ}C$  to  $105^{\circ}C$ , (unless otherwise noted)

|                          | PARAMETER                         | TEST CONDITIONS                                                                        | MIN  | TYP  | MAX  | UNIT |

|--------------------------|-----------------------------------|----------------------------------------------------------------------------------------|------|------|------|------|

| Power S                  | UPPLY SUPPLY CURRENT              |                                                                                        |      |      |      |      |

|                          | Owner has a summared              | SHARE+ = 1 V, SENSE = 0 V                                                              |      | 4    | 6    | mA   |

| ICC Supply current       |                                   | V <sub>CC</sub> = 20 V                                                                 |      | 6    | 10   | mA   |

| UNDERV                   | OLTAGE LOCKOUT                    |                                                                                        |      |      |      |      |

| VCC                      | Startup voltage                   | SHARE+ = 0.2 V, SENSE = 0 V, COMP = 1 V                                                | 2.3  | 2.5  | 2.7  | .,   |

|                          | Hysteresis                        | SHARE+ = 0.2 V, SENSE = 0 V, COMP = 1 V                                                | 60   | 100  | 140  | V    |

| CURREN                   | IT SENSE AMPLIFIER                |                                                                                        |      |      |      |      |

| V <sub>IO</sub>          | Input offset voltage              | 0.1 V ≤ V <sub>(SHARE+)</sub> ≤ 1.1 V                                                  | -2.5 | -0.5 | 1.5  | mV   |

|                          | SENSE to SHARE gain               | 0.1 V ≤ V(SHARE+) ≤ 1.1 V                                                              | -41  | -40  | -39  | V    |

| R <sub>IN</sub>          | Input resistance                  |                                                                                        | 0.6  | 1    | 1.5  | V    |

| SHARE [                  | DRIVE AMPLIFIER                   | •                                                                                      |      |      |      |      |

|                          |                                   | $V_{CC} = 2.5 \text{ V}$ $V_{(SENSE)} = -50 \text{ mV}$ $I_{(SHARE+)} = -1 \text{ mA}$ | 1.2  | 1.4  |      |      |

| VOH High-level of SHARE+ | High-level output voltage, SHARE+ | $V_{CC} = 12 \text{ V}$ $V_{(SENSE)} = -250 \text{ mV}$ $I_{(SHARE+)} = -1 \text{ mA}$ | 9.6  | 10.0 | 10.4 | V    |

|                          |                                   | $V_{CC} = 20 \text{ V}$ $V_{(SENSE)} = -250 \text{ mV}$ $I_{(SHARE+)} = -1 \text{ mA}$ | 9.6  | 10.0 | 10.4 |      |

|                          |                                   | $V_{CC} = 2.5 \text{ V}$ $V_{(SENSE)} = 10 \text{ mV}$ $I_{(SHARE+)} = -1 \text{ mA}$  |      | 20   | 50   |      |

| $V_{OL}$                 | Low-level output voltage, SHARE+  | $V_{CC} = 12 \text{ V}$ $V_{(SENSE)} = 10 \text{ mV}$ $I_{(SHARE+)} = -1 \text{ mA}$   |      | 20   | 50   |      |

|                          |                                   | $V_{CC} = 20 \text{ V}$ $V_{(SENSE)} = 10 \text{ mV}$ $I_{(SHARE+)} = -1 \text{ mA}$   |      | 20   | 50   | mV   |

| VO                       | Output voltage, SHARE+            | $V(SENSE) = 0$ mV, $R(SHARE+) = 200 \Omega$ (SHARE+ to GND)                            |      | 20   | 40   |      |

| CMRR                     | Common mode rejection ratio       | 0 V ≤ V(SHARE-) ≤ 1 V,<br>SENSE used as input to amplifier                             | 50   | 90   |      | dB   |

|                          | Load regulation                   | Load on SHARE+, 1 mA $\leq$ ILOAD $\leq$ -20 mA V(SENSE) = -25 mV                      |      | 0    | 20   | mV   |

| Isc                      | Short circuit current             | V(SHARE+) = 0 V, V(SENSE) = -25 mV                                                     | -85  | -50  | -20  | mA   |

|                          | Classinate                        | V(SENSE) = 10 mV to -90 mV step<br>R(SHARE+) = 200 Ω (SHARE+ to GND)                   | 0.12 | 0.26 | 0.38 | \//  |

|                          | Slew rate                         | V(SENSE) = -90 mV to 10 mV step<br>R(SHARE+) = 200 Ω (SHARE+ to GND)                   | 0.12 | 0.26 | 0.38 | V/μs |

# **ELECTRICAL CHARACTERISTICS (continued)**

$T_J = -40^{\circ}C$  to  $105^{\circ}C$ , (unless otherwise noted)

|                                    | PARAMETER                        | TEST CONDITIONS                                                                                                          | MIN  | TYP   | MAX  | UNIT     |

|------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|-------|------|----------|

| SHARE SEI                          | NSE AMPLIFIER                    |                                                                                                                          |      |       |      |          |

|                                    | Lord Superdone                   | V(SHARE+) = 1 V, V(SHARE-) = GND<br>V(SENSE) = 10 mV                                                                     | 8    | 15    |      | 1.0      |

| R <sub>IN</sub>                    | Input impedance                  | $R(SHARE+) = 200 \Omega$ (SHARE+ to GND)<br>V(SHARE-) = 1 V, $V(SENSE) = 10 \text{ mV}$                                  | 8    | 15    |      | kΩ       |

| V(SHARE)                           | Threshold voltage                | V(SENSE) = 0 V                                                                                                           | 41   | 70    | 100  | mV       |

| CMRR                               | Common mode rejection ratio      | $0 \text{ V} \leq \text{V}(\text{SHARE}_{-}) \leq 1 \text{ V}, \text{V}(\text{SENSE}) = -2.5 \text{ mV}$                 | 50   | 60    |      |          |

| AVO.                               | DESCRIPTION from SHARE+ to       | V(SENSE) = -2.5 mV,<br>5 nF capacitor from COMP to GND,<br>1 kΩ resistor from ADJR to GND                                | 50   | 68    |      | dB       |

| AVOL                               | ADJR                             | V(SENSE) = -2.5 mV,<br>5 nF capacitor from COMP to GND,<br>150 $\Omega$ resistor from ADJR to GND                        | 50   | 50 66 |      |          |

|                                    | Slew rate                        | V(SHARE+) = 0 mV to 10 V step through a 200-Ω resistor, $R(COMP) = 500$ Ω, $V(SENSE) = 10$ mV, $VCC = 10$ V              | 0.2  | 0.5   | 0.8  | V/μs     |

| ERROR AM                           | PLIFIER                          | •                                                                                                                        |      |       |      |          |

| 9M                                 | Transconductance, SHARE+ to COMP | 200-Ω resistor SHARE+ to GND                                                                                             | 3.0  | 4.5   | 6.0  | mS       |

| ІОН                                | High-level output current        | V(COMP) = 1.5 V, SHARE+ ≥ 300 mV<br>V(SENSE) = -10 mV                                                                    | -450 | -325  | -200 |          |

| lOL                                | Low-level output current         | 200-Ω resistor SHARE+ to GND,<br>V(COMP) = 1.5 V, V(SENSE) = 10 mV                                                       | 80   | 150   | 250  | μΑ       |

| V <sub>IO</sub>                    | Input offset voltage             |                                                                                                                          | 15   | 35    | 65   | mV       |

| $\Delta V_{IO}/\Delta V_{(SENSE)}$ |                                  | 1-kΩ resistor ADJR to GND<br>-2.5 mV ≤ V(SENSE) ≤ -25 mV                                                                 | -6   | 0     | 6    | mV/V     |

| ADJ AMPLI                          | FIER                             |                                                                                                                          |      |       |      |          |

|                                    | ADJR low voltage                 | 200-Ω resistor SHARE+ to GND,<br>V(SENSE) = 10 mV                                                                        | -1   | 0     | 1    | mV       |

|                                    | ADJR high voltage                | V(SENSE) = 10 mV, V(SHARE+) = 1 V                                                                                        | 1.4  | 1.8   | 2.1  | V        |

|                                    |                                  | I <sub>(ADJR)</sub> = -0.5 mA, V <sub>(ADJ)</sub> = 2.5 V,<br>V <sub>(SENSE)</sub> = 10 mV, V <sub>(SHARE+)</sub> = 1 V  | 0.96 | 0.99  | 1.02 |          |

|                                    | Current gain ADJR to ADJ         | I <sub>(ADJR)</sub> = -0.5 mA, V <sub>(ADJ)</sub> = 20 V,<br>V(SENSE) = 10 mV, V(SHARE+) = 1 V                           | 0.96 | 0.99  | 1.02 | A /A     |

|                                    |                                  | $I_{(ADJR)} = -10 \text{ mA}, \ V_{(ADJ)} = 2.5 \text{ V},$<br>$V_{(SENSE)} = 10 \text{ mV}, V_{(SHARE+)} = 1 \text{ V}$ | 0.96 | 0.99  | 1.02 | A/A<br>2 |

|                                    |                                  | $I_{(ADJR)} = -10 \text{ mA}, \ V_{(ADJ)} = 20 \text{ V}, \ V_{(SENSE)} = 10 \text{ mV}, V_{(SHARE+)} = 1 \text{ V}$     | 0.96 | 0.99  | 1.02 |          |

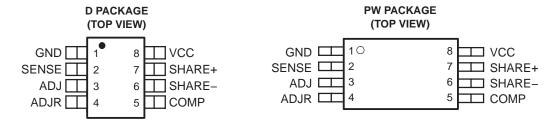

### **ORDERING INFORMATION**

| TA            | PACKAGE(2)      | PART NUMBER |

|---------------|-----------------|-------------|

| 4000 to 0500  | Plastic DIP (D) | UC2902D     |

| -40°C to 85°C | SOIC (PW)       | UC2902PW    |

| 200 1- 7000   | Plastic DIP (D) | UC3902D     |

| 0°C to 70°C   | SOIC (PW)       | UC3902PW    |

<sup>(2)</sup> The PW package is also available taped and reeled. Add an R suffix to the device type (i.e., bq24901PWR) for quantities of 3,000 devices per reel.

### **TERMINAL FUNCTIONS**

| TERMINAL |     |     | DECORPORION                                                    |

|----------|-----|-----|----------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                    |

| ADJ      | 3   | 1   | Current output of the adjust amplifier circuit (NPN collector) |

| ADJR     | 4   | 0   | Current adjust amplifier range set (NPN emitter)               |

| COMP     | 5   | I/O | Output of the error amplifier, input of the adjust amplifier   |

| GND      | 1   | _   | Local power supply return and signal ground                    |

| SENSE    | 2   | - 1 | Inverting input of the current sense amplifier                 |

| SHARE+   | 7   | I/O | Positive input from share bus or drive-to-share bus            |

| SHARE-   | 6   | 1   | Reference for SHARE+ pin                                       |

| VCC      | 8   | 1   | Local power supply (positive)                                  |

#### APPLICATION INFORMATION

The values of five passive components must be determined to configure the UC3902 load share controller. The output and return lines of each converter are connected together at the load, with current sense resistor  $R_{SENSE}$  inserted in each negative return line. Another resistor,  $R_{ADJ}$ , is also inserted in each positive remote sense line. The differential share bus terminals (SHARE+ and SHARE-) of each UC3902 are connected together respectively, and the SHARE- node is also connected to the system ground. A typical application is illustrated in Figure 1.

The load share controller design can be executed by following the next few steps:

#### Step 1.

$$R_{SENSE} = \frac{V_{SHARE(max)}}{A_{CSA} \times I_{O(max)}}$$

(1)

where A<sub>CSA</sub> is 40, the gain of the current sense amplifier

At full load, the voltage drop across the R<sub>SENSE</sub> resistor is  $I_{O(max)} \times R_{SENSE}$ . Taking into account the gain of the current sense amplifier, the voltage at full load on the current share bus,

$$V_{SHARE(max)} = \frac{A_{CSA} \times I_{O(max)}}{R_{SENSE}}$$

(2)

This voltage must stay 1.5-V below  $V_{CC}$  or below 10 V whichever is smaller.  $V_{SHARE}$  represents an upper limit but the designer should select the full scale share bus voltage keeping in mind that every volt on the load share bus increases the master controller's supply current by approximately 100 mA times the number of slave units connected parallel.

#### Step 2.

$$R_{G} = \frac{V_{ADJ(max)}}{I_{ADJ(max)}}$$

(3)

Care must be taken to ensure that  $I_{ADJ(max)}$  is low enough so that both the drive current and power dissipation are within the device's capability. For most applications, an  $I_{ADJ(max)}$  current between 5 mA and 10 mA is acceptable. In a typical application, a 360- $\Omega$  R<sub>G</sub> resistor from the ADJR pin to ground sets  $I_{ADJ(max)}$  to approximately 5 mA.

#### Step 3.

$$R_{ADJ} = \frac{\Delta V_{O(max)} - \left(I_{O(max)} \times R_{SENSE}\right)}{I_{ADJ(max)}}$$

(4)

$R_{ADJ}$  must be low enough to not affect the normal operation of the converter's voltage feedback loop. Typical  $R_{ADJ}$  values are between 20  $\Omega$  to100  $\Omega$  depending on  $V_O$ ,  $\Delta V_{O(max)}$  and the selected  $I_{ADJ(max)}$  value.

### Step 4.

$$C_{C} = \frac{g_{M}}{2\pi \times f_{C}} \times \frac{R_{ADJ}}{R_{G}} \times \frac{R_{SENSE}}{R_{LOAD}} \times A_{CSA} \times A_{PWR} \quad (f_{C})$$

(5)

The share loop compensation capacitor,  $C_C$  is calculated to produce the desired share loop unity gain crossover frequency,  $f_C$ . The share loop error amplifier's transconductance,  $g_M$  is nominally 4.5 ms. The values of the resistors are already known. Typically,  $f_C$  is set to at least one order of magnitude below the converter's closed loop bandwidth. The load share circuit is primarily intended to compensate for each converter's initial output voltage tolerance and temperature drift, not for differences in their transient response. The term  $A_{PWR(f_C)}$  is the gain of the power supply measured at the desired share loop crossover frequency,  $f_C$ . This gain can be measured by injecting the measurement signal between the positive output and the positive sense terminal of the power supply.

### Step 5.

$$R_{C} = \frac{1}{2\pi \times f_{C} \times C_{C}} \tag{6}$$

A resistor in series with  $C_C$  is required to boost the phase margin of the load share loop. The zero is placed at the load share loop crossover frequency,  $f_C$ .

When the system is powered up, the converter with the highest output voltage tends to source the most current and take control of the share bus. The other converters increase their output voltages until their output currents are proportional to the share bus voltage minus 50 mV. The converter which in functioning as the master may change due to warmup drift and differences in load and line transient response of each converter.

#### **ADDITIONAL INFORMATION**

Please refer to the following topic for additional application information.

1. Application Note U–163, (TI Literature No. SLUA128) The UC3902 Load Share Controller and Its Performance in Distributed Power Systems by Laszlo Balogh

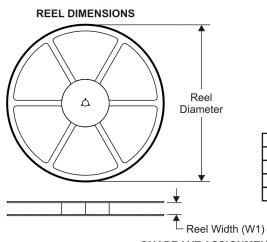

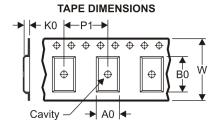

### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

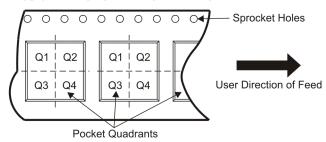

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device    | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------|-----------------|--------------------|---|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| UC2902DTR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

| UC2902DTR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

| UC3902DTR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

| UC3902DTR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

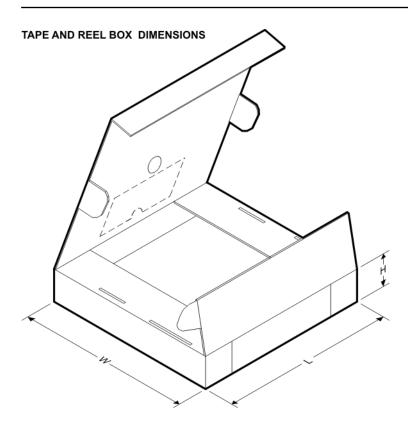

\*All dimensions are nominal

| Device    | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC2902DTR | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| UC2902DTR | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

| UC3902DTR | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| UC3902DTR | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated