# TMS320VC5471 Fixed-Point Digital Signal Processor

# Data Manual

Literature Number: SPRS180C June 2001 – Revised December 2002

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated

### **REVISION HISTORY**

| REVISION | REVISION DATE PRODUCT STATUS      |                 | HIGHLIGHTS                                                                                                                                                            |

|----------|-----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *        | June 2001                         | Product Preview | Original                                                                                                                                                              |

| А        | December 2001                     | Production Data | Updated characteristic data                                                                                                                                           |

| В        | July 2002                         | Production Data | Updated ARM SRAM read and write timing diagrams                                                                                                                       |

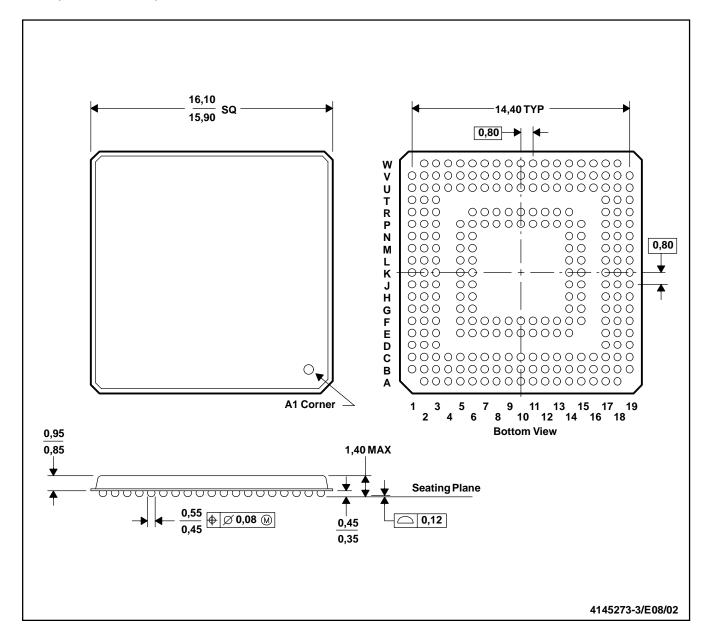

| С        | C December 2002 Production Data C |                 | Added industrial temperature specifications to the Recommended Operating Conditions and the Absolute Maximum Ratings (page 47). Updated mechanical drawing (page 87). |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

|          |                                   |                 |                                                                                                                                                                       |

# **Contents**

| Se | ection |          |                                                | Pa |

|----|--------|----------|------------------------------------------------|----|

| 1  | TMS3   | 20VC547  | 1 Features                                     |    |

| 2  | Introd | uction   |                                                |    |

|    | 2.1    | Descrip  | ition                                          |    |

|    | 2.2    | Pin Ass  | signments                                      |    |

|    | 2.3    | Termina  | al Functions                                   |    |

| 3  | DSP S  | Subsyste | m Functional Overview                          |    |

|    | 3.1    | DSP Co   | ore                                            |    |

|    |        | 3.1.1    | DSP Memory Space and Buses                     |    |

|    |        | 3.1.2    | DSP Scan-Based Emulation Logic                 |    |

|    | 3.2    | DSP Me   | emory                                          |    |

|    |        | 3.2.1    | DSP On-Chip RAM                                |    |

|    |        | 3.2.2    | Normal Mode DSP Memory Map                     |    |

|    |        | 3.2.3    | API Boot Mode                                  |    |

|    |        | 3.2.4    | API Boot-Mode DSP Memory Map                   |    |

|    |        | 3.2.5    | DSP Extended Program Memory                    |    |

|    |        | 3.2.6    | DSP Relocatable Interrupt Vector Table         |    |

|    | 3.3    | DSP Re   | egisters                                       |    |

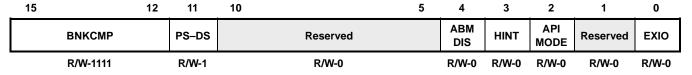

|    |        | 3.3.1    | Bank-Switching Control Register                |    |

|    |        | 3.3.2    | Programmable Bank-Switching Wait-States        |    |

|    |        | 3.3.3    | Processor Mode Status Register                 |    |

|    | 3.4    | DSP Pe   | eripherals                                     |    |

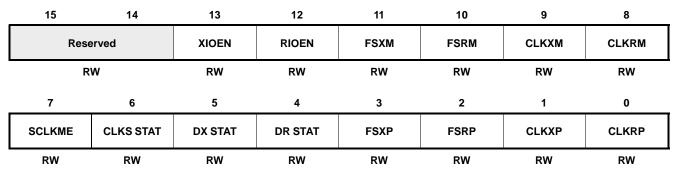

|    |        | 3.4.1    | Multichannel Buffered Serial Port (McBSP)      |    |

|    |        | 3.4.2    | DSP Direct Memory Access (DMA) Controller      |    |

|    |        | 3.4.3    | ARM Port Interface (API)                       |    |

|    |        | 3.4.4    | DSP External Memory Interface                  |    |

|    |        | 3.4.5    | DSP Software-Programmable Wait-State Generator |    |

|    |        | 3.4.6    | DSP Timer                                      |    |

|    |        | 3.4.7    | DSP Clocking                                   |    |

|    | 3.5    |          | ower Management                                |    |

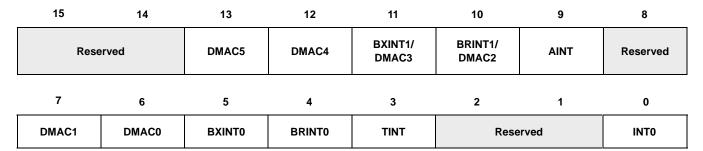

|    | 3.6    |          | terrupts                                       |    |

|    | MO: /  | 01       | Toward and Occupations                         |    |

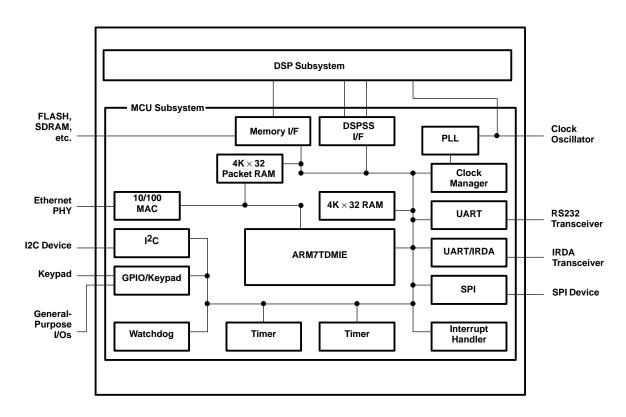

| 4  |        | -        | em Functional Overview                         |    |

|    | 4.1    |          | ore                                            |    |

|    |        | 4.1.1    | ARM7TDMI Emulation Features                    |    |

|    | 4.5    | 4.1.2    | MCU Memory Space                               |    |

|    | 4.2    |          | lemory Interface                               |    |

|    |        | 4.2.1    | MCU Memory Interface Wait-States               |    |

|    |        | 4.2.2    | MCU API Interface                              |    |

|    |        | 4.2.3    | MCU SDRAM Memory Interface                     |    |

|    |        |          |                                                |    |

| Se | ection |                                                    |                                                        |

|----|--------|----------------------------------------------------|--------------------------------------------------------|

|    | 4.3    | MCU Peripherals                                    |                                                        |

|    |        | 4.3.1 MCU Etherne                                  | et Interface Module                                    |

|    |        | 4.3.2 MCU Univers                                  | al Asynchronous Receiver/Transmitter (UART) Interfaces |

|    |        | 4.3.3 MCU Serial P                                 | Peripheral Interface (SPI)                             |

|    |        | 4.3.4 MCU General                                  | I-Purpose I/O                                          |

|    |        | 4.3.5 MCU Inter-Int                                | tegrated Circuit (I <sup>2</sup> C) Interface          |

|    |        | 4.3.6 MCU Timers                                   |                                                        |

|    |        | 4.3.7 MCU Interrup                                 | t Handler                                              |

|    | 4.4    | MCU Power-Down Mode                                | es                                                     |

|    | 4.5    | MCU Peripheral Clock M                             | Management                                             |

|    | 4.6    | Initialization                                     |                                                        |

|    |        | 4.6.1 Initial MCU C                                | ode                                                    |

|    |        | 4.6.2 DSP Boot Mo                                  | ode                                                    |

|    |        | 4.6.3 Emulation Su                                 | pport                                                  |

| 5  | Docur  | nentation Support                                  |                                                        |

|    |        |                                                    |                                                        |

| 6  |        | •                                                  |                                                        |

|    | 6.1    |                                                    | ngs                                                    |

|    | 6.2    |                                                    | ng Conditions                                          |

|    | 6.3    | Electrical Characteristics Temperature (Unless Otl | s Over Recommended Operating Case herwise Noted)       |

|    | 6.4    |                                                    | tance Characteristics                                  |

|    | 6.5    |                                                    | ology                                                  |

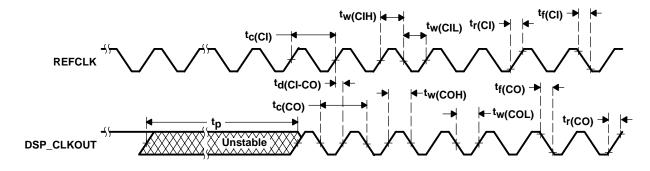

|    | 0.0    |                                                    | o/Divide-By-Four Clock Option Timing                   |

|    |        |                                                    | Clock Option (PLL Enabled) Timing                      |

|    | 6.6    | 1,,,                                               | Interface Timing                                       |

|    | 0.0    | •                                                  | d                                                      |

|    |        | ,                                                  | e                                                      |

|    |        | ,                                                  | ort Read Timing Requirements                           |

|    |        |                                                    | ort Write Switching Characteristics                    |

|    | 6.7    |                                                    | ally Generated Wait-States                             |

|    | 6.8    |                                                    |                                                        |

|    | 6.9    |                                                    | DSP_IAQ) and Interrupt Acknowledge (DSP_IACK) Timings  |

|    | 6.10   |                                                    | and DSP_TOUT Timings                                   |

|    | 6.11   | = :                                                | erial Port (McBSP) Timings                             |

|    |        |                                                    | ive and Transmit Timings                               |

|    |        |                                                    | eral-Purpose Timings                                   |

|    |        |                                                    | PI Master or Slave Timings                             |

|    | 6.12   |                                                    | nings                                                  |

|    | 6.13   | -                                                  |                                                        |

|    | 6.14   | _                                                  |                                                        |

|    | 6.15   | _                                                  |                                                        |

|    | 6.16   | _                                                  |                                                        |

|    |        |                                                    |                                                        |

| 7  |        |                                                    |                                                        |

|    | 7.1    | Ball Grid Array Mechanic                           | cal Data                                               |

# **List of Figures**

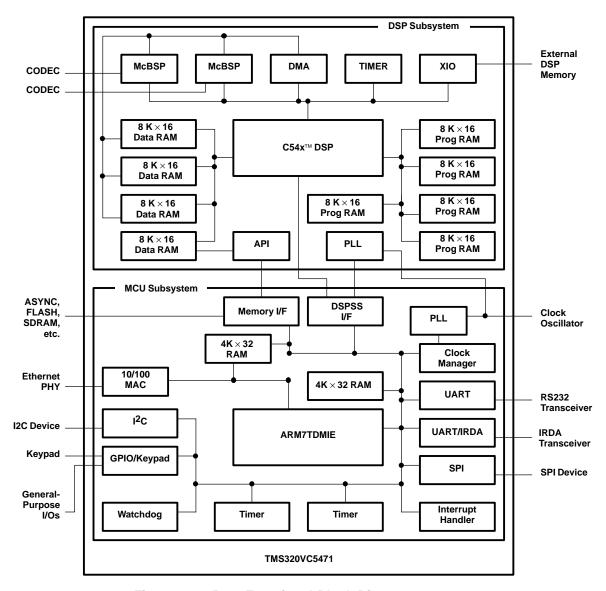

| 5471 Functional Block Diagram                                            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

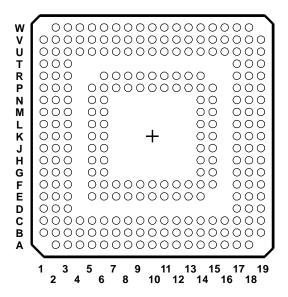

| 257-Ball GHK Package (Bottom View)                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

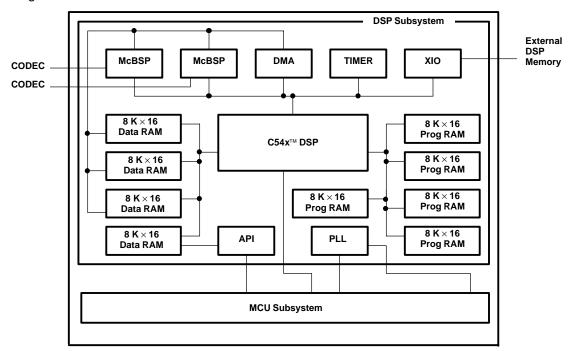

| 5471 DSP Subsystem Functional Block Diagram                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

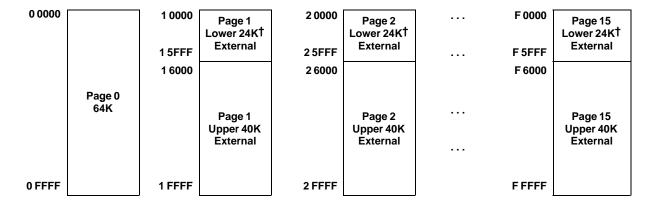

| Memory Map for DSP Accesses (DSP_APIBN = 1 or ABMDIS = 1)                | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| API Boot Mode Memory Map for DSP Accesses (DSP_APIBN = 0 and ABMDIS = 0) | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                          | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                          | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IFR and IMR Registers                                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5471 MCU Subsystem Functional Block Diagram                              | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

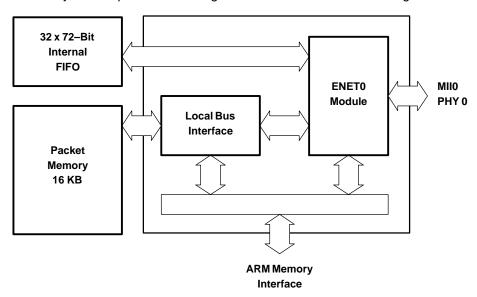

| Ethernet Interface Block Diagram                                         | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

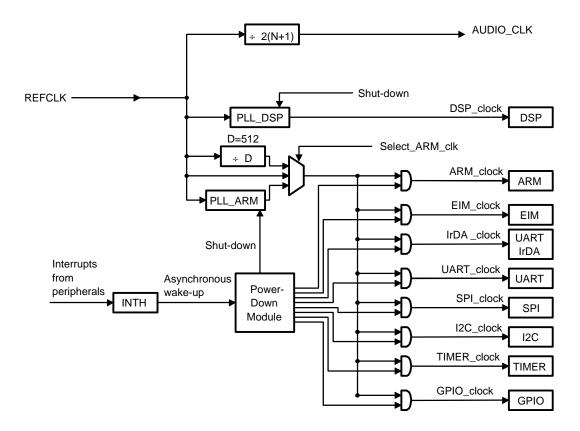

| Clock Management Module                                                  | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

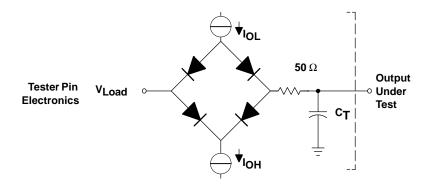

| 3.3-V Test Load Circuit                                                  | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

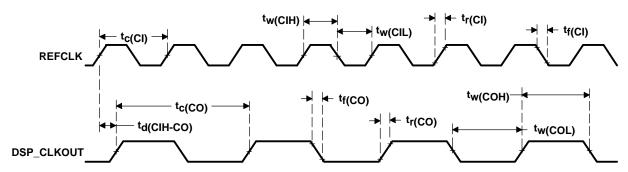

| External Divide-by-Two Clock Timing                                      | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| External Multiply-by-One Clock Timing                                    | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

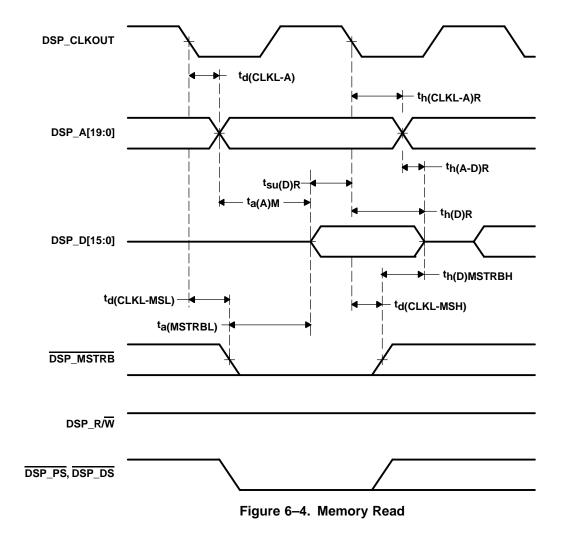

| Memory Read                                                              | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

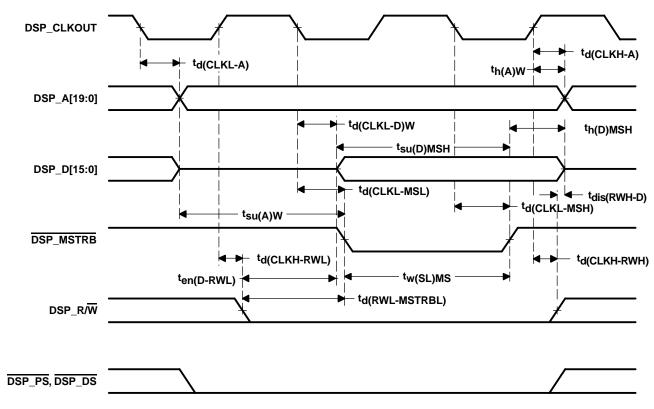

| Memory Write                                                             | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

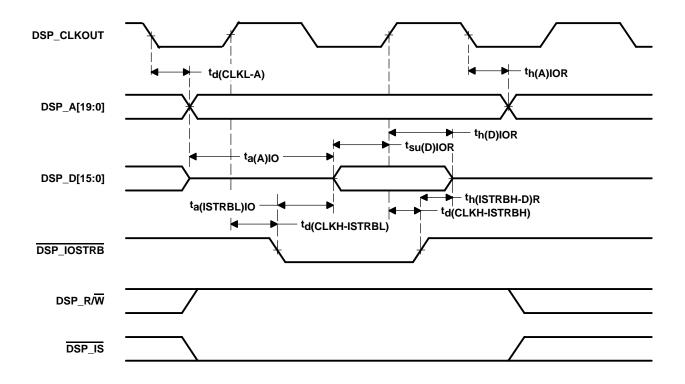

| Parallel I/O Port Read                                                   | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

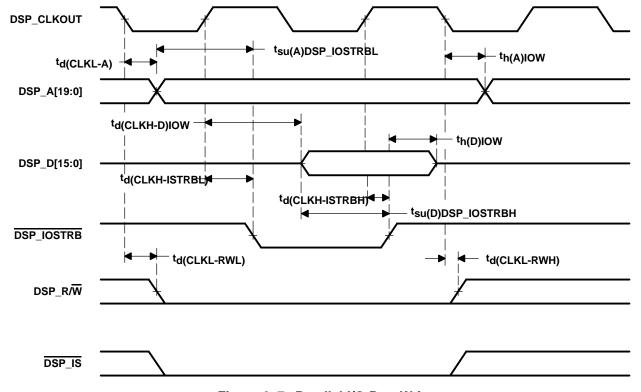

| Parallel I/O Port Write                                                  | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

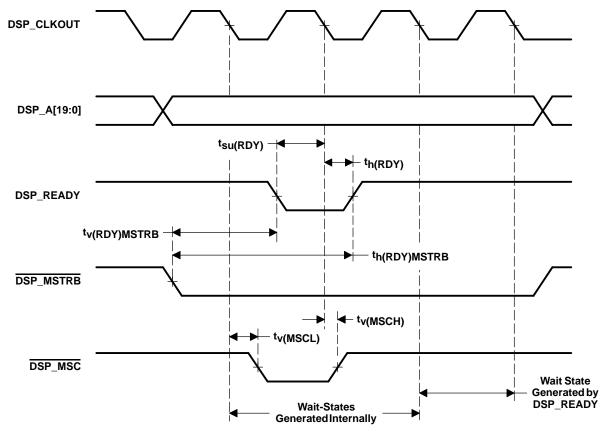

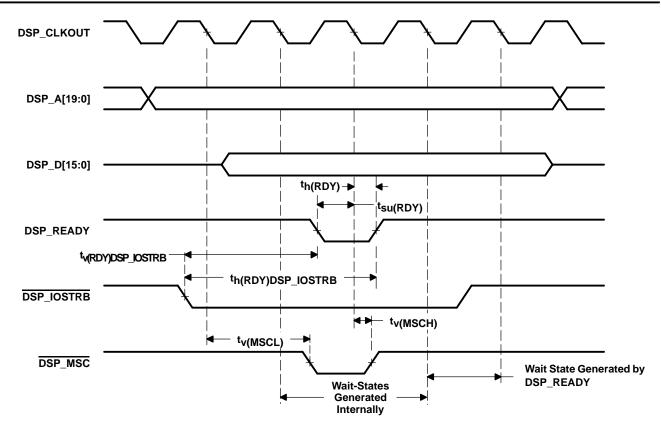

| Memory Read With Externally Generated Wait-States                        | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

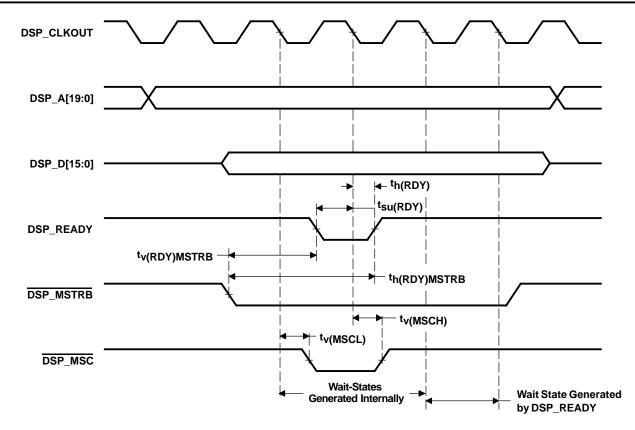

| Memory Write With Externally Generated Wait-States                       | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                          | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

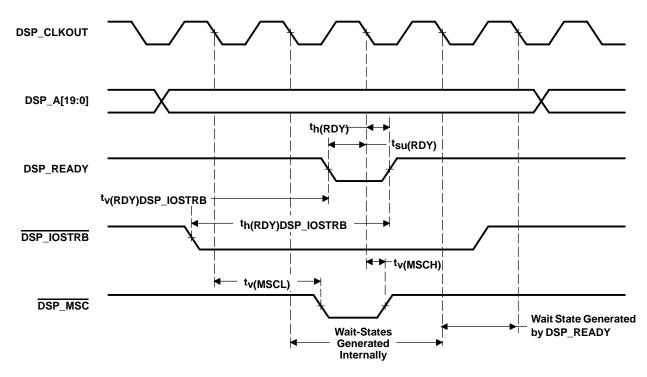

| I/O Write With Externally Generated Wait-States                          | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

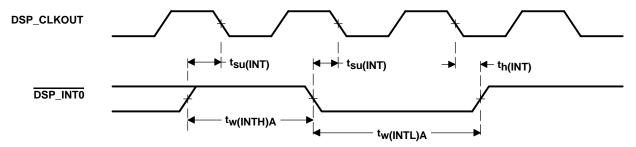

| Interrupt Timing                                                         | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

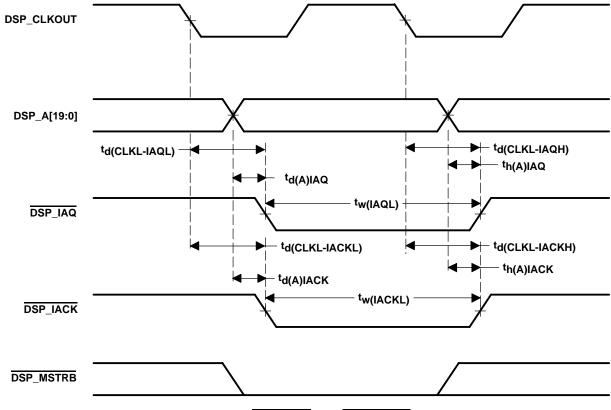

| DSP_IAQ and DSP_IACK Timings                                             | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

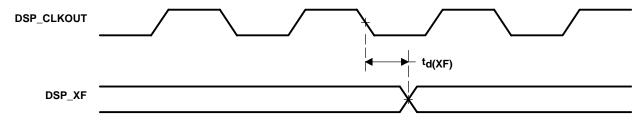

| DSP_XF Timing                                                            | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

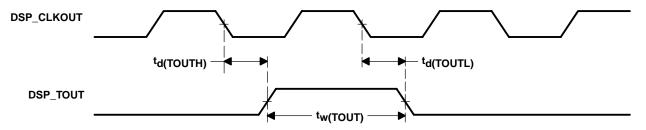

| DSP_TOUT Timing                                                          | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

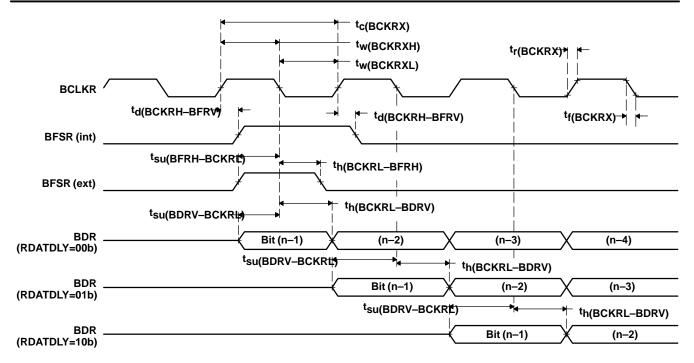

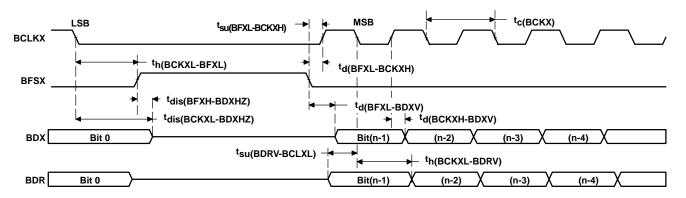

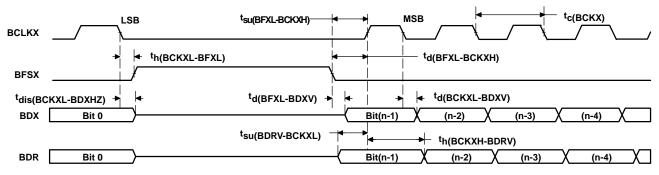

| McBSP Receive Timings                                                    | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

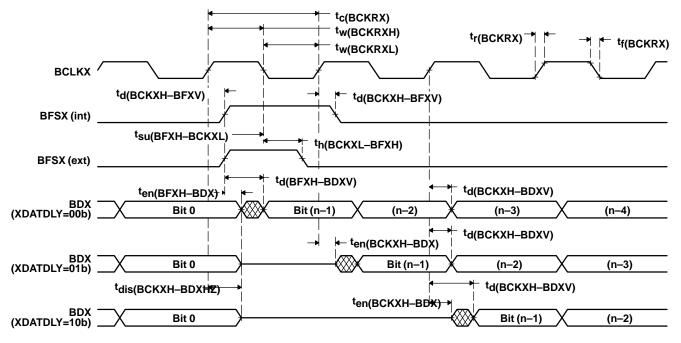

| McBSP Transmit Timings                                                   | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

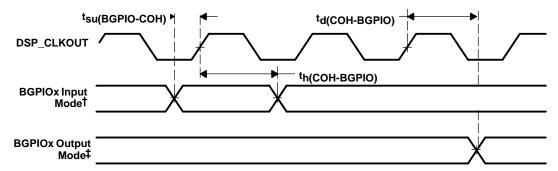

| McBSP General-Purpose I/O Timings                                        | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ·                                                                        | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -                                                                        | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

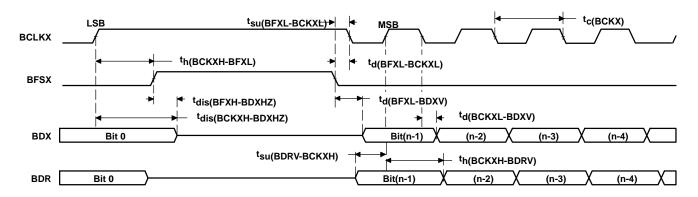

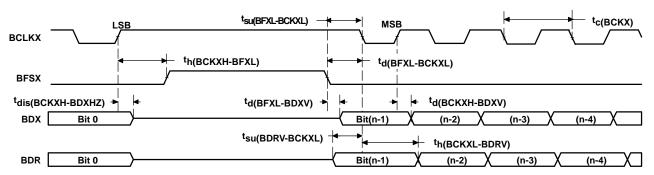

| McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1             | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1             | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

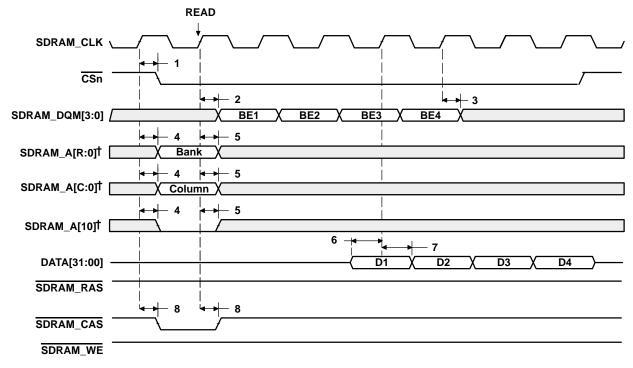

| SDRAM Read Command (CAS Latency 3)                                       | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

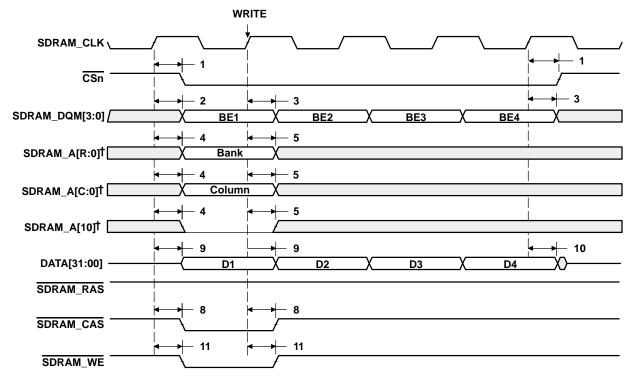

|                                                                          | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

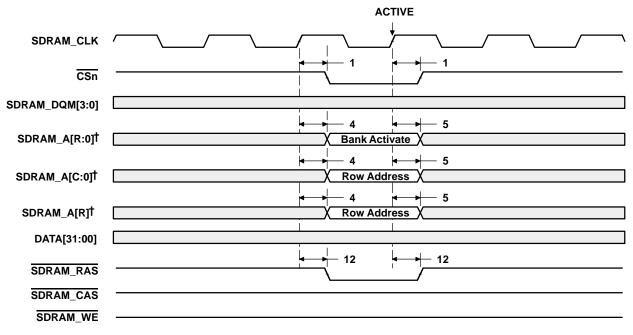

| SDRAM Active Command                                                     | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

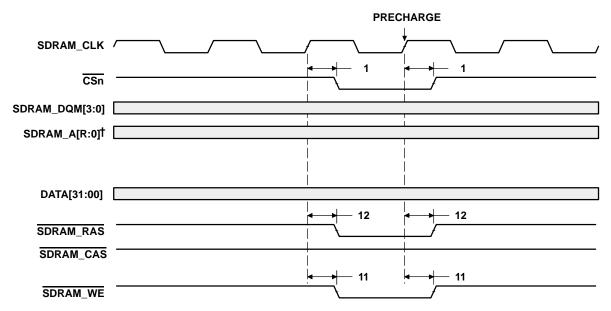

| SDRAM Precharge Command                                                  | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                          | Memory Map for DSP Accesses (DSP_APIBN = 1 or ABMDIS = 1)  API Boot Mode Memory Map for DSP Accesses (DSP_APIBN = 0 and ABMDIS = 0)  DSP Extended Program Memory Map  Bank-Switching Control Register (BSCR)  Pin Control Register (PCR)  IFR and IMR Registers  5471 MCU Subsystem Functional Block Diagram  Ethernet Interface Block Diagram  Clock Management Module  3.3-V Test Load Circuit  External Divide-by-Two Clock Timing  External Multiply-by-One Clock Timing  Memory Read  Memory Write  Parallel I/O Port Read.  Parallel I/O Port Read.  Parallel I/O Port Write .  Memory Read With Externally Generated Wait-States  Memory Write With Externally Generated Wait-States  I/O Read With Externally Generated Wait-States  I/O Read With Externally Generated Wait-States  Interrupt Timing  DSP_IAQ and DSP_IACK Timings  DSP_IAQ and DSP_IACK Timings  DSP_IAC Timing  McBSP Receive Timing  McBSP General-Purpose I/O Timings  McBSP Transmit Timings  McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0  McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 0  McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1  SDRAM Read Command (CAS Latency 3)  SDRAM Write Command |

#### Figures

| Figure |                                                                     | Page |

|--------|---------------------------------------------------------------------|------|

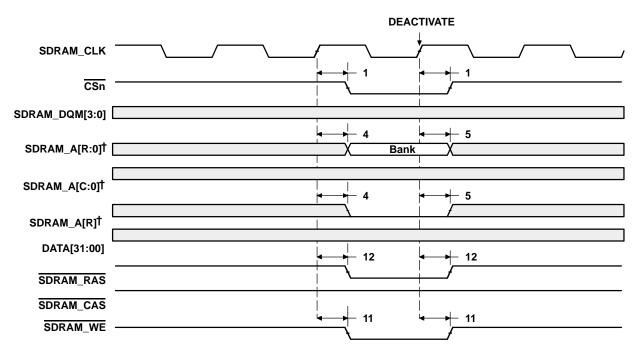

| 6–27   | SDRAM Deactivate Command                                            | 74   |

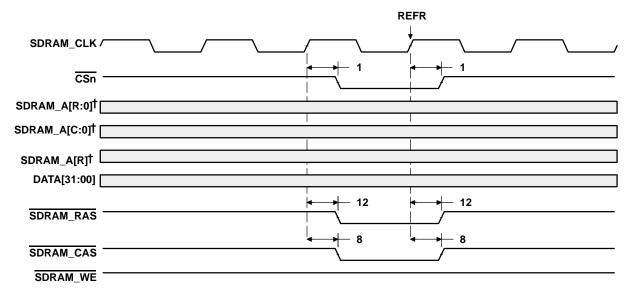

| 6–28   | SDRAM Refresh Command                                               | 75   |

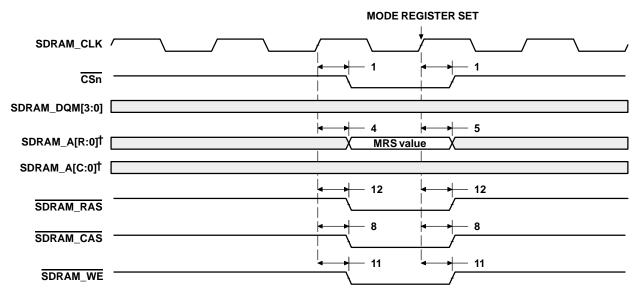

| 6–29   | SDRAM Mode Register Set Command                                     | 75   |

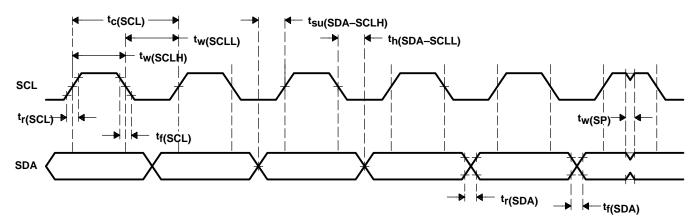

| 6–30   | Definition of Timing on the I <sup>2</sup> C Bus                    | 76   |

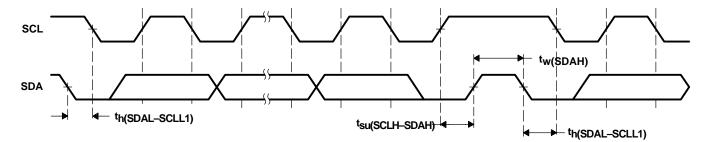

| 6–31   | I <sup>2</sup> C Bus Timings (STOP and START Conditions)            | 77   |

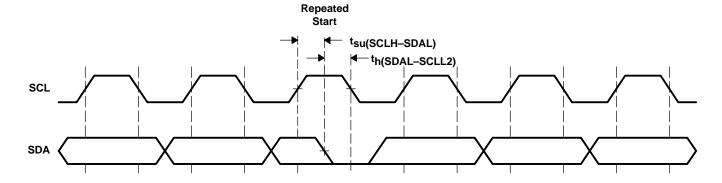

| 6–32   | I <sup>2</sup> C Bus Timings (Repeated START Condition)             | 77   |

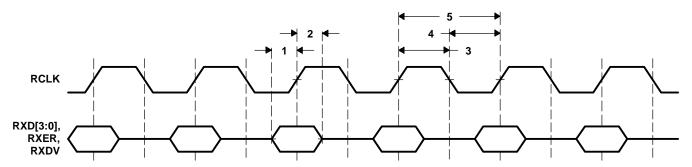

| 6–33   | MII Receive Timing                                                  | 78   |

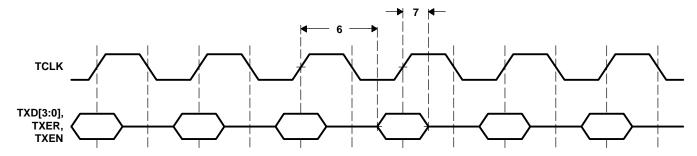

| 6–34   | MII Transmit Timing                                                 | 79   |

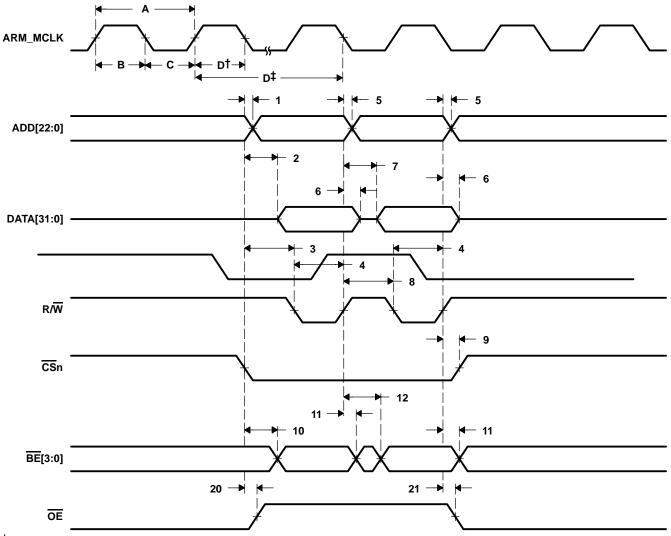

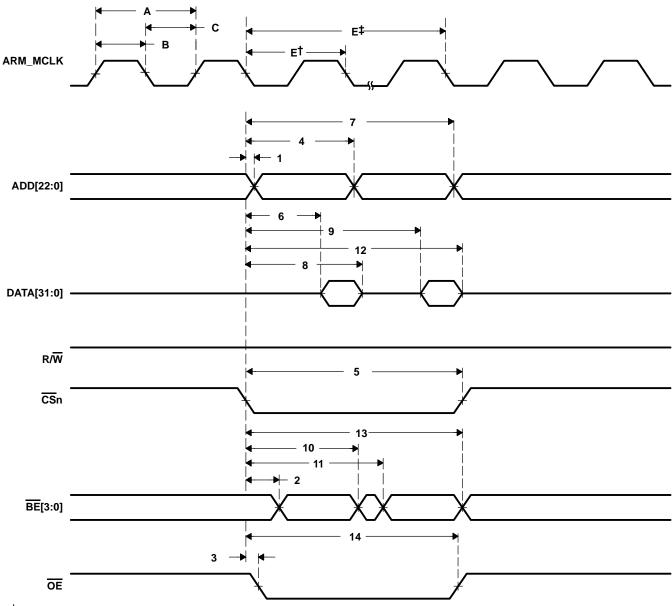

| 6–35   | ARM SRAM Write Timing                                               | 81   |

| 6–36   | ARM SRAM Read Timing                                                | 83   |

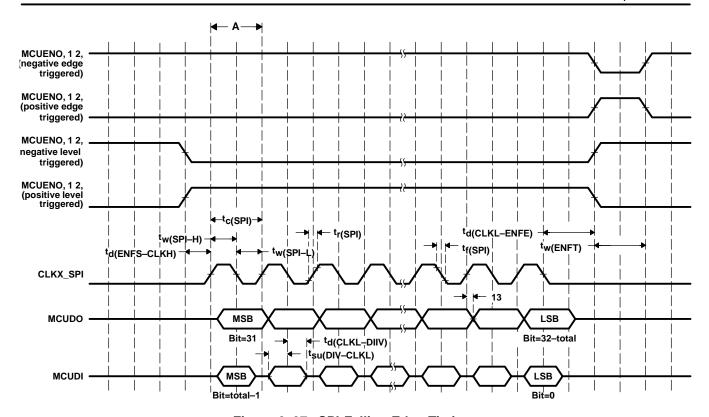

| 6–37   | SPI Falling Edge Timings                                            | 85   |

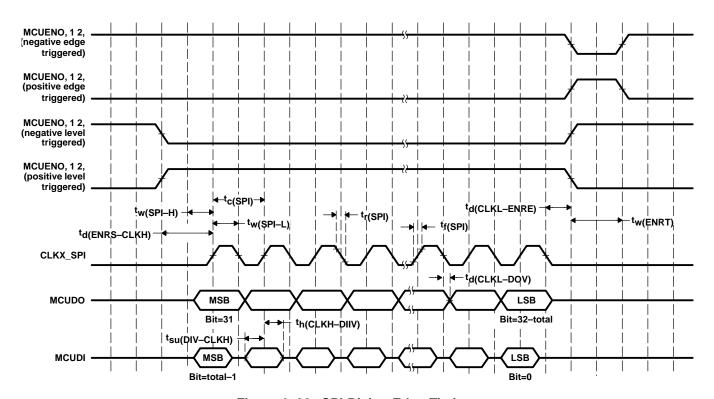

| 6–38   | SPI Rising Edge Timings                                             | 86   |

| 7_1    | TMS320VC5471 257-Ball MicroStar BGA Plastic Ball Grid Array Package | 87   |

# **List of Tables**

| Table        |                                                                                                   | Page     |

|--------------|---------------------------------------------------------------------------------------------------|----------|

| 2–1          | Pin Assignments for the GHK Package                                                               | 4        |

| 2–2          | Terminal Functions                                                                                | 7        |

| 2–3          | Internal Pullup/Pulldown Terminal List                                                            | 11       |

| 3–1          | CPU Memory-Mapped Registers                                                                       | 17       |

| 3–2          | Peripheral Memory-Mapped Registers                                                                | 18       |

| 3–3          | McBSP Control Registers and Subaddresses                                                          | 19       |

| 3–4          | Bank-Switching Control Register (BSCR) Bit Fields                                                 | 20       |

| 3–5          | Relationship Between BNKCMP and Bank Size                                                         | 21       |

| 3–6          | State of Signals When External Bus Interface is Disabled (EXIO = 1)                               | 21       |

| 3–7          | Sample Rate Generator Clock Source Selection                                                      | 22       |

| 3–8          | DMA Interrupts                                                                                    | 23       |

| 3–9          | DMA Synchronization Events                                                                        | 24       |

| 3–10         | DMA Channel Interrupt Selection                                                                   | 24       |

| 3–11         | DSP Clock Scaler Values and Minimum REFCLK Frequencies                                            | 26       |

| 3–12         | DSP Interrupt Mapping                                                                             | 27       |

| 3–13         | IFR and IMR Register Bit Fields                                                                   | 28       |

| 4–1          | MCU Memory Space                                                                                  | 30       |

| 4–2          | GPIO Control/Status Bits                                                                          | 38       |

| 4–3          | GPIO_IRQ Bits Definition                                                                          | 38       |

| 4–4          | MCU Peripheral Interrupt Mapping                                                                  | 41       |

| 4–5          | Reset Management                                                                                  | 43       |

| 4–6          | DSP Boot Memory                                                                                   | 44       |

| 4–7          | Emulation Mode Selection                                                                          | 44       |

| 4–8          | JTAG TAP Controller Instruction Register Lengths                                                  | 45       |

| 6–1          | Thermal Resistance Characteristics                                                                | 49       |

| 6–2          | Divide-By-Two/Divide-By-Four Clock Option Timing Requirements                                     | 50       |

| 6–3          | Divide-By-Two/Divide-By-Four Clock Option Switching Characteristics                               | 50       |

| 6–4          | Multiply-By-N Timing Requirements                                                                 | 51       |

| 6–5          | Multiply-By-N Switching Characteristics                                                           | 51       |

| 6–6          | Memory Read Timing Requirements                                                                   | 52       |

| 6–7          | Memory Read Switching Characteristics                                                             | 52       |

| 6–8          | Memory Write Switching Characteristics                                                            | 54       |

| 6–9          | Parallel I/O Port Read Timing Requirements                                                        | 56       |

| 6–10         | Parallel I/O Port Read Switching Characteristics                                                  | 56       |

| 6–11         | Parallel I/O Port Write Switching Characteristics                                                 | 57       |

| 6–12         | Ready Timing For Externally Generated Wait-States Timing Requirements                             | 58       |

| 6–13         | Reset and Interrupt Timing Requirements                                                           | 61       |

| 6–14         | DSP_IAQ and DSP_IACK Switching Characteristics                                                    | 62       |

| 6–15         | DSP_XF and DSP_TOUT Switching Characteristics                                                     | 63       |

| 6–16         | McBSP Receive and Transmit Timing Requirements                                                    | 64       |

| 6–17         | McBSP Receive and Transmit Switching Characteristics                                              | 65<br>67 |

| 6–18<br>6–19 | McBSP General-Purpose Timing Requirements         McBSP General-Purpose Switching Characteristics | 67<br>67 |

| 0-19         | Michail General-Lathose amirching Characteristics                                                 | 07       |

| Table |                                                                                     | Page |