# SONY

# **CXA1884N**

# Low-voltage FM IF Amplifier

#### Description

The CXA1884N is designed for FM communication devices. They incorporate a paging system, mixer, IF limiter, FM detector, operational amplifier, comparator, and others.

#### **Features**

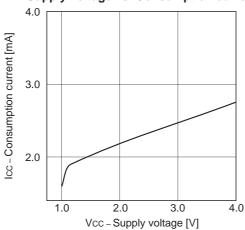

• Low operating voltage

1.0 to 4.0V

• Low power consumption

2mA at 1.5V

Built-in power source voltage monitor

# **Applications**

IF Amplifier for Paging System Receiver

#### Structure

Bipolar silicon monolithic IC

#### **Absolute Maximum Ratings** (Ta = 25°C)

Supply voltage

Vcc

7

Operating temperature Topr −20 to +75

• Storage temperature Tstg -65 to +150

#### **Recommended Operating Conditions**

Supply voltage Vcc 1.0 to 4.0 V

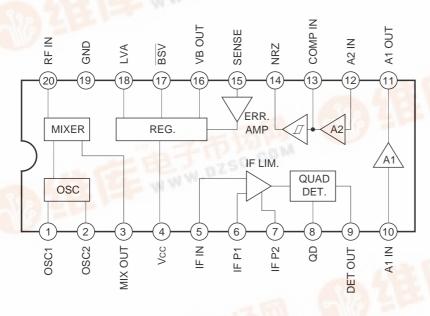

# **Block Diagram and Pin Configuration**

Note) DET.: DETECTOR

LIM.: LIMITER REG.: REGURATOR

**ERR.: ERROR CORRECTION**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

°C

°C

# **Pin Description**

| Pin<br>No. | Symbol  | Equivalent circuit   | Description                                                                                                                                     |

|------------|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | OSC1    | Vcc<br>1<br>W-<br>W- | Those pins are connected to the external parts of an oscillating circuit. The oscillator is an internally-biased Colpitts                       |

| 2          | OSC2    | GND                  | type with the collector, base, and emitter connections at Vcc, pins 1 and 2 respectively.                                                       |

| 3          | MIX OUT | 3 Vcc GND            | Mixer output pin. Connect a 455kHz ceramic filter between this pin and the IF IN pin.                                                           |

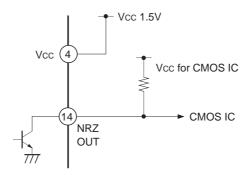

| 4          | Vcc     |                      | Vcc pin.                                                                                                                                        |

| 5          | IF IN   |                      | Input pin for the IF limiter amplifier.                                                                                                         |

| 6          | IF P1   | Vcc<br>5<br>6<br>GND | Connection pin of the bypass capacitor for the IF limiter amplifier. Connect a capacitor of about 0.047µF between this pin and ground (or Vcc). |

| 7          | IF P2   | Vcc<br>W GND         | Connection pin of the bypass capacitor for the IF limiter amplifier. Connect a capacitor of about 0.047µF between this pin and ground (or Vcc). |

| 8          | QD      | 8 Vcc GND            | Connected to a quadrature detector phase shifter.                                                                                               |

| Pin<br>No. | Symbol     | Equivalent circuit | Description                                                                                     |  |

|------------|------------|--------------------|-------------------------------------------------------------------------------------------------|--|

| 9          | DET OUT    | 9 Vcc<br>GND       | Recovered signal output.                                                                        |  |

| 10         | A1 IN      | Vcc<br>10<br>GND   | Input pin of inverting OP amplifier A1.                                                         |  |

| 11         | A1 OUT     | Vcc<br>11) W GND   | Output pin of OP amplifier A1.                                                                  |  |

| 12         | A2 IN      | Vcc<br>12<br>W GND | Input pin of OP amplifier A2.                                                                   |  |

| 13         | COMP<br>IN | Vcc<br>(13) GND    | Input pin of the comparator. This pin is internally connected to the output of OP amplifier A2. |  |

| Pin<br>No. | Symbol | Equivalent circuit                       | Description                                                                                                   |  |  |

|------------|--------|------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| 14         | NRZ    | 14 W GND                                 | NRZ (Non Return Zero) output pin.                                                                             |  |  |

| 15         | SENSE  | Vcc<br>15<br>GND                         | Voltage control pin for external bias supply.                                                                 |  |  |

| 16         | VB OUT | Vcc<br>16 W GND                          | Supplies bias voltage to external circuit transistors and others.                                             |  |  |

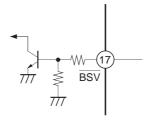

| 17         | BSV    | (17)———————————————————————————————————— | Reduces IC power consumption. Lowering pin voltage below 0.35V stops IC operation.                            |  |  |

| 18         | LVA    | (18) — W — GND                           | Output pin for Low Voltage Alarm (LVA). The pin turns to high impedance when power voltage drops below 1.05V. |  |  |

| 19         | GND    |                                          | Ground pin.                                                                                                   |  |  |

| 20         | RF IN  | Vcc Q0 GND                               | Mixer input pin.                                                                                              |  |  |

#### **Electrical Characteristics**

$(Vcc = 1.5V, Ta = 25^{\circ}C, fs = 21.7MHz, fmod = 256Hz, fdiv = 2.3kHz, AMmod = 30%)$

| Item                                      | Symbol    | Condition                       | Min. | Тур. | Max. | Unit  |

|-------------------------------------------|-----------|---------------------------------|------|------|------|-------|

| Power consumption (during operation)      | Icc       | Test circuit 1                  | 1.2  | 2.0  | 2.6  | mA    |

| Power consumption (during battery saving) | Iccs      | Test circuit 1<br>Vı = 0.3V     | _    | _    | 20   | μA    |

| Input for –3dB Limiting                   | VIN (LIM) | Test circuit 3                  | _    | 7    |      | dΒμ   |

| AM rejection ratio                        | AMRR      | VIN = 60dBµ<br>Test circuit 3   | 25   | _    | _    | dB    |

| OP amplifier input bias current           | IBIAS     | Test circuit 2                  | _    | 30   | 100  | nA    |

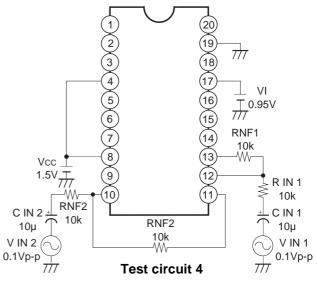

| OP amplifier open loop gain               | Av        | Test ciTcuit 4                  | 45   | 60   | _    | dB    |

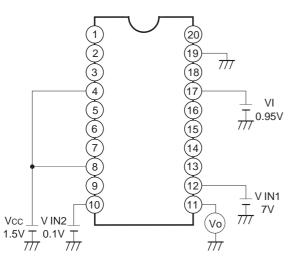

| OP amplifier output voltage amplitude     | Vo        | Test circuit 5                  | 0.25 | _    | _    | Vp-p  |

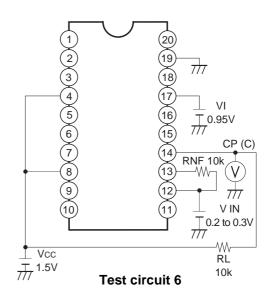

| Comparator hysteresis width               | VTW       | Test circuit 6                  | 30   | 40   | 50   | mV    |

| NRZ* output leak current                  | ILNRZ     | Test circuit 7                  | _    | _    | 5.0  | μΑ    |

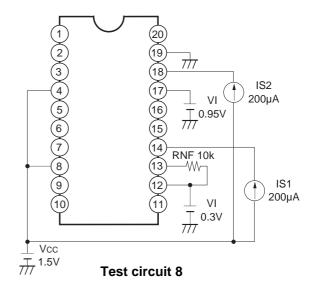

| NRZ* saturation voltage                   | VSATNRZ   | Isink = 200µA<br>Test circuit 8 | _    | _    | 0.4  | V     |

| VB output current                         | Іоит      | VB = 0.9V                       | 0.1  | _    | _    | mA    |

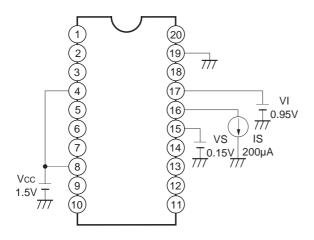

| VB output voltage                         | Vвоит     | Test circuit 9                  | 0.95 | _    | _    | V     |

| Sense voltage                             | Vsen      | Test circuit 2                  | 85   | 100  | 115  | mV    |

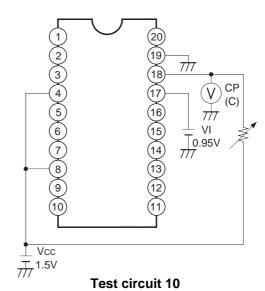

| LVA threshold voltage                     | VPML      | Test circuit 10                 | 1.00 | 1.05 | 1.10 | V     |

| LVA hysteresis width                      | VРМТН     | VPMH — VPML                     | 35   | 50   | 70   | mV    |

| LVA output leak current                   | ILLVA     | Test circuit 7                  | _    |      | 5.0  | μA    |

| LVA saturation voltage                    | VSATLVA   | Test circuit 8                  |      |      | 0.4  | V     |

| Recovered signal voltage                  | VDET      | Test circuit 3                  | 10   | _    | _    | mVrms |

| BSV high level                            | VTHBSV    |                                 | 0.95 |      |      | V     |

| BSV low level                             | VTLBSV    |                                 | _    | _    | 0.35 | V     |

<sup>\*</sup> NRZ: Non Return Zero

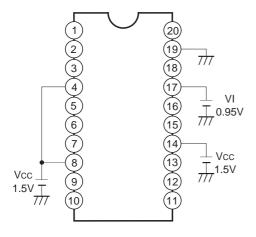

#### **Electrical Characteristics Test Circuit**

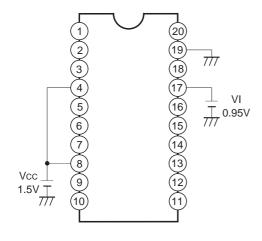

Test circuit 1

Test circuit 2

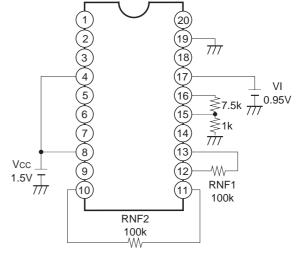

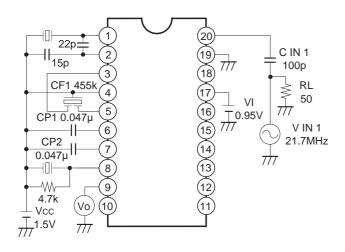

**Test circuit 3**

**Test circuit 5**

-6-

SONY

CXA1884N

Test circuit 7

Test circuit 9

#### **Test Method**

# Input for -3dB Limiting VIN (LIM)

Use test circuit 3. Apply a signal with the following characteristics to SIG IN.

Signal frequency: fs = 21.7MHz Modulation frequency: fmod = 256Hz

Frequency deviation:  $f_{DIV} = 2.3kHz$  Signal level:  $V_L = 40dB\mu$

Here, the value of Vac is specified as Vac1. Next, the signal level VL is changed to 19dBµ and Vac value is hence specified as Vac2.

$$20 \log \frac{V_{AC1}}{V_{AC2}} < 3dB$$

# AM rejection ratio (AMRR)

Use test circuit 3. Apply a signal with the following characteristics to SIG IN.

Signal frequency: fs = 21.7MHz Modulation frequency: fmod = 256Hz

Frequency deviation:  $f_{DIV} = 2.3kHz$  Signal level:  $V_L = 40dB\mu$  Here, the value of Vac is specified as Vac1. Next, AM is modified to:

Modulation ratio: AMMOD = 30% Modulation frequency: fMOD = 256Hz

and the Vac value is hence specified as Vac2.

$$AMRR = 20 \log \frac{V_{AC1}}{V_{AC2}} > 25 dB$$

#### Recovered signal voltage VDET

Use test circuit 3. Apply a signal with the following characteristics to SIG IN.

Signal frequency: fs = 21.7MHz Modulation frequency: fmod = 256Hz

Frequency deviation:  $f_{DIV} = 2.3kHz$  Signal level:  $V_L = 50dB\mu$  Here, the value of the Pin 9 output voltage is expressed as  $V_{DET}$ .

# OP amplifier output voltage amplitude Vo

Use test circuit 5. If output voltage V is expressed as  $V_1$  when  $V_{IN}$  is 0.1V, and as  $V_2$  when  $V_{IN}$  is 0.3V, it follows that:

$$Vo = V_1 - V_2$$

#### Comparator hysteresis width VTW

Use test circuit 6. Vary VIN between 0.1 to 0.3V.

Specify VIN voltage, as V1 when (C) voltage changes from low to high.

Similarly, specify V<sub>IN</sub> voltage as V<sub>2</sub>, when (C) voltage changes from high to low.

Therefore: VHY  $V_{TW} = V_1 - V_2$

#### LVA threshold voltage VPML and recovery voltage VPMH

Use test circuit 10. Vary power voltage Vcc from 1.3 to 0.95V.

Specify Vcc as VPML, when (C) voltage changes from low to high.

Similarly, specify Vcc as VPMH, when (C) voltage changes from high to low.

## **Design Reference Values**

| Item                            | Symbol     | Condition              | Min. | Тур. | Max. | Unit   |

|---------------------------------|------------|------------------------|------|------|------|--------|

| Mixer input resistance          | RIN (MIX)  |                        | 1.3  | 1.6  | 1.9  | kΩ     |

| Mixer input capacity            | CIN (MIX)  |                        | _    | 4.0  | _    | pF     |

| Mixer output resistance         | Rout (MIX) |                        | 1.44 | 1.8  | 2.16 | kΩ     |

| IF input resistance             | RIN (IF)   |                        | 1.44 | 1.8  | 2.16 | kΩ     |

| IF gain stability               | GN (IF)    | Ta = $-20$ to $+60$ °C | _    | ±6   | _    | dB     |

| Detector output resistance      | ROUT (QD)  |                        | 1.28 | 1.6  | 2.0  | kΩ     |

| OP amplifier max. input voltage | VINMAX     |                        |      |      | 0.39 | \<br>\ |

| OP amplifier min. input voltage | VINMIN     |                        | 0.05 | _    | _    | V      |

| Comparator max. input voltage   | VINMAXCOMP |                        | _    | _    | 0.39 | V      |

| Comparator min. input voltage   | VINMINCOMP |                        | 0.05 | _    | _    | V      |

| OP amplifier off-set voltage    | Vors       |                        | _    |      | 3    | mV     |

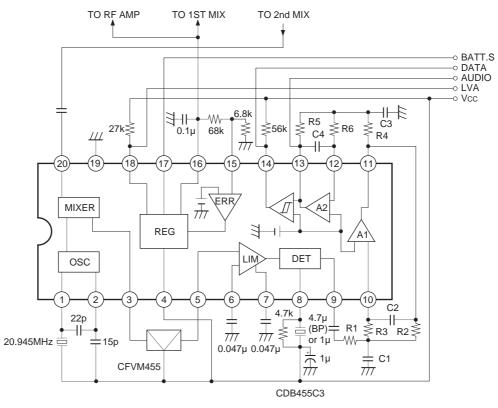

# **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### 1) Supply

This IC incorporates a regulation and is designed to operate steadily on a wide range of supply voltage from 1.0 to 4.0V.

Decoupling on the wiring to the supply pin (Pin 4) should be done as close to the pin as possible.

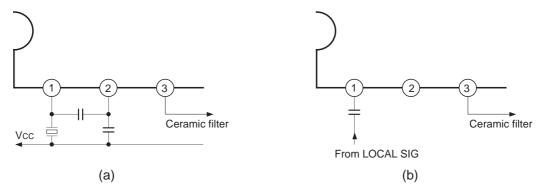

## 2) Oscillation input

Oscillation input method

- (a) Using Pins 1 and 2, input self-excited oscillation signals through the composition of a Colpitts type crystal oscillating circuit.

- (b) Input local oscillation signals to Pin 1 directly.

Fig. 1

#### 3) Mixer

This IC's mixer is of the double balance type. Pin 24 is the input pin. Input through a suitable alignment circuit. Input impedance is at  $1.6k\Omega$ . The mixer output features a built-in  $1.6k\Omega$  load resistance at Pin 3.

# 4) IF filter

The filter to be connected between this IC's mixer and the IF limiter should have the following specifications.

I/O impedance:  $1.6k\Omega \pm 10\%$

Band width: Use according to application

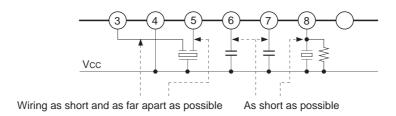

#### 5) IF limiter

The IF limiter of this IC features a gain of about 100dB. To this effect, the following points should be considered for the wiring connecting IF limiter input pin (Pin 5) and decoupling capacitor pins (Pins 6 and 7).

- (a) Wiring to mixer output (Pin 3) and IF limiter input (Pin 5) should be as short and as far apart as possible to avoid neutral interference.

- (b) Connect a decoupling capacitor to IF limiter IF P1 (Pin 6) and IF P2 (Pin 7).

Here the decoupling capacitor should be positioned as close as possible to each pin and the wiring be as short as can be.

- (c) As IF limiter output shows at QD (Pin 8), keep the wiring connected to QD pin R, L, C and the ceramic discriminator as short as possible. Interference to the mixer output, IF limiter input and others must be kept to a minimum.

Fig. 2

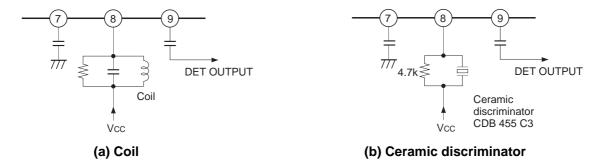

#### 6) Detector

The detector is of the quadrature type. To phase shift, either R, L, C resonance circuit or the ceramic discriminator is connected to Pin 8.

The phase capacitor of the quadrature detector is built-in. FM (FSK) signals demodulated by this detector have their high frequency components dropped by the LPF formed inside from CRs, to be output at DET OUT (Pin 9). DET OUT output impedance is about  $3k\Omega$ .

For the CXA1884N ceramic discriminator, CDB 455 C3 (Murata Production) is recommended.

Fig. 3

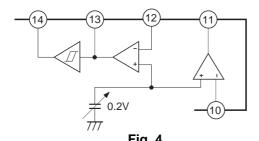

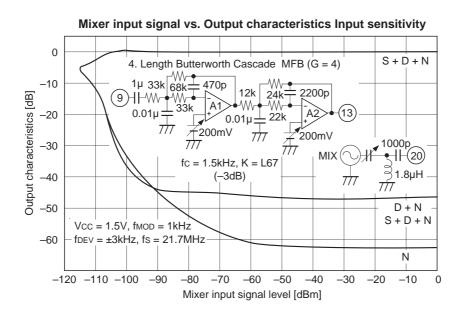

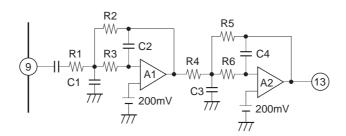

#### 7) OP AMP, NRZ OUT

This IC has 2 built-in operation amplifiers.

One of these operation amplifiers is connected inside the IC to NRZ comparator.

Making use of these operation amplifiers an LPF or the sort is made up to eliminate noise during signal demodulation and input to the following NRZ comparator.

NRZ comparator molds the waveform of input signals to output them as square waves. NRZ comparator output is an open collector.

Accordingly as CPU is a CMOS, in case the supply voltage differs, by following the method indicated in Fig. 5 direct interfacing becomes possible.

Fig. 5

#### 8) VB SENSE, VB OUT

This controls the base bias of the external transistor. Pin 16 VB OUT can be used as the previous amplifier 1st mixer bias.

#### 9) LVA OUT

When supply voltage turns low this pin turns to High (Open). Output is an open collector, and similarly as NRX OUT, can directly drive CMOS.

This LVA setting voltage is at 1.05V ± 50mV with hysterisis versus supply voltage.

Hysterisis width is at 50mV ± 10mV.

# 10) BSV

By turning this pin to low, this IC's operation can be stopped.

This pin can also be directly connected to CMOS.

Consumption current with BSV is 20µA (at 1.5V) and below.

Fig. 6

# 4th LP Butterworth cascade MFB constant using OP1 and OP2 inside CXA1884N

| fмор      | 256Hz   |  |  |

|-----------|---------|--|--|

| fc (-3dB) | 400Hz   |  |  |

| A1 Gain   | 1       |  |  |

| A2 Gain   | 4       |  |  |

| R1        | 47kΩ    |  |  |

| R2        | 47kΩ    |  |  |

| R3        | 22kΩ    |  |  |

| R4        | 47kΩ    |  |  |

| R5        | 180kΩ   |  |  |

| R6        | 33kΩ    |  |  |

| C1        | 0.012µF |  |  |

| C2        | 680pF   |  |  |

| C3        | 0.015µF |  |  |

| C4        | 1200pF  |  |  |

Supply voltage vs. Consumption current

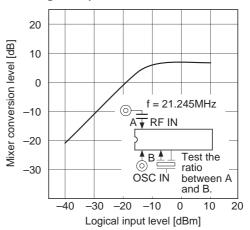

Logical input level vs. Mixer conversion

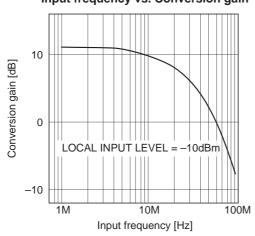

Input frequency vs. Conversion gain

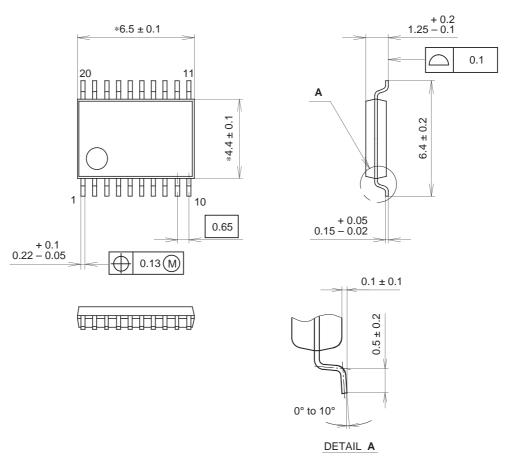

# Package Outline Unit: mm

# 20PIN SSOP (PLASTIC)

NOTE: Dimension "\*" does not include mold protrusion.

#### PACKAGE STRUCTURE

|            |                | PACKAGE MATERIAL | EPOXY RESIN                   |

|------------|----------------|------------------|-------------------------------|

| SONY CODE  | SSOP-20P-L01   | LEAD TREATMENT   | SOLDER / PALLADIUM<br>PLATING |

| EIAJ CODE  | SSOP020-P-0044 | LEAD MATERIAL    | 42/COPPER ALLOY               |

| JEDEC CODE |                | PACKAGE MASS     | 0.1g                          |

**NOTE: PALLADIUM PLATING**

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).