## **DSPI**

# Serial Peripheral Interface – Master/Slave ver 2.07

#### OVERVIEW

The DSPI is a fully configurable SPI master/slave device, which allows user to configure polarity and phase of serial clock signal SCK.

The DSPI allows the microcontroller to communicate with serial peripheral devices. It is also capable of interprocessor communications in a multi-master system. A serial clock line (SCK) synchronizes shifting and sampling of the information on the two independent serial data lines. DSPI data are simultaneously transmitted and received.

The DSPI is a technology independent design that can be implemented in a variety of process technologies.

The DSPI system is flexible enough to interface directly with numerous standard product peripherals from several manufacturers. The system can be configured as a master or a slave device. Data rates as high as CLK/4. Clock control logic allows a selection of clock polarity and a choice of two fundamentally different clocking protocols to accommodate most available synchronous serial peripheral devices. When the SPI is configured as a master, software selects one of eight different bit rates for the serial clock.

The DSPI automatically drive selected by SSCR (Slave Select Control Register) slave select outputs (SS7O – SS0O), and address SPI slave device to exchange serially shifted data. Error-detection logic is included to support interprocessor communications. A write-collision detector indicates when an attempt is

made to write data to the serial shift register while a transfer is in progress. A multiple-master mode-fault detector automatically disables DSPI output drivers if more than one SPI devices simultaneously attempts to become bus master.

DSPI is **fully customizable**, which means it is delivered in the exact configuration to meet users' requirements. There is no need to pay extra for not used features and wasted silicon. It includes **fully automated testbench** with **complete set of tests** allowing easy package validation at each stage of SoC design flow.

#### APPLICATIONS

- Embedded microprocessor boards

- Consumer and professional audio/video

- Home and automotive radio

- Digital multimeters

#### **KEY FEATURES**

- SPI Master

- Master and Multi-master operations

- o 8 SPI slave select lines

- System error detection

- Mode fault error

- Write collision error

- Interrupt generation

- Supports speeds up 1/4 of system clock

All trademarks mentioned in this document are trademarks of their respective owners.

http://www.DigitalCoreDesign.com http://www.dcd.pl

## 查询 **Bit spice Tell spice T**

- Four transfer formats supported

- Simple interface allows easy connection to microcontrollers

- SPI Slave

- Slave operation

- System error detection

- o Interrupt generation

- Supports speeds up ¼ of system clock

- Simple interface allows easy connection to microcontrollers

- Four transfer formats supported

- Fully synthesizable, static synchronous design with no internal tri-states

#### **DELIVERABLES**

- Source code:

- ♦ VHDL Source Code or/and

- VERILOG Source Code or/and

- ♦ Encrypted, or plain text EDIF netlist

- VHDL & VERILOG test bench environment

- Active-HDL automatic simulation macros

- ModelSim automatic simulation macros

- ♦ Tests with reference responses

- Technical documentation

- Installation notes

- ♦ HDL core specification

- ⋄ Datasheet

- Synthesis scripts

- Example application

- Technical support

- ♦ IP Core implementation support

- ♦ 3 months maintenance

- Delivery the IP Core updates, minor and major versions changes

- Delivery the documentation updates

- Phone & email support

#### LICENSING

Comprehensible and clearly defined licensing methods without royalty fees make using of IP Core easy and simply.

<u>Single Design</u> license allows use IP Core in single FPGA bitstream and ASIC implementation.

<u>Unlimited Designs</u>, <u>One Year</u> licenses allow use IP Core in unlimited number of FPGA bitstreams and ASIC implementations.

In all cases number of IP Core instantiations within a design, and number of manufactured chips are unlimited. There is no time restriction except <u>One Year</u> license where time of use is limited to 12 months.

- Single Design license for

- VHDL, Verilog source code called <u>HDL</u> Source

- Encrypted, or plain text EDIF called <u>Netlist</u>

- One Year license for

- Encrypted Netlist only

- Unlimited Designs license for

- HDL Source

- Netlist

- Upgrade from

- HDL Source to Netlist

- Single Design to Unlimited Designs

### 查询"DSPI"供**感育 M B O L**

#### PINS DESCRIPTION

| PIN        | TYPE   | DESCRIPTION               |  |

|------------|--------|---------------------------|--|

| clk        | input  | Global clock              |  |

| rst        | input  | Global reset              |  |

| datai(7:0) | input  | Data bus input            |  |

| addr(1:0)  | input  | Processor address lines   |  |

| cs         | input  | Chip select               |  |

| rd         | input  | Processor read strobe     |  |

| we         | input  | Processor write strobe    |  |

| scki       | input  | SPI clock input           |  |

| mi         | input  | Master serial data input  |  |

| si         | input  | Slave serial data input   |  |

| ss         | input  | Slave select              |  |

| datao(7:0) | output | Data bus output           |  |

| irq        | output | Interrupt request         |  |

| scko       | output | SPI clock output          |  |

| sckz       | output | SPI clock output enable   |  |

| mo         | output | Master serial data output |  |

| so         | output | Slave serial data output  |  |

| ss7o-ss0o  | output | Slave select outputs      |  |

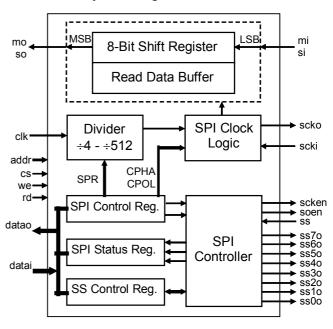

#### **BLOCK DIAGRAM**

Shift register and Read Data Buffer - it is a central element in the SPI system. The system is single buffered in the transmit direction and double buffered in the receive direction. This fact means new data for transmission cannot be written to the shifter until the previous transaction is complete; however, received data is transferred into a parallel read data buffer so the shifter is free to accept a second serial character. As long as the first character is read out of the read data buffer before the next serial character is ready to be transferred, no overrun condition will occur. When an SPI transfer occurs, an 8-bit character is shifted out on data pin while a different 8-bit character is simultaneously shifted in a second data pin. Another way to view this transfer is that an 8-bit shift register in the master and another 8-bit shift register in the slave are connected as a circular 16-bit shift register. When a transfer occurs, this distributed shift register is shifted eight bit positions; thus, the characters in the master and slave are effectively exchanged.

**Control Register** may be read or written at any time, is used to configure the DSPI System. This register controls the mode of transmission (Master, Slave), polarity and phase of SPI Clock and transmission speed.

**Status Register** (SPSR) is read only register contains flags indicating the completion of transfer or occurrence of system errors. All

http://www.DigitalCoreDesign.com http://www.dcd.pl fier and cleared by software sequence.

Slave Select Control Register configures which slave select output should be driven while SPI master transfer. Contents of SSCR register is automatically assigned on SS70-SS00 pins when DSPI master transmission starts.

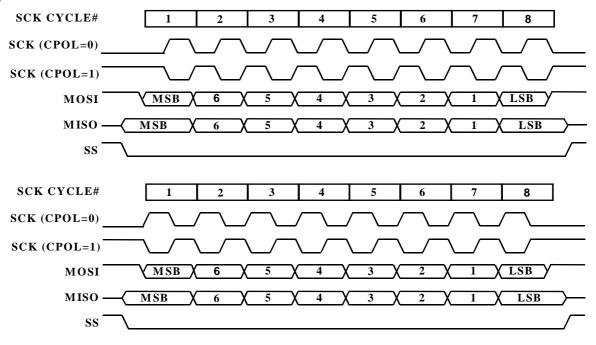

SPI Clock Logic - Software can select any of four combinations of serial clock (SCK) phase and polarity using two bits in the SPI control register (SPCR). The clock polarity is specified by the CPOL control bit, which selects an active high or active low clock and has no significant effect on the transfer format. The clock phase (CPHA) control bit selects one of two fundamentally different transfer formats. The clock phase and polarity should be identical for the master SPI device and the communicating slave device. In some cases, the phase and polarity are changed between transfers to allow a master device to communicate with peripheral slaves having different requirements. The flexibility of the SPI system on the DSPI allows direct interface to almost any existing synchronous serial peripheral.

**SPI Controller** manages the Master/Slave operation and controls the transmission. The SPI Controller manages the transmission speed and format (Phase and polarity). Controller is also responsible for generating of interrupt request and detection of transmission errors.

#### PERFORMANCE

The following table gives a survey about the Core performance in the ALTERA® devices after Place & Route (all key features have been included):

| Device    | Speed grade | Logic Cells | F <sub>max</sub> |

|-----------|-------------|-------------|------------------|

| CYCLONE   | -6          | 181         | 303 MHz          |

| CYCLONE2  | -6          | 172         | 310 MHz          |

| STRATIX   | -5          | 181         | 320 MHz          |

| STRATIX2  | -3          | 151         | 387 MHz          |

| STRATIXGX | -5          | 181         | 307 MHz          |

| APEX2A    | -7          | 196         | 244 MHz          |

| APEX20KC  | -7          | 196         | 211 MHz          |

| APEX20KE  | -1          | 196         | 169 MHz          |

| APEX20K   | -1          | 196         | 135 MHz          |

| ACEX1K    | -1          | 205         | 156 MHz          |

| FLEX10KE  | -1          | 205         | 156 MHz          |

| MAX2      | -3          | 181         | 209 MHz          |

| MAX3K     | -5          | 119         | 96 MHz           |

| MAX7K     | -5          | 119         | 96 MHz           |

Core performance in ALTERA® devices

#### 查询"DSPI"供应商

#### **Transfer Formats**

Software can select any of four combinations of serial clock (SCK) phase and polarity using two bits in the SPI control register (SPCR). The clock polarity is specified by the CPOL control bit, which selects an active high or active low clock and has no significant effect on the transfer format. The clock phase (CPHA) control bit selects one of two fundamentally different transfer formats. The clock phase and polarity should be identical for the master SPI device and the communicating slave device. In some cases, the phase and polarity are changed between transfers to allow a master device to communicate with peripheral slaves having different requirements. The flexibility of the SPI system on the DSPI allows direct interface to almost any existing synchronous serial peripheral.

## 查询"DSPI"**供应**和 TACTS

For any modification or special request please contact to Digital Core Design or local distributors.

#### **Headquarters:**

Wroclawska 94

41-902 Bytom, POLAND

e-mail: info@dcd.pl

tel. : +48 32 282 82 66 fax : +48 32 282 74 37

#### **Distributors:**

Please check http://www.dcd.pl/apartn.php