## LP3952 6-Channel Color LED Driver with Audio Synchronization

## **General Description**

f.dzsc.com

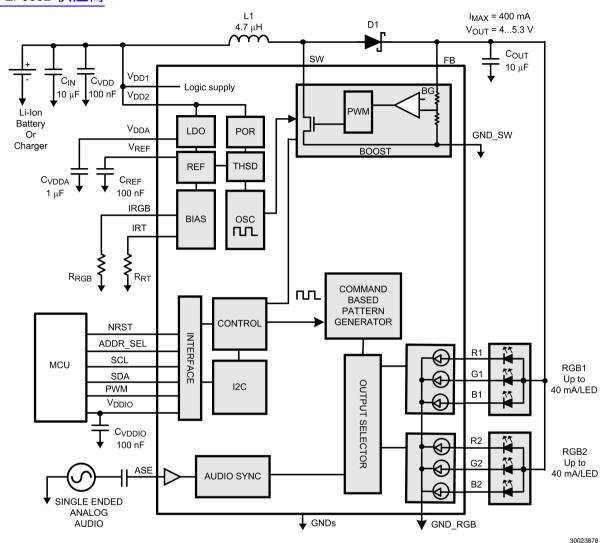

LP3952 is a color LED driver for battery powered handheld devices. It drives any color LEDs including RGB LEDs, indicator LEDs and keypad backlight LEDs. The boost DC-DC converter drives high current loads with high efficiency. The stand-alone command based RGB controller is feature rich and easy to configure. Different lighting patterns and blinking sequences can be programmed to driver registers. Built-in audio synchronization feature allows user to synchronize the color LEDs to audio signal. LED lighting can be controlled either by audio signal amplitude or frequency. There are many controls available for audio synchronization to get desired lighting effect, including gain, speed, and different filter settings. The flexible I<sup>2</sup>C interface allows easy control of LP3952. LED outputs can be also controlled with external PWM signal. Small micro SMDxt package together with minimum number of external components is a best fit for handheld devices.

#### Features

- Constant current and PWM controlled color LED drivers

- Maximum current 40mA / output in constant current mode, supports also switch mode control with 50 mA maximum current / output

- Complete audio synchronization for color/RGB LEDs with amplitude, frequency and speed optimization

- Command based lighting pattern generator for RGB LEDs

- Programmable ON/OFF blinking sequences for RGB1 outputs

- High efficiency Boost DC-DC converter with programmable V<sub>OUT</sub>and f<sub>SW</sub>

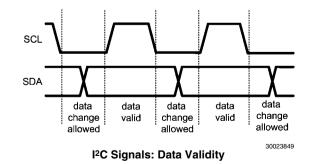

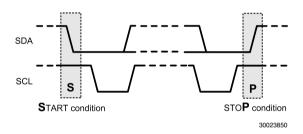

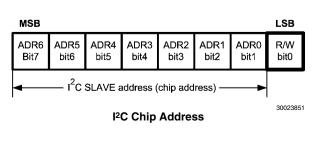

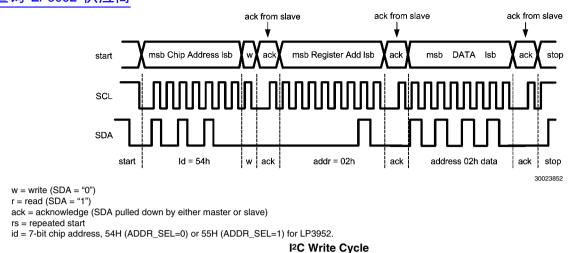

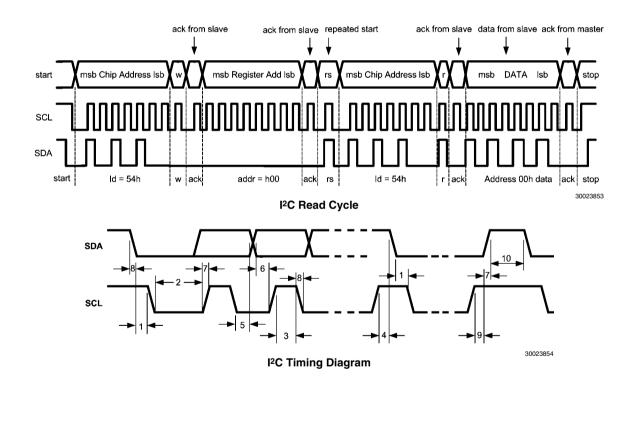

- I<sup>2</sup>C compatible interface

- Possibility for external PWM dimming control

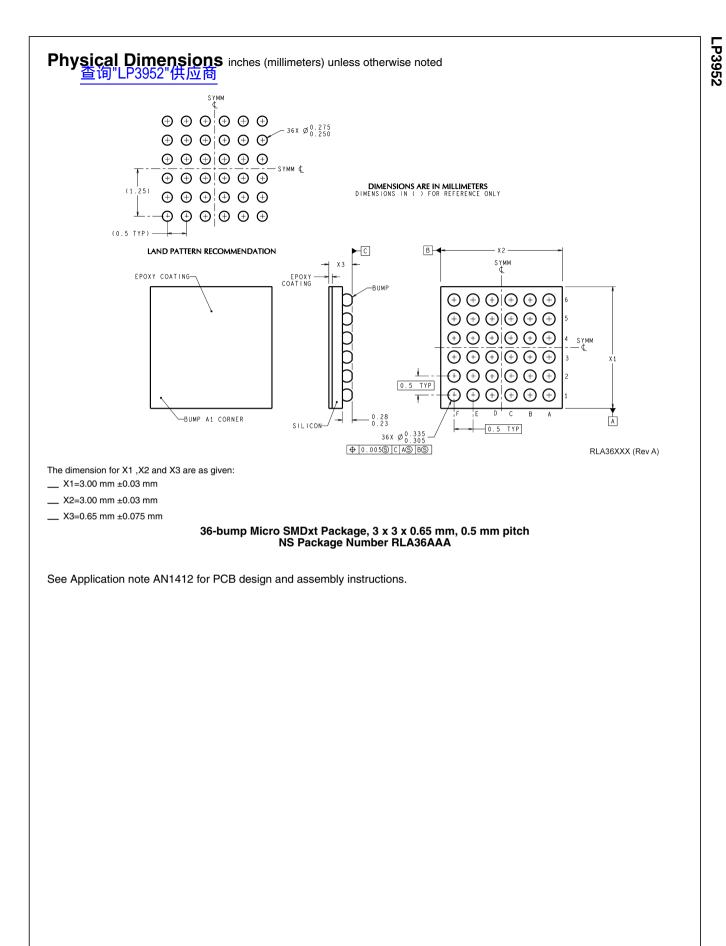

- Small package 36-bump micro SMDxt, 3.0 x 3.0 x 0.65 mm

## Applications

- Cellular Phones

- PDAs, MP3 players

Julv 2007

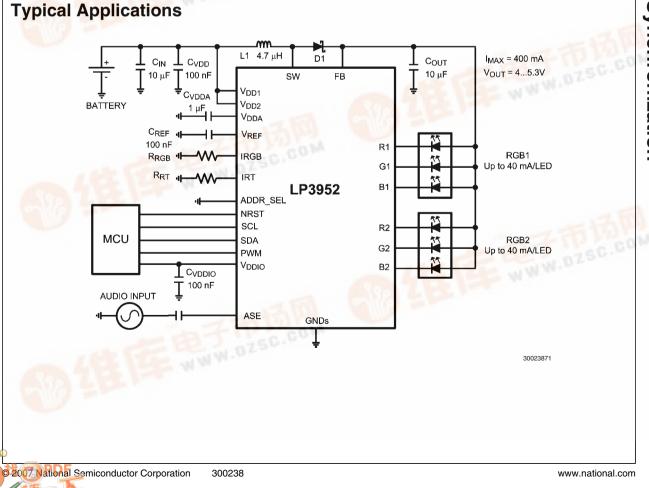

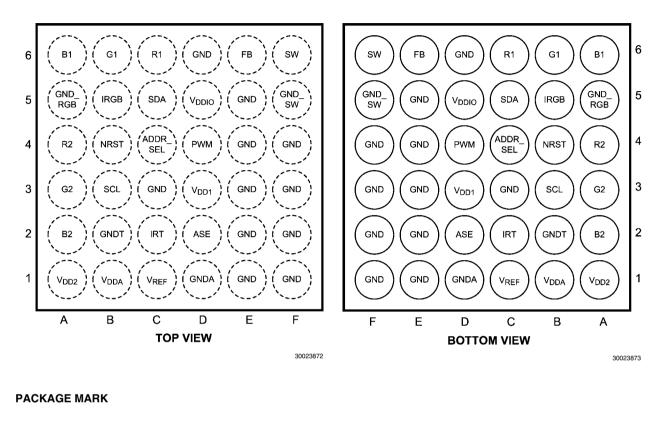

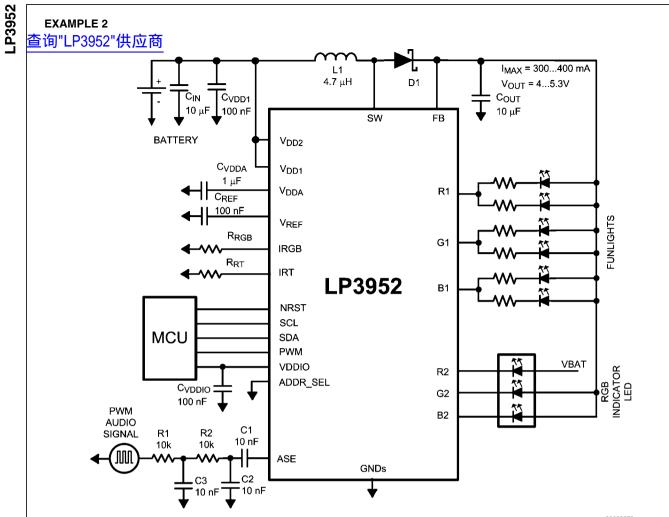

#### Connection Diagrams and Package Mark Information 查询"LP3952"供应商 CONNECTION DIAGRAMS

36-bump Micro SMDxt Package, 3.0 x 3.0 x 0.65 mm, 0.5 mm pitch NS Package Number RLA36AAA

## **Ordering Information**

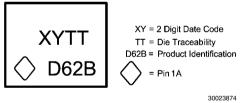

| Order Number | Package Marking | Supplied As | Spec/Flow |  |

|--------------|-----------------|-------------|-----------|--|

| LP3952RL     | D62B            | TNR 250     | NoPb      |  |

| LP3952RLX    | D62B            | TNR 1000    | NoPb      |  |

| Pin # | escriptions<br>词"LP3952"供<br>Name | Туре               | Description                                                |

|-------|-----------------------------------|--------------------|------------------------------------------------------------|

| 6F    | SW                                | Output             | Boost Converter Power Switch                               |

| 6E    | FB                                | Input              | Boost Converter Feedback                                   |

| 6D    | GND                               | Ground             | Ground                                                     |

| 6C    | R1                                | Output             | Red LED 1 Output                                           |

| 6B    | G1                                | Output             | Green LED 1 Output                                         |

| 6A    | B1                                | Output             | Blue LED 1 Output                                          |

| 5F    | GND_SW                            | Ground             | Power Switch Ground                                        |

| 5E    | GND                               | Ground             | Ground                                                     |

| 5D    | V <sub>DDIO</sub>                 | Power              | Supply Voltage for Logic Input/Output Buffers and Drivers  |

| 5C    | SDA                               | Logic Input/Output | Serial Data In/Out (I <sup>2</sup> C)                      |

| 5B    | IRGB                              | Input              | Bias Current Set Resistor for RGB Drivers                  |

| 5A    | GND_RGB                           | Ground             | Ground for RGB Currents                                    |

| 4F    | GND                               | Ground             | Ground                                                     |

| 4E    | GND                               | Ground             | Ground                                                     |

| 4D    | PWM                               | Logic Input        | External PWM Control for LEDs. Connect to GND if not used. |

| 4C    | ADDR_SEL                          | Logic Input        | Address Select (I <sup>2</sup> C)                          |

| 4B    | NRST                              | Logic Input        | Reset Pin                                                  |

| 4A    | R2                                | Output             | Red LED 2 Output                                           |

| 3F    | GND                               | Ground             | Ground                                                     |

| 3E    | GND                               | Ground             | Ground                                                     |

| 3D    | V <sub>DD1</sub>                  | Power              | Supply Voltage                                             |

| 3C    | GND                               | Ground             | Ground                                                     |

| 3B    | SCL                               | Logic Input        | Clock (I <sup>2</sup> C)                                   |

| 3A    | G2                                | Output             | Green LED 2 Output                                         |

| 2F    | GND                               | Ground             | Ground                                                     |

| 2E    | GND                               | Ground             | Ground                                                     |

| 2D    | ASE                               | Input              | Audio Synchronization Input                                |

| 2C    | IRT                               | Input              | Oscillator Frequency Resistor                              |

| 2B    | GNDT                              | Ground             | Ground                                                     |

| 2A    | B2                                | Output             | Blue LED 2 Output                                          |

| 1F    | GND                               | Ground             | Ground                                                     |

| 1E    | GND                               | Ground             | Ground                                                     |

| 1D    | GNDA                              | Ground             | Ground for Analog Circuitry                                |

| 1C    | VREF                              | Output             | Reference Voltage                                          |

| 1B    | V <sub>DDA</sub>                  | Power              | Internal LDO Output                                        |

| 1A    | V <sub>DD2</sub>                  | Power              | Supply Voltage                                             |

Absolute Maximum Ratings (Notes 1, 2) If ## P3952 ## Notes In Multiary Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| V (SW, FB, R1-2, G1-2, B1-2)<br>(Notes 3, 4)                               | -0.3V to +7.2V                                    |

|----------------------------------------------------------------------------|---------------------------------------------------|

| V <sub>DD1</sub> , V <sub>DD2</sub> , V <sub>DDIO</sub> , V <sub>DDA</sub> | -0.3V to +6.0V                                    |

| Voltage on ASE, IRT, IRGB, VREF                                            | -0.3V to V <sub>DD1</sub> +0.3V<br>with 6.0V max  |

| Voltage on Logic Pins                                                      | -0.3V to V <sub>DDIO</sub> +0.3V<br>with 6.0V max |

| V(all other pins): Voltage to GND                                          | -0.3V to 6.0V                                     |

| I (V <sub>REF</sub> )                                                      | 10 µA                                             |

| I(R1, G1, B1, R2, G2, B2)                                                  | 100 mA                                            |

| Continuous Power Dissipation (Note 5)                                      | Internally Limited                                |

| Junction Temperature (T <sub>J-MAX</sub> )                                 | 150°C                                             |

| Storage Temperature Range                                                  | -65°C to +150°C                                   |

| Maximum Lead Temperature<br>(Soldering) (Note 6)<br>ESD Rating (Note 7)    | 260°C                                             |

| Human Body Model:                                                          | 2 kV                                              |

### **Operating Ratings** (Notes 1, 2)

|                                                      | , ,                       |

|------------------------------------------------------|---------------------------|

| V (SW, FB, R1-2, G1-2, B1-2)                         | 0 to 6.0V                 |

| $V_{DD1,2}$ with external LDO                        | 2.7 to 5.5V               |

| V <sub>DD1,2</sub> with internal LDO                 | 3.0 to 5.5V               |

| V <sub>DDA</sub>                                     | 2.7 to 2.9V               |

| V <sub>DDIO</sub>                                    | 1.65V to V <sub>DD1</sub> |

| Voltage on ASE                                       | 0.1V to $V_{DDA}$ –0.1V   |

| Recommended Load Current                             | 0 to 300 mA               |

| Junction Temperature (T <sub>J</sub> ) Range         | -30°C to +125°C           |

| Ambient Temperature (T <sub>A</sub> ) Range (Note 8) | -30°C to +85°C            |

|                                                      |                           |

### **Thermal Properties**

Junction-to-Ambient Thermal Resistance( $\theta_{JA}$ ), RLA36AAA Package (Note 9)

60°C/W

#### Electical Characteristics (Notes 2, 10)

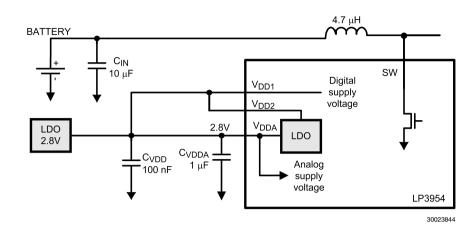

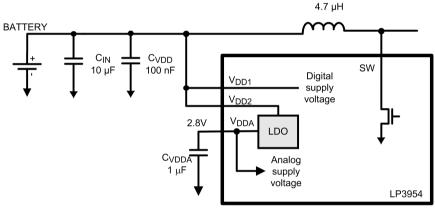

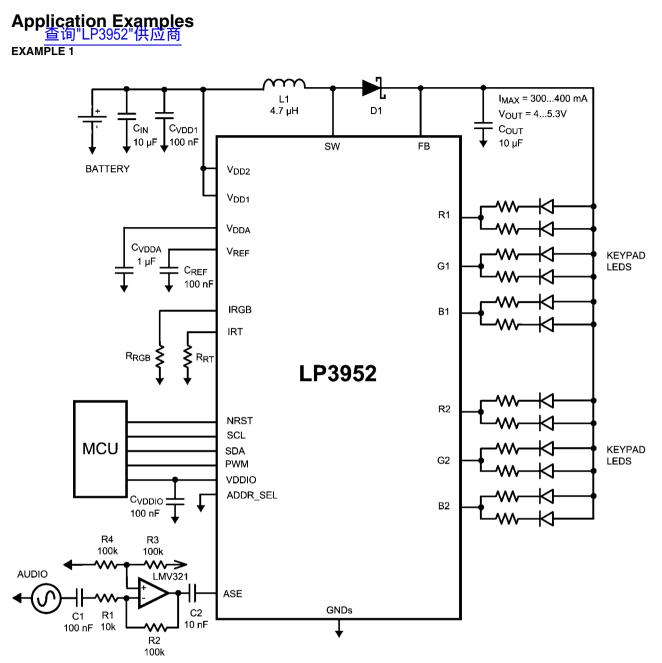

Limits in standard typeface are for  $T_J = 25^{\circ}$ C. Limits in **boldface** type apply over the operating ambient temperature range (-30°C <  $T_A < +85^{\circ}$ C). Unless otherwise noted, specifications apply to the LP3952 Block Diagram with:  $V_{DD1} = V_{DD2} = 3.6$ V,  $V_{DDIO} = 2.8$ V,  $C_{VDDD} = C_{VDDIO} = 100$  nF,  $C_{OUT} = C_{IN} = 10$  µF,  $C_{VDDA} = 1$  µF,  $C_{REF} = 100$  nF,  $L_1 = 4.7$  µH,  $R_{RGB} = 5.6$  k $\Omega$  and  $R_{RT} = 82$  k $\Omega$  (Note 11)

| Symbol             | Parameter                        | Condition                                         | Min  | Тур  | Max  | Units |

|--------------------|----------------------------------|---------------------------------------------------|------|------|------|-------|

| I <sub>VDD</sub>   | Standby supply current           | NSTBY (bit) = L, NRST (pin) = H                   |      | 1    | 8    | μA    |

|                    | $(V_{DD1} + V_{DD2})$            | SCL=H, SDA = H                                    |      |      |      | -     |

|                    | No-boost supply current          | NSTBY (bit) = H,                                  |      |      | 450  | μA    |

|                    | $(V_{DD1} + V_{DD2})$            | EN_BOOST(bit) = L                                 |      |      |      |       |

|                    |                                  | SCL = H, SDA = H                                  |      |      |      |       |

|                    |                                  | Audio sync and LEDs OFF                           |      |      |      |       |

|                    | No-load supply current           | NSTBY (bit) = H,                                  |      |      | 1    | mA    |

|                    | $(V_{DD1} + V_{DD2})$            | EN_BOOST (bit) = H                                |      |      |      |       |

|                    |                                  | SCL = H, SDA = H                                  |      |      |      |       |

|                    |                                  | Audio sync and LEDs OFF                           |      |      |      |       |

|                    |                                  | Autoload OFF                                      | _    |      |      |       |

|                    | RGB drivers                      | CC mode at R1, G1, B1 and R2, G2, B2 set to 15 mA |      | 150  |      | μA    |

|                    | $(V_{DD1} + V_{DD2})$            | SW mode                                           |      | 150  |      |       |

| $I_{VDD}$          | Audio synchronization            | Audio sync ON                                     |      |      |      |       |

|                    | $(V_{DD1} + V_{DD2})$            | $V_{DD1,2} = 2.8V$                                |      | 390  |      | μA    |

|                    |                                  | $V_{DD1,2} = 3.6V$                                |      | 700  |      |       |

| I <sub>VDDIO</sub> | V <sub>DDIO</sub> Standby Supply | NSTBY (bit)=L                                     |      |      | 1    | μA    |

|                    | current                          | SCL = H, SDA = H                                  |      |      |      | -     |

| IEXT LDO           | External LDO output              | 7V tolerant application only                      |      |      | 6.5  | mA    |

| 0                  | current                          | I <sub>BOOST</sub> = 300 mA                       |      |      |      |       |

|                    | $(V_{DD1}, V_{DD2}, V_{DDA})$    |                                                   |      |      |      |       |

| V <sub>DDA</sub>   | Output voltage of internal       | (Note 12)                                         | 2.72 | 2.80 | 2.88 | V     |

|                    | LDO for analog parts             |                                                   | -3   |      | +3   | %     |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pins.

Note 3: Battery/Charger voltage should be above 6V no more than 10% of the operational lifetime.

**Note 4:** Voltage tolerance of LP3952 above 6.0V relies on fact that  $V_{DD1}$  and  $V_{DD2}$  (2.8V) are available (ON) at all conditions. If  $V_{DD1}$  and  $V_{DD2}$  are not available (ON) at all conditions, National Semiconductor does not guarantee any parameters or reliability for this device.

Note 5: Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J=160^{\circ}C$  (typ.) and disengages at  $T_J=140^{\circ}C$  (typ.).

Note 6: For detailed soldering specifications and information, please refer to National Semiconductor Application Note AN1412 : Micro SMDxt Wafer Level Chip Scale Package

Note 7: The Human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin.

**Note 8:** In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A-MAX})$  is dependent on the maximum operating junction temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ , the maximum power dissipation of the device in the application  $(P_{D-MAX})$ , and the junction-to ambient thermal resistance of the part/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

Note 9: Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

Note 10: Min and Max limits are guaranteed by design, test, or statistical analysis. Typical numbers are not guaranteed, but do represent the most likely norm. Note 11: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics.

Note 12: V<sub>DDA</sub> output is not recommended for external use.

#### **Block Diagram** 查询"LP3952"供应商

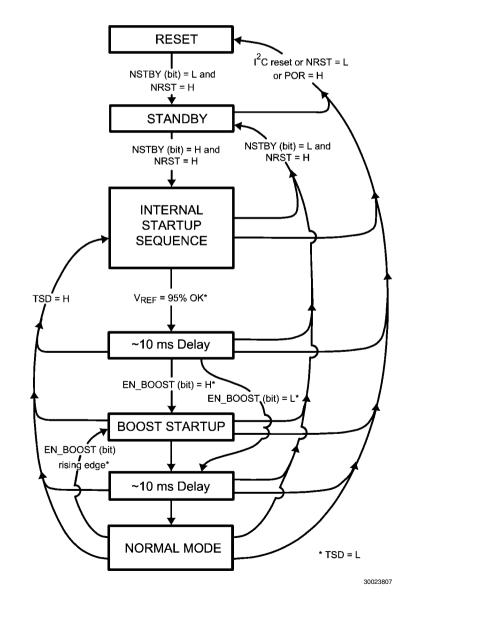

#### Modes of Operation 查询"LP3952"供应商

RESET: In the RESET mode all the internal registers are reset to the default values and the chip goes to STANDBY mode after reset. NSTBY control bit is low after reset by default. Reset is active always if NRST input pin is low or internal Power On Reset is active. LP3952 can be also reset by writing any data to Reset Register in address 60H. Power On Reset (POR) will activate during the chip startup or when the supply voltage V<sub>DD2</sub> falls below 1.5V. Once V<sub>DD2</sub> rises above 1.5V, POR will inactivate and the chip will continue to the STANDBY mode.

**STANDBY:** The STANDBY mode is entered if the register bit NSTBY is LOW. This is the low power consumption mode, when all circuit functions are disabled. Registers can be written in this mode and the control bits are effective immediately after power up.

**STARTUP:** When NSTBY bit is written high, the INTERNAL STARTUP SEQUENCE powers up all the needed internal blocks (Vref, Bias, Oscillator etc..). To ensure the correct oscillator initialization, a 10 ms delay is generated by the internal state-machine. If the chip temperature rises too high, the Thermal Shutdown (TSD) disables the chip operation and STARTUP mode is entered until no thermal shutdown event is present.

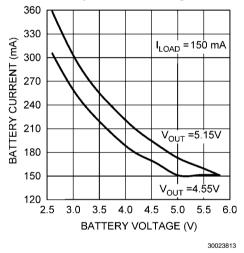

**BOOST STARTUP:** Soft start for boost output is generated in the BOOST STARTUP mode. The boost output is raised in PFM mode during the 10 ms delay generated by the state-machine. The Boost startup is entered from Internal Startup Sequence if EN\_BOOST is HIGH or from Normal mode when EN\_BOOST is written HIGH. During the 10 ms Boost Startup time all LED outputs are switched off to ensure smooth start-up.

**NORMAL:** During NORMAL mode the user controls the chip using the Control Registers. The registers can be written in any sequence and any number of bits can be altered in a register in one write

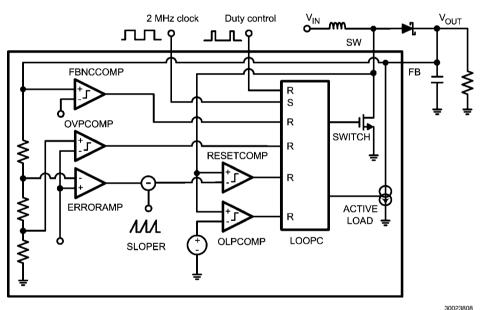

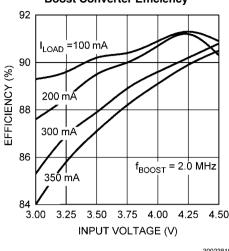

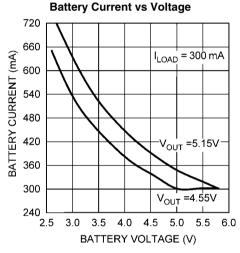

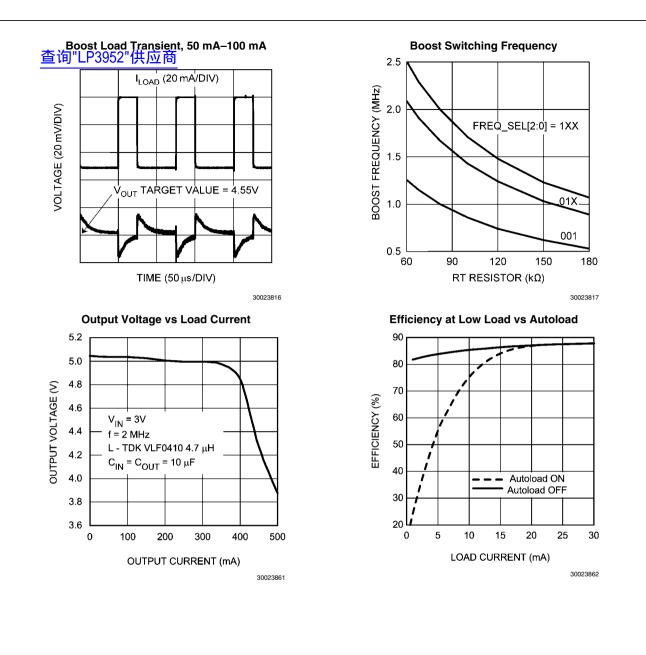

## Magnetic Boost DC/DC Converter

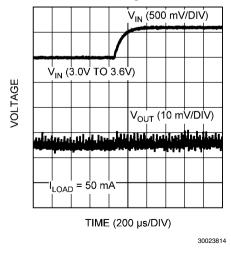

**The LP3952 Boost BCD**C Converter generates a 4.0 – 5.3V voltage for the LEDs from single Li-lon battery (3V...4.5V). The output voltage is controlled with an 8-bit register in 9 steps. The converter is a magnetic switching PWM mode DC/DC converter with a current limit. The converter has three options for switching frequency, 1 MHz, 1.67 MHz and 2 MHz (default), when timing resistor RT is 82 kΩ. Timing resistor defines the internal oscillator frequency and thus directly affects boost frequency and all circuit's internally generated timing (RGB patterns).

The LP3952 Boost Converter uses pulse-skipping elimination to stabilize the noise spectrum. Even with light load or no load a minimum length current pulse is fed to the inductor. An active load is used to remove the excess charge from the output capacitor at very light loads. At very light load and when input and output voltages are very close to each other, the pulse skipping is not completely eliminated. Output voltage should be at least 0.5V higher than input voltage to avoid pulse skipping. Reducing the switching frequency will also reduce the required voltage difference.

Active load can be disabled with the en\_autoload bit. Disabling will increase the efficiency at light loads, but the downside is that pulse skipping will occur. The Boost Converter should be stopped when there is no load to minimise the current consumption. The topology of the magnetic boost converter is called CPM control, current programmed mode, where the inductor current is measured and controlled with the feedback. The user can program the output voltage of the boost converter. The output voltage control changes the resistor divider in the feedback loop.

The following figure shows the boost topology with the protection circuitry. Four different protection schemes are implemented:

- 1. Over voltage protection, limits the maximum output voltage

- Keeps the output below breakdown voltage.

- Prevents boost operation if battery voltage is much higher than desired output.

- 2. Over current protection, limits the maximum inductor current

- Voltage over switching NMOS is monitored; too high voltages turn the switch off.

- 3. Feedback break protection. Prevents uncontrolled operation if FB pin gets disconnected.

- 4. Duty cycle limiting, done with digital control.

**Boost Converter Topology**

| Symbol               | Parameter                           | Conditions                                                                                    | Min               | Тур                                      | Max               | Units |

|----------------------|-------------------------------------|-----------------------------------------------------------------------------------------------|-------------------|------------------------------------------|-------------------|-------|

| I <sub>LOAD</sub>    | Load Current                        | $3.0V \le V_{IN}$<br>$V_{OUT} = 5V$                                                           | 0                 |                                          | 300               |       |

|                      |                                     | $3.0V \le V_{IN}$<br>$V_{OUT} = 4V$                                                           | 0                 |                                          | 400               | mA    |

| V <sub>OUT</sub>     | Output Voltage Accuracy<br>(FB Pin) | $3.0V \le V_{IN} \le V_{OUT} - 0.5$<br>$V_{OUT} = 5.0V$                                       | -5                |                                          | +5                | %     |

|                      | Output Voltage<br>(FB Pin)          | 1 mA $\leq$ I <sub>LOAD</sub> $\leq$ 300 mA<br>V <sub>IN</sub> > 5V + V <sub>(SCHOTTKY)</sub> |                   | V <sub>IN</sub> -V <sub>(SCHOTTKY)</sub> |                   | v     |

| RDS <sub>ON</sub>    | Switch ON Resistance                | V <sub>DD1,2</sub> = 2.8V, I <sub>SW</sub> = 0.5A                                             |                   | 0.4                                      | 0.8               | Ω     |

| f <sub>boost</sub>   | PWM Mode Switching<br>Frequency     | RT = 82 kΩ<br>freq_sel[2:0] = 1XX                                                             |                   | 2                                        |                   | MHz   |

|                      | Frequency Accuracy                  | 2.7 ≤ VDDA ≤ 2.9<br>RT = 82 kΩ                                                                | -6<br><b>-9</b>   | ±3                                       | +6<br><b>+9</b>   | %     |

| t <sub>PULSE</sub>   | Switch Pulse Minimum<br>Width       | no load                                                                                       |                   | 25                                       |                   | ns    |

| t <sub>STARTUP</sub> | Startup Time                        | Boost startup from STANDBY                                                                    |                   | 10                                       |                   | ms    |

| I <sub>SW_MAX</sub>  | SW Pin Current Limit                |                                                                                               | 700<br><b>550</b> | 800                                      | 900<br><b>950</b> | mA    |

#### BOOST STANDBY MODE

User can stop the Boost Converter operation by writing the Enables register bit EN\_BOOST low. When EN\_BOOST is written high, the converter starts for 10 ms in PFM mode and then goes to PWM mode.

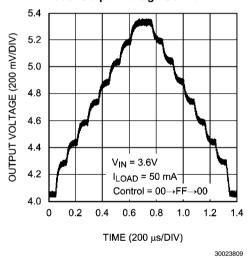

#### BOOST OUTPUT VOLTAGE CONTROL

User can control the boost output voltage by boost output 8bit register.

| Boost Ou<br>Regist | tput [7:0]<br>er 0DH | Boost Output<br>Voltage (typical) |

|--------------------|----------------------|-----------------------------------|

| Bin                | Hex                  |                                   |

| 0000 0000          | 00                   | 4.00                              |

| 0000 0001          | 01                   | 4.25                              |

| 0000 0011          | 03                   | 4.40                              |

| 0000 0111          | 07                   | 4.55                              |

| 0000 1111          | 0F                   | 4.70                              |

| 0001 1111          | 1F                   | 4.85                              |

| 0011 1111          | 3F                   | 5.00 Default                      |

| 0111 1111          | 7F                   | 5.15                              |

| 1111 1111          | FF                   | 5.30                              |

Boost Output Voltage Control

#### BOOST FREQUENCY CONTROL

| freq_sel[2:0] | frequency |

|---------------|-----------|

| 1XX           | 2.00 MHz  |

| 01X           | 1.67 MHz  |

| 001           | 1.00 MHz  |

Register 'boost freq' (address 0EH). Register default value after reset is 07H.

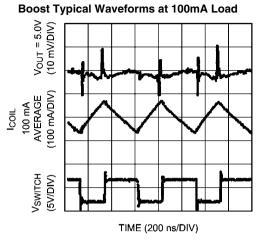

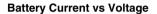

# Boost Converter Typical Performance Characteristics 查询"L<u>83853"供应商</u>if not otherwise stated

30023812

30023811

**Boost Startup with No Load**

www.national.com

## Functionality of Color LED Outputs (R1, G1, B1; R2, G2, B2)

3 outputs and the sets can be controlled in 4 different ways:

- 1. Command based pattern generator control (internal PWM)

- 2. Audio synchronization control

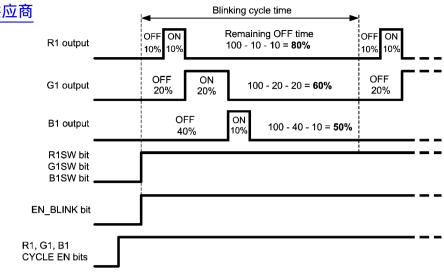

- 3. Programmable ON/OFF blinking sequences for RGB1

- 4. External PWM control

By using **command based pattern generator** user can program any kind of color effect patterns. LED intensity, blinking cycles and slopes are independently controlled with 8 16-bit commands. Also real time commands are possible as well as loops and step by step control. If analog audio is available on system, the user can use **audio synchronization** for synchronizing LED blinking to the music. The different modes together with the various sub modes generate very colorful and interesting lighting effects. **Direct ON/OFF** control is mainly for switching on and off LEDs. **External PWM control** is for applications where external PWM signal is available and required to control the color LEDs. PWM signal can be connected to any color LED separately as shown later.

#### COLOR LED CONTROL MODE SELECTION

The RGB\_SEL[1:0] bits in the Enables register (08H) control the output modes for RGB1 (R1, G1, B1) and RGB2 (R2, G2, B2) outputs as seen in the following table.

| RGB_SEL<br>[1:0] | Audio sync  | Pattern generator | Blinking<br>control |

|------------------|-------------|-------------------|---------------------|

| 00               | -           | RGB1 & RGB2       | -                   |

| 01               | -           | RGB2              | RGB1                |

| 10               | RGB2        | RGB1              | -                   |

| 11               | RGB1 & RGB2 | -                 | -                   |

**RGB Control register** (00H) has control bits for direct on/off control of all color LEDs. Note that the LEDs have to be turned on in order to control them with audio synchronization or pattern generator.

The external PWM signal can control any LED depending on the control register setup. External PWM signal is connected to PWM pin. The controls are in the Ext. PWM Control register (address 07H):

| Ext. PWM Control (07H) |       |                        |  |

|------------------------|-------|------------------------|--|

| r1_pwm                 | bit 5 | PWM controls R1 output |  |

| g1_pwm                 | bit 4 | PWM controls G1 output |  |

| b1_pwm                 | bit 3 | PWM controls B1 output |  |

| r2_pwm                 | bit 2 | PWM controls R2 output |  |

| g2_pwm                 | bit 1 | PWM controls G2 output |  |

| b2_pwm                 | bit 0 | PWM controls B2 output |  |

**Note:** Maximum external PWM frequency is 1kHz. If during the external PWM control the internal PWM is on, the result will be product of both functions.

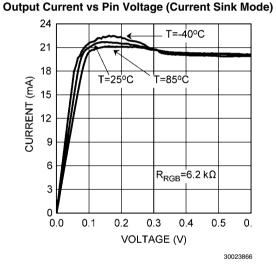

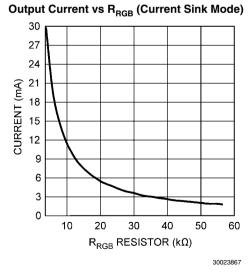

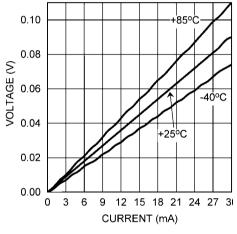

## CURRENT CONTROL OF COLOR LED OUTPUTS (R1, R2, G1, G2, B1, B2)

Both RGB output sets can be separately controlled as constant current sinks or as switches. This is done using cc\_rgb1/2 bits in the RGB control register. In constant current mode one or both RGB output sets are controlled with constant current sinks (no external ballast resistors required). The maximum output current for both drivers is set by one external resistor  $R_{RGB}$ . User can decrease the maximum current for an individual LED driver by programming as shown later.

The maximum current for all RGB drivers is set with  ${\rm R}_{\rm RGB}.$  The equation for calculating the maximum current is

$$I_{MAX} = 100 \times 1.23 V / (R_{RGB} + 50 \Omega)$$

where

${\rm I}_{\rm MAX}$  - maximum RGB current in any RGB output in constant current mode

1.23V - reference voltage

100 - internal current mirror multiplier

R<sub>RGB</sub>- resistor value in Ohms

$50\Omega$  - internal resistor in the  $I_{RGB}$  input

For example if 22mA is required for maximum RGB current  $\mathrm{R}_{\mathrm{RGB}}$  equals to

R<sub>RGB</sub>=100×1.23V / I<sub>MAX</sub>-50Ω=123V / 0.022A-50Ω**=5.54kΩ**

Each individual RGB output has a separate maximum current programming. The control bits are in registers **RGB1 max** current and **RGB2 max current** (12H and 13H) and programming is shown in table below. The default value after reset is 00b.

| IR1[1:0], IG1[1:0],<br>IB1[1:0], IR2[1:0],<br>IG2[1:0], IB2[1:0] | Maximum<br>current/output |

|------------------------------------------------------------------|---------------------------|

| 00                                                               | $0.25 	imes I_{MAX}$      |

| 01                                                               | $0.50 	imes I_{MAX}$      |

| 10                                                               | $0.75 	imes I_{MAX}$      |

| 11                                                               | $1.00 	imes I_{MAX}$      |

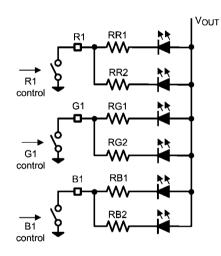

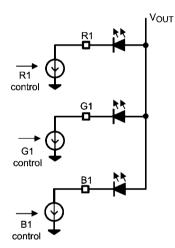

#### SWITCH MODE

The switch mode is used if there is a need to connect parallel LEDs to output or if the RGB output current needs to be increased.

Please note that the switch mode **requires an external ballast resistors** at each output to limit the LED current.

The switch/current mode and on/off controls for RGB are in the RGB\_ctrl register (00H).

## 查询"L<u>P3952"供应商</u>

#### RGB\_ctrl register (00H)

| 13332   |      |   |                                                                              |  |  |  |

|---------|------|---|------------------------------------------------------------------------------|--|--|--|

| CC RGB1 | bit7 | 1 | R1, G1 and B1 are switches $\rightarrow$ limit current with ballast resistor |  |  |  |

|         | DIL7 | 0 | R1, G1 and B1 are constant current sinks, current limited internally         |  |  |  |

| CC RGB2 | bit6 | 1 | R2, G2 and B2 are switches $\rightarrow$ limit current with ballast resistor |  |  |  |

|         | DILO | 0 | R2, G2 and B2 are constant current sinks, current limited internally         |  |  |  |

| r1sw    | bit5 | 1 | R1 is on                                                                     |  |  |  |

| TISW    | DILD | 0 | R1 is off                                                                    |  |  |  |

| g1sw    | bit4 | 1 | G1 is on                                                                     |  |  |  |

| gisw    | 0114 | 0 | G1 is off                                                                    |  |  |  |

| b1sw    | bit3 | 1 | B1 is on                                                                     |  |  |  |

| DISW    |      | 0 | B1 is off                                                                    |  |  |  |

| r2sw    | bit2 | 1 | R2 is on                                                                     |  |  |  |

| 12500   | UILZ | 0 | R2 is off                                                                    |  |  |  |

| g2sw    | bit1 | 1 | G2 is on                                                                     |  |  |  |

| 925W    |      | 0 | G2 is off                                                                    |  |  |  |

| b2sw    | bit0 | 1 | B2 is on                                                                     |  |  |  |

| 523W    | DILU | 0 | B2 is off                                                                    |  |  |  |

RGB1 output as switch (SW)

RGB1 output as a constant current sink (CC)

30023818

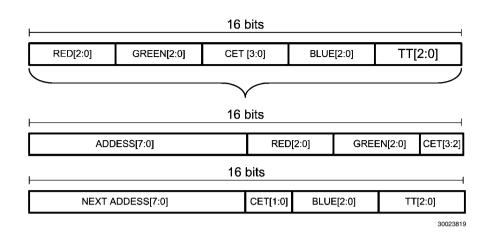

#### Command Based Pattern Generator for Color LEDs 间"LP3952"供应商

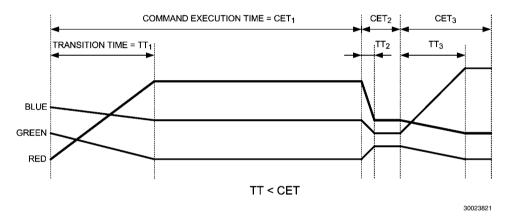

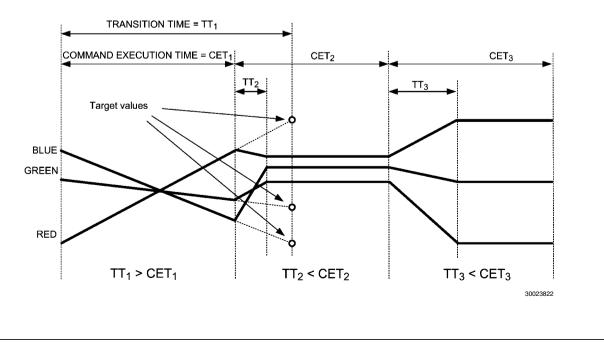

The LP3952 has an unique stand-alone command based pattern generator with 8 user controllable 16-bit commands. Since registers are 8-bit long one command requires 2 write cycles. Each command has intensity level for each LED, command execution time (CET) and transition time (TT) as seen in the following figures.

#### **COMMAND REGISTER WITH 8 COMMANDS**

| COMMAND 1 | ADDRESS 50H | R2   | R1   | R0 | G2 | G1 | G0  | CET3 | CET2 |

|-----------|-------------|------|------|----|----|----|-----|------|------|

|           | ADDRESS 51H | CET1 | CET0 | B2 | B1 | B0 | TT2 | TT1  | TT0  |

| COMMAND 2 | ADDRESS 52H | R2   | R1   | R0 | G2 | G1 | G0  | CET3 | CET2 |

|           | ADDRESS 53H | CET1 | CET0 | B2 | B1 | B0 | TT2 | TT1  | TT0  |

| COMMAND 3 | ADDRESS 54H | R2   | R1   | R0 | G2 | G1 | G0  | CET3 | CET2 |

|           | ADDRESS 55H | CET1 | CET0 | B2 | B1 | B0 | TT2 | TT1  | TT0  |

| COMMAND 4 | ADDRESS 56H | R2   | R1   | R0 | G2 | G1 | G0  | CET3 | CET2 |

|           | ADDRESS 57H | CET1 | CET0 | B2 | B1 | B0 | TT2 | TT1  | TT0  |

| COMMAND 5 | ADDRESS 58H | R2   | R1   | R0 | G2 | G1 | G0  | CET3 | CET2 |

|           | ADDRESS 59H | CET1 | CET0 | B2 | B1 | B0 | TT2 | TT1  | TT0  |

| COMMAND 6 | ADDRESS 5AH | R2   | R1   | R0 | G2 | G1 | G0  | CET3 | CET2 |

|           | ADDRESS 5BH | CET1 | CET0 | B2 | B1 | B0 | TT2 | TT1  | TT0  |

| COMMAND 7 | ADDRESS 5CH | R2   | R1   | R0 | G2 | G1 | G0  | CET3 | CET2 |

|           | ADDRESS 5DH | CET1 | CET0 | B2 | B1 | B0 | TT2 | TT1  | TT0  |

| COMMAND 8 | ADDRESS 5EH | R2   | R1   | R0 | G2 | G1 | G0  | CET3 | CET2 |

|           | ADDRESS 5FH | CET1 | CET0 | B2 | B1 | B0 | TT2 | TT1  | TT0  |

#### COLOR INTENSITY CONTROL

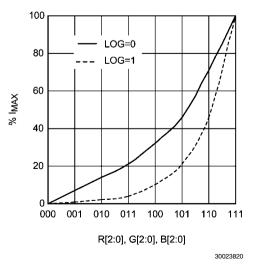

Each color has 3-bit intensity level. Level control is logarithmic, 2 curves are selectable. The LOG bit in register 11H defines the curve used as seen in the following table.

| R[2:0], G[2:0], | CURRENT                        |       |  |

|-----------------|--------------------------------|-------|--|

| B[2:0]          | [% × I <sub>MAX(COLOR)</sub> ] |       |  |

|                 | LOG=0                          | LOG=1 |  |

| 000             | 0                              | 0     |  |

| 001             | 7                              | 1     |  |

| 010             | 14                             | 2     |  |

| 011             | 21                             | 4     |  |

| 100             | 32                             | 10    |  |

| 101             | 46                             | 21    |  |

| 110             | 71                             | 46    |  |

| 111             | 100                            | 100   |  |

#### COMMAND EXECUTION TIME (CET) AND TRANSITION TIME (TT)

The command execution times are defined as follows, when  $R_T=82k\Omega$ :

| CET [3:0] | CET duration, ms |

|-----------|------------------|

| 0000      | 197              |

| 0001      | 393              |

| 0010      | 590              |

| 0011      | 786              |

| 0100      | 983              |

| 0101      | 1180             |

| 0110      | 1376             |

| 0111      | 1573             |

| 1000      | 1769             |

| 1001      | 1966             |

| 1010      | 2163             |

| 1011      | 2359             |

| 1100      | 2556             |

| 1101      | 2753             |

| CET [3:0] | CET duration, ms |

|-----------|------------------|

| 1110      | 2949             |

| 1111      | 3146             |

Transition time TT is duration of transition from the previous RGB value to programmed new value. Transition times are defined as follows:

| TT [2:0] | Transition time, ms |

|----------|---------------------|

| 000      | 0                   |

| 001      | 55                  |

| 010      | 110                 |

| 011      | 221                 |

| 100      | 442                 |

| 101      | 885                 |

| 110      | 1770                |

| 111      | 3539                |

The figure below shows an example of RGB CET and TT times.

The command execution time also may be less than the transition time - the figure below illuminates this case.

# -P3952

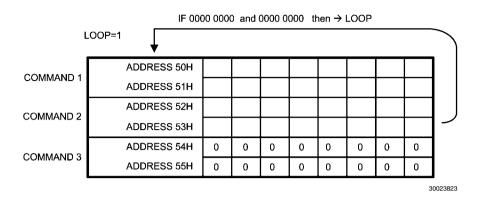

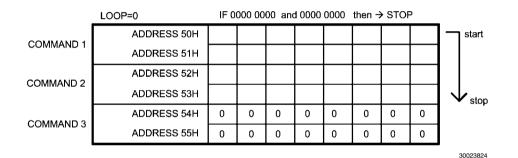

### LOOP CONTROL

#### SINGLE PROGRAM

If control bit LOOP=0 the program will start from Command 1 and run to either last command or to empty "0000 0000 / 0000 0000" command.

The LEDs maintain the brightness of the last command when the single program stops. Changes in command register will not be effective in this phase. The RGB\_START bit has to be toggled off and on to make changes effective.

#### START BIT

Pattern\_gen\_ctrl register's RGB\_START bit will enable command execution starting from Command 1.

| Pattern gen ctrl register (11H) |       |                                                            |  |  |

|---------------------------------|-------|------------------------------------------------------------|--|--|

| rgb start Bit 2                 |       | 0 – Pattern generator disabled                             |  |  |

| Typ_start                       | DIL Z | 1 – execution pattern starting from command 1              |  |  |

| loop                            | Bit 1 | 0 – pattern generator loop disabled (single pattern)       |  |  |

| юор                             |       | 1 – pattern generator loop enabled (execute until stopped) |  |  |

| log Bit 0                       |       | 0 – color intensity mode 0                                 |  |  |

|                                 |       | 1 – color intensity mode 1                                 |  |  |

## Audio Synchronization

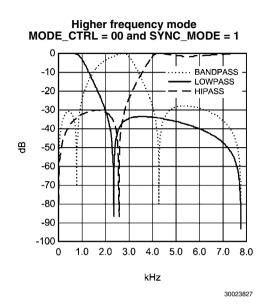

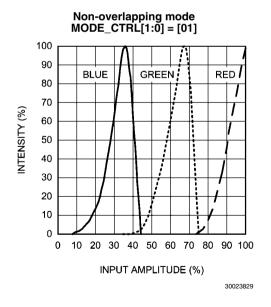

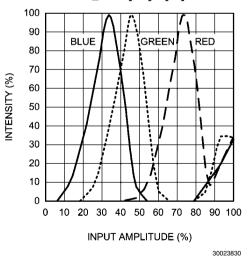

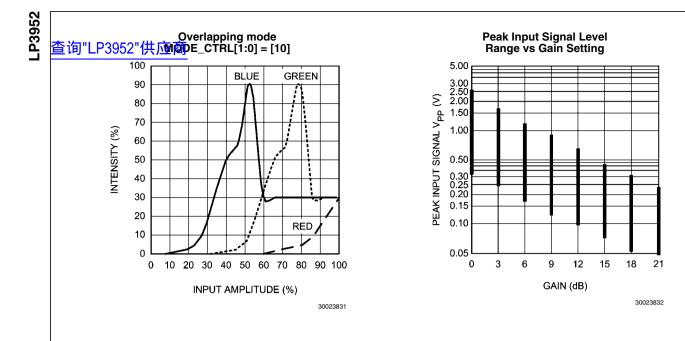

The contract of the synchronization feature. Audio Sync has 2 modes. **Amplitude mode** synchronizes color LEDs based on input signal's peak amplitude. In the amplitude mode the user can select between 3 different amplitude mapping modes and 4 different speed configurations. The **frequency mode** synchronizes the color LEDs based on bass, middle and treble amplitudes (= low pass, band pass and high pass filters). User can select between 2 different frequency responses and 4 different speed configurations for best audio-visual user experience. Programmable gain and AGC function are also available for adjustment of input signal amplitude to light response. The Audio Sync functionality is described more closely below.

## USING A DIGITAL PWM AUDIO SIGNAL AS AN AUDIO SYNCHRONIZATION SOURCE

If the input signal is a PWM signal, use a first or second order low pass filter to convert the digital PWM audio signal into an analog waveform. There are two parameters that need to be known to get the filter to work successfully: frequency of the PWM signal and the voltage level of the PWM signal. Suggested cut-off frequency (-3 dB) should be around 2 kHz to 4 kHz and the stop-band attenuation at sampling frequency should be around -48 dB or better. Use a resistor divider to reduce the digital signal amplitude to meet the specification of the analog audio input. Because a low-order low-pass filter attenuates the high-frequency components from audio signal, MODE\_CTRL=01b selection is recommended when frequency synchronization mode is enabled. Application example 5 shows an example of a second order RC-filter for 29 kHz PWM signal with 3.3V amplitude. Active filters, such as a Sallen-Key filter, may also be applied. An active filter gives better stop-band attenuation and cut-off frequency can be higher than for a RC-filter.

To make sure that the filter rolls off sufficiently quickly, connect your filter circuit to the audio input(s), turn on the audio synchronization feature, set manual gain to maximum, apply the PWM signal to the filter input and keep an eye on LEDs. If they are blinking without an audio signal (modulation), a sharper roll-off after the cut-off frequency, more stop-band attenuation, or smaller amplitude of the PWM signal is required.

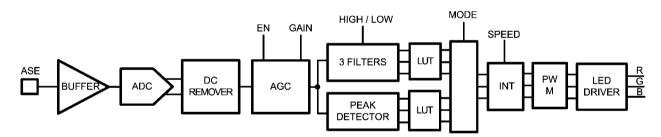

#### AUDIO SYNCHRONIZATION SIGNAL PATH

LP3952 audio synchronization is mainly done digitally and it consists of the following signal path blocks:

- Input Buffers

- AD Converter

- DC Remover

- Automatic Gain Control (AGC)

- Programmable Gain

- 3 Band Digital Filter

- Peak Detector

- Look-up Tables (LUT)

- Mode Selector

- Integrators

- PWM Generator

- Output Drivers

The digitized input signal has DC component that is removed by digital DC REMOVER (-3 dB @ 400 Hz). Since the light response of input audio signal is very much amplitude dependent the AGC adjusts the input signal to suitable range automatically. User can disable AGC and the gain can be set manually with PROGRAMMABLE GAIN. LP3952 has 2 audio synchronization modes: amplitude and frequency. For amplitude based synchronization the PEAK DETECTION method is used. For frequency based synchronization **3** BAND FILTER separates high pass, low pass and band bass signals. For both modes the predefined LUT is used to optimize the audio visual effect. MODE SELECTOR selects the synchronization mode. Different response times to music beat can be selected using INTEGRATOR speed variables. Finally PWM GENERATOR sets the driver FET duty cycles.

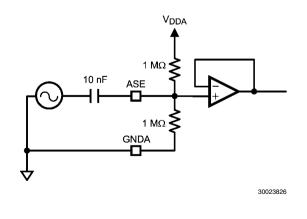

#### INPUT SIGNAL TYPE AND BUFFERING

LP3952 supports single ended audio input as shown in the figure below. The electric parameters of the buffer are de-

scribed in the Audio Synch table. The buffer is rail-to-rail input operational amplifier connected as a voltage follower. DC level of the input signal is set by a simple resistor divider

30023825

##

| Symbol           | Parameter                     | Conditions   | Min | Typical     | Мах                   | Units |

|------------------|-------------------------------|--------------|-----|-------------|-----------------------|-------|

| Z <sub>IN</sub>  | Input Impedance of ASE        |              | 250 | 500         |                       | kΩ    |

| A <sub>IN</sub>  | Audio Input Level Range       | Gain = 21 dB | 0.1 |             |                       | V     |

|                  | (peak-to-peak)                | Gain = 0 dB  |     |             | V <sub>DDA</sub> -0.1 |       |

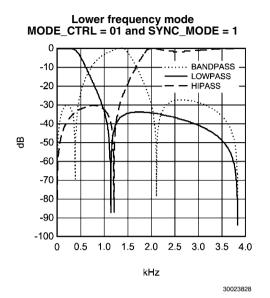

| f <sub>3dB</sub> | Crossover Frequencies (-3 dB) |              |     |             |                       |       |

|                  | Narrow Frequency Response     | Low Pass     |     | 0.5         |                       |       |

|                  |                               | Band Pass    |     | 1.0 and 1.5 |                       |       |

|                  |                               | High Pass    |     | 2.0         |                       | kHz   |

|                  | Wide Frequency Response       | Low Pass     |     | 1.0         |                       |       |

|                  |                               | Band Pass    |     | 2.0 and 3.0 |                       |       |

|                  |                               | High Pass    |     | 4.0         |                       |       |

#### CONTROL OF ADC AND AUDIO SYNCHRONIZATION

The following table describes the controls required for audio synchronization.

| Audio_sync_CTRL1 (2AH) |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                        | Input signal gain control. R                                                | ange 021 dB, step 3 dB:                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Dito 7 5               | [000] = 0 dB (default)                                                      | [011] = 9 dB                                                                                                                                                                                                                                                                                                                                                                                                                                             | [110] = 18 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| DIIS 7-0               | [001] = 3 dB                                                                | [100] = 12 dB                                                                                                                                                                                                                                                                                                                                                                                                                                            | [111] = 21 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                        | [010] = 6 dB                                                                | [101] = 15 dB                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                        | Synchronization mode sele                                                   | ctor.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Bit 4                  | SYNCMODE = 0 → Amplitu                                                      | ude Mode (default)                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                        | SYNCMODE = 1 → Freque                                                       | ency Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                        | Automatic Gain Control en                                                   | able                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Bit 3                  | 1 = enabled                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                        | 0 = disabled (Gain Select e                                                 | enabled) (default)                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                        |                                                                             | ble                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Bit 2                  | 1 = Enabled                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 2.12                   | Note : If AGC is enabled, AGC gain starts from current GAIN_SEL gain value. |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |