## SHA-1/HMAC BASED SECURITY AND AUTHENTICATION IC WITH SDQ INTERFACE

#### **FEATURES**

- **Provides Authentication of Battery Packs** Through SHA-1 Engine Based HMAC

- 160 Bytes OTP, 16 Bytes EEPROM

- **Internal Time-Base Eliminates External Crystal** Oscillator

- **Low Power Operating Modes:**

- Active: < 50 μA

- Sleep: 8 μA Typical

- Single-Wire SDQ Interface

- **Powers Directly From the Communication Bus**

- 6 Lead SON Package

#### APPLICATIONS

- **Cellular Phones**

- WWW.DZSG.COM **PDA and Smart Phones**

- **MP3 Plavers**

- **Digital Cameras**

- **Internet Appliances**

- **Handheld Devices**

#### DESCRIPTION

The bq26100 provides a method to authenticate battery packs, ensuring that only packs manufactured by authorized sub-contractors are used in the end application. The security is achieved using the SHA-1 hash function inside the widely adopted HMAC construction. A unique 128-bit key is stored in each bg26100 device, allowing the host to authenticate each pack.

The bg26100 communicates to the system over a simple one-wire bi-directional serial interface. The 5-kbits/s SDQ bus interface reduces communications overhead in the external microcontroller. The bq26100 also derives power over the SDQ bus line via an external capacitor.

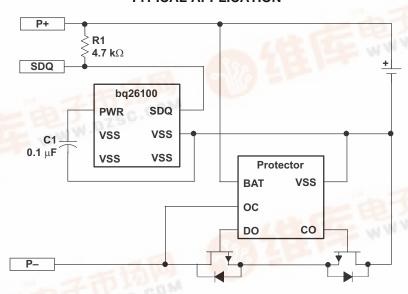

#### TYPICAL APPLICATION

df.dzsc.com

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE    | PART NUMBER |

|----------------|------------|-------------|

| -40°C to 85°C  | 6-lead SON | bq26100DRP  |

(1) For the most current package and ordiering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

## ABSOLUTE MAXIMUM RATINGS(1)

|                  |                                              | VALUE       | UNIT |

|------------------|----------------------------------------------|-------------|------|

|                  | Supply voltage (SDQ all with respect to VSS) | -0.3 to 7.7 | V    |

|                  | Output current (SDQ)                         | 5           | mA   |

| T <sub>A</sub>   | Operating free-air temperature range         | -40 to 85   | °C   |

| T <sub>stg</sub> | Storage temperature range                    | -65 to 150  | °C   |

| TJ               | Junction temperature range                   | -40 to 90   | °C   |

|                  | Lead temperature (Soldering, 10 sec)         | 300         | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|           |                                      | MIN | MAX | UNIT |

|-----------|--------------------------------------|-----|-----|------|

| $V_{sdq}$ | Pull-up voltage                      | 2.5 | 5.0 | V    |

| TJ        | Operating free-air temperature range | -40 | 85  | °C   |

## **ELECTRICAL CHARACTERISTICS**

all parameters over operating free-air temperature and supply voltage range (unless otherwise noted) (memory programming and authentication were tested with R1 = 4.7 k $\Omega$ , C1 = 0.1  $\mu$ F over pull-up voltage range)

|                        | PARAMETER                                 | TEST CONDITIONS             | MIN | TYP | MAX  | UNIT    |

|------------------------|-------------------------------------------|-----------------------------|-----|-----|------|---------|

|                        | Power up communication delay              | Power capacitor charge time |     | 100 |      | ms      |

| I <sub>sleep</sub>     | Sleep current                             |                             |     | 8   | 11   | μΑ      |

| I <sub>sdq(Vsdq)</sub> | V <sub>sdq</sub> Current                  | $V_{sdq} \ge V_{sdq(min)}$  |     |     | 50   | μΑ      |

|                        | OTP Memory programming voltage            |                             | 6.8 | 7   | 7.7  | V       |

|                        | OTP Memory programming time               |                             |     | 100 |      | μs/byte |

|                        | EEPROM Programming current (peak current) |                             |     | 83  |      | μΑ      |

|                        | EEPROM Peak current duration              |                             |     | 100 |      | μs      |

|                        | EEPROM Programming time                   |                             |     | 50  |      | ms      |

| SDQ                    |                                           |                             |     |     |      |         |

| $V_{IL}$               | Input low-level voltage                   |                             |     |     | 0.63 | V       |

| I <sub>OL</sub>        | Output low sink current                   | V <sub>OL</sub> = 0.4 V     |     |     | 1    | mA      |

## STANDARD SERIAL COMMUNICATION (SDQ) TIMING

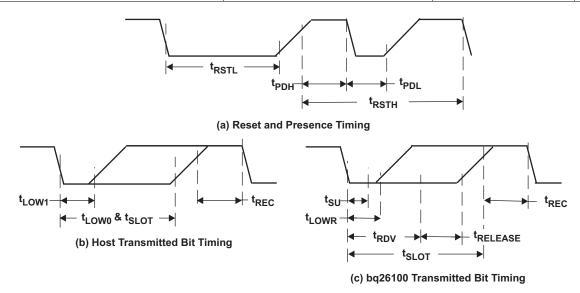

over recommended operating temperature and supply voltage range (unless otherwise noted) (See Figure 1)

|                   | PARAMETER              | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|-------------------|------------------------|-----------------|-----|---------|------|

| t <sub>RSTL</sub> | Reset time – low       |                 | 480 |         | μs   |

| t <sub>RSTH</sub> | Reset time – high      |                 | 480 |         | μs   |

| t <sub>PDL</sub>  | Presence detect – low  |                 | 60  | 240     | μs   |

| t <sub>PDH</sub>  | Presence detect – high |                 | 15  | 60      | μs   |

| t <sub>REC</sub>  | Recovery time          |                 | 1   |         | μs   |

## STANDARD SERIAL COMMUNICATION (SDQ) TIMING (continued)

over recommended operating temperature and supply voltage range (unless otherwise noted) (See Figure 1)

|                      | PARAMETER            | TEST CONDITIONS | MIN | TYP        | MAX | UNIT |

|----------------------|----------------------|-----------------|-----|------------|-----|------|

| t <sub>SLOT</sub>    | Host bit window      |                 | 60  |            | 120 | μs   |

| t <sub>LOW1</sub>    | Host sends 1         |                 | 1   |            | 13  | μs   |

| t <sub>LOW0</sub>    | Host sends 0         |                 | 60  |            | 120 | μs   |

| t <sub>LOWR</sub>    | Host read bit start  |                 | 1   |            | 13  | μs   |

| t <sub>SLOT</sub>    | bq26100 bit window   |                 | 60  |            | 120 | μs   |

| t <sub>SU</sub>      | bq26100 data setup   |                 |     |            | 1   | μs   |

| t <sub>RDV</sub>     | bq26100 data valid   |                 |     | exactly 15 |     | μs   |

| t <sub>RELEASE</sub> | bq26100 data release |                 | 0   | 15         | 45  | μs   |

Figure 1. SDQ Timing Diagrams

The SDQ protocol requires a CRC calculation as part of the communication flow. The CRC, based on a polynomial of  $x^8+x^5+x^4+1$ , is computed to determine data integrity and its use varies in the protocol. The Memory Function flows show what data is shifted through the CRC and when the value is transmitted from the slave. Each data byte used in the CRC calculation is pushed through the CRC shift register from LSB to MSB. The byte wide CRC computation is:

```

for (i = 0; i < 8; i++)

{

if (crc[0] ^ input[i])

crc = (crc >> 1) ^ 0x8C;

else

crc = crc >> 1;

}

```

Where did the magic number 0x8C come from? CRC polynomials are defined such that the highest order simply shows the number of bits, so  $x^8+x^5+x^4+1$  defines an 8-bit value with a binary value of 00110001 (bits 0, 4, and 5 are 1 and all others are 0). Since the SDQ CRC is computed by shifting in the LSB, the polynomial must be used in reverse bit order – binary 10001100 or hexadecimal 0x8C.

The CRC value is reset to 0 prior to the first byte being shifted through. The CRC is also reset when the CRC is shifted out as part of the SDQ protocol.

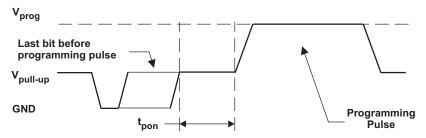

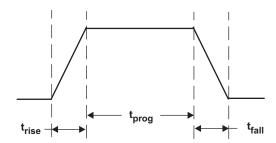

## **OTP PROGRAMMING SPECIFICATIONS**

|                   | PARAMETER          | TEST CONDITIONS         | MIN - | TYP MAX | UNIT |

|-------------------|--------------------|-------------------------|-------|---------|------|

| t <sub>pon</sub>  | Program setup time |                         | 2     |         | μs   |

| t <sub>rise</sub> | Pulse rise time    |                         | 1     | 10      | μs   |

| t <sub>prog</sub> | Pulse high time    | Single byte programming | 300   |         | μs   |

|                   |                    | Key programming         | 3     |         | μs   |

| t <sub>fall</sub> | Pulse fall time    |                         | 1     | 10      | μs   |

Figure 2. bq26100 Communication to OTP Programming Pulse Diagram

Figure 3. OTP Programming Pulse Detail

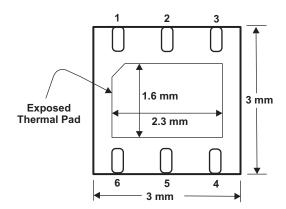

#### **PIN ASSIGNMENT**

#### **TERMINAL FUNCTIONS**

| 7    | TERMINAL   |     | DESCRIPTION                       |  |

|------|------------|-----|-----------------------------------|--|

| NAME | NO.        | 1/0 | DESCRIPTION                       |  |

| PWR  | 1          | I/O | Power capacitor connection        |  |

| SDQ  | 6          | I/O | Single wire SDQ interface to host |  |

| VSS  | 2, 3, 4, 5 | I   | Ground                            |  |

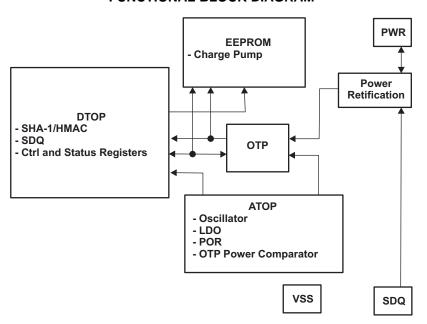

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

The bq26100 provides the same basic functionality as the bq2022 with added battery pack/accessory authentication functions. In addition to four 32-byte pages of general use One Time Programmable (OTP) non-volatile memory available on the bq2022, the bq26100 adds a fifth 32-byte page of OTP and a 16-byte page of EEPROM to be used at the host system designer's discretion. An external high voltage is required for programming the OTP, but not necessary for programming the EEPROM.

A modified form of the SHA-1/HMAC provides the authentication function of the bq26100. Both the host and the bq26100 share two 64-bit keys used in the authentication calculation. To authenticate a battery pack, the host

writes a random 20-byte message to the bq26100 and sets the AUTH bit in the CTRL register. The bq26100 calculates the HMAC digest in less than  $500~\mu s$ , replacing the random message sent by the host with the HMAC result. To complete the authentication process, the host computes the HMAC function with the same 20-byte random message originally written to the bq26100. The result is compared to the HMAC result computed by the bq26100. If the values match, the pack is authenticated.

The key is separated into two 64-bit spaces, allowing multiple parties to program separate portions of the key and providing an added level of security. Programming a key utilizes the SHA-1 algorithm to provide a mix from the values used to program the device to the actual key stored on the device. When put into key programming mode, the device combines the 160-bit message space with a pad as required to get the minimum 512-bit SHA-1 block, and run through the SHA-1 engine once. The 160-bit output is truncated to the lower 64 bits, scrambled internally, and then written to the appropriate non-volatile memory key space. The key can only be read and descrambled by the authentication engine, not by the communication engine, of the bq26100.

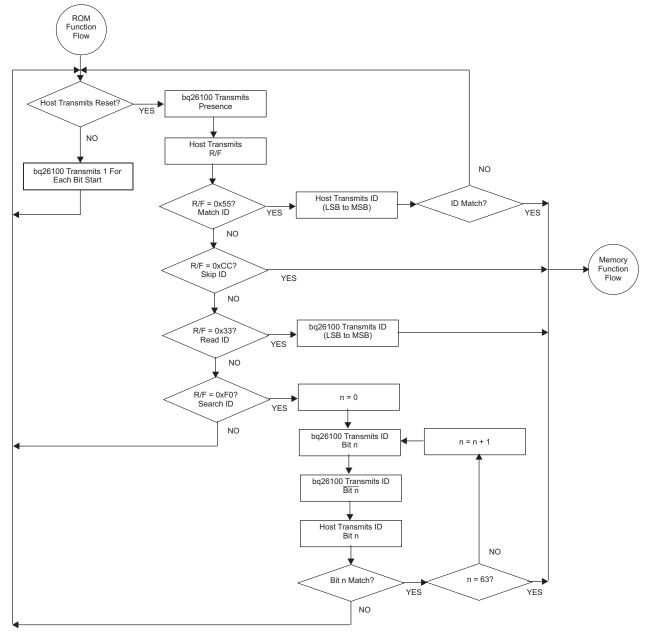

## Communicating with the bq26100

The bq26100 communication protocol starts when the host pulls the bus low for reset time. All devices on the bus are to respond with a presence pulse, which is active low. The host can then transmit the ROM Function command, which is used to address the devices on the bus. The ROM functions include Match ID, Skip ID, Read ID, and Search ID.

| Match ID  | The host transmits the 64-bit ID of the 1-wire based device to communicate.                                                                                                                                                                                                                  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Skip ID   | No ID is necessary for communication. Used only if one device is connected to the host.                                                                                                                                                                                                      |

| Read ID   | The 1-wire slave transmits its 64 bit address. This command is only useful if there is only one device connected to the host.                                                                                                                                                                |

| Search ID | Useful if there are multiple devices on the bus. This command initiates a communication with a single device, but it is more useful in allowing the host to determine the address of every device on the bus. The Match ID can then be used to communicate with a specific addressed device. |

Figure 4. ROM Function Flow Chart

The 64-bit device ID is made up of an 8-bit family code, 48-bit random value, and a final 8-bit CRC.

| ID MSB       | ID MSB                |                                        |  |

|--------------|-----------------------|----------------------------------------|--|

| CRC (8 bits) | Random Data (48 bits) | Family Code (8 bits, defaults to 0x09) |  |

Contact Texas Instruments if specific data should be programmed into the ID.

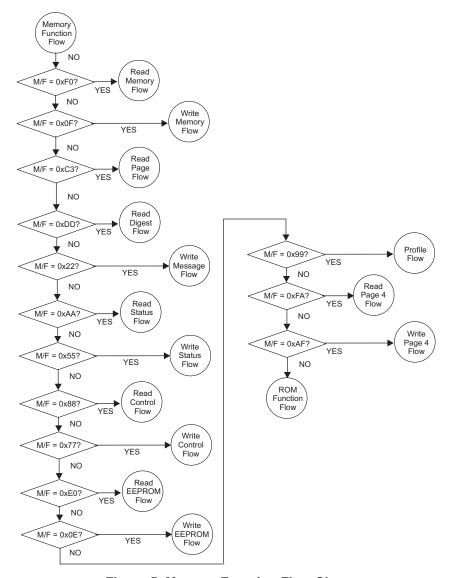

After the ROM function command is issued and the bq26100 is selected, a Memory Function command can be issued. The Memory Function commands are Read Memory, Read EEPROM, Read Status, Read Page, Read Page 4, Read Digest, Read Control, Write Memory, Write Page 4, Write EEPROM, Write Status, Write Message, Write Control, and Profile.

Figure 5 shows the flow for the Memory Function selection. Figure 6 through Figure 12 illustrate the flow for each memory function.

**Figure 5. Memory Function Flow Chart**

#### **MEMORY DESCRIPTIONS**

The bq26100 has a memory and command structure that is compatible with the bq2022, however additional memory and commands have been added. The bq26100 uses a combination of non-volatile One-Time-Programmable (OTP), non-volatile EEPROM, and volatile registers. The memory is split into the following sections:

## **Non-Volatile OTP Memory**

The One Time Programmable (OTP) memory is intended for factory programming. Programming the OTP requires putting a 7-V pulse on the communication pin after writing the data to the intended address.

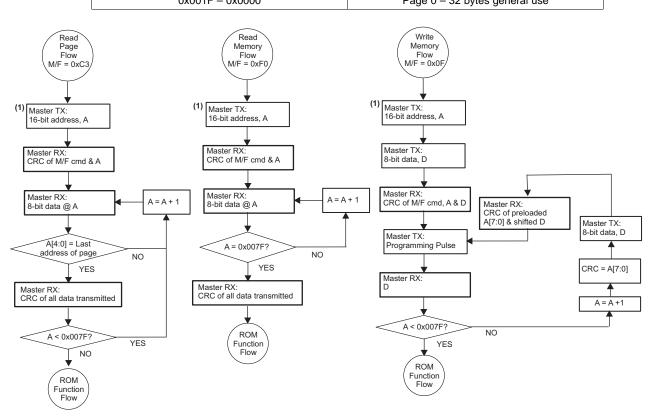

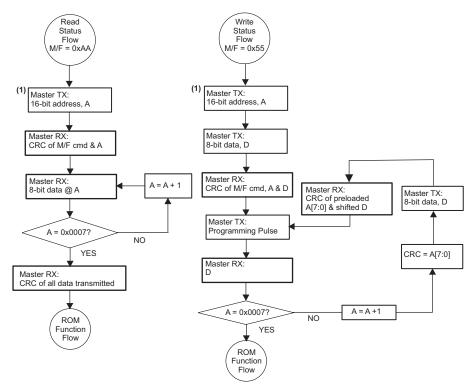

## General Use – Memory Function Commands 0xF0 (Read) and 0x0F (Write)

The general use space is erased to read 0x00. Data written to the general space is ORed with data already present at the address to be written. A bit can only be flipped from **0** to **1**.

ADDRESSES

FUNCTION

0x007F - 0x0060

Page 3 - 32 bytes general use

0x005F - 0x0040

Page 2 - 32 bytes general use

0x003F - 0x0020

Page 1 - 32 bytes general use

0x001F - 0x0000

Page 0 - 32 bytes general use

**Table 1. General Memory Space Addressing**

Figure 6. General Memory OTP Write/Read Flows

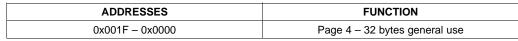

## General Use — Memory Function Commands 0xFA (Read) and 0xAF (Write)

The general use space is erased to read 0x00. Data written to the general space is ORed with data already present at the address to be written. A bit can only be flipped from **0** to **1**.

**Table 2. General Memory Space Addressing**

Figure 7. General Memory OTP Write/Read Flows

# /w.ti.com "B<u>Q26100"供应商</u>

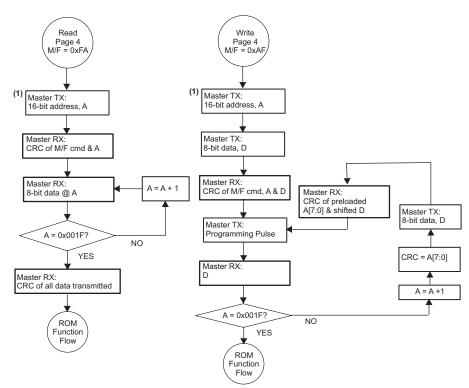

## Status – Memory Function Commands 0xAA (Read) and 0x55 (Write)

Unlike the general use pages, the status bytes read 0xFF when not programmed and a bit is programmed from 1 to 0. A zero represents the active state.

#### Address 0x0007 Reserved

Default value is 0xFF

## Address 0x0006 Key Index

The host can determine which one of multiple keys was programmed into the bg26100 by reading the key index value.

## Address 0x0005 - 0x0001 Page Redirection

A pointer for alternative page information, these bytes can be used if information in the original page has been invalidated. The host can read these locations and direct reads and/or writes to the page pointed to by the value in the register. For example, if the data in page 2 is corrupted by an incorrectly written data value, and the corrected data is in page 1, the value written to address 0x0003 would be 0xFE (1's complement value of 0x01). Upon reading address 0x0003, the host would receive 0xFE and would take the 1's complement to determine that page 1 contains redirected data.

**Table 3. Page Redirection**

| ADDRESS | PAGE REDIRECTED |

|---------|-----------------|

| 0x0005  | Page 4          |

| 0x0004  | Page 3          |

| 0x0003  | Page 2          |

| 0x0002  | Page 1          |

| 0x0001  | Page 0          |

There is no hardware mapping of the page redirection bytes. The host is responsible for sending the correct address for a redirected page.

#### Address 0x0000 PAGE LOCK

|          | BIT 7  | BIT 6  | BIT 5 | BIT 4  | BIT 3  | BIT 2  | BIT 1  | BIT 0  |

|----------|--------|--------|-------|--------|--------|--------|--------|--------|

| FUNCTION | LOCKK1 | LOCKK0 | RSVD  | PAGE 4 | PAGE 3 | PAGE 2 | PAGE 1 | PAGE 0 |

- **LOCKK1** Programming this bit to **0** locks the upper 64 bits of the device key, preventing additional writes. This bit can only be written once.

- **LOCKKO** Programming this bit to **0** locks the lower 64 bits of the device key, preventing additional writes. This bit can only be written once.

- **PAGEX** Programming this bit to **0** locks page designated by x, preventing additional writes. This bit can only be programmed once.

Figure 8. Status OTP Write/Read Flows

## **Non-Volatile EEPROM Memory**

The EEPROM memory is intended for in-field programming. Programming the EEPROM is no different than writing to RAM or registers, but the timing between the write and read back is different. A bit can be written to 1 or cleared to 0 multiple times and the value is retained when power to the device is removed.

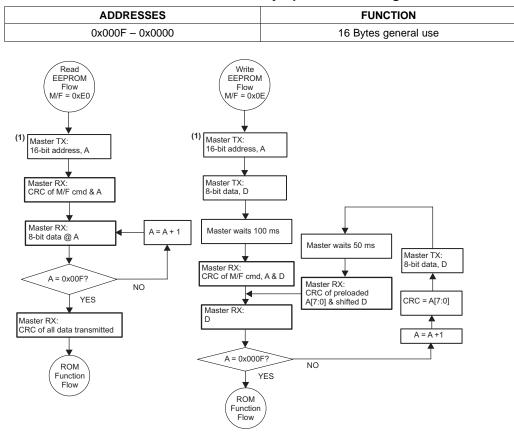

## General Use - Memory Function Commands 0xE0 (Read) and 0x0E (Write)

**Table 4. General Memory Space Addressing**

Figure 9. EEPROM Write/Read Flows

## **Volatile Register Memory**

The register memory is intended for in-field programming.

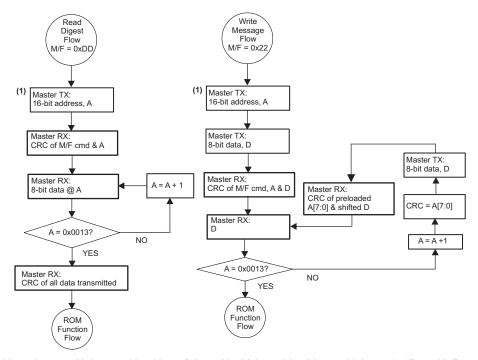

## Message and Digest Registers - Memory Function Command 0xDD (Read) and 0x22 (Write)

The message is a 160-bit input to the HMAC calculation, and the digest is the 160-bit output of the HMAC calculation. The message and digest share the same memory space, meaning that the message cannot be read back once the digest has been computed. The MSB of the message should be written to address 0x0013, and the LSB written to address 0x0000. The digest overwrites the message in the following manner.

Table 5. Message/Digest Space Addressing

| ADDRESS         | MESSAGE VALUE | DIGEST VALUE |

|-----------------|---------------|--------------|

| 0x0013 - 0x0010 | M[159:128]    | A[31:0]      |

| 0x000F - 0x000C | M[127:96]     | B[31:0]      |

| 0x000B - 0x0008 | M[95:64]      | C[31:0]      |

| 0x0007 - 0x0004 | M[63:32]      | D[31:0]      |

| 0x0003 - 0x0000 | M[31:0]       | E[31:0]      |

#### NOTE:

See the SHA-1 and HMAC descriptions for more information on the meaning of the variables in the above table.

Figure 10. Message/Digest Write/Read Flows

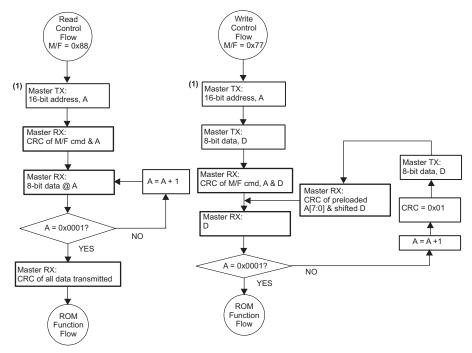

## Control and Version Registers – Memory Function Command 0x88 (Read) and 0x77 (Write)

The control register starts authentication, clears the message/digest values, and flags when the authentication process has completed. The version register is used to determine the silicon revision.

**Table 6. General Memory Space Addressing**

| ADDRESSES | FUNCTION                |  |  |  |

|-----------|-------------------------|--|--|--|

| 0x0001    | Silicon Revision Number |  |  |  |

| 0x0000    | Control Register        |  |  |  |

The bits of the Control register are as follows:

|            | BIT 7  | BIT 6  | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------------|--------|--------|-------|-------|-------|-------|-------|-------|

| NAME       | PROGK1 | PROGK0 | RSVD  | CLEAR | RSVD  | POR   | DONE  | AUTH  |

| POR STATUS | 0      | 0      | 0     | 0     | 0     | 1     | 0     | 0     |

**PROGK1** If LOCKK1 is **1** (see Status Register), writing this bit to **1** enables the programming of Device Key 1. Further information about the programming of the keys is found in the SHA-1 section.

**PROGK0** If the LOCKK0 bit is **1** (see Status Register), writing this bit to **1** enables the programming of Device Key 0. Further information about the programming of the keys is found in the SHA-1 section.

**RSVD** These bits are reserved for future use. They should always be written to **0**.

CLEAR Writing this bit to 1 clears the message/digest registers. This can be done before the message is written to ensure that all data values are known or after the digest is read to clear the HMAC calculation output. The bq26100 resets the bit back to 0.

POR This bit is set when the device comes out of a POR condition. The bit can be written to **0** to clear the flag. Writing the bit to **1** has no effect on device operation.

**DONE** This bit is set when the device completes the HMAC calculation. The host should poll for this bit to determine when the digest is available for reading. This bit is automatically cleared when the AUTH bit is written to **1**. This bit is also cleared at POR.

**AUTH** This bit is set to initiate the HMAC calculation. This bit is automatically cleared when the DONE bit is written to **1**.

(1) 16-Bit address is sent with lower 8-bit address followed by higher 8-bit address with least significant bit first.

Figure 11. Control Register Write/Read Flows

#### **Profile Command**

Pack manufacturers can use the profile command to determine how the device should be programmed.

Figure 12. Profile Command Flow

### **SLEEP MODE DESCRIPTION**

The bq26100 enters sleep mode when the SDQ enters a stop state or when SDQ encounters an invalid ID.

## **SHA-1 DESCRIPTION**

The SHA-1 is known as a one-way hash function, meaning there is no known mathematical method of computing the input given only the output. The specification of the SHA-1, as defined by FIPS 180-2, states that the input consists of 512 bit blocks with a total input length less than 2<sup>64</sup> bits. Inputs which do not conform to integer multiples of 512 bit blocks are padded before any block is input to the hash function. The SHA-1 algorithm outputs 160 bits, commonly referred to as the digest.

The full SHA-1 specification and algorithm can be found at http://csrc.nist.gov/publications/fips under FIPS 180. (As of April 23, 2004 the latest revision is FIPS 180-2).

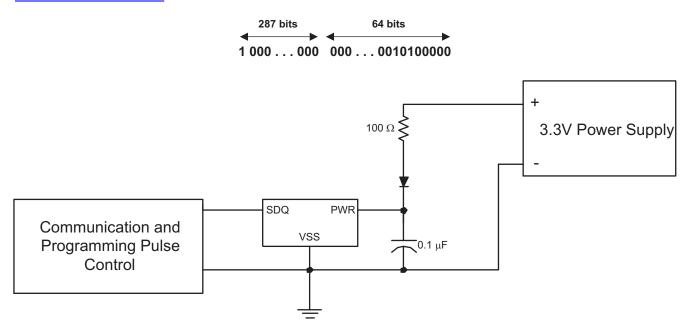

The bq26100 generates an SHA-1 input block of 288 bits (total input = 160 bit message + 128 bit key). To complete the 512 bit block size requirement of the SHA-1, the bq26100 pads the key and message with a 1, followed by 159 0's, followed by the 64 bit value for 288 (000...00100100000), which conforms to the pad requirements specified by FIPS 180-2:

#### **HMAC DESCRIPTION**

The SHA-1 engine is used to calculate a modified HMAC value. Using a public message and a secret key, the HMAC output is considered to be a secure *fingerprint* that authenticates the device used to generate the HMAC.

To compute the HMAC let H designate the SHA-1 hash function, M designate the message transmitted to the bq26100, and  $K_D$  designate the unique 128 bit device key of the bq26100. HMAC(M) is defined as:

$H[K_D || H(K_D || M)]$ , where || symbolizes an append operation

The message, M, is appended to the device key,  $K_D$ , and padded to become the input to the SHA-1 hash. The output of this first calculation is then appended to the device key,  $K_D$ , padded again, and cycled through the SHA-1 hash a second time. The output is the HMAC digest value.

#### **KEY PROGRAMMING DESCRIPTION**

The 128-bit key used in the HMAC calculation is built from two 64-bit key spaces on the bq26100. Each key can be programmed independently, allowing multiple parties to program part of the full 128-bit key without the knowledge necessary to reproduce the full 128-bit key. To further protect the 128-bit key, the value written to each 64-bit non-volatile key space is the output of a SHA-1 calculation on a 160-bit input. Figure 13 provides a flow for the programming of the 128-bit device key. Once KEYx has been programmed, the LOCKKx bit should be programmed to 0 in the status register, preventing another value from overwriting that key space.

Figure 13. Key Programming Flow

This flow is run twice, for KEY0 and KEY1. An external power source is required on the PWR pin during key programming. Figure 14 shows a typical connection for the external power source.

Since there is no key pre-appended to the message, the key message is padded with a 1, followed by 287 0's, followed by the 64-bit value for 160 (00..01010000):

Figure 14. External Power Source Connection

## PACKAGE OPTION ADDENDUM

查询"BQ26100"供应商

8-Dec-2009

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package<br>Type | Package<br>Drawing | Pins P | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|------------|-----------------|--------------------|--------|----------------|---------------------------|------------------|------------------------------|

| BQ26100DRPR      | ACTIVE     | VSON            | DRP                | 6      | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| BQ26100DRPRG4    | ACTIVE     | VSON            | DRP                | 6      | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND**: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

查询"BQ26100"供应商

8-Dec-2009

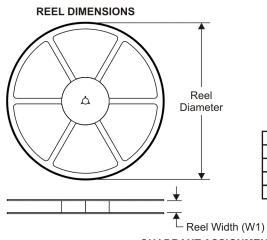

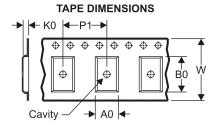

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

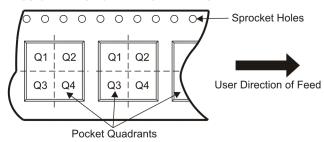

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

## \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| BQ26100DRPR | VSON            | DRP                | 6 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

查询"BQ26100"供应商

8-Dec-2009

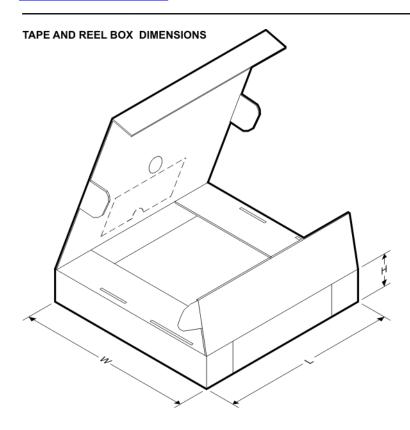

#### \*All dimensions are nominal

|   | Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| I | BQ26100DRPR | VSON         | DRP             | 6    | 3000 | 346.0       | 346.0      | 29.0        |

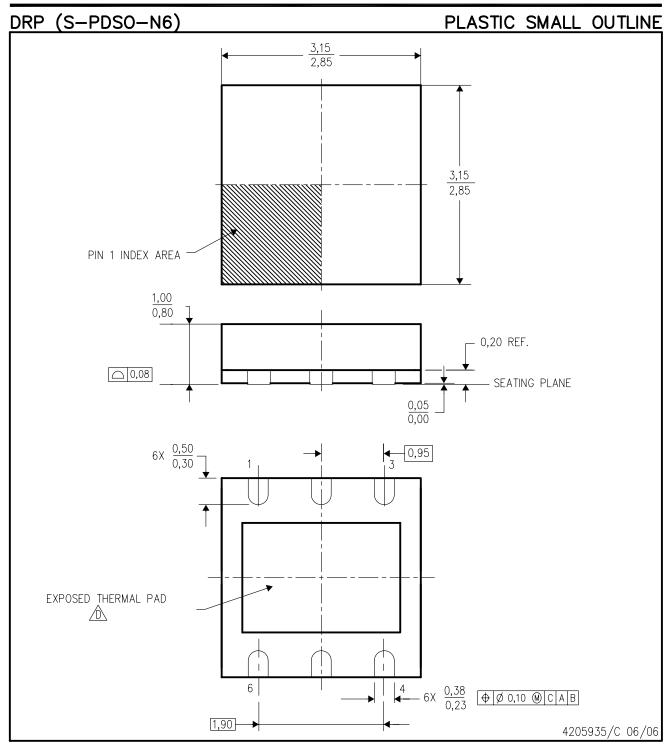

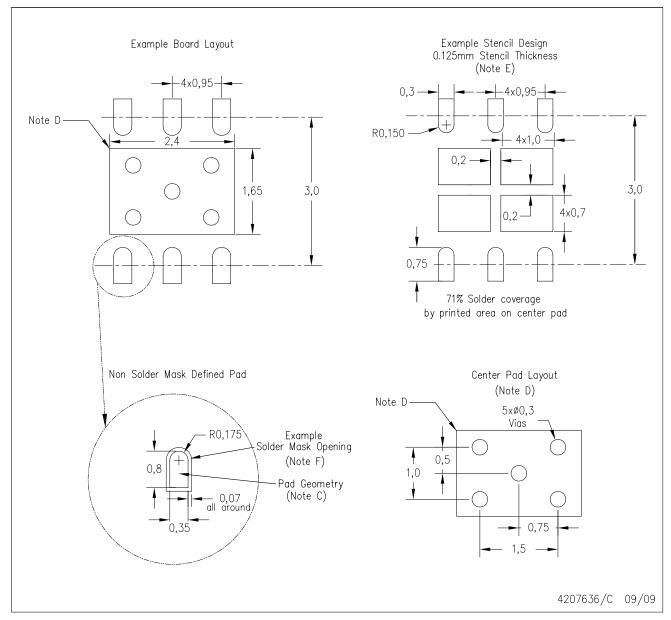

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. Small Outline No-Lead (SON) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

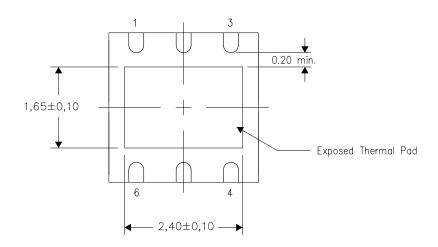

## THERMAL PAD MECHANICAL DATA

DRP (S-PVSON-N6)

## THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

## DRP (S-PVSON-N6)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, QFN Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for solder mask tolerances.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com **DLP® Products** Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface Military www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated