#

# USB Single Channel Transceiver

The NCN2500 Integrated Circuit is a single channel transceiver designed to accommodate the physical USB Port with a microcontroller digital I/O. The part is fully USB compliant and supports the full 12 Mbps speed. On the other hand, the NCN2500 device includes the pullup resistors as defined by the USB–ECN new specifications.

#### Features

- Compliant to the USB Specification, Version 2.0, Low and Full Speed

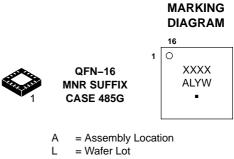

- Very Small Footprint Due to the QFN-16 Package

- Integrated D+/D- Pullup Resistors

- Operates Over the Full 1.5 V to 3.6 V Supply

- Pb–Free Package is Available\*

#### **Typical Applications**

- Portable Computer

- Cellular Phone

### **ON Semiconductor®**

http://onsemi.com

- Y = Year

- W = Work Week

- = Pb–Free Package

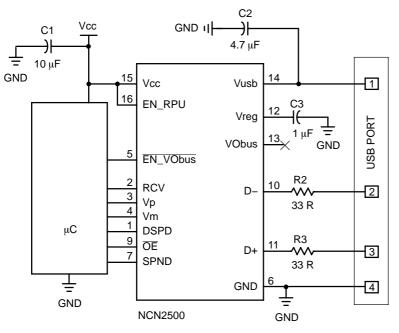

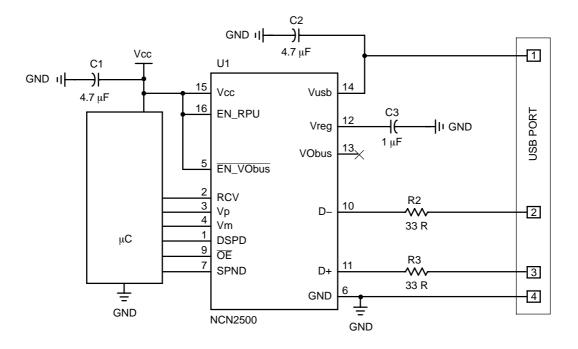

**Figure 1. Typical Application**

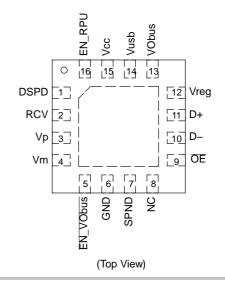

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

| Device       | Package             | Shipping†        |

|--------------|---------------------|------------------|

| NCN2500MNR2  | QFN-16              | 3000 Tape & Reel |

| NCN2500MNR2G | QFN-16<br>(Pb-Free) | 3000 Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

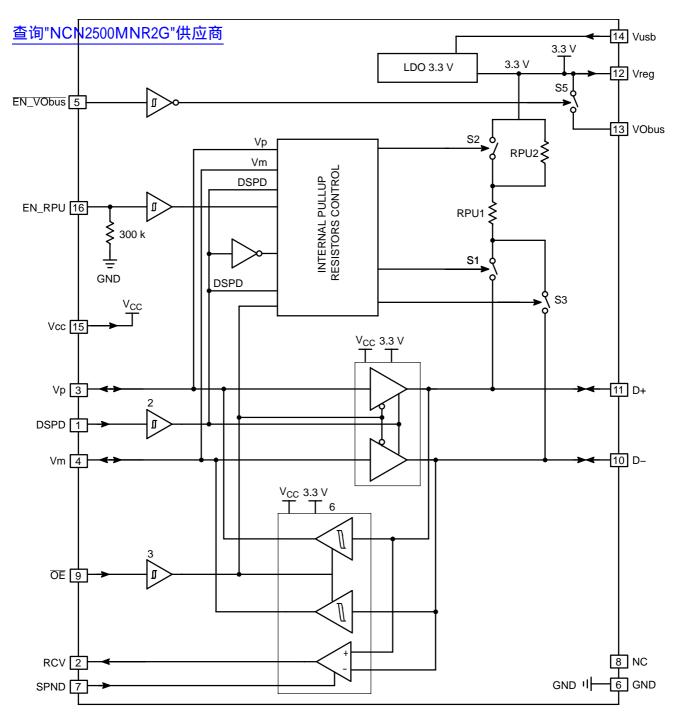

Figure 2. Block Diagram

#### PIN FUNCTION DESCRIPTION 查省"NCN2500MNR2G"供应商

| Pin | Symbol   | Function    | Description                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-----|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | DSPD     | INPUT       | The DSPD logic level (Data Speed) activates the Low or the High speed<br>operation on the USB port.<br>DSPD = Low Low Speed, RPU1 and RPU2 connected to D–<br>DSPD = High Full Speed, RPU1 and RPU2 connected to D+                                                                                                                                                                                                       |  |  |  |

| 2   | RCV      | OUTPUT      | This pin interfaces the USB signals with the microcontroller digital line. The data present on the D+/D– pins are translated onto this signal.                                                                                                                                                                                                                                                                            |  |  |  |

| 3   | Vp       | I/O         | $ \begin{array}{l} \mbox{This pin, associated with Vm, is an I/O system interface signal depending upon the \overline{OE} logic state: \ensuremath{\overline{OE}}\xspace = Low & Vp \mbox{ is a Plus driver Input (from $\mu$C to USB bus)} \\ \ensuremath{\overline{OE}}\xspace = High & Vp \mbox{ is a Plus receiver Output (from USB bus to $\mu$C)} \end{array} $                                                     |  |  |  |

| 4   | Vm       | I/O         | $ \begin{array}{l} \label{eq:constraint} \hline This pin, associated with Vp, is an I/O system interface signal depending upon the \\ \hline \overline{OE} \mbox{ logic state:} \\ \hline \overline{OE} \mbox{ = } \mbox{ Low } Vm \mbox{ is a Minus driver Input (from $\mu$C to USB bus)} \\ \hline \overline{OE} \mbox{ = } \mbox{ High } Vm \mbox{ is a Minus receiver Output (from USB bus to $\mu$C)} \end{array} $ |  |  |  |

| 5   | EN_VObus | INPUT       | Digital input to control the VObus voltage.      EN_VObus    = Low    VObus connected to Vreg      EN_VObus    = High    VObus disconnected from Vreg (Hi Z)                                                                                                                                                                                                                                                              |  |  |  |

| 6   | GND      | PWR         | This pin carries the digital and USB ground level. High Quality PCB design shall be observed to avoid uncontrolled voltage spikes.                                                                                                                                                                                                                                                                                        |  |  |  |

| 7   | SPND     | INPUT       | The SPND digital signal (SUSPEND) selects the operation mode to reduce the power supply current.      SPND = Low    Normal operation      SPND = High    Suspend mode, no activity takes place                                                                                                                                                                                                                            |  |  |  |

| 8   | NC       | -           | No Connection, shall be neither grounded, nor connected to Vcc or Vbus.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 9   | ŌĒ       | INPUT       | This pin activates the operating mode of the D-/D+ signals. $\overline{OE}$ = Low logic levelData are transmitted onto the USB bus $\overline{OE}$ = High logic levelData are received from the USB bus                                                                                                                                                                                                                   |  |  |  |

| 10  | D-       | I/O         | This pin is connected to the USB Minus Data line I/O. The data direction depends upon the $\overline{\text{OE}}$ logic state.                                                                                                                                                                                                                                                                                             |  |  |  |

| 11  | D+       | I/O         | This pin is connected to the USB Plus Data line I/O The data direction depends upon the $\overline{\text{OE}}$ logic state.                                                                                                                                                                                                                                                                                               |  |  |  |

| 12  | Vreg     | PWR         | This pin provides a 3.3 V regulated voltage to supply the internal USB blocks and the external termination bias resistor. An external circuit can be connected to this LDO, assuming the current does not extend the maximum rating (50 mA).                                                                                                                                                                              |  |  |  |

| 13  | VObus    | OUTPUT, PWR | This pin connects the Vreg voltage to the 1.5 k external pullup resistor. The VObus voltage is controlled by the logic states present Pin 5. The R <sub>DSon</sub> of the internal PMOS device (reference S5 in the Block Diagram) is 10 $\Omega$ typical.                                                                                                                                                                |  |  |  |

| 14  | Vusb     | PWR         | This pin is connected to the USB port +Vcc supply voltage.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 15  | Vcc      | PWR         | This pin provides the interface power supply. The power source can be an external supply or can be derived from the USB + Vusb voltage.                                                                                                                                                                                                                                                                                   |  |  |  |

| 16  | EN_RPU   | INPUT       | This pin activates or deactivate the internal RPU1 and RPU2 pullup resistors:      EN_RPU = H    RPU1 and RPU2 activated      EN_RPU = L    RPU1 and RPU2 deactivated                                                                                                                                                                                                                                                     |  |  |  |

# 者希MMMRATINGS, IR2G"供应商

| Rating                                                                                                        | Symbol                              | Value                                    | Unit          |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------|---------------|

| Power Supply Voltage                                                                                          | Vcc                                 | 6.0                                      | V             |

| Digital Input Pins                                                                                            | Vind                                | -0.5 V < Vin < Vcc + 0.5 V, but < 6.0 V  | V             |

| Digital Input Pins                                                                                            | Vid                                 | -0.5 V < Vin < AGND + 0.5 V, but < 6.0 V | V             |

| Digital Input Pins                                                                                            | Ibias                               | –35 mA < Ibias < 35 mA                   | mA            |

| ESD Capability, HBM (Note 1)<br>Vusb, D+, D–, GND<br>Any Other Pins<br>Machine Model, Any Pins                | V <sub>ESD</sub>                    | 10<br>2.0<br>200                         | kV<br>kV<br>V |

| QFN-16 Package<br>Power Dissipation @ Tamb = +85°C<br>Thermal Resistance, Junction-to-Air (R <sub>0JA</sub> ) | P <sub>DS</sub><br>R <sub>θJA</sub> | 470<br>85                                | mW<br>°C/W    |

| Operating Ambient Temperature Range                                                                           | T <sub>A</sub>                      | -40 to +85                               | °C            |

| Operating Junction Temperature Range                                                                          | TJ                                  | -40 to +125                              | °C            |

| Maximum Junction Temperature (Note 2)                                                                         | T <sub>Jmax</sub>                   | +150                                     | °C            |

| Storage Temperature Range                                                                                     | T <sub>sg</sub>                     | -65 to +150                              | °C            |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected. 1. Human Body Model,  $R = 1500 \Omega$ , C = 100 pF; Machine Model. 2. Absolute Maximum Rating beyond which damage(s) to the device may occur.

### 查询CTRURALSONARIARDERI供应商

| Characteristic                                                                                    | Symbol             | Pin                     | Min              | Тур          | Max        | Unit |

|---------------------------------------------------------------------------------------------------|--------------------|-------------------------|------------------|--------------|------------|------|

| DIGITAL PARAMETERS SECTION @ 1.5 V < Vcc < 3.6 V (                                                |                    |                         |                  | ess otherwis | e noted.)  |      |

| NOTE: Digital inputs undershoot < -0.3 V to ground, digital in                                    | -                  |                         |                  |              | 1          |      |

| High Level Input Voltage DSPD, Vp, Vm, EN_VObus,<br>SPND, OE, EN_RPU                              | V <sub>IH</sub>    | 1, 3, 4, 5,<br>7, 9, 16 | 0.80*Vcc         | -            | _          | V    |

| Low Level Input Voltage DSPD, Vp, Vm, <u>EN_VObus</u> ,<br>SPND, OE, EN_RPU                       | V <sub>IL</sub>    | 1, 3, 4, 5,<br>7, 9, 16 | -                | -            | 0.20*Vcc   | V    |

| High Level Output Voltage RCV, Vp, Vm @ I <sub>OH</sub> = 1.0 mA                                  | V <sub>OH</sub>    | 2, 3, 4                 | 0.80*Vcc         | -            | -          | V    |

| Low Level Output Voltage RCV, Vp, Vm @ $I_{OL}$ = 1.0 mA                                          | V <sub>OL</sub>    | 2, 3, 4                 | _                | -            | 0.20*Vcc   | V    |

| Input Leakage Current DSPD, Vp, Vm, EN_VObus,<br>SPND, OE, EN_RPU                                 | I <sub>IL</sub>    | 1, 3, 4, 5,<br>7, 9, 16 | -                | _            | ±5.0       | μΑ   |

| Input EN_RPU Pulldown Resistor @VCC = 3.3 V                                                       | RPU                | -                       | _                | 300          | -          | kΩ   |

| TRANSCEIVER SECTION @ 1.5 V < Vcc < 3.6 V $(-40^{\circ}C \text{ to})$                             | +85°C ambie        | ent temperatur          | e, unless otherv | wise noted.) |            |      |

| Static Output High, D–, D+ @ $\overline{OE}$ = Low, R <sub>L</sub> = 15 k $\Omega$ to GND         | V <sub>OH</sub>    | 10, 11                  | 2.8              | _            | 3.6        | V    |

| Static Output Low, D–, D+ @ $\overline{OE}$ = Low, R <sub>L</sub> = 1.5 k $\Omega$ to Vreg        | V <sub>OL</sub>    | 10, 11                  | _                | -            | 0.3        | V    |

| Single Input Receiver Threshold                                                                   | V <sub>SE</sub>    | 10, 11                  | 0.8              | _            | 2.0        | V    |

| Single Ended Receiver Hysteresis (Note 3)                                                         | -                  | -                       | _                | 200          | -          | mV   |

| Differential Input Sensitivity $  D+ - D-   @ 0.8 V < V_{CM} < 2.5 V (Note 3)$                    | V <sub>DI</sub>    | 10, 11                  | 0.2              | _            | -          | V    |

| Differential Common Mode Including the $V_{DI}$                                                   | V <sub>CM</sub>    | 10, 11                  | 0.8              | -            | 2.5        | V    |

| Differential Receiver Hysteresis (Note 3)                                                         | -                  | 10, 11                  | _                | 70           | -          | mV   |

| D+ and D– Transceiver Hi–Z State Leakage Current @ $\overline{\text{OE}}$ = 1, 0 V < Vusb < 3.3 V | I <sub>LO</sub>    | 10, 11                  | -                | _            | ±10        | μΑ   |

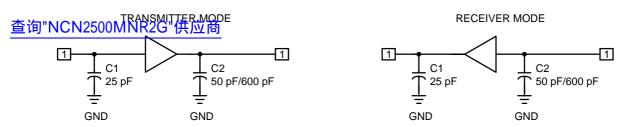

| Transceiver Input Capacitance (Note 3)                                                            | Cin                | 10, 11                  | -                | -            | 20         | pF   |

| Transceiver Output Resistance (Note 3)                                                            | Z <sub>DRV</sub>   | 10, 11                  | 28               | -            | 44         | Ω    |

| Transceiver Input Impedance (Note 3)                                                              | Z <sub>IN</sub>    | 10, 11                  | 10               | -            | -          | MΩ   |

| Internal RPU1 Pull Resistor                                                                       | R <sub>RPU-1</sub> | 10, 12                  | 900              | -            | 1575       | Ω    |

| Internal RPU2 Pull Up Resistor                                                                    | R <sub>RPU-2</sub> | 10, 12                  | 525              | -            | 1515       | Ω    |

| LOW SPEED DRIVER OPERATION (Note 3)                                                               |                    |                         |                  |              |            |      |

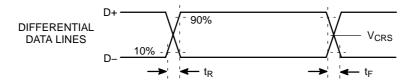

| Transition Rise Time<br>@ $C_L = 50 \text{ pF}$<br>@ $C_L = 600 \text{ pF}$                       | tr                 | 10, 11                  | 75<br>75         |              | 300<br>300 | ns   |

| Transition Fall Time<br>@ $C_L = 50 \text{ pF}$<br>@ $C_L = 600 \text{ pF}$                       | tf                 | 10, 11                  | 75<br>75         | -            | 300<br>300 | ns   |

| Rise and Fall Time Matching                                                                       | tr, tf             | 10, 11                  | 80               | _            | 125        | %    |

| Output Signal Crossover Voltage                                                                   | V <sub>CRS</sub>   | 10, 11                  | 1.3              | -            | 2.0        | V    |

| Data Transaction Rate                                                                             | Drate              | 10, 11                  | _                | _            | 1.5        | Mbs  |

3. Parameter guaranteed by design, not production tested.

### 查诺CTRICALSCHARACTERI 年 医新加加加

| Characteristic                                                                                                                                                                     | Symbol           | Pin             | Min            | Тур           | Max  | Unit     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|----------------|---------------|------|----------|

| FULL SPEED DRIVER OPERATION (Note 4)                                                                                                                                               |                  |                 |                |               |      |          |

| Transition Rise Time @ $C_L = 50 \text{ pF}$                                                                                                                                       | tr               | 10, 11          | 4.0            | -             | 20   | ns       |

| Transition Fall Time @ $C_L = 50 \text{ pF}$                                                                                                                                       | tf               | 10, 11          | 4.0            | -             | 20   | ns       |

| Rise and Fall Time Matching                                                                                                                                                        | tr, tf           | 10, 11          | 90             | -             | 110  | %        |

| Output Signal Crossover Voltage                                                                                                                                                    | V <sub>CRS</sub> | 10, 11          | 1.3            | -             | 2.0  | V        |

| Data Transaction Rate                                                                                                                                                              | Drate            | 10, 11          | -              | -             | 12   | Mbs      |

| TRANSCEIVER TIMING (Note 4)                                                                                                                                                        |                  |                 |                |               |      |          |

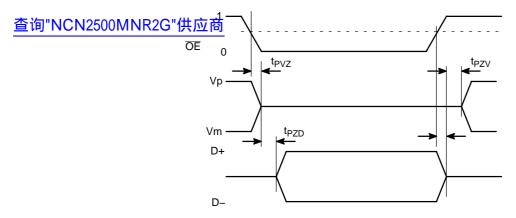

| OE to RCVR Hi–Z Delay (see Figure 3)                                                                                                                                               | t <sub>PVZ</sub> | 9               | -              | -             | 15   | ns       |

| Receiver Hi–Z to Transmit Delay (see Figure 3)                                                                                                                                     | t <sub>PZD</sub> | -               | 15             | -             | -    | ns       |

| OE to DRVR Hi–Z Delay (see Figure 3)                                                                                                                                               | t <sub>PDZ</sub> | -               | -              | -             | 15   | ns       |

| Driver Hi–Z to Receiver Delay (see Figure 3)                                                                                                                                       | t <sub>PZV</sub> | -               | 15             | -             | -    | ns       |

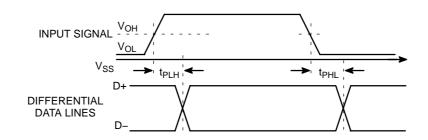

| Vp/Vm to D+/D- Propagation Delay (see Figure 6)                                                                                                                                    | t <sub>PLH</sub> | 3, 4, 10, 11    | -              | -             | 15   | ns       |

| Vp/Vm to D+/D- Propagation Delay (see Figure 6)                                                                                                                                    | t <sub>PHL</sub> | 3, 4, 10, 11    | -              | -             | 15   | ns       |

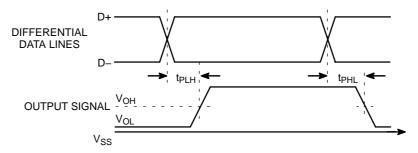

| D+/D- to RCV Propagation Delay @ $1.5 < Vcc < 5.5 V$<br>(see Figure 5) C <sub>L</sub> = 25 pF tr = tf = $3.0 \text{ ns}$                                                           | t <sub>PLH</sub> | 11, 10, 2       | -              | -             | 15   | ns       |

| D+/D– to RCV Propagation Delay @ $1.5 < Vcc < 5.5 V$<br>(see Figure 5) C <sub>L</sub> = 25 pF tr = tf = $3.0 \text{ ns}$                                                           | t <sub>PHL</sub> | 11, 10, 2       | -              | _             | 15   | ns       |

| D+/D– to Vp/D– Propagation Delay @ $1.5 < Vcc < 5.5 V$<br>(see Figure 5) C <sub>L</sub> = 25 pF tr = tf = $3.0 \text{ ns}$                                                         | t <sub>PLH</sub> | 11, 10, 3       | -              | _             | 8.0  | ns       |

| D+/D– to Vm/D– Propagation Delay @ $1.5 < Vcc < 5.5 V$<br>(see Figure 5) C <sub>L</sub> = 25 pF tr = tf = 3.0 ns                                                                   | t <sub>PHL</sub> | 11, 10, 4       | -              | -             | 8.0  | ns       |

| POWER SUPPLY SECTION @ 1.5 V < Vcc < 3.6 V (-40°C                                                                                                                                  | to +85°C am      | bient temperatu | re, unless oth | erwise noted. | )    |          |

| Digital Supply Voltage                                                                                                                                                             | Vcc              | 15              | 1.5            | -             | 3.6  | V        |

| USB Port Input Supply Voltage                                                                                                                                                      | Vusb             | 14              | 4.0            | -             | 5.25 | V        |

| Output Regulated Voltage @ 4.0 V < Vusb < 5.25 V,<br>Cin = 4.7 $\mu$ F, Cout = 1.0 $\mu$ F, Ireg = 100 mA                                                                          | Vreg             | 12              | 3.0            | 3.3           | 3.6  | V        |

| Output Switched Voltage @ Io = 1.0 mA, Cin = $4.7 \mu\text{F}$                                                                                                                     | Vobus            | 13              | 3.0            | 3.3           | 3.6  | V        |

| Line Regulation Output Voltage                                                                                                                                                     | Vreg             | 12              | _              | 0.1           | -    | %        |

| Standby Current @ Vusb = 5.25 V, $\overline{OE}$ = H, SPND = H,<br>D+ and D- are Idle, Vcc = 3.6 V                                                                                 | IVCC             | 14              | -              | 1.0           | -    | μΑ       |

| Standby Current @ Vusb = 5.25 V, $\overline{OE}$ = H, SPND = L, D+ and D– are Idle, Vcc = 3.6 V                                                                                    | I <sub>VCC</sub> | 14              | -              | 1.0           | -    | μΑ       |

| Operating Current $\overline{OE}$ = L, D– and D+ Active, SPND = L<br>(Note 4), Transmitter Mode<br>@ F = 6.0 MHz, C <sub>L</sub> = 50 pF<br>@ F = 750 kHz, C <sub>L</sub> = 600 pF | Ivcc             | 14              | -              | 300<br>40     |      | μΑ       |

| Operating Current $\overline{OE} = H$ , D- and D+ Active, SPND = L<br>(Note 4), Receiver Mode<br>@ F = 6.0 MHz, C <sub>L</sub> = 25 pF<br>@ F = 750 kHz, C <sub>L</sub> = 25 pF    | Ivcc             | 14              | _              | 1.5<br>250    | -    | mA<br>μA |

4. Parameter guaranteed by design, not production tested.

#### 查诺CTRICAL CHARACTERI (CG帝 ontinued)

| Characteristic                                                                                                                                                                                                                                                                                                                                     | Symbol           | Pin | Min         | Тур                      | Max                  | Unit                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------------|--------------------------|----------------------|----------------------|

| <b>POWER SUPPLY SECTION</b> @ <b>1.5</b> V < Vcc < <b>3.6</b> V (continued) (-40°C to +85°C ambient temperature, unless otherwise noted.)                                                                                                                                                                                                          |                  |     |             |                          |                      | )                    |

| USB Supply Current @ D- and D+ are Idle,<br>Vusb = $5.25$ V and:<br>@ SPND = 1, $\overrightarrow{OE}$ = 1, DSPD = 0, EN_RPU = 0<br>@ SPND = 0, $\overrightarrow{OE}$ = 1, DSPD = 1, EN_RPU = 0<br>@ SPND = 0, $\overrightarrow{OE}$ = 0, DSPD = 0, EN_RPU = 0<br>@ SPND = 1, $\overrightarrow{OE}$ = 1, DSPD = 0, EN_RPU = 1                       | I <sub>BUS</sub> | 14  | -<br>-<br>- | 120<br>1.7<br>1.7<br>320 | 200<br>-<br>-<br>500 | μA<br>mA<br>mA<br>μA |

| @ D- and D+ are Active, $C_L = 50 \text{ pF}$ , Vusb = 5.25 V,<br>SPND = 0, $\overline{OE} = 0$ , DSPD = 1, F = 6.0 MHz (Note 5)<br>@ EN_RPU = Low<br>@ EN_RPU = High<br>@ D- and D+ are Active (Note 5)<br>Vusb = 5.25 V, SPND = 0, $\overline{OE} = 0$ , DSPD = 1,<br>F = 750 kHz, $C_L = 600 \text{ pF}$<br>F = 750 kHz, $C_L = 300 \text{ pF}$ |                  |     | -<br>-<br>- | 8.3<br>9.4<br>5.4<br>3.9 |                      | mA<br>mA<br>mA<br>mA |

5. Parameter guaranteed by design, not production tested.

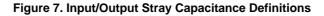

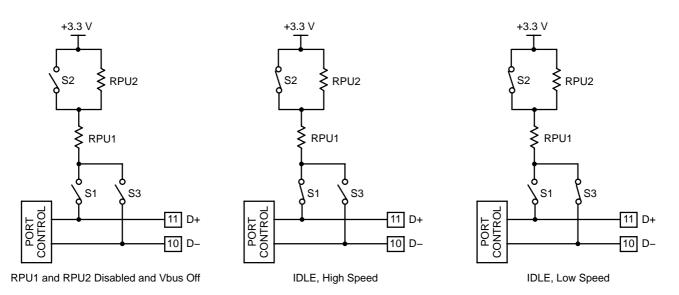

## Table 1, Internal RPU1 and RPU2 Pullup Resistors Control

| EN_RPU | DSPD | <b>S</b> 1 | S2    | S3    | Data Line | USB        | Note                                                   |

|--------|------|------------|-------|-------|-----------|------------|--------------------------------------------------------|

| 0      | Х    | Х          | Х     | Х     | Х         | Х          | Internal RPU Deactivated,<br>S1 and S3 are Forced OPEN |

| 1      | 1    | Open       | Х     | Open  | Vbus Off  | Х          | Internal RPU disabled                                  |

| 1      | 1    | Close      | Close | Open  | Idle      | Full Speed | Internal RPU Activated                                 |

| 1      | 1    | Closed     | Open  | Open  | Receiving | Full Speed | Internal RPU Activated                                 |

| 1      | 0    | Open       | Х     | Open  | Vbus Off  | Х          | Internal RPU disabled                                  |

| 1      | 0    | Open       | Close | Close | Idle      | Low Speed  | Internal RPU Activated                                 |

| 1      | 0    | Open       | Open  | Close | Receiving | Low Speed  | Internal RPU Activated                                 |

6. See Figure 8 and Figure 9.

#### Table 2. Transmit Mode Interface Control ( $\overline{OE} = 0 \rightarrow$ Transmit Mode)

| SPND | Vp | Vm | D+ | D- | RCV | STATE     |

|------|----|----|----|----|-----|-----------|

| 0    | 0  | 0  | 0  | 0  | Х   | SE0       |

| 0    | 0  | 1  | 0  | 1  | 0   | Low       |

| 0    | 1  | 0  | 1  | 0  | 1   | High      |

| 0    | 1  | 1  | 1  | 1  | Х   | Undefined |

| 1    | 0  | 0  | 0  | 0  | 0   | Suspend   |

| 1    | 0  | 1  | 0  | 1  | 0   | Suspend   |

| 1    | 1  | 0  | 1  | 0  | 0   | Suspend   |

| 1    | 1  | 1  | 1  | 1  | 0   | Suspend   |

#### Table 3. Receive Mode Interface Control ( $\overline{OE} = 1 \rightarrow \text{Receive Mode}$ )

| SPND | D+ | D- | Vp | Vm | RCV | STATE     |

|------|----|----|----|----|-----|-----------|

| 0    | 0  | 0  | 0  | 0  | Х   | SE0       |

| 0    | 0  | 1  | 0  | 1  | 0   | Low       |

| 0    | 1  | 0  | 1  | 0  | 1   | High      |

| 0    | 1  | 1  | 1  | 1  | Х   | Undefined |

| 1    | 0  | 0  | 0  | 0  | 0   | Suspend   |

| 1    | 0  | 1  | 0  | 1  | 0   | Suspend   |

| 1    | 1  | 0  | 1  | 0  | 0   | Suspend   |

| 1    | 1  | 1  | 1  | 1  | 0   | Suspend   |

Figure 3. Enable and Disable USB Times

Figure 4. USB Line Rise and Fall Times

Figure 5. Receiver Propagation Delays

Figure 6. Driver Propagation Delays

Figure 8. Internal RPU1 and RPU2 Pullup Resistors Operation, IDLE Mode

NOTE: Internal Pullup Resistor Range: RPU1: 900  $\Omega$  min–1575  $\Omega$  max, RPU2: 525  $\Omega$  min–1515  $\Omega$  max

#### Figure 9. Internal RPU1 and RPU2 Pullup Resistors Activated, RECEIVING Mode

### 查询"NCN2500MNR2G"供应商

**TYPICAL APPLICATIONS**

In this application, the two internal pullup resistors (RPU1 and RPU2) are used to bias the USB line. Consequently, the VObus voltage is deactivated (Pin 5 connected to Vcc).

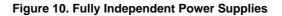

Figure 11. Peripheral are Powered by the Vreg Supply

# 查询"NCN2500MNR2G"供应商

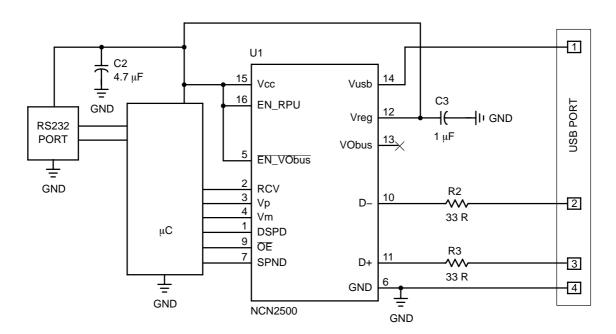

Note: Pin 16 can be left open, due to the internal pull-down resistor, or connected to ground.

Figure 12. Using External Pullup Resistors

### 查询"NCN2500MNR2G"供应商

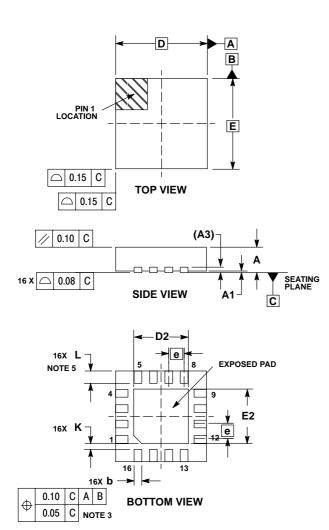

#### PACKAGE DIMENSIONS

QFN-16 **MNR SUFFIX** CASE 485G-01 ISSUE B

- NOTES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

Lmax CONDITION CAN NOT VIOLATE 0.2 MM MINIMUM SPACING BETWEEN LEAD TIP AND FLAG

|     | MILLIMETERS |      |  |  |  |  |

|-----|-------------|------|--|--|--|--|

| DIM | MIN         | MAX  |  |  |  |  |

| Α   | 0.80        | 1.00 |  |  |  |  |

| A1  | 0.00        | 0.05 |  |  |  |  |

| A3  | 0.20 REF    |      |  |  |  |  |

| b   | 0.18        | 0.30 |  |  |  |  |

| D   | 3.00        | BSC  |  |  |  |  |

| D2  | 1.65        | 1.85 |  |  |  |  |

| Е   | 3.00        | BSC  |  |  |  |  |

| E2  | 1.65        | 1.85 |  |  |  |  |

| е   | 0.50 BSC    |      |  |  |  |  |

| κ   | 0.20        |      |  |  |  |  |

| L   | 0.30        | 0.50 |  |  |  |  |

查询"NCN2500MNR2G"供应商

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use payes that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunit//Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082–1312 USA Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.