- Instruction Cycle Time: — 132 ns . . . (TMS34010-60) - 160 ns . . . (TM\$34010-50) - 200 ns . . . (TMS34010-40)

- Fully Programmable 32-Bit General-Purpose Processor with 128-Megabyte Address Range

- Pixel Processing, XY Addressing, and Window Checking Built into the Instruction

- Programmable 1, 2, 4, 8, or 16-Bit Pixel Size with 16 Boolean and 6 Arithmetic Pixel Processing Options (Raster-Ops)

- 30 General-Purpose 32-bit Registers and 32-bit Stack Pointer

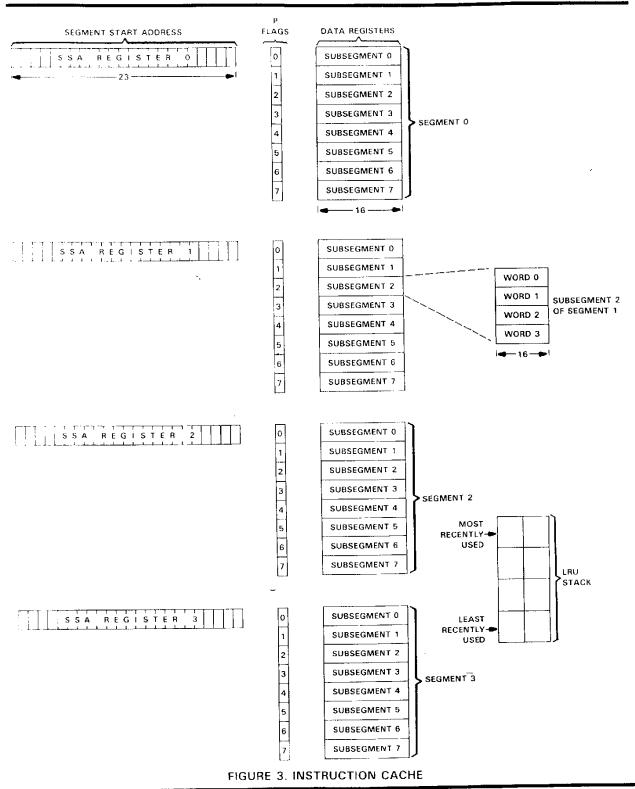

- 256-Byte LRU On-Chip Instruction Cache

- Direct Interfacing to Both Conventional **DRAM and Multiport Video RAM**

- Dedicated 8/16-Bit Host Processor Interface and HOLD/HLDA Interface

- Programmable CRT Control (HSYNC, VSYNC, BLANK)

- High-Level Language Support

- Full Line of Hardware and Software Development Tools Including a "C" Compiler

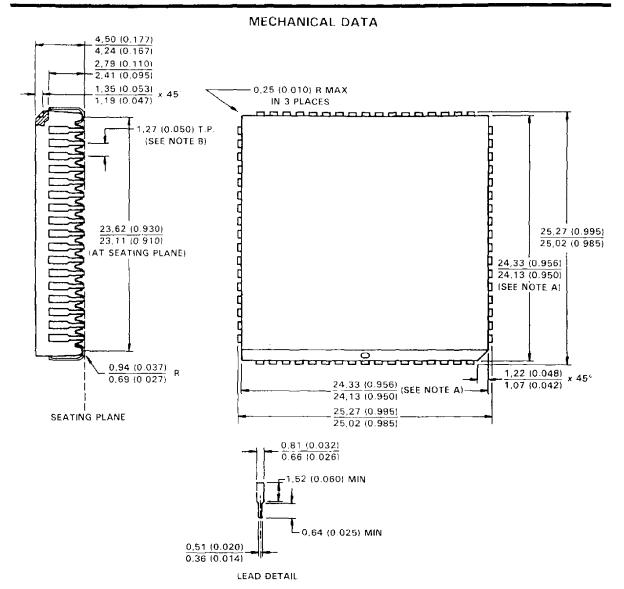

- 68-Leaded Packaging (PLCC)

- 5-Volt CMOS Technology

## description

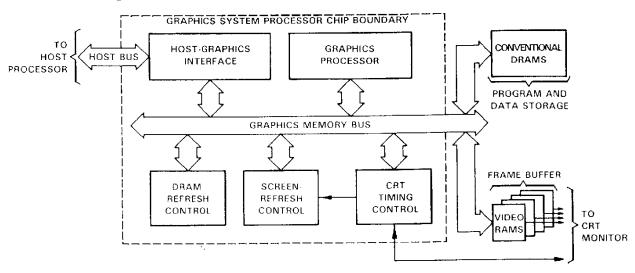

The TMS34010 Graphics System Processor (GSP) is an advanced high-performance CMOS 32-bit microprocessor optimized for graphics display systems. With a built-in instruction cache, the ability to simultaneously access memory and registers, and an instruction set designed specifically for raster graphics operation, the TMS34010 provides user-programmable control of the CRT interface as well as the memory interface (both standard DRAM and multiport video RAM). The 1-gigabit address space is completely bitaddressable on bit boundaries using variable width data fields (1 to 32 bits). Additional graphics addressing modes support 1, 2, 4, 8, and 16-bit wide pixels. The TMS34010 is exceptionally well-supported by graphics software interface standards such as TIGA, MS-Windows, the X Window System, DGIS, and CGI, as well as a full line of hardware and software support tools. Current support is highlighted in the TMS34010 Third Party Reference Guide (literature number SPVB066C).

## architecture

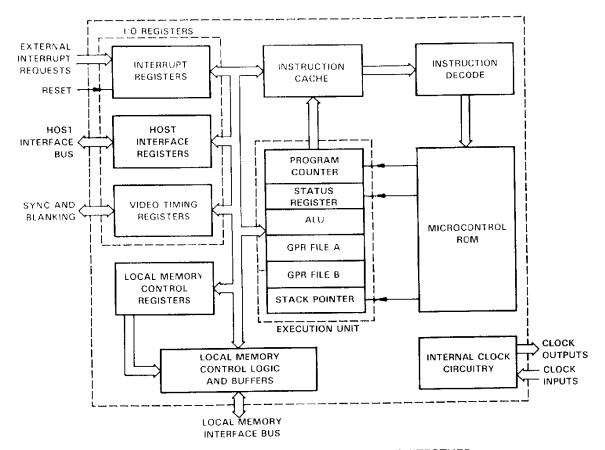

The TMS34010 is a CMOS 32-bit processor with hardware support for graphics operations such as PixBlts traster ops) and curve-drawing algorithms. Also included is a complete set of general-purpose instructions with addressing tuned to support high-level languages. In addition to its ability to address a large external memory range, the TMS34010 contains 30 general-purpose 32-bit registers, a hardware stack pointer

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SPVS002C - JUNE 1986 - REVISED JUNE 1991

and a 256-byte instruction cache. On-chip functions include 28 programmable I/O registers that contain CRT control, input/output control, and instruction parameters. The TMS34010 directly interfaces to dynamic RAMs and video RAMs and generates video monitor control signals. It also accommodates a conventional HOLD/HLDA shared access as well as a separate, generalized interface for communicating with any standard host processor.

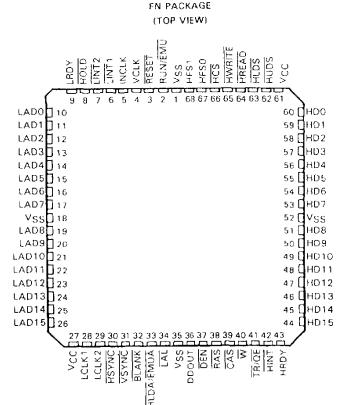

## pin descriptions

| PI!            | N I           |     | DECCRIPTION                                    |  |  |  |  |  |

|----------------|---------------|-----|------------------------------------------------|--|--|--|--|--|

| NAME           | NUMBER        | 1/0 | DESCRIPTION                                    |  |  |  |  |  |

|                |               |     | Host Interface Bus Pins                        |  |  |  |  |  |

| <del>HCS</del> | 66            | ĺ   | Host chip select                               |  |  |  |  |  |

| HDO-HD15       | 44-51, 53-60  | I/O | Host bidirectional data bus                    |  |  |  |  |  |

| HESO, HES1     | 67, 68        | 1   | Host function select                           |  |  |  |  |  |

| HINŤ           | 42            | Ö   | Fost interrupt request                         |  |  |  |  |  |

| HLDS           | 63            | 1   | Host lower data select                         |  |  |  |  |  |

| HUDS           | 62            |     | Host upper data select                         |  |  |  |  |  |

| HRDY           | 43            | Ö   | Host ready                                     |  |  |  |  |  |

| HREAD          | 64            |     | Host read strobe                               |  |  |  |  |  |

| <b>HWRITE</b>  | 65            |     | Host write strobe                              |  |  |  |  |  |

|                | :             |     | Local Bus Interface Pins                       |  |  |  |  |  |

| RAS            | 38            | O   | Local row-address strobe                       |  |  |  |  |  |

| CAS            | 39            | O   | Local column-address strobe                    |  |  |  |  |  |

| DDOUT          | 36            | O   | Local data direction out                       |  |  |  |  |  |

| DÉÑ            | 37            | О   | Local data enable                              |  |  |  |  |  |

| LADO LAD15     | 10-17, 19 26  | FO  | Local address/data bus                         |  |  |  |  |  |

| LAL            | 34            | O   | Local address latched                          |  |  |  |  |  |

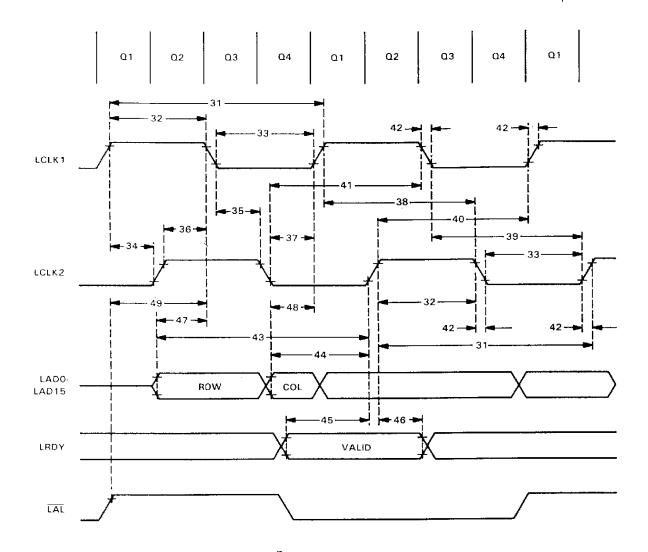

| LCLK1, 1 CLK2  | 28, 29        | 0   | Local output clocks                            |  |  |  |  |  |

| (INT 1, EIN 2  | 6, 7          | 1   | Local interrupt request pins                   |  |  |  |  |  |

| YCRJ           | 9             | 1   | Local ready                                    |  |  |  |  |  |

| TR:OF          | 41            | Э   | Local shift register transfer or output enable |  |  |  |  |  |

| $\overline{W}$ | 40            | 0   | Local write strobe                             |  |  |  |  |  |

| :NCLK          | 5             | 1   | Input clock                                    |  |  |  |  |  |

|                |               |     | Hold and Emulation                             |  |  |  |  |  |

| ਜ <b>ਹਿ D</b>  | 8             | I.  | Holo request                                   |  |  |  |  |  |

| RUN/EMU        | 2             | l I | Run/Not emulate                                |  |  |  |  |  |

| HLDA/EMUA      | 33            | 0   | Hold acknowledge or emulate acknowledge        |  |  |  |  |  |

|                |               |     | Video Timing Signals                           |  |  |  |  |  |

| BLANK          | 32            | 0   | Blanking                                       |  |  |  |  |  |

| HSYNC          | 30            | 1/0 | Horizontal sync                                |  |  |  |  |  |

| VCLK           | 4             | l   | Video clock                                    |  |  |  |  |  |

| VSYNC          | 31            | EO. | Vertical sync                                  |  |  |  |  |  |

|                |               |     | Miscellaneous                                  |  |  |  |  |  |

| RESET          | 3             | ,   | Reset                                          |  |  |  |  |  |

| Ycc            | 27. 61        |     | Nominal 5-volt power supply                    |  |  |  |  |  |

| Vss -          | 1, 18, 35, 52 | [   | Ground                                         |  |  |  |  |  |

#### system block diagram

FIGURE 1. TMS34010 INTERNAL ARCHITECTURE

SPVS002C - JUNE 1986 - REVISED JUNE 1991

The TMS34010 provides single-cycle execution of most common integer arithmetic and Boolean operations from its instruction cache. Additionally, the TMS34010 incorporates a hardware barrel shifter that provides a single state bidirectional shift and rotate function for 1 to 32 bits.

A microcoded local memory controller supports pipelined memory write operations of variable-size fields that can be performed in parallel with subsequent instruction execution.

TMS34010 graphics processing hardware supports pixel and pixel-array processing capabilities for both monochrome and color systems that have a variety of pixel sizes. The hardware incorporates two-operand raster operations with Boolean and arithmetic operations, XY addressing, window clipping, window checking operations, 1 to n bits per pixel transforms, transparency, and plane masking. The architecture further supports operations on single pixels (PIXT instructions) or on two-dimensional pixel arrays of arbitrary size (PixBlts).

The TMS34010's flexible graphics processing capabilities allow software-based graphics algorithms without sacrif cing performance. These algorithms include: arbitrary window size, custom incremental curve drawing, and two-operand raster operations.

#### register files

Boolean, arithmetic, byte, and field move instructions operate on data within the TMS34010's general-purpose register files. The TMS34010 contains thirty-one 32-bit registers, including a system stack pointer (SP). The SP is accessible to both Register File A and B as the sixteenth register. Transfers between registers and memory are facilitated via a complete set of field MOVE instructions with selectable field sizes. Transfers between registers are facilitated via the MOVE instruction.

The fifteen general-purpose registers in Register File A are used for high-level language support and assembly language programming. The fifteen registers in Register File B are dedicated to special functions during PixBlts and other pixel operations, but can be used as general-purpose registers at other times.

FIGURE 2. REGISTER FILES A AND B

# program counter (PC)

The TMS34010's 32-bit program counter register points to the next instruction-stream word to be fetched. Since instruction words are aligned to 16-bit boundaries, the four LSBs of the PC are always zero.

#### instruction cache

An on-chip instruction cache contains 256 bytes of RAM and provides fast access to instructions. It operates automatically and is transparent to software. The cache is divided into four 64-byte segments. Associated with each segment is a 23-bit segment address register to identify the addresses in memory corresponding to the current contents of the cache segment. Each cache segment is further partitioned into eight subsegments of four words each. Each subsegment has associated with it a present (P) flag to indicate whether the subsegment contains valid data.

SPV\$002C - JUNE 1986 -- REVISED JUNE 1991

SPVS002C - JUNE 1986 - REVISED JUNE 1991

The cache is loaded only when an instruction requested by the TMS34010 is not already contained within the cache. A least-recently-used (LRU) algorithm is used to determine which of the four segments of the cache is overwritten with the new data. For this purpose, an internal four-by-two LRU stack is used to keep track of cache usage.

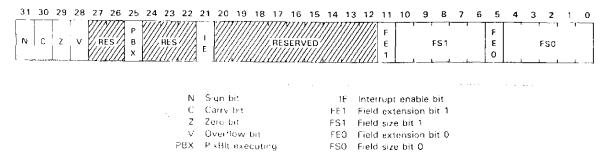

#### status register

The status register (ST) is a special-purpose 32-bit register dedicated to status codes set by the results of implicit and explicit compare operations and parameters used to specify the length and behavior of fields 0 and 1.

FIGURE 4. STATUS REGISTER

# fields, bytes, pixels, and pixel arrays

A 26-bit address output by the TMS34010 selects a 16-bit word of physical memory; logically, however, the TMS34010 views memory data as fields addressable at the bit level. Primitive data types supported by the TMS34010 include: bytes, pixels, two 1- to 32-bit fields, and user-defined pixel arrays.

Fields 0 and 1 are specified independently to be from 1 to 32 bits in length. Bytes are special 8-bit cases of the field data type, while pixels are 1, 2, 4, 8 or 16 bits in length. In general, fields (including bytes) may start and terminate on arbitrary bit boundaries; pixels must pack evenly into 16-bit words.

## pixel operations

Pixel arrays are two-dimensional data types of user-defined width, height, pixel depth (number of bits per pixel), and pitch (distance between rows). A pixel or pixel array may be accessed by means of either its memory address or its XY coordinates. Transfers of individual pixels or pixel blocks are influenced by the pixel processing, transparency, window checking, plane masking, or corner adjust operations selected.

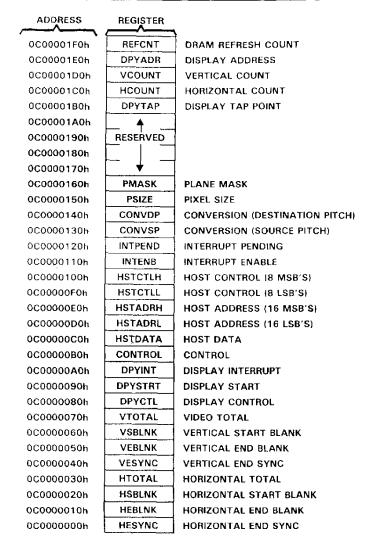

### I/O registers

The GSP contains an on-chip block of fwenty-eight 16-bit I/O registers mapped into the TMS34010's memory address space. They can be accessed either by the TMS34010's CPU or by the host processor via the host interface. The I/O registers contain control parameters necessary to configure the operation of the following interfaces: interface to host processor (5 I/O registers), interface to local memory (6 registers), video timing and screen refresh functions (15 registers), and externally and internally generated interrupts (2 registers). The I/O registers also furnish status information on these interfaces.

FIGURE 5. I/O REGISTERS

#### host interface registers

The host interface registers are provided for communications between the TMS34010 and the host processor. The registers are mapped into five of the I/O register locations accessible to the TMS34010. These same registers are mapped into four locations in the GSP interface to the host.

One of the registers is devoted to host interface control functions such as the passing of interrupt requests and 3-bit status codes from host to TMS34010 and from TMS34010 to host. Other control functions available to the host processor include flushing the instruction cache, halting the TMS34010, and transmitting a non-maskable interrupt request to the TMS34010.

The remaining host registers are used for block transfers between the TMS34010 and host processor. The host uses these registers to indirectly access blocks within the TMS34010's local memory. Two of the 16-bit registers contain the 32-bit address of the current word location in memory. Another 16-bit register buffers data transferred to and from the memory by the host processor. The host interface can be programmed to automatically increment the pointer address following each transfer to provide the host with rapid access to a block of sequential addresses.

#### memory interface control registers

Six of the I/O registers are dedicated to various local memory interface functions including:

- · Frequency and type of DRAM refresh cycles

- Pixel size

- · Masking (write protection) of individual color planes

- Various pixel access control parameters

- Window checking mode

Boolean or arithmetic pixel processing operation

- Transparency

- -- PixBlt direction control

#### video timing and screen refresh

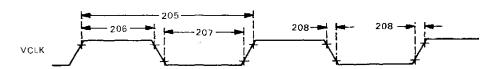

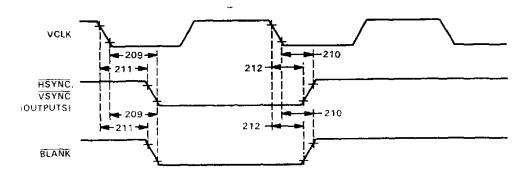

Fourteen I/O registers are dedicated to video timing and screen refresh functions. The TMS34010 generates the horizontal sync (HSYNC), vertical sync (VSYNC), and blanking (BLANK) signals used to drive a video monitor in a graphics system. These signals are controlled by means of a set of programmable video timing i C registers and are based on the input video clock, VCLK, VCLK does not have to be synchronous with respect to INCLK, the TMS34010's CPU input clock.

The TMS34010 directly supports multiport video RAMs (VRAMs) by generating the memory-to-register load cycles necessary to refresh the display being shown on the video monitor. The memory locations from which display information is taken, as well as the number of horizontal scan lines displayed between memory-to-register load cycles, are programmable. VRAM tap point addresses are also fully programmable to support horizontal panning.

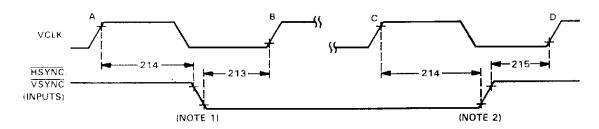

The TMS34010 supports various screen resolutions and either interlaced or noninterlaced video. The TMS34010 can optionally be programmed to synchronize to externally generated sync signals so that graphics images created by the TMS34010 can be superimposed upon images created externally. The external sync mode can also be used to synchronize the video signals generated by two or more TMS34010 chips in a multiple-TMS34010 graphics system.

#### interrupt interface registers

Two dedicated I/O registers monitor and mask interrupt requests to the TMS34010, including two externally generated interrupts and three internally generated interrupts. An internal interrupt request can be generated on one of the following conditions:

- Window violation: an attempt has been made to write a pixel to a location inside or outside a specified window boundary.

- · Host interrupt: the host processor has set the interrupt request bit in the host control register.

- Display interrupt: a specified line number in the frame has been displayed on the screen.

A nonmaskable interrupt occurs when the host processor sets a particular control bit in the host interface registers. The TMS34010 reset function is controlled by a dedicated pin.

#### memory controller/local memory interface

The memory control or manages the TMS34010's interface to the local memory and automatically performs the bit alignment and masking necessary to access data located at arbitrary bit boundaries within memory. The memory controller operates autonomously with respect to the CPU. It has a "write queue" one field (1 to 32 bits) deep that permits it to complete the memory cycles necessary to insert the field into memory without delaying the execution of subsequent instructions. Only when a second memory operation is required before the memory controller has completed the first operation is the TMS34010 forced to defer instruction execution.

The TMS34010 directly interfaces to all standard dynamic RAMs and, in particular to JEDEC standard 64K and 256K video RAMs such as the TMS4161 and TMS4461 Multiport VRAMs. The TMS34010 memory interface consists of a triple-multiplexed address/data bus plus the associated control signals. Row address, column address, and data are multiplexed over the same address/data lines. DRAM refresh is supported with a variety of modes including  $\overline{CAS}$  before  $\overline{RAS}$  refresh.

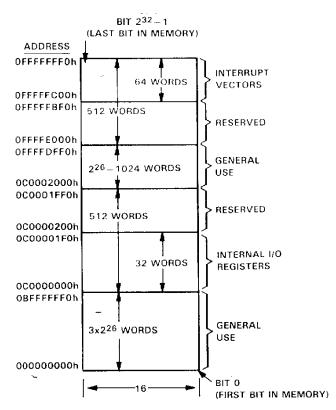

## TMS34010 memory map

From the programmer's point of view, the TMS34010 treats data and instructions as residing in the same memory space.

FIGURE 6. MEMORY MAP

SPVS002C JUNE 1986 -- REVISED JUNE 1991

#### instruction set

The TMS34010 instructions fall into three categories. The *graphics instructions* manipulate pixel data, accessed via memory addresses or XY coordinates. They provide support for graphics operations such as array and raster ops, pixel processing, windowing, plane masking, and transparency. The *move instructions* comprehend bit addressing and field operations; they manipulate fields of data using linear addressing for transfer to and from memory and the register file. The TMS34010 *general-purpose instructions* provide a complete set of arithmetic and Boolean operations on the register file as well as general program control and data processing. Partial timing information is provided in the table below. The two values given for jump instructions in the Minimum Cycles column indicate the jump and no-jump conditions, respectively. Full timing information can be obtained in the *TMS34010 User's Guide* (number SPVU001B).

The following abbreviations are used below in the opcodes: S (source register), D (destination register), R (register file select), F (field select), K (constant), M (cross A/B file boundary), Z (draw option), code (jump select code), X (don't care), N (trap select and stack adjust), RS (source register), RD (destination register), xxxx (address displacement), IL (32-bit immediate operand), and IW (16-bit immediate operand).

#### **GRAPHICS INSTRUCTIONS**

| SYNTAX              | DESCRIPTION                                   | NO.<br>WORDS | MINIMUN |      | 16-BIT | OPCOD | E    | ; | STA<br>BI | TU:<br>TS | S |

|---------------------|-----------------------------------------------|--------------|---------|------|--------|-------|------|---|-----------|-----------|---|

|                     |                                               |              |         | MSB  |        |       | LSB  |   |           |           |   |

| ADDXY Rs, Rd        | Add Registers in XY Mode                      | 1            | 1       | 1110 | 000S   | SSSR  | DDDD | N | С         | Z         | V |

| CMPXY Rs, Rd        | Compare X and Y Halves of Registers           | 1            | 3       | 1110 | 0108   | SSSR  | GDDD | N | С         | Z         | ν |

| CPW Rs, Rd          | Compare Point to Window                       | 1            | 1       | 1110 | 0115   | SSSR  | DDDD | _ |           | _         | V |

| CVXYL Rs, Rd        | Convert XY Address to Linear Address          | 1            | 3       | 1110 | 1005   | SSSR  | dada | _ |           | _         |   |

| DRAV Rs, Rd         | Draw and Advance                              | 1            | t       | 1111 | 0118   | SSSR  | DDDD | _ | _         | _         | V |

| FILL L              | Fill Array with Processed Pixels: Linear      | 1            | †       | 0000 | 1111   | 1100  | 0000 |   | _         |           |   |

| FILL XY             | Fili Array with Processed Pixels: XY          | 1            | ‡       | 0000 | 1111   | 1110  | 0000 | _ | •         | _         | V |

| LINE Z              | Line Draw                                     | 1            | Ť       | 1101 | 1111   | Z001  | 1010 | _ | _         | _         | ٧ |

| MOVX As, Rd         | Move X Half of Register                       | 1            | 1       | 1110 | 1108   | SSSR  | aaaa |   |           | -         |   |

| MOVY Rs, Rd         | Move Y Half of Register                       | 1            | 1       | 1110 | 1118   | SSSR  | DOOD |   | _         | _         | - |

| PIXBLT B,L          | Pixel Block Transfer: Binary to Linear        | 1            | t       | 0000 | 1111   | 1000  | 0000 |   |           | _         |   |

| PIXBLT B, XY        | Pixel Block Transfer and Expand: Binary to XY | 1            | †       | 0000 | 1111   | 1010  | 0000 |   |           | _         | V |

| PIXBLT L.L          | Pixel Block Transfer: Linear to Linear        | 1            | †       | 0000 | 1111   | 0000  | 0000 | _ |           | _         |   |

| PIXBLT L,XY         | Pixel Block Transfer: Linear to XY            | 1            | t       | 0000 | 1111   | 0010  | 0000 | _ | _         | _         | ٧ |

| PIXBLT XY, L        | Pixel Block Transfer: XY to Linear            | 1            | †       | 0000 | 1111   | 0100  | 0000 | _ | _         | _         |   |

| PIXBLT XY,XY        | Pixel Block Transfer: XY to XY                | 1            | †       | 0000 | 1111   | 0110  | 0000 | _ |           | _         | V |

| PIXT Rs, *Rd        | Pixel Transfer: Register to Indirect          | 1            | †       | 1111 | 100S   | SSSR  | DDDD | - | _         | _         |   |

| PIXT Rs, *Rd.XY     | Pixel Transfer: Register to Indirect XY       | 1            | t       | 1111 | 000S   | SSSR  | DDDD | ~ | _         | -         | ٧ |

| PIXT *Rs, Rd        | Pixel Transfer: Indirect to Register          | 1            | 4       | 1111 | 101S   | SSSR  | DDDD |   | _         | _         | - |

| PIXT *Rs,*Rd        | Pixel Transfer: Indirect to Indirect          | 1            | †       | 1111 | 1108   | SSSR  | DDDD | _ | _         | _         | _ |

| PIXT *Rs.XY. Rd     | Pixel Transfer: Indirect XY to Register       | 1            | 6       | 1111 | 0015   | SSSR  | DDDD | _ | _         |           | ~ |

| PIXT *Rs.XY, *Rd XY | Pixel Transfer: Indirect XY to Indirect XY    | 1            | †       | 1111 | 0108   | SSSR  | DDDD | _ |           | _         | V |

| SUBXY Rs.Rd         | Subtract Registers in XY Mode                 | 1            | 1       | 1110 | 0015   | SSSR  | DDDD | Ν | С         | Z         | ٧ |

<sup>\*</sup>Number of cycles depends on pixel size an/or pixel array size and graphics option selected. See TMS34010 User's Guide (SPVU001B)

SPVS002C -- JUNE 1986 - REVISED JUNE 1991

# MOVE INSTRUCTIONS

|                                |                                                                    | NO.    | MINIMUM |                                         | STATUS   |

|--------------------------------|--------------------------------------------------------------------|--------|---------|-----------------------------------------|----------|

| SYNTAX                         | DESCRIPTION                                                        | WORDS  | CYCLES  | 16-BIT OPCODE  MSB LSB                  | BITS     |

| MOVB Rs.*Rd                    | Maria Distance Description to 1. Hours                             | 1      | 1       | 1000 110S SSSR DDDD                     |          |

| MOVB *Rs, Rd                   | Move Byte: Register to Indirect                                    | 1      | t t     | 1000 1115 SSSR DDDD                     |          |

| MOVB *Rs, *Rd                  | Move Byte: Indirect to Register  Move Byte: Indirect to Indirect   | 1      | 1       | 1001 110S SSSR DDDD                     |          |

| MOV5 As, "Rd(offset)           | "                                                                  | 2      | t t     | 1010 1105 SSSR DDDD                     |          |

| MOVB *Rs; offset) Rd           | Make Byte: Register to Indirect with offset.                       | 2      | t       | 1010 1115 SSSR DDDD                     |          |

| MOVB "Risothsett, "Rotoffset)  | Move Byte: Indirect with offset, to Register                       | 2      | ·       | 1010 1113 33311 0000                    | 14 – 2 0 |

| VOVE ASSORBET, ROTOTISETS      | Move Byte: ind. with offset, to Ind.                               | 3      | 1       | 1011 110S SSSR DDDD                     |          |

| MOVB Rs.@Dadoress              | with offset                                                        | 3      | t       | 0000 0101 111R SSSS                     |          |

| MCVB @Saddress.Rc              | Move Byte: Register to Absolute                                    | 3      | †       | 0000 0101 111R DDDD                     |          |

| MOVE @Saddress,@Daddress       | Move Byte: Absolute to Register  Move Byte: Absolute to Absolute   | 5<br>5 | t       | 0000 0011 0100 0000                     |          |

| MCVF Rs Rd                     | Move Register to Register                                          | 1      | 1       | 0100 11MS SSSR DDDD                     |          |

| MOVE Rs, *Rd,F                 | Move Field: Register to Indirect                                   | 1      | †       | 1000 00FS SSSR DDDD                     | _        |

| MOVE Rs. 1Rd,1                 | Move Field: Register to Indirect (pre-dec)                         | 1      | †       | 1010 00FS SSSR DDDD                     |          |

| MOVE Rs. *Rd + F               | Move Field: Register to Indirect (pre-dec)                         | 1      | t       | 1001 00FS SSSR DDDD                     |          |

| MOVE 1Rs Rd,F                  | Move Field: Indirect to Register                                   | 1      | †       | 1000 01FS SSSR DDDD                     |          |

| MOVE *Rs,Rd,F                  | Move Field: Indirect (pre-dec) to Register                         | 1      | †       | 1010 01FS SSSR DDDD                     |          |

| MOVE RsRd,F                    | Move Field: Indirect (post-inc) to Register                        | 1      | t       | 1001 01FS SSSR DDDD                     |          |

| MOVE 'Rs 'Rd F                 | Move Field: Indirect to Indirect  Move Field: Indirect to Indirect | 1      | t       | 1000 10FS SSSR DDDD                     |          |

| MOVE 18s - 18d.F               | Move Field Ind. (pre-dec) to Ind. (pre-dec)                        | 1      | 1       | 1010 10FS SSSR DDDD                     |          |

| MOVE TRS - TRd - F             | Move Field: Ind. (post-inc) to Ind. (post-inc)                     | 1      | t       | 1001 10FS SSSR DODD                     |          |

| MOVE Rs * Paraffsett, F        | Move Field: Register to Indirect with offset.                      | 2      | t       | 1011 OOFS SSSR DDDD                     |          |

| MOVE "Rs;offset).Rd,F          | Move Field: Indirect with offset, to Register                      | 2      | t       | 1011 OIFS SSSR DDDD                     |          |

| MOVE *Rs(offset), *Rd - ,F     | Move Field: Ind. with offset, to Ind.                              | •.     |         |                                         |          |

| 11107 12 111107                | (post-inc)                                                         | 2      | t       | 1101 OOFS SSSR DDDD                     | )        |

| MOVE *Rstoffset) *Rd(offset),F | Move Field: Ind. with offset, to Ind.                              | -      |         | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |          |

| 11.012 11.01.000               | with offset.                                                       | 3      | t       | 1011 10FS SSSR DDDD                     | )        |

| MOVE Rs,@Daddress,F            | Move Field: Register to Absolute                                   | 3      | t       | 0000 01F1 100R SSSS                     |          |

| MOVE @Saddress,Rd,F            | Move Field: Absolute to Register                                   | 3      | t       | 0000 01F1 101R DDDD                     | N - Z O  |

| MOVE @Saddress.*Rd+,F          | Move Field: Absolute to Indirect (post-inc)                        | 3      | t       | 1101 01F0 000R DDDD                     | )        |

| MOVE @Saodress.@Daddress F     | Move Field: Absolute to Absolute                                   | 5      | t       | 0000 01F1 1100 0000                     |          |

<sup>\*</sup>Number of cycles depends on field size and alignment. See TMS34010 User's Guide (SPVU001B).

# **GENERAL INSTRUCTIONS**

| PVNITA V               |                                     | NO.   | MINIMUM      |      |        |           | STATUS     |

|------------------------|-------------------------------------|-------|--------------|------|--------|-----------|------------|

| SYNTAX                 | DESCRIPTION                         | WORDS | CYCLES       |      | 16 BIT | OPCODE    | BITS       |

| ADC D4                 |                                     |       |              | MSB  |        | LSB       |            |

| ABS Rd                 | Store Absolute Value                | 1     | 1            | 0000 |        | 100R DDDD | N - Z 0    |

| AOD Rs,Rd              | Add Registers                       | 1     | 1            | 0100 |        | SSSR DDDD | N C Z V    |

| ADDC Rs,Rd             | Add Register with Carry             | 1     | 1            | 0100 | 0015   | SSSR DDDD | N C Z V    |

| ADD: IW.Rd             | Add Immediate (16 Bits)             | 2     | 2            | 0000 | 1011   | OOOR DDDD | N C Z V    |

| ADDI IL,Rd             | Add Immediate (32 Bits)             | 3     | 3            | 0000 | 1011   | 001R DDDD | N C Z V    |

| ADDK K,Rd              | Add Constant (5 Bits)               | 1     | 1            | 0001 | OOKK   | KKKR DDDD | NCZV       |

| AND Rs,Rd              | AND Registers                       | 1     | 1            | 0101 | 0008   | SSSR DDDD | Z -        |

| ANDI IL.Rd             | AND Immediate (32 Bits)             | 3     | 3            | 0000 | 1011   | 100R DDDD | Z -        |

| ANDN Rs,Rd             | AND Register with Complement        | 1     | 1            | 0101 | 0018   | SSSR DDDD | Z -        |

| ANDNI IL,Rd            | AND Not Immediate (32 Bits)         | 3     | 3            | 0000 | 1011   | 100R DDDD | Z -        |

| BTST K.Rd              | Test Register Bit - Constant        | 1     | 1            | 0001 | 11KK   | KKKR DDDD | Z          |

| BTST Rs.Rd             | Test Register Bit Register          | 1     | 2            | 0100 | 1015   | SSSR DDDD | Z -        |

| CLR Rd                 | Clear Register                      | 1     | 1            | 0101 | 011D   | DDDR DDDD |            |

| CLRC                   | Clear Carry                         | 1     | 1            | 0000 | 0011   | 0010 0000 | - 0        |

| CMP Rs.Rd              | Compare Registers                   | 1     | 1            | 0100 |        | SSSR DDDD | NCZV       |

| CMPLIW,Rd              | Compare Immediate (16 Bits)         | 2     | 2            | 0000 |        | O1OR DDDD | NCZV       |

| CMPLIL,Rd              | Compare Immediate (32 Bits)         | 3     | 3            | 0000 | 1011   | 011R DDDD | NCZV       |

| DEC Rd                 | Decrement Register                  | 1     | 1            | 0001 |        | 001R DDDD |            |

| DINT                   | Disable Interrupts                  | 1     | 3            | 0000 |        | 0110 0000 |            |

| DIVS Rs,Rd             | Divide Registers Signed             | 1     | 40           | 0101 |        | SSSR DDDD | N - Z V    |

| DiVU Rs,Rd             | Divide Registers Unsigned           | 1     | 37           | 0101 |        | SSSR DDDD | Z V        |

| EINT                   | Enable Interrupts                   | 1     | 3            | 0000 |        | 0110 0000 |            |

| EXGF Rd,F              | Exchange Field Size                 | 1     | 1            | 1101 |        | OOOR DDDD |            |

| INC Rd                 | Increment Register                  | 1     | 1            | 0001 |        | 001R DDDD |            |

| LMO Rs.Rd              | Leftmost One                        | 1     | 1            |      |        | SSSR DDDD | Z -        |

| MMFM Rs, Register List | Move Multiple Registers from Memory | 2     | Ť            |      |        | 101R DDDD |            |

| MMTM Rd,Register List  | Move Multiple Registers to Memory   | 2     | t            | 0000 |        | 100R DDDD |            |

| MODS Rs.Rd             | Modulus Signed                      | 1     | 40           |      |        | SSSR DDDD | N Z V      |

| MODU Rs,Rd             | Modulus Unsigned                    | 1     | 35           |      |        | SSSR DDDD | Z V        |

| MOVI IW, Rd            | Move Immediate (16 Bits)            | 2     | 2            |      |        | 110R DDDD | N - Z 0    |

| MOVI IL,Rd             | Move_Immediate (32 Bits)            | 3     | 3            | 0000 |        | 111R DDDD | N - Z = 0  |

| MOVK K,Rd              | Move Constant (5 Bits)              | 1     | 1            |      |        | KKKA DDDD | - <b>-</b> |

| MPYS Rs,Rd             | Multiply Registers (Signed)         | 1     | 5 + FS1      |      |        | SSSR DDDD | N - Z -    |

|                        | Worth Garters (Signed)              | '     | _            | 0101 | 1103   | 333R DDDD | N - Z -    |

| MPYU Rs,Rd             | Multiply Registers (Unsigned)       | 1     | 5 + FS1<br>2 | 0101 | 1115   | SSSR DDDD | – - Z ···  |

| NEG Rd                 | Negate Register                     | 1     | 1            | 0000 | 0011   | 101R DDDD | NCZV       |

| NEGB Rd                | Negate Register with Borrow         | 1     | 1            | 0000 | 0011   | 110R DDDD | NCZV       |

| NOP                    | No operation                        | 1     | 1            |      |        | 0000 0000 |            |

| NOT Rd                 | Complement Register                 | 1     | 1            |      |        | 111R DDDD | Z -        |

| OR Rs,Rd               | OR Registers                        | 1     | 1            |      |        | SSSR DDDD |            |

| ORI IL,Rd              | OR Immediate (32 bits)              | 3     | 3            |      |        | 101R DDDD |            |

| RL K,Rd                | Rotate Left - Constant              | 1     | 1            |      |        | KKKR DDDD |            |

| RL Rs,Rd               | Rotate Left - Register              | 1     | 1            |      |        | SSSR DDDD |            |

| SETC                   | Set Carry                           | 1     | 1            |      |        | 1110 0000 |            |

| SETF FS,FE,F           | Set Field Parameters                | 1     | 1,2          |      |        | O1FS SSSS |            |

| SEXT Rd,F              | Sign Extend to Long                 | 1     | 3            |      |        | OOOR DDDD |            |

|                        | · p                                 | •     | -            |      |        |           | _          |

<sup>&</sup>lt;sup>1</sup>Number of cycles depends on number of registers in list and stack alignment. See TMS34010 User's Guide (SPVU001B).

SPVS002C -- JUNE 1986 -- REVISED JUNE 1991

|             |                                          | NO.   | MINIMUM | 1    |        |       |      | 5 | STA | TUS | 5  |

|-------------|------------------------------------------|-------|---------|------|--------|-------|------|---|-----|-----|----|

| SYNTAX      | DESCRIPTION                              | WORDS | CYCLES  |      | 16-BIT | OPCOD | E    |   | BI  | TS  |    |

|             |                                          |       |         | MSB  |        |       | LSB  |   |     |     |    |

| SLA K.Rd    | Shift Left Arithmetic - Constant         | 1     | 3       | 0010 | OOKK   | KKKR  | DDDD | Ν | С   | Z   | ٧  |

| SLA Rs,Rd   | Shift Left Arithmetic Register           | 1     | 3       | 0110 | 000S   | SSSR  | DDDD | N | С   | Z   | V  |

| SEL K,Rd    | Shift Left Logical - Constant            | 1     | 1       | 0010 | 01KK   | KKKR  | DDDD | _ | C   | Z   | _  |

| Sul Rs,Rc   | Shift Left Logical - Register            | 1     | 1       | 0110 | 001S   | SSSR  | DDDD |   | С   | Z   | -  |

| SRA KJRa    | Shift Right Anthmetic Constant           | 1     | 1       | 0010 | 10KK   | KKKR  | DDDD | Ν | C   | Z   | ٠. |

| SRA Rs.Ra   | Shift Right Arithmetic Register          | 1     | 1       | 0110 | 0108   | SSSR  | adda | Ν | C   | Z   | _  |

| SRL K Sa    | Shift Right Logical - Constant           | 1     | 1       | 0010 | 11KK   | KKKR  | ODDO |   | C   | Z.  |    |

| SRL Rs.Rd   | Shift Right Logical Register             | 1     | 1       | 0110 | 0118   | SSSR  | DDDD | _ | C   | Z   | _  |

| SUB Hs Ra   | Subtract Registers                       | 1     | 1       | 0100 | 0105   | SSSR  | DDDD | Ν | C   | 2   | V  |

| SUBB Rs Rd  | Subtract Registers with Borrow           | 1     | 1       | 0100 | 0115   | SSSR  | DDDD | N | С   | Z   | V  |

| SUBI IW, Rd | Subtract Immediate (16 Bits)             | 2     | 2       | 0000 | 1011   | 111R  | DDDD | Ν | С   | Z   | V  |

| SUBI IL,Rd  | Subtract Immediate (32 Bits)             | 3     | 3       | 0000 | 1101   | 000R  | DDDD | Ν | С   | Z   | V  |

| SUBK K.Rd   | Subtract Immediate (5 Bits)              | 1     | 1       | 0001 | 01KK   | KKKR  | adaa | Ν | С   | Z   | V  |

| XOR Rs,Rd   | Exclusively OR Registers                 | 1     | 1       | 0101 | 011S   | SSSR  | aaaa | _ | _   | z   |    |

| XORI IL.Rd  | Exclusively OR Immediate Value (32 Bits) | 3     | 3       | 0000 | 1011   | 110D  | DDDD | _ | _   | Z   | _  |

| ZEXT Rd,F   | Zero Extend to Long                      | 1     | 1       | 0000 | 01F1   | 001R  | DDDD |   |     | Z   |    |

|             |                                          |       |         |      |        |       |      |   |     |     |    |

# PROGRAM CONTROL AND CONTEXT SWITCHING

|                   |                                                 | NO.   | MINIMUN | 4    |        |       |      | 5 | STA | TU | s |

|-------------------|-------------------------------------------------|-------|---------|------|--------|-------|------|---|-----|----|---|

| SYNTAX            | DESCRIPTION                                     | WORDS | CYCLES  |      | 16-BIT | OPCOD | E    |   | ы   | TS |   |

|                   |                                                 |       |         | MSB  |        |       | LSB  |   |     |    |   |

| CALL Rs           | Call Subroutine Indirect                        | 1     | 6       | 0000 | 1001   | 001R  | DDDD | _ |     |    | _ |

| CALLA Address     | Call Subroutine Absolute                        | 3     | 6       | 0000 | 1101   | 0101  | 1111 |   | ~~  | _  | _ |

| CALLR Address     | Call Subroutine Relative                        | 2     | 5       | 0000 | 1101   | 0011  | 1111 |   | -   | _  |   |

| DSJ Rd.Address    | Decrement Register and Skip Jump                | 2     | 3,2     | 0000 | 1101   | 100R  | DDDD | _ | _   | _  |   |

| DSJEQ Rd.Address  | Conditionally Decrement Register and Skip Junip | 2     | 3,2     | 0000 | 1101   | 101R  | DDDD | _ | -   | -  | _ |

| DSJNE Rd, Address | Conditionally Decrement Register and Skip Jump  | 2     | 3,2     | 0000 | 1101   | 110R  | DDDD |   | ~   |    | _ |

| DSJS Rd,Address   | Decrement Register and Skip Jump - Short        | 1     | 2,3     | 0011 | 1Dxx   | xxxR  | DDDD | _ |     |    |   |

| EMU               | Initiate Emulation                              | 1     | 6       | 0000 | 0001   | 0000  | 0000 |   |     | _  | _ |

| EXGPC Rd          | Exchange Program Counter with Register          | 1     | 2       | 0000 | 0001   | 001R  | DDDD |   | _   | _  | - |

| GETPC Rd          | Get Program Counter into Register               | 1     | 1       | 0000 | 0001   | 010R  | DDDD |   | -   |    |   |

| GETST Ro          | Get Status Register into Register               | 1     | 1       | 0000 | 0001   | 100R  | DDDD |   | -   |    |   |

| BAdd Address      | Jump Absolute Conditional                       | 3     | 3,4     | 1100 | code   | 1000  | 0000 | _ |     |    |   |

| JRcc Address      | Jump Relative Conditional                       | 2     | 3,2     | 1100 | code   | 0000  | 0000 | _ | _   | _  | _ |

| JRcc Address      | Jump Relative Conditional - Short               | 1     | 2,1     | 1100 | code   | xxxx  | xxxx | - | *   |    |   |

| JUMP Rs           | Jump Indirect                                   | 1     | 2       | 0000 | 0001   | 011R  | DDDD |   |     | _  |   |

| POPST             | Pop Status Register from Stack                  | 1     | 8       | 0000 | 0001   | 1100  | 0000 | _ | _   | _  | _ |

| PUSHST            | Push Status Register onto Stack                 | 1     | 2       | 0000 | 0001   | 1110  | 0000 |   |     | _  |   |

| PUTST Rs          | Copy Register into Status                       | 1     | 3       | 0000 | 0001   | 101R  | DDDD | N | С   | Z  | ٧ |

| RETI              | Return from Interrupt                           | 1     | 11      | 0000 | 1001   | 0100  | 0000 | Ν | С   | Z  | ٧ |

| RETS (N)          | Return from Subroutine                          | 1     | 7       | 0000 | 1001   | 011N  | NNNN |   | _   | _  | - |

| REV Rd            | Get Revision Number                             | 1     | 1       | 0000 | 0000   | 001R  | DDDD |   | _   | _  |   |

| TRAP N            | Software Interrupt                              | 1     | 16      | 0000 | 1001   | 000N  | NNNN | 0 | 0   | 0  | 0 |

|                   |                                                 |       |         |      |        |       |      |   |     |    |   |

<sup>\*</sup>Where two numbers appear, the first number assumes that the jump is taken, and the second assumes that the jump is not taken.

hardware and software support for the TMS34010

#### PART NUMBER

#### DESCRIPTION

#### TMS340SDK-PC

#### TMS340 Software Developer's Kit

The SDK meets the needs of those developers of TIGA-compatible software applications and drivers who must develop custom extensions to the standard TIGA graphics library. Included in this package are the TMS340 Family Code Generation Tools, TIGA Software Developer's Package, TMS340 Family Graphics Library, and TMS340 C Source Debugger. The software runs on the IBM PC-AT and compatible MS-DOS machines.

TMS340 Family Code Generation Tools: Includes a C compiler, TMS340 assembler, linker, archiver, and ROM utility. These software tools generate code for both the TMS34010 and TMS34020. TMS34082 support is provided.

TIGA Software Developer's Package: Provides the utilities needed by the developer to produce TIGA drivers for software applications.

TMS340 Family Graphics Library: Provides source and object code for the standard TIGA graphics functions. This package provides a convenient starting point for those developing TMS34010 and TMS34020 code for non-TIGA environments. This product replaces two older products: the TMS34010 Math/Graphics Function Library and the TMS34010 Font Library.

TMS340 Family C Source Debugger: Provides symbolic and high-level language facilities for debugging code for the TMS34010 and TMS34020 written in both C and TMS340 assembly language. Runs on any TIGA board.

## TMS340SPK-PC

## TIGA Software Porting Kit

The SPK meets the needs of OEM equipment makers who are porting the TIGA software interface to their TMS34010- and TMS34020-based hardware products. This package contains the complete source code necessary to build and run TIGA on a TMS340-based board. The SPK also contains the TIGA driver for MS Windows 3.0, and the complete TMS340 Software Developer's Kit (described above).

## SPVZ071

## TIGA Driver Developer's Kit

The TIGA DDK meets the needs of those developers of TIGA-compatible software applications and drivers who do not need to develop custom extensions to the standard TIGA graphics library. Included in this package are the TIGA application interface libraries, example programs, and other TIGA-related files and information. All that is needed in addition to the DDK is an IBM-compatible PC, a TIGA board, and a C compiler for MS-DOS machines.

| TMDS3442203018 |  |

|----------------|--|

| TMDS3442213018 |  |

| TMDS3442553008 |  |

TMS340 Family C Compiler for VAX/VMS TMS340 Family C Compiler for VAX TMS340 Family C Compiler for SUN

TMDSTDB10 TMDS3469910000 TMDS3469981000 TMS34010 TIGA Development Board TMS34010 XDS/22 Realtime Hardware Emulator, U.S. TMS34010 XDS/22 Realtime Hardware Emulator, Europe

SPVS002C - JUNE 1986 - REVISED JUNE 1991

SPVS002C - JUNE 1986 - REVISED JUNE 1991

#### reset

Reset puts the TMS34010 into a known initial state. It is entered when the input signal at the RESET pin is asserted low. RESET must remain active low for a minimum of 40 local clock (LCLK1 and LCLK2) periods to ensure that the TMS34010 has sufficient time to establish its initial internal state.

While RESET remains asserted, all outputs are in a known state, no DRAM-refresh cycles take place, and no screen-refresh cycles are performed.

At the low-to-high transition of the RESET signal, the state of the HCS input determines whether the TMS34010 will be halted or begin executing instructions. The TMS34010 may be in one of two modes, host-present or self-bootstrap mode.

#### 1. Host-Present Mode

If HCS is high at the end of reset, TMS34010 instruction execution is halted and remains halted until the host clears the HLT (halt) bit in HSTCTL (host control register). Following reset, the eight RAS-only refresh cycles required to initialize the dynamic RAMs are performed automatically by the TMS34010 memory control logic. As soon as the eight RAS-only cycles are completed, the host is allowed access to TMS34010 memory. At this time, the TMS34010 begins to automatically perform DRAM refresh cycles at regular intervals. The TMS34010 remains halted until the host clears the HLT bit. Only then does the GSP fetch the level-0 vector address from location OFFFFFFE0h and begin executing its reset service routine.

#### 2. Self-Bootstrap Mode

If HCS is low at the end of reset, the TMS34010 first performs the eight RAS-only refresh cycles required to initialize the DRAMs. Immediately following the eight RAS-only cycles, the TMS34010 fetches the level-0 vector address from location OFFFFFEOh, and begins executing its reset service routine.

Unlike other interrupts and software traps, reset does not save previous ST or PC values. This is because the value of the stack pointer just before a reset is generally not valid, and saving its value on the stack is unnecessary. A TRAP 0 instruction, which uses the same vector address as reset, similarly does not save the ST or PC values.

#### asserting reset

A reset is initiated by asserting the RESET input pin at its active-low level. To reset the TMS34010 at power up. RESET must remain active low for a minimum of 40 local clock periods after power levels have become stable. At times other than power up, the TMS34010 is also reset by holding RESET low for a minimum of 40 clock periods. The 40-clock interval is required to bring TMS34010 internal circuitry to a known initial state. While RESET remains asserted, the output and bidirectional signals are driven to a known state.

The TMS34010 drives its  $\overline{\text{RAS}}$  signal inactive high as long as  $\overline{\text{RESET}}$  remains low. The specifications for certain DRAM and VRAM devices, including the TMS4161, TMS4164 and TMS4464 devices, require that the  $\overline{\text{RAS}}$  signal be driven inactive-high for 100 microseconds during system reset. Holding  $\overline{\text{RESET}}$  low for 150 microseconds will cause the  $\overline{\text{RAS}}$  signal to remain high for the 100 microseconds required to bring the memory devices to their initial states. DRAMs such as the TMS4256 specify an initial  $\overline{\text{RAS}}$  high time of 200 microseconds, requiring that  $\overline{\text{RESET}}$  be held low for 250 microseconds. In general, holding  $\overline{\text{RESET}}$  low for t microseconds ensures that  $\overline{\text{RAS}}$  remains high initially for t – 50 microseconds.

SPVS002C - JUNE 1986 REVISED JUNE 1991

# suspension of DRAM-refresh cycles during reset

An active-low level at the RESET pin is considered to be a power-up condition, and DRAM refresh is not performed until RESET goes inactive high. Consequently, the previous contents of the local memory may not be valid after a reset.

#### initial state following reset

While the RESET pin is asserted low, the TMS34010's output and bidirectional pins are forced to the states listed below.

| OUTPUTS DRIVEN TO HIGH LEVEL | OUTPUTS DRIVEN TO LOW LEVEL | BIDIRECTIONAL PINS DRIVEN TO HIGH IMPEDANCE |

|------------------------------|-----------------------------|---------------------------------------------|

| TUODD                        | BLANK                       | HSYNC                                       |

| HRDY                         |                             | VSYNC                                       |

| DEN                          |                             | HD0-HD15                                    |

| t <del>A</del> L             |                             | LADO-LAD15                                  |

| TR/QE                        |                             | ]                                           |

| RAS                          |                             | ļ                                           |

| CAS                          |                             |                                             |

| ₩                            |                             | [                                           |

| HINT                         |                             |                                             |

| HLDA/EMUA                    |                             |                                             |

INITIAL STATE OF PINS FOLLOWING A RESET

Immediately following reset, all I/O registers are cleared (set to 0h), with the possible exception of the HLT bit in the HSTCTL register. The HLT bit is set to 1 if HCS is high just prior to the low-to-high transition of RESET.

Just prior to execution of the first instruction in the reset routine, the TMS34010's internal registers are in the following state:

- General-purpose register files A and B are uninitialized.

- The ST is set to 00000010h.

- The PC contains the 32-bit vector fetched from memory address OFFFFFEOh.

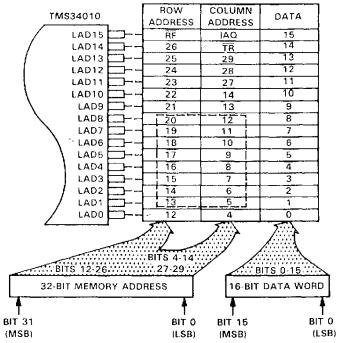

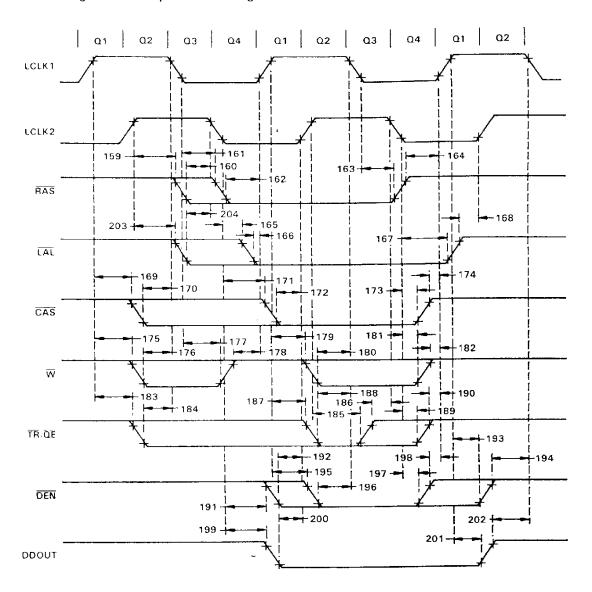

## TMS34010 local memory interface

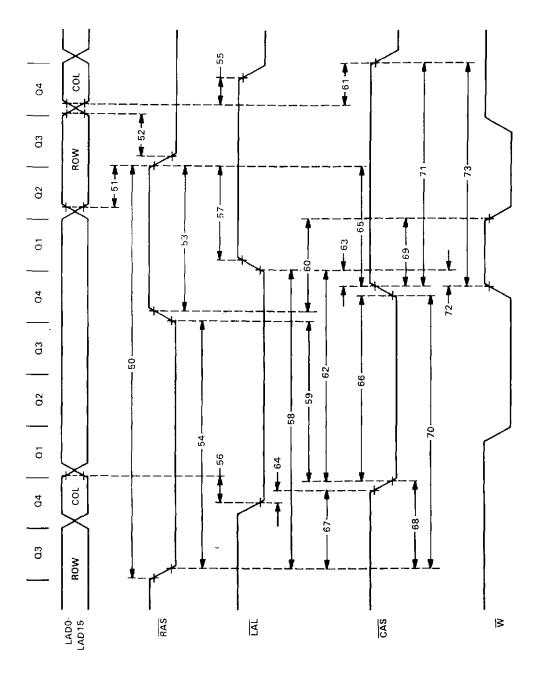

The TMS34010 local memory interface consists of a triple-multiplexed address/data bus on which row addresses, column addresses, and data are transmitted. The associated memory control signals support direct interfacing to both DRAMs and VRAMs. At the beginning of a typical memory cycle, the address is output in multiplexed fashion as a row address followed by a column address. The remainder of the cycle is used to transfer data between the TMS34010 and memory.

# TMS34010 local memory interface

The TMS34010 local memory interface consists of a triple-multiplexed address/data bus on which row addresses, column addresses, and data are transmitted. The associated memory control signals support direct interfacing to both DRAMs and VRAMs. At the beginning of a typical memory cycle, the address is output in multiplexed fashion as a row address followed by a column address. The remainder of the cycle is used to transfer data between the TMS34010 and memory.

RF : DRAM-REFRESH BUS STATUS BIT

1AQ - INSTRUCTION ACQUISITION BUS STATUS BIT

TR × VRAM SHIFT-REGISTER-TRANSFER BUS STATUS BIT

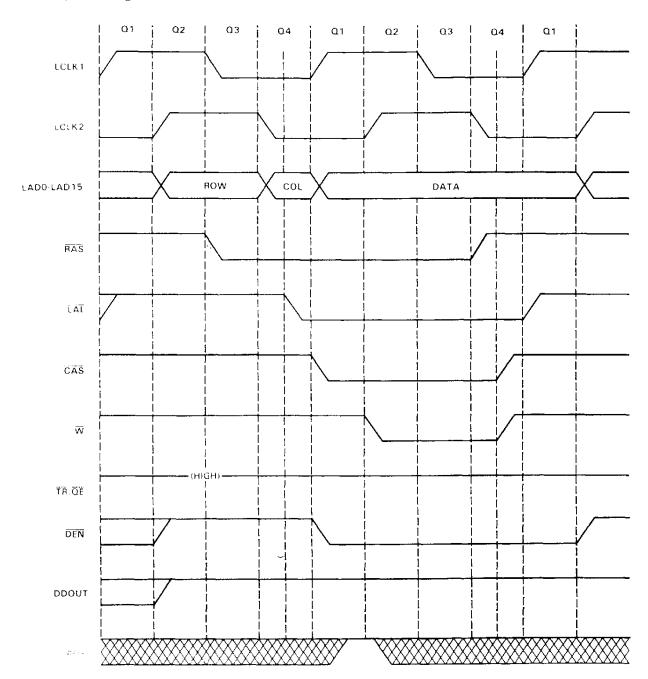

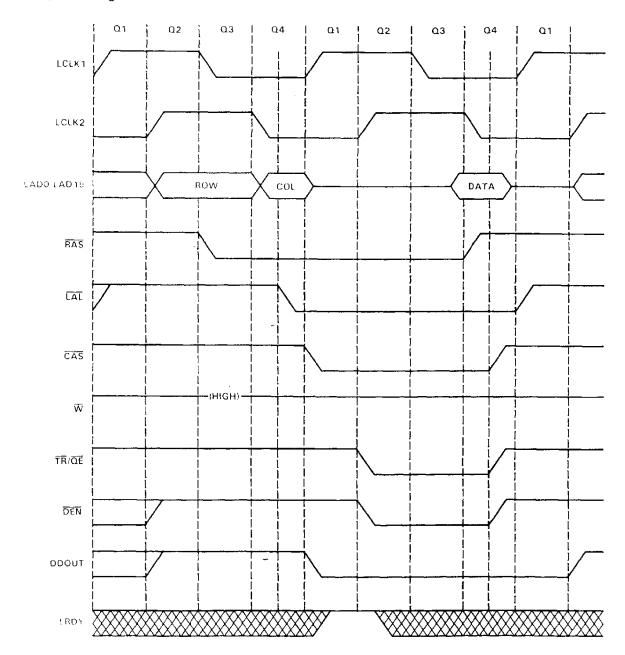

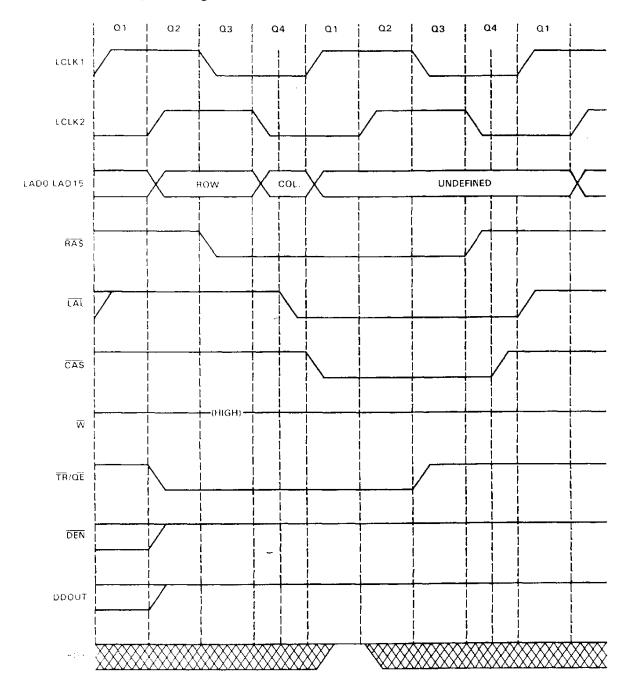

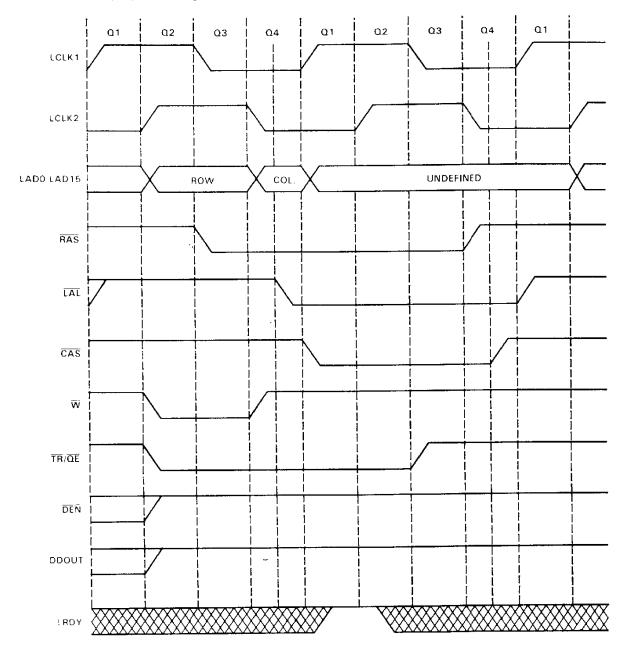

FIGURE 7. TRIPLE MULTIPLEXING OF ADDRESSES AND DATA

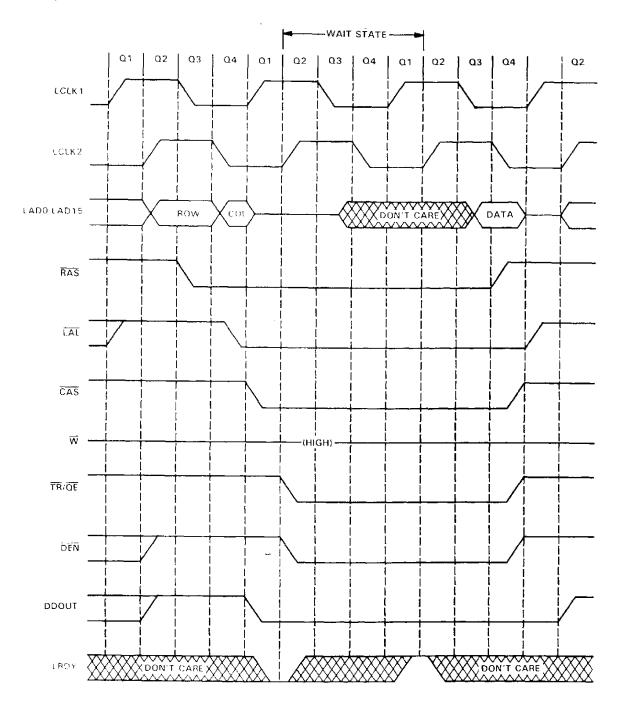

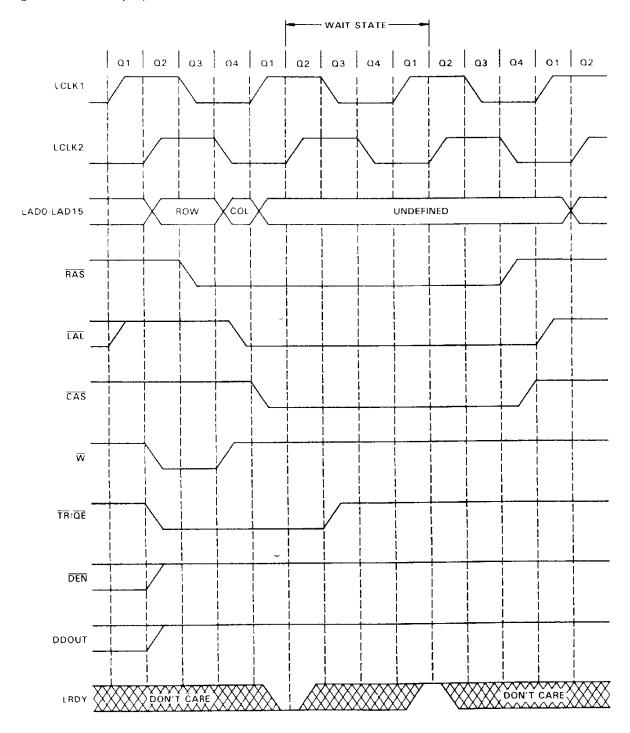

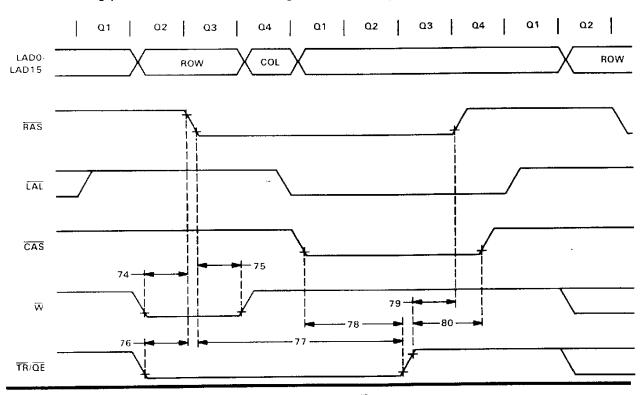

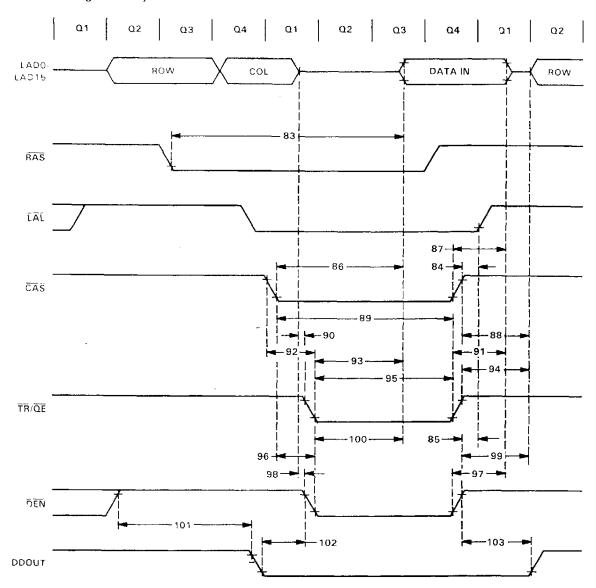

The following types of memory cycles are supported: read, write, VRAM memory-to-register, VRAM register-to-memory, RAS-only DRAM refresh and CAS-before-RAS DRAM refresh. The functional timing for these cycles is shown in the next six figures. Each memory cycle is a minimum of two maching states (a state is one local clock period) in duration. The seventh figure indicates the timing signals output during an internal cycle, i.e., a cycle during which no memory access takes place. An internal cycle is one state in duration.

During a memory cycle, the row address, column address, and data are transmitted over the same physical bus lines. The manner in which logical addresses are output at the memory interface makes external multiplexing hardware unnecessary, while supporting a wide variety of memory configurations. For example, in Figure 7, 16 consecutive address bits (5 through 20) are output on LAD1-LAD8 during the row and column address times. Output along with the address are bus status signals that indicate when DRAM refresh cycles, screen refresh (VRAM memory-to-register) cycles, and instruction fetch cycles are occurring.

SPVS002C JUNE 1986 - REVISED JUNE 1991

The following remarks apply to memory timing in general. A row address is output on LAD0-LAD15 at the start of the cycle, and is valid before and after the fall of RAS. Next a column address is output on LAD0-LAD15. The column address is valid briefly before and after the falling edge of LAL, but is not valid at the falling edge of CAS. The column address is clocked into an external transparent latch to g., a 74AS373 octal latch) on the falling edge of LAL to provide the hold time on the column address required for dynamic RAMs and video RAMs. A transparent latch is required in order that the row address be available at the outputs of the latch during the start of the cycle.

Very large memory configurations may require external buffering of data lines. The  $\overline{\text{DEN}}$  signal serves as the drive-enable signal to external bidirectional buffers, e.g., 74AS245 octal buffers. The DDOUT signal serves as the direction control for the buffers.

When an I/O register is addressed by the TMS34010, a special memory read or write cycle is performed. During this cycle, the external RAS signal falls, but the external CAS remains inactive-high for the duration of the cycle.

The timing shown in the first six functional timing diagrams assumes that the LRDY input remains high during the cycle. The LRDY pin is pulled low by slower memories requiring a longer cycle time. The TMS34010 samples the LRDY input at the end of Q1, as indicated in the figures. If LRDY is low, the LMS34010 inserts an additional state, called a "wait" state, into the cycle. Wait states continue to be inserted until LRDY is sampled at a high level. The cycle then completes in the manner indicated in the functional timing diagrams. A wait state is one local clock period in duration. Three additional timing diagrams provide examples of cycles extended by wait states.

The LRDY input is ignored by the TMS34010 during internal cycles.

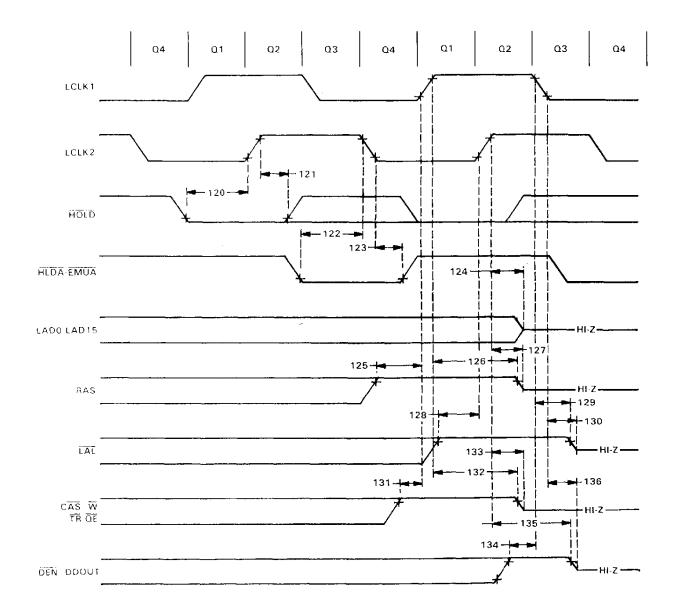

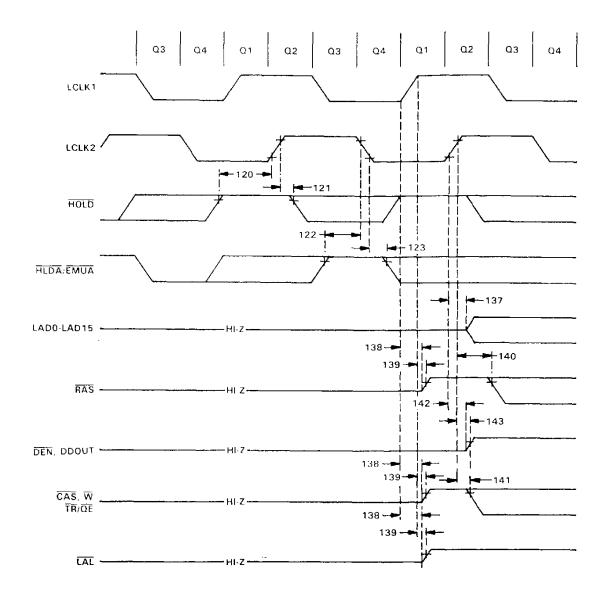

A hold/hold acknowledge capability is also built into the local memory interface to allow external devices to request control of the bus. After acknowledging a hold request, the TMS34010 releases the bus by driving its address data bus and control outputs into high impedance.

SPVS002C JUNE 1986 - REVISED JUNE 1991

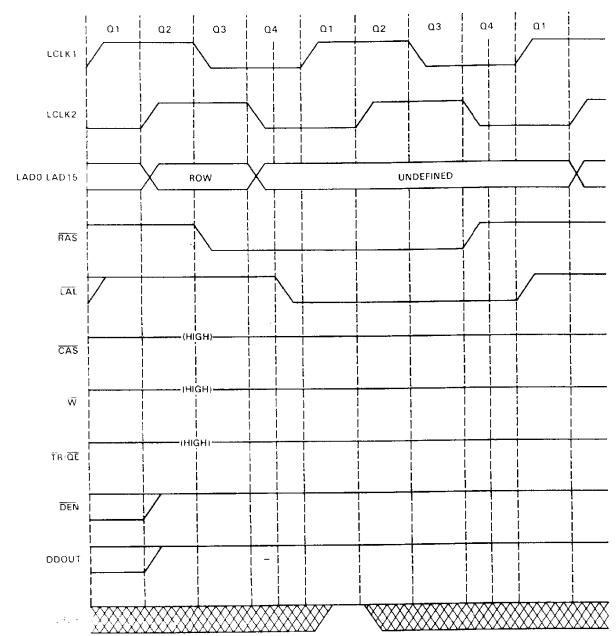

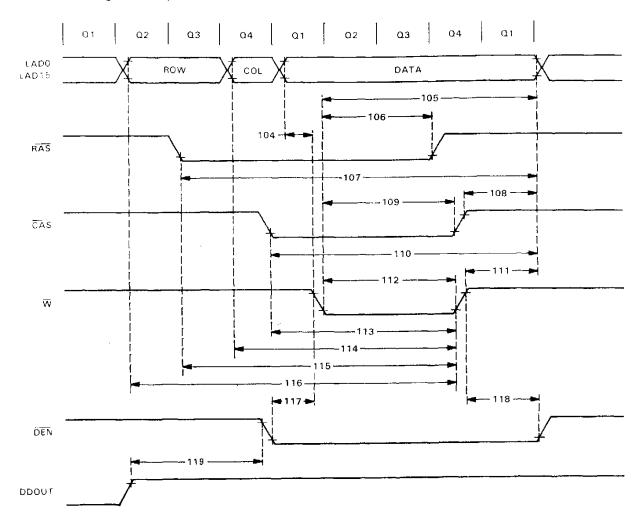

# write cycle timing

SPVS002C JUNE 1986 - REVISED JUNE 1991

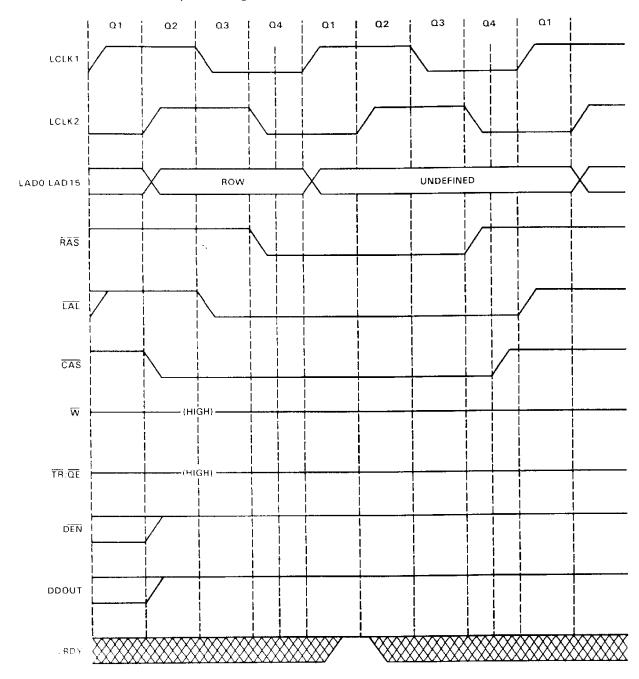

# read cycle timing

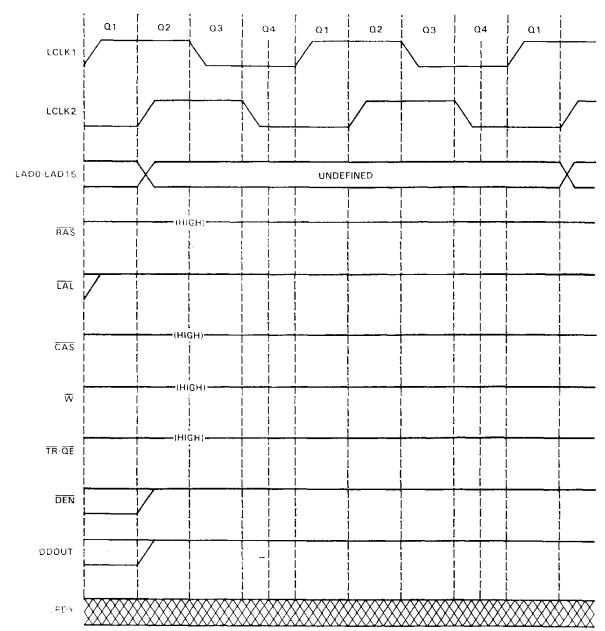

# memory-to-register cycle timing

# register-to-memory cycle timing

SPVS002C - JUNE 1986 - REVISED JUNE 1991

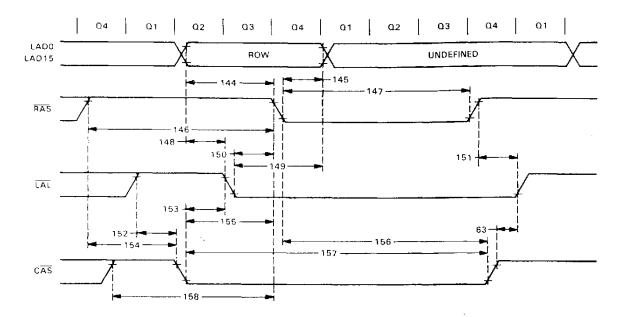

# RAS-only DRAM refresh cycle timing

SPVS002C - JUNE 1986 - REVISED JUNE 1991

# $\overline{\text{CAS}}\text{-before-RAS}$ refresh cycle timing

SPVS002C - JUNE 1986 - REVISED JUNE 1991

# internal cycles back to back

SPVS002C JUNE 1986 - REVISED JUNE 1991

write cycle with one wait state

read cycle with one wait state

SPVS002C - JUNE 1986 - REVISED JUNE 1991

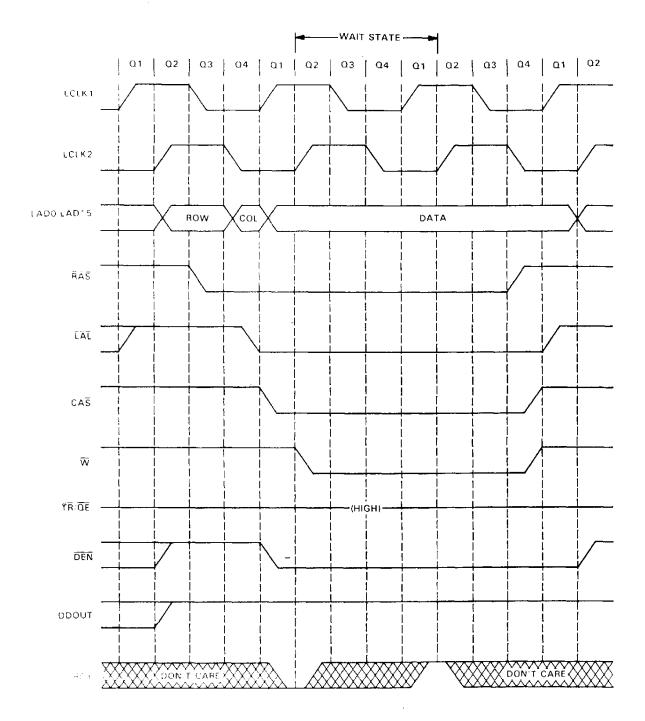

register-to-memory cycle with one wait state

# **GRAPHICS SYSTEM PROCESSOR**

SPVS002C - JUNE 1986 - REVISED JUNE 1991

# absolute maximum ratings over operating free-air temperature range<sup>1</sup>

| Supply voltage, VCC                  | 7 V           |

|--------------------------------------|---------------|

| Input voltage range                  | 0.3 V to 20 V |

| Off-state output voltage range       | -2 V to $7 V$ |

| Operating free-air temperature range | 0°C to 70°C   |

| Storage temperature range            | )°C to 150°C  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating 1.3 Fig. 1.1 and operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" the offices specify about the impred. Exposure to absolute maximum rated conditions for extended periods may affect device reliability contage values are with respect to the VSS pins of the chip.

## recommended operating conditions

|                |                                | MIN  | NOM | MAX   | UNIT |

|----------------|--------------------------------|------|-----|-------|------|

| Vcc            | Supply voltage                 | 4.75 | 5.0 | 5,25  | V    |

| VSS            | Supply voltage <sup>†</sup>    | 0    | 0   | 0     | V    |

| Іон            | High-level output current      |      |     | - 400 | μА   |

| lOr.           | Low-level output current       |      |     | 2.0‡  | mA   |

| T <sub>A</sub> | Operating free-air temperature |      |     | 70    | °C   |

Care should be taken by card designers to provide a minimum inductance path between the VSS pins and system ground in order to minimize VSS noise.

#### DC electrical characteristics

|        | PARAMETER                                      |                            | TEST COM                        | NDITIONS                                         | MIN <sup>†</sup> | TYP <sup>‡</sup> | MAX <sup>†</sup> | UNIT |  |

|--------|------------------------------------------------|----------------------------|---------------------------------|--------------------------------------------------|------------------|------------------|------------------|------|--|

| V.,14§ | 니gh level input<br>voltage, TTL-level          | All inputs except INCLK    | Vcc =                           | V <sub>CC</sub> = 5.0 V                          |                  | v                | CC+0.3           | v    |  |

|        | signal                                         | INCLK                      | ACC = p'O A                     |                                                  | 3.0              | _ V              | CC+0.3           |      |  |

| VIL    | Low level input voltage, TTL-evel              | All inputs except INCLK    |                                 |                                                  | -0.3             |                  | 0.8              |      |  |

|        | signal                                         | INCLK                      |                                 |                                                  | -0.3             |                  | 0.8              |      |  |

| ۷ОН    | High-level output voltage,  H TTL-level signal |                            | VCC = min,                      |                                                  | 2.6              |                  |                  | V    |  |

| ۷O۲    | Low-level output v                             | voltage,                   |                                 | max,                                             |                  | _                | 0.6              | V    |  |

| 10     | High impedance le                              | eakage current,            | V <sub>CC</sub> = max           | V <sub>O</sub> = 2.8 V<br>V <sub>O</sub> = 0.6 V |                  |                  | 20<br>- 20       | μΑ   |  |

| ij     | Input current                                  | All inputs except RUN/EMU§ | V <sub>I</sub> = V <sub>S</sub> | s to V <sub>CC</sub>                             |                  |                  | ± 20             | μΑ   |  |

|        |                                                |                            | V <sub>CC</sub> = ma            | ax, 40 MHz                                       |                  |                  | 125              | 1    |  |

| ICC    | Supply current                                 |                            | VCC = ma                        | ax, 50 MHz                                       |                  |                  | 150              | mA   |  |

| ~-     |                                                |                            | V <sub>CC</sub> = ma            | ax, 60 MHz                                       |                  |                  | 175              | ļ.,  |  |

| $c_1$  | Input capacitance                              |                            |                                 |                                                  |                  | 10               |                  | pF   |  |

| co     | Output capacitano<br>address;data lines        | ·                          |                                 |                                                  |                  | 10               |                  | pF   |  |

<sup>&</sup>quot;For conditions shown as "min" or "max," use the appropriate value specified under "Recommended Operating Conditions.

<sup>&</sup>lt;sup>5</sup>RUN EMU will be no connected in a typical configuration. The nominal pull-up current will be 250 μA.

Dutput current of 2.0 mA is sufficient to drive five low-power Schottky TTL loads or 10 advanced low-power Schottky TTL loads (worst case).

As typical values are at  $V_{CC}=5$  V,  $T_A=25$  °C.

SPVS002C - JUNE 1986 - REVISED JUNE 1991

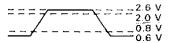

signal transition levels

FIGURE 8. TTL-LEVEL OUTPUTS

TTL-level outputs are driven to a minimum logic-high level of 2.6 volts and to a maximum logic-low level of 0.6 volts. Output transition times are specified as follows.

For a high-to-low transition on a TTL-compatible output signal, the level at which the output is said to be "no longer high" is 2.0 volts, and the level at which the output is said to be "low" is 0.8 volts. For a low-to-high transition, the level at which the output is said to be "no longer low" is 0.8 volts, and the level at which the output is said to be "high" is 2.0 volts.

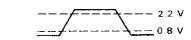

FIGURE 9. TTL-LEVEL INPUTS

Transition times for TTL-compatible inputs are specified as follows. For a high-to-low transition on an input signal, the level at which the input is said to be "no longer high" is 2.2 volts, and the level at which the input is said to be "low" is 0.8 volts. For a low to-high transition on an input signal, the level at which the input is said to be "no longer low" is 0.8 volts, and the level at which the input is said to be "high" is 2.2 volts.

### test measurement

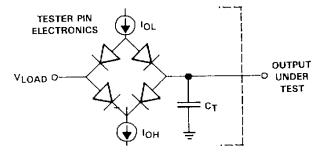

The test load circuit shown in Figure 10 represents the programmable load of the tester pin electronics, which are used to verify timing parameters of TMS34010 output signals.

Where:  $l_{OL} = 2.0 \text{ mA DC}$  level verification (all outputs)

$I_{OH} = 400 \, \mu A \, (all \, outputs)$

$V_{LOAD} = 1.5 V DC$  level verification

0.7 V Timing verification

CT = 65 pF typical load circuit capacitance

FIGURE 10. TEST LOAD CIRCUIT

SPVS002C - JUNE 1986 REVISED JUNE 1991

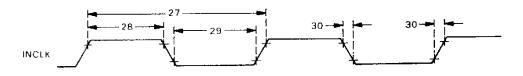

## timing parameter symbology

Timing parameter symbols have been created in accordance with JEDEC Standard 100. In order to shorten the symbols, some of the pin names and other related terminology have been abbreviated as follows:

| ΑL  | LAL             | HS  | HSYNC or VSYNC                            |

|-----|-----------------|-----|-------------------------------------------|

| С   | CAS             | ICK | INCLK                                     |

| CA  | Column address  | LR  | LRDY                                      |

| CK  | LCLK1 and LCLK2 | QE  | TR/QE, when used as output enable         |

| CK1 | LCLK1           | R   | RAS                                       |

| CK2 | LCLK2           | RA  | Row address                               |

| CS  | HCS             | RS  | HREAD                                     |

| D   | Data            | RY  | HRDY                                      |

| DD  | DDOUT           | S   | HREAD or HWRITE                           |

| EN  | DEN             | TR  | TR/QE, when used as shift register enable |

| F   | HFSO, HFS1      | VCK | VCLK                                      |

| HK  | HLDA/EMUA       | W   | ₩                                         |

| HR  | HOLD            | WS  | HWRITE                                    |

Lowercase subscripts and their meaning are:

- a access time

- c cycle time (period)

- d delay time

- h hold time

- su setup time

- t transition time

- t transmon time

- w pulse duration (width)

The following additional letters and symbols and their meaning are:

- H High

- L Low

- V Valid

- Z High impedance

- 1 No longer low

- No longer high

SPVS002C JUNE 1986 -- REVISED JUNE 1991

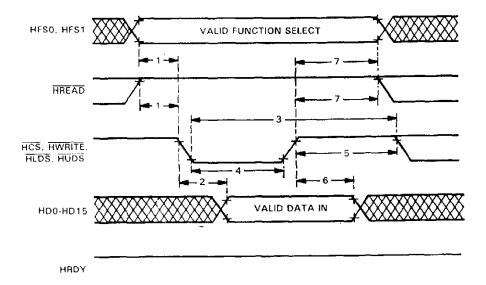

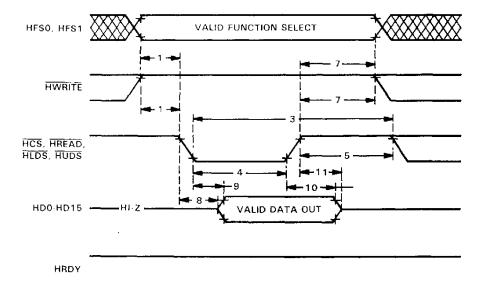

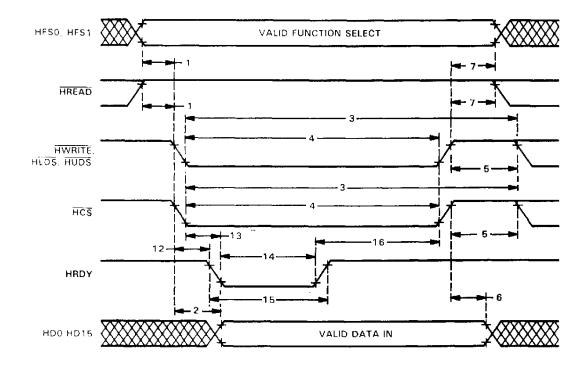

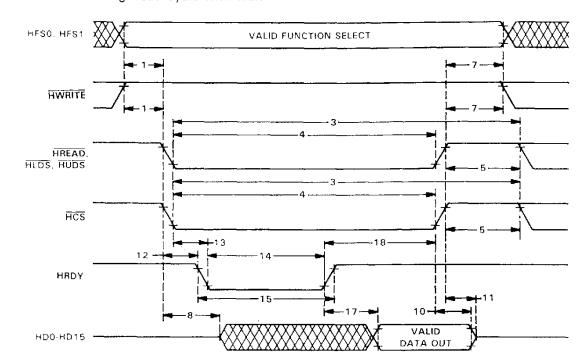

## host interface timing parameters

The timing parameters for host interface signals are shown in the next four figures. The purpose of these figures and the accompanying table is to quantify the timing relationships among the various signals. The explanation of the logical relationships among signals will be found in the *TMS34010 User's Guide* (number SPVU001B).

The write strobe referred to in the following table is the enabling signal during a write to one of the host interface registers (see comment 2 on the next page). Similarly, the read strobe is the enabling signal during a read.

Quarter clock time  $t_Q$ , which appears in the following table, is one quarter of a local output clock period, or twice the input clock period,  $t_{CI(CK)}$ .

| NO. | PARAMETER               |                                                                                    | TMS34010-40 |      | TMS34010-50<br>TMS34010-60 |                 | UNIT |

|-----|-------------------------|------------------------------------------------------------------------------------|-------------|------|----------------------------|-----------------|------|

|     |                         |                                                                                    | MIN         | MAX  | MIN                        | MAX             |      |

| 1   | t <sub>SU</sub> (FV-SL) | Setup time of HWRITE/HREAD high or HFSO, HFS1 valid to read or write strobel       | 10          |      | 10                         |                 | ns   |

| 2   | †d(WSL-DV)              | Delay from write strobe! to data in valid, write cycle                             |             | 2tQ  |                            | 2t <sub>Q</sub> | ns   |

| 3   | <sup>t</sup> d(SL-SL)   | Delay from read or write strobe low to next read or write strobe!                  | 7tQ+10      | -    | 7t <sub>Q</sub> + 10       |                 | ns   |

| 4   | tw(SL)                  | Duration of read or write strobe low                                               | во          |      | 80                         |                 | ns   |

| 5   | ¹d(\$1+ \$L)            | Delay from read or write strobe high to next read or write strobel                 | 60          |      | 60                         |                 | ns   |

| 6   | GWSH DVI                | Hold time of data in valid after write strobe high, write cycle                    | 2           |      | 2                          |                 | ns   |

| 7   | IniSH FVI               | Hold time of HWR(TE/HREAD high or HFSO, HFS1 valid after read or write strobe high | 10          |      | 10                         |                 | ns   |

| 8   | th(RSL-DZ)              | Hold time of data high impedance after read strobel, read cycle                    | O §         |      | 0 §                        |                 | ns   |

| 9   | td(RSL DV)              | Delay from read strobe low to data out valid, read cycle with no wait              |             | 90   |                            | 90              | ns   |

| 10  | tn(RSH-DV)              | Hold time of data out valid after read strobel, read cycle                         | 0           |      | 0                          |                 | пѕ   |

| 11  | lo(RSH DZ)              | Delay from read strobe high to data out high impedance, read cycle                 |             | 30 9 |                            | 30 <sup>§</sup> | กร   |

| 12  | thiCSL-RYHI             | Hold time of HRDY high after HCS1, cycle with wait                                 | 0           |      | 0                          |                 | ns   |

| .3  | d(CSL RYL)              | Delay from HCS low to HRDY low, cycle with wait                                    |             | 40   |                            | 40              | ns   |

| 14  | * WIRYLI                | Pulse duration of HRDY low, cycle with wait                                        |             | Ť    |                            | †               | ns   |

| 1.5 | la:RYL RYH;             | Delay from HRDY) to HRDY high, cycle with wait                                     | 0‡          |      | O‡                         |                 | ns   |

| . 6 | <sup>т</sup> h,RYH-WSL  | Hold time of write strobe low after HRDY*,                                         | 40          | _    | 40                         |                 | ns   |

| 17  | to(RYH DV)              | Delay from HRDY1 to data out valid, read cycle with wait                           |             | 30   |                            | 30              | ns   |

| 18  | th(RYH-RSL)             | Hold time of read strobe low after HRDY1, read cycle with wait                     | 40          |      | 40                         |                 | ns   |

<sup>\*</sup>Parameter 14 is a function of local bus memory contention. This parameter is not tested. Refer to the TMS34010 User's Guide for details.

<sup>\*</sup>Parameter 15 is specified as minimum 0 ns to indicate that a low-going pulse on HRDY can be arbitrarily narrow.

$<sup>\</sup>S$ These values are derived from characterization and are not tested.

## general comments on host interface timing

The following general comments apply to host interface timing:

- 1 The HRDY signal is enabled by an active low level on the HCS input. When HCS is inactive-high, HRDY is forced high regardless of the internal state of the device. Low-going transient pulses on HCS may result in low-going transient pulses on HRDY, but otherwise have no effect unless accompanied by active levels on other control signals.

- 2. A host interface write cycle occurs when HCS, HWRITE, and HLDS are low, or when HCS, HWRITE, and HUDS are low. The combination of these signals defines a write strobe. In either case, the last of the three signals to make the high-to-low transition is the strobe (write strobe) that begins the cycle. The first of the three signals to make the low-to-high transition ends the cycle. Similarly, a host interface read cycle occurs when HCS, HREAD, and HLDS are low, or when HCS, HREAD, and HUDS are low. The combination at these signals define a read strobe. In either case, the last of the three signals to make the high-to-low transition is the strobe (read strobe) that begins the cycle. The first of the three signals to make the low-to-high transition ends the cycle. All access times are specified with respect to the strobing edges that begin and end the cycle.

- 3. During a host interface read or write, HWRITE and HREAD must not be active-low simultaneously.

- 4. Host interface input signals HCS, HUDS, HLDS, HFSO, HFS1, HREAD, and HWRITE are assumed to be asynchronous with respect to the output clocks LCLK1 and LCLK2.

## host interface timing: write cycle with no wait

host interface timing: read cycle with no wait

host interface timing: write cycle with wait

host interface timing: read cycle with wait

SPVS002C - JUNE 1986 - REVISED JUNE 1991

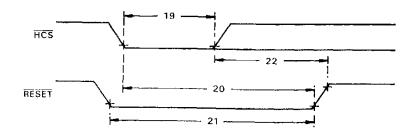

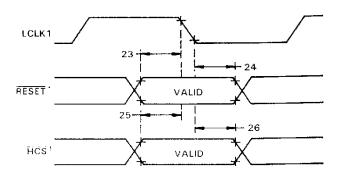

#### reset timing

The timing parameters for device reset are shown in the next two figures. The purpose of these figures is to quantify the timing relationships among the RESET, HCS, and LCLK1 signals. RESET and HCS are asynchronous inputs that are internally synchronized by latches internal to the TMS34010. The timing relationships specified for these signals relative to LCLK1 need be met only to guarantee recognition of a transition of one of these signals at a particular clock edge. The explanation of the logical relationships among signals will be found in the TMS34010 User's Guide.

Quarter clock time  $t_Q$  which appears in the following table, is one quarter of a local output clock period, or twice the input clock period,  $t_C(ICK)$ .

| NO. | PARAMETER                 |                                                                                              | TMS34010-40            |                                   | TMS34010-50<br>TMS34010-60 |                       | UNIT |

|-----|---------------------------|----------------------------------------------------------------------------------------------|------------------------|-----------------------------------|----------------------------|-----------------------|------|

|     |                           |                                                                                              |                        | MAX                               | MIN                        | MAX                   |      |

| 19  | tw(CSL)                   | Duration of HC\$ low to configure GSP to run in self-bootstrap mode                          | 4ta+55                 |                                   | 4t <sub>Q</sub> +55        |                       | กร   |

| 20  | (su(CSL REH)              | Setup time of HCS low to RESET1 to configure the GSP to run in self-bootstrap mode           | 8t <sub>Q</sub> + 55   |                                   | 8t <sub>Q</sub> + 55       |                       | ns   |

| 21  | twiREL:                   | Duration of RESET low to ensure that GSP is properly reset                                   | 160t <sub>Q</sub> - 40 |                                   | 160t <sub>Q</sub> - 40     |                       | ns   |

| 22  | td(CSH-REH)               | Delay from HCS1 to RESET high, end of reset, to configure GSP to run in self-bootstrap mode  |                        | 4t <sub>Q</sub> – 50 <sup>†</sup> |                            | 4ta - 50 <sup>†</sup> | ns   |

| 23  | (su(REV-CK1L)             | Setup time of RESET valid to LCLK11 to guarantee recognition at a particular clock edge      | 40‡                    |                                   | 40‡                        |                       | ns   |

| 24  | th(CK1L-REV)              | Hold time of RESET valid after LCLK1 low to guarantee recognition at a particular clock edge | 10 <sup>‡</sup>        |                                   | 10 <sup>‡</sup>            | -                     | ns   |

| 25  | t <sub>su(CSV-CK1L)</sub> | Setup time of HCS valid to LCLK11 to guarantee recognition at a particular clock edge        | 40 <sup>‡</sup>        |                                   | 40 <sup>‡</sup>            |                       | ns   |

| 26  | th(CK1L-CSV)              | Hold time of HCS valid after LCLK1 low to guarantee recognition at a particular clock edge   | 10 <sup>‡</sup>        |                                   | 10‡                        |                       | ns   |