SEMICONDUCTORTM

April 1988 Revised August 1999

# 74F401 CRC Generator/Checker

#### **General Description**

The 74F401 Cycle Redundancy Check (CRC) Generator/ Checker provides an advanced tool for implementing the most widely used error detection scheme in serial digital data handling systems. A 3-bit control input selects one-of-eight generator polynomials. The list of polynomials includes CRC-16 and CRC-CCITT as well as their reciprocals (reverse polynomials). Automatic right justification is incorporated for polynomials of degree less than 16. Separate clear and preset inputs are provided for floppy disk and other applications. The Error output indicates whether or not a transmission error has occurred. Another control input inhibits feedback during check word transmission. The 74F401 is fully compatible with all TTL families.

#### **Features**

- Eight selectable polynomials

- Error indicator

- Separate preset and clear controls

- Automatic right justification

- Fully compatible with all TTL logic families

- 14-pin package

- 9401 equivalent

- Typical applications:

Floppy and other disk storage systems

Digital cassette and cartridge systems

Data communication systems

#### Ordering Code:

| Order Number Package Number |      | Package Description                                                         |  |  |  |  |  |

|-----------------------------|------|-----------------------------------------------------------------------------|--|--|--|--|--|

| 74F401SC                    | M14A | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow |  |  |  |  |  |

| 74F401PC                    | N14A | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |  |  |  |  |  |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

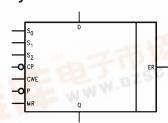

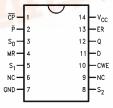

#### **Logic Symbol**

#### **Connection Diagram**

#### **Unit Loading/Fan Out**

| Dia Nama                       | December 1                                       | U.L.     | Input I <sub>IH</sub> /I <sub>IL</sub>  |  |

|--------------------------------|--------------------------------------------------|----------|-----------------------------------------|--|

| Pin Names                      | Description                                      | HIGH/LOW | Output I <sub>OH</sub> /I <sub>OL</sub> |  |

| S <sub>0</sub> -S <sub>2</sub> | Polynomial Select Inputs                         | 1.0/1.0  | 20 μA/-0.6 mA                           |  |

| D                              | Data Input                                       | 1.0/1.0  | 20 μA/–0.6 mA                           |  |

| CP                             | Clock Input (Operates on HIGH-to-LOW Transition) | 1.0/1.0  | 20 μA/-0.6 mA                           |  |

| CWE                            | Check Word Enable Input                          | 1.0/1.0  | 20 μA/–0.6 mA                           |  |

| P                              | Preset (Active LOW) Input                        | 1.0/1.0  | 20 μA/-0.6 mA                           |  |

| MR                             | Master Reset (Active HIGH) Input                 | 1.0/1.0  | 20 μA/–0.6 mA                           |  |

| Q                              | Data Output                                      | 50/33.3  | −1 mA/20 mA                             |  |

| ER                             | Error Output                                     | 50/33.3  | −1 mA/20 mA                             |  |

#### **Functional Description**

The 74F401 is a 16-bit programmable device which operates on serial data streams and provides a means of detecting transmission errors. Cyclic encoding and decoding schemes for error detection are based on polynomial manipulation in modulo arithmetic. For encoding, the data stream (message polynomial) is divided by a selected polynomial. This division results in a remainder which is appended to the message as check bits. For error checking, the bit stream containing both data and check bits is divided by the same selected polynomial. If there are no detectable errors, this division results in a zero remainder. Although it is possible to choose many generating polynomials of a given degree, standards exist that specify a small number of useful polynomials. The 74F401 implements the polynomials listed in Table 1 by applying the appropriate logic levels to the select pins  $S_0$ ,  $S_1$  and  $S_2$ .

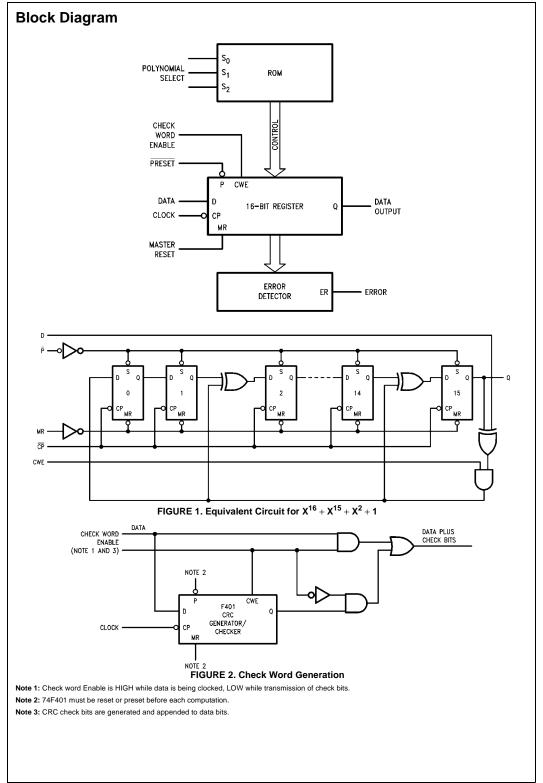

The 74F401 consists of a 16-bit register, a Read Only Memory (ROM) and associated control circuitry as shown in the block diagram. The polynomial control code presented at inputs  $S_0$ ,  $S_1$  and  $S_2$  is decoded by the ROM, selecting the desired polynomial by establishing shift mode operation on the register with Exclusive OR gates at appropriate inputs. To generate the check bits, the data stream is entered via the Data inputs (D), using the HIGH-to-LOW

transition of the Clock input  $(\overline{CP})$ . This data is gated with the most significant output (Q) of the register, and controls the Exclusive OR gates Figure 1. The Check Word Enable (CWE) must be held HIGH while the data is being entered. After the last data bit is entered, the CWE is brought LOW and the check bits are shifted out of the register and appended to the data bits using external gating Figure 2.

To check an incoming message for errors, both the data and check bits are entered through the D input with the CWE input held HIGH. The 74F401 is not in the data path, but only monitors the message. The Error Output becomes valid after the last check bit has been entered into the 74F401 by a HIGH-to-LOW transition of  $\overline{\text{CP}}$ . If no detectable errors have occurred during the data transmission, the resultant internal register bits are all LOW and the Error Output (ER) is LOW. If a detectable error has occurred, ER is HIGH.

A HIGH on the Master Reset input (MR) asynchronously clears the register. A LOW on the Preset input  $(\overline{P})$  asynchronously sets the entire register if the control code inputs specify a 16-bit polynomial; in the case of 12- or 8-bit check polynomials only the most significant 12 or 8 register bits are set and the remaining bits are cleared.

TABLE 1.

| Select Code    |                |                | Polynomial                                             | Remarks           |  |  |  |

|----------------|----------------|----------------|--------------------------------------------------------|-------------------|--|--|--|

| S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Polynomiai                                             | Remarks           |  |  |  |

| L              | L              | L              | $X^{16} + X^{15} + X^2 + 1$                            | CRC-16            |  |  |  |

| L              | L              | Н              | $X^{16} + X^{14} + X + 1$                              | CRC-16 REVERSE    |  |  |  |

| L              | Н              | L              | $X^{16} + X^{15} + X^{13} + X^7 + X^4 + X^2 + X^1 + 1$ |                   |  |  |  |

| L              | Н              | Н              | $X^{12} + X^{11} + X^3 + X^2 + X + 1$                  | CRC-12            |  |  |  |

| Н              | L              | L              | $X^8 + X^7 + X^5 + X^4 + X + 1$                        |                   |  |  |  |

| Н              | L              | Н              | $X^8 + 1$                                              | LRC-8             |  |  |  |

| Н              | Н              | L              | $X^{16} + X^{12} + X^5 + 1$                            | CRC-CCITT         |  |  |  |

| Н              | Н              | Н              | $X^{16} + X^{11} + X^4 + 1$                            | CRC-CCITT REVERSE |  |  |  |

#### **Absolute Maximum Ratings**(Note 4)

Storage Temperature  $-65^{\circ}\text{C} \text{ to } +150^{\circ}\text{C}$

$\begin{array}{lll} \mbox{Ambient Temperature under Bias} & -55^{\circ}\mbox{C to } +125^{\circ}\mbox{C} \\ \mbox{Junction Temperature under Bias} & -55^{\circ}\mbox{C to } +150^{\circ}\mbox{C} \\ \mbox{V}_{\mbox{CC}} \mbox{ Pin Potential to Ground Pin} & -0.5\mbox{V to } +7.0\mbox{V} \\ \end{array}$

Voltage Applied to Output

in HIGH State (with  $V_{CC} = 0V$ )

$\begin{array}{ll} \text{Standard Output} & -0.5 \text{V to V}_{\text{CC}} \\ \text{3-STATE Output} & -0.5 \text{V to } +5.5 \text{V} \end{array}$

Current Applied to Output

in LOW State (Max) twice the rated  $I_{OL}$  (mA)

## Recommended Operating Conditions

Free Air Ambient Temperature  $0^{\circ}$ C to  $+70^{\circ}$ C Supply Voltage +4.5V to +5.5V

Note 4: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation

under these conditions is not implied.

Note 5: Either voltage limit or current limit is sufficient to protect inputs.

#### **DC Electrical Characteristics**

| Symbol           | Parameter                            |                     | Min  | Тур | Max  | Units | v <sub>cc</sub> | Conditions                                                   |                         |

|------------------|--------------------------------------|---------------------|------|-----|------|-------|-----------------|--------------------------------------------------------------|-------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage                   |                     | 2.0  |     |      | V     |                 | Recognized as a HIGH Signal                                  |                         |

| V <sub>IL</sub>  | Input LOW Voltage                    |                     |      |     | 0.8  | V     |                 | Recognized as a LOW Signal                                   |                         |

| V <sub>CD</sub>  | Input Clamp Diode Voltage            |                     |      |     | -1.2 | V     | Min             | $I_{IN} = -18 \text{ mA}$                                    |                         |

| V <sub>OH</sub>  | Output HIGH                          | 10% V <sub>CC</sub> | 2.5  |     |      | V     | N.C             | Min                                                          | I <sub>OH</sub> = -1 mA |

|                  | Voltage                              | $5\% V_{CC}$        | 2.7  |     |      | · v   | IVIIII          | $I_{OH} = -1 \text{ mA}$                                     |                         |

| V <sub>OL</sub>  | Output LOW<br>Voltage                | 10% V <sub>CC</sub> |      |     | 0.5  | V     | Min             | I <sub>OL</sub> = 20 mA                                      |                         |

| I <sub>IH</sub>  | Input HIGH Current                   |                     |      |     | 5.0  | μΑ    | Max             | V <sub>IN</sub> = 2.7V                                       |                         |

| I <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test |                     |      |     | 7.0  | μА    | Max             | V <sub>IN</sub> = 7.0V                                       |                         |

| I <sub>CEX</sub> | Output HIGH<br>Leakage Current       |                     |      |     | 50   | μА    | Max             | $V_{OUT} = V_{CC}$                                           |                         |

| V <sub>ID</sub>  | Input Leakage<br>Test                |                     | 4.75 |     |      | V     | 0.0             | $I_{\text{ID}} = 1.9 \mu\text{A}$<br>All Other Pins Grounded |                         |

| I <sub>OD</sub>  | Output Leakage<br>Circuit Current    |                     |      |     | 3.75 | μА    | 0.0             | V <sub>IOD</sub> = 150 mV<br>All Other Pins Grounded         |                         |

| I <sub>IL</sub>  | Input LOW Current                    |                     |      |     | -0.6 | mA    | Max             | V <sub>IN</sub> = 0.5V                                       |                         |

| I <sub>OS</sub>  | Output Short-Circuit Current         |                     | -60  |     | -150 | mA    | Max             | V <sub>OUT</sub> = 0V                                        |                         |

| I <sub>CCH</sub> | Power Supply Current                 |                     |      | 70  | 105  | mA    | Max             | V <sub>O</sub> = HIGH                                        |                         |

#### **AC Electrical Characteristics**

| Symbol           | Parameter                     |     | $T_A = +25^{\circ}C$ $V_{CC} = +5.0V$ $C_L = 50 \text{ pF}$ |      |     | $T_A = 0$ °C to +70°C<br>$V_{CC} = +5.0V$<br>$C_L = 50$ pF |     |  |

|------------------|-------------------------------|-----|-------------------------------------------------------------|------|-----|------------------------------------------------------------|-----|--|

|                  |                               | Min | Тур                                                         | Max  | Min | Max                                                        | İ   |  |

| f <sub>MAX</sub> | Maximum Clock Frequency       | 100 |                                                             |      | 85  |                                                            | MHz |  |

| t <sub>PLH</sub> | Propagation Delay             | 4.5 |                                                             | 11.5 | 4.5 | 13.5                                                       |     |  |

| t <sub>PHL</sub> | CP to Q                       | 4.0 |                                                             | 10.0 | 4.0 | 11.0                                                       | ns  |  |

| t <sub>PHL</sub> | Propagation Delay MR to Q     | 3.0 |                                                             | 7.5  | 3.0 | 8.0                                                        | ns  |  |

| t <sub>PLH</sub> | Propagation Delay P to Q      | 3.0 |                                                             | 8.5  | 3.0 | 9.5                                                        | ns  |  |

| t <sub>PHL</sub> | Propagation Delay<br>MR to ER | 3.5 |                                                             | 11.0 | 3.5 | 12.0                                                       | ns  |  |

| t <sub>PLH</sub> | Propagation Delay P to ER     | 3.0 |                                                             | 8.5  | 3.0 | 10.0                                                       | ns  |  |

| t <sub>PLH</sub> | Propagation Delay             | 5.0 |                                                             | 13.0 | 5.0 | 14.5                                                       | 200 |  |

| t <sub>PHL</sub> | CP to ER                      | 4.5 |                                                             | 11.5 | 4.5 | 12.5                                                       | ns  |  |

### **AC Operating Requirements**

|                    |                              | $T_A = +25$ °C $V_{CC} = +5.0V$ |     | $T_A = 0$ °C to +70°C<br>$V_{CC} = +5.0V$ |     | Units |

|--------------------|------------------------------|---------------------------------|-----|-------------------------------------------|-----|-------|

| Symbol             | Parameter                    |                                 |     |                                           |     |       |

|                    |                              | Min                             | Max | Min                                       | Max |       |

| t <sub>S</sub> (H) | Set-up Time, HIGH or LOW     | 5.0                             |     | 5.5                                       |     |       |

| t <sub>S</sub> (L) | D to CP                      | 5.0                             |     | 5.5                                       |     |       |

| t <sub>S</sub> (H) | Set-up Time, HIGH or LOW     | 4.0                             |     | 4.5                                       |     |       |

| t <sub>S</sub> (L) | CWE to CP                    | 4.0                             |     | 4.5                                       |     | ns    |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW       | 2.0                             |     | 2.0                                       |     |       |

| t <sub>H</sub> (L) | D and CWE to CP              | 2.0                             |     | 2.0                                       |     |       |

| t <sub>W</sub> (L) | P Pulse Width, LOW           | 7.0                             |     | 8.0                                       |     | ns    |

| t <sub>W</sub> (H) | Clock Pulse Width,           | 5.0                             |     | 6.0                                       |     | ns    |

| t <sub>W</sub> (L) | HIGH or LOW                  | 5.0                             |     | 6.0                                       |     | 115   |

| t <sub>W</sub> (H) | MR Pulse Width, HIGH         | 5.0                             |     | 5.5                                       |     | ns    |

| t <sub>REC</sub>   | Recovery Time                | 4.0                             |     | 4.5                                       |     |       |

|                    | MR to $\overline{\text{CP}}$ |                                 |     | 4.5                                       |     | ns    |

| t <sub>REC</sub>   | Recovery Time                | 2.0                             |     | 2.0                                       |     | ns    |

|                    | P to CP                      |                                 |     | 2.0                                       |     | 115   |

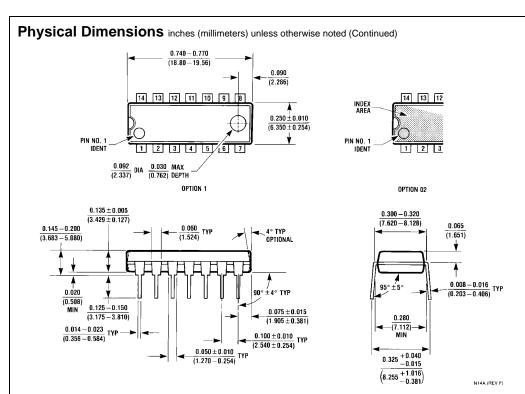

#### Physical Dimensions inches (millimeters) unless otherwise noted $\frac{0.335 - 0.344}{(8.509 - 8.738)}$ LEAD NO. 1 IDENT 0.010 (0.254) MAX $\frac{0.150-0.157}{(3.810-3.988)}$ $\frac{0.053 - 0.069}{(1.346 - 1.753)}$ $\frac{0.010-0.020}{(0.254-0.508)}$ 8° MAX TYP ALL LEADS $\frac{0.004 - 0.010}{(0.102 - 0.254)}$ SEATING PLANE 0.014 (0.356) 0.008 - 0.010 (0.203 - 0.254) TYP ALL LEADS 0.050 (1.270) TYP $\frac{0.014-0.020}{(0.356-0.508)}\,\mathrm{TYP}$ 0.016 - 0.050 (0.406 - 1.270) TYP ALL LEADS 0.004 (0.102) ALL LEAD TIPS $\frac{0.008}{(0.203)}$ TYP

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow Package Number M14A

M14A (REV H)

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N14A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com