# TEXAS INSTRUMENTS

## DUAL-SLOT PCI HOT-PLUG POWER CONTROLLER

## FEATURES

- 12-V, –12-V, 3.3-V, 5-V Main Power Switching and Auxiliary 3.3-V Power Switching

- 12-V, -12-V And Auxiliary 3.3-V Power FETs

- Hot-Swap Protection and Control of All Supplies

- Overcurrent Protection for All Supplies

- Isolation of Any Load Fault in One Slot from Any Other Slot

- Undervoltage Monitoring for the Main 12-V, 3.3-V, 5-V and Auxiliary 3.3-V Supplies

- Power Fault Latching

- Overtemperature Shutdown

- Slot Status Readout with Open-Drain LED Drivers

- Mechanical Switch Inputs for Attention Request and Electrical Interlock

- Serial Interface for Power Control, Power Status, Slot Control and Slot Status

- Compatible With 33-MHz, 66-MHz, and 133-MHz Bus Speeds

- Compliant To PCI And PCI-X Hot Plug Specifications

- One TPS2340A Supports Two Slots

## DESCRIPTION

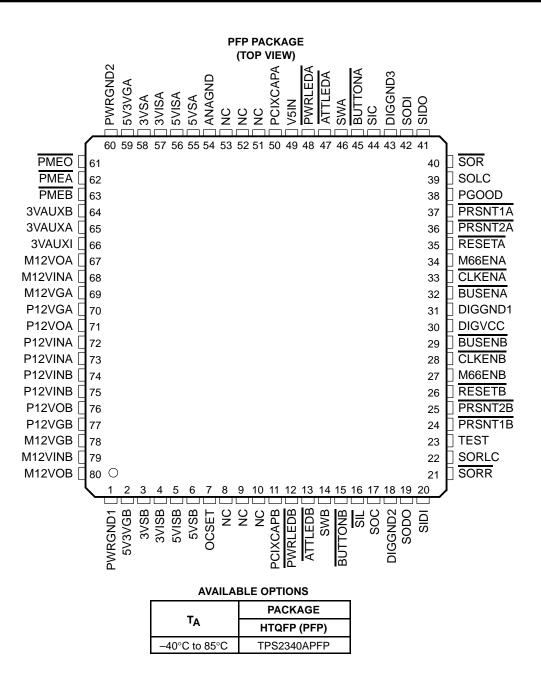

The TPS2340A contains main supply power control, auxiliary supply power control, power FETs for 12 V, -12 V and auxiliary 3.3 V supplies, and a serial interface for communications with and control of slots. Each TPS2340A contains supply control and switching for two slots.

The main power control circuits start with all supplies off and hold all supplies off until power to the TPS2340A is valid on all positive supplies. When power is requested via the serial interface, the control circuit applies constant current to the gates of the power FETs, allowing each FET to ramp load voltage linearly. Each supply can be programmed for a desired ramp rate by selecting a gate capacitor for the power FET for that supply. The power control circuits also monitor load current and latch off that slot if the load current exceeds a programmed maximum value. In addition, once the 12-V, the 5-V, and the 3.3-V FETs are fully enhanced, the load voltage is monitored. If load voltage drops out of specification after these FETs are fully enhanced, the slot latches off. This provides another level of protection from load fault.

The auxiliary power control circuit switches, ramps, and monitors 3.3-V auxiliary power to each slot. The auxiliary control circuit also controls data switches that connect slot interrupts (power management event [PME] outputs) to the main interrupt PME bus after 3.3-V auxiliary supply is connected. PME is disconnected when a board is turned off or faulted.

Each TPS2340A contains power FETs for 12 V at 500 mA, -12 V at 100 mA, and auxiliary 3.3 V at 375 mA for each slot. These power FETs are short-circuit protected, slew rate controlled, and over-temperature protected.

The serial interface communicates with a slot controller using a synchronous serial protocol. The interface communicates with the slot, status LEDs, and mechanical switches with individual, dedicated lines. The interface operates from 3.3-V power but inputs are 5-V tolerant. Status LED drivers are capable of driving 24-mA LEDs via integrated open-drain MOSFETs. Mechanical switch inputs have internal pull-up and hysteresis buffers. The serial interface controls slot power, bus connection, and LED outputs, and monitors board capability, power fault, and switch input status.

#### SLUS528A - MARCH 2002 - REVISED AUGUST 2002

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Input voltage range:  | P12VIN<br>M12VIN<br>All others                                                                     | –15.0 V to 0.5 V |

|-----------------------|----------------------------------------------------------------------------------------------------|------------------|

| Output voltage range: | P12VO, 5V3VG<br>P12VG<br>M12VO, M12VG                                                              | –0.5 V to 28 V   |

| Output current pulse: | P12VO (DC internally limited)                                                                      |                  |

| Storage temperature r | erature range, T <sub>J</sub><br>ange, T <sub>stg</sub><br>mm (1/16 inch) from case for 10 seconds | –55°C to 150°C   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltages are respect to DGND.

### electrical characteristics over recommended operating temperature range, P12VINA = P12VINB = 12 V, V5IN = 5 V, DIGVCC = 3.3 V, M12VINA = M12VINB = -12 V, 3VAUXI = 3.3 V, all outputs unloaded, $T_A = T_J$ (unless otherwise noted)

#### 5-V/3.3-V Supply

| PARAMETER                                              | TEST CO                                                   | NDITIONS    | MIN  | TYP  | MAX   | UNIT |

|--------------------------------------------------------|-----------------------------------------------------------|-------------|------|------|-------|------|

| 5V <sub>OC</sub> input threshold voltage               | R <sub>OCSET</sub> = 6.04 kΩ                              | 43          | 53   | 63   | mV    |      |

| 5VISA, 5VISB voltage fault threshold                   | After P12VG and 5V3                                       | VG good     | 4.16 | 4.65 | 4.92  | V    |

| 5VISA, 5VISB voltage fault minimum captured pulse      |                                                           |             |      | 75   | 135   | ns   |

| 5VSA input bias current                                | VSA input bias current PWRENx = high                      |             |      |      | 100   |      |

| 5VISA, 5VISB input bias current                        | PWRENx = high                                             |             | 100  | 250  | 500   | μA   |

| 5VISA, 5VISB bleed current PWRENx = low, 5VISx = 5 V   |                                                           |             |      | 10   | 20    | mA   |

| 3VOC Input threshold voltage                           | ROCSET = $6.04 \text{ k}\Omega$                           |             | 53   | 63   | 72    | mV   |

| 3VISA, 3VISB voltage fault threshold                   | After P12VG and 5V3                                       | VG good     | 2.64 | 2.86 | 3.08  | V    |

| 3VISA, 3VISB voltage fault minimum captured pulse time |                                                           |             |      | 75   | 135   | ns   |

| 3VSA, 3VSB input bias current                          | PWRENx = high                                             |             | -100 |      | 100   |      |

| 3VISA, 3VISB input bias current                        | PWRENx = high                                             |             | 100  | 250  | 500   | μA   |

| 3VISA, 3VISB bleed current                             | PWRENx = low,                                             | 5VISx = 5 V | 5    | 10   | 20    | mA   |

| 5V3VGA, 5V3VGB charge current                          |                                                           |             | -25  | -20  | -14.5 | μΑ   |

| 5V3VGA, 5V3VGB discharge current                       |                                                           |             |      | 200  |       | mA   |

| 5V3VGA, 5V3VGB good threshold                          | P12VIN = 12V                                              |             | 9.5  | 11   | 11.5  | V    |

| 5V3VGA, 5V3VGB turn-off time                           | $C_{5V3VG} = 0.022 \mu\text{F},$<br>5V3VG falling from 90 | % to 10%    |      | 1    | 3.5   | μs   |

electrical characteristics over recommended operating temperature range, P12VINA = P12VINB = 12 V, V5IN = 5 V, DIGVCC = 3.3 V, M12VINA = M12VINB = -12 V, 3VAUXI = 3.3 V, all outputs unloaded, T<sub>A</sub> = T<sub>J</sub> (unless otherwise noted) (continued)

| PARAMETER                                                | TEST CON                                                                                  | DITIONS                               | MIN  | TYP   | MAX   | UNIT |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------|------|-------|-------|------|

| +12-V Internal NMOS on-resistance                        | PWREN = HIGH,<br>T <sub>A</sub> = T <sub>J</sub> = 25°C                                   | I <sub>D</sub> = 0.5 A                |      | 0.18  | 0.3   | Ω    |

|                                                          | PWREN = HIGH,                                                                             | I <sub>D</sub> = 0.5 A                |      |       | 0.4   | Ω    |

| -12-V Internal NMOS on-resistance                        | PWREN = HIGH,<br>T <sub>A</sub> = T <sub>J</sub> = 25°C                                   | I <sub>D</sub> = 0.1 A                |      | 0.5   | 0.75  | Ω    |

|                                                          | PWREN = HIGH,                                                                             | I <sub>D</sub> = 0.1 A                |      |       | 0.9   |      |

| +12-V overcurrent threshold                              | ROCSET = 6.04 k $\Omega$                                                                  |                                       | 0.83 | 1.00  | 1.17  | ^    |

| -12-V overcurrent threshold                              | ROCSET = $6.04 \text{ k}\Omega$                                                           |                                       | 0.12 | 0.19  | 0.25  | A    |

| P12VOA, P12VOB fault threshold voltage                   | After P12VG and 5V3VC                                                                     | G good                                | 9.50 | 10.80 | 11.15 | V    |

| P12VOA, P12VOB voltage fault minimum captured pulse time |                                                                                           |                                       |      | 75    | 135   | ns   |

| M12VGA, M12VGB gate charge current                       |                                                                                           |                                       | -25  | -20   | -14.5 | μA   |

| M12VGA, M12VGB gate discharge current                    |                                                                                           |                                       |      | 200   |       | mA   |

| P12VGA, P12VGB, charge current                           | Derived from charge pur                                                                   | mp                                    | 1.0  | 4.0   | 8.5   | μA   |

| P12VGA, P12VGB, discharge current                        |                                                                                           |                                       |      | 100   |       | mA   |

| P12VGA, P12VGB good threshold                            | P12VIN = 12 V                                                                             |                                       | 19   | 20.5  | 22    | V    |

| <b>T</b>                                                 | PWREN = HIGH to M12<br>$C_{M12VG} = 0.022 \mu\text{F},$<br>$C_{M12VO} = 50 \mu\text{F}$   | VO = -10.4 V,<br>RL = 120 Ω           |      | 15    | 20    |      |

| Turn-on time                                             | PWREN = HIGH to P12'<br>$C_{12PVG} = 0.022 \mu\text{F},$<br>$C_{P12VO} = 200 \mu\text{F}$ | VO = 11.4 V,<br>R <sub>L</sub> = 24 Ω |      | 60    | 75    | ms   |

| <b>-</b> "··                                             | PWREN = LOW to P12\<br>CP12VG = 0.022 μF                                                  | /O = 0.6 V,                           |      | 1.5   | 3.5   | μs   |

| Turn-off time                                            | PWREN = LOW to M12 <sup>V</sup><br>CM12VG = 0.022 μF                                      | VO = -0.6 V,                          |      | 1.5   | 3.5   | μs   |

| M12VO bleed current                                      |                                                                                           |                                       |      | -20   | -5    |      |

| P12VO bleed current                                      |                                                                                           |                                       | 5    | 10    |       | mA   |

#### input/output control

| PARAMETER                         | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------|-----------------|------|------|------|------|

| P12VIN supply current             | P12VIN = 12 V   |      | 1    | 2    |      |

| V5IN supply current               | V5IN = 5 V      |      | 1.00 | 2.75 | mA   |

| DIGVCC supply current             | DIGVCC = 3.3 V  |      | 500  | 2000 |      |

| M12VIN supply current             | M12VIN –12 V    |      | 250  | 2000 | μA   |

| 3VAUXI supply current             | 3VAUXI = 3.3 V  |      | 200  | 2000 |      |

| Overcurrent fault response time   |                 |      | 500  | 960  | ns   |

| DIGVCC start-up threshold voltage |                 | 2.60 | 2.80 | 2.95 |      |

| DIGVCC stop threshold voltage     |                 | 2.40 | 2.55 | 2.80 |      |

| V5IN start-up threshold voltage   |                 | 4.2  | 4.4  | 4.6  | .,   |

| V5IN stop threshold voltage       |                 | 3.8  | 4.0  | 4.4  | V    |

| P12VIN start-up threshold voltage |                 | 10.2 | 10.3 | 11.2 |      |

| P12VIN stop threshold voltage     |                 | 9.5  | 9.4  | 10.6 |      |

electrical characteristics over recommended operating temperature range, P12VINA = P12VINB = 12 V, V5IN = 5 V, DIGVCC = 3.3 V, M12VINA = M12VINB = -12 V, 3VAUXI = 3.3 V, all outputs unloaded, T<sub>A</sub> = T<sub>J</sub> (unless otherwise noted) (continued)

#### noise filter

| PARAMETER                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------------------|-----------------|-----|-----|-----|------|

| Ignored spike from overcurrent |                 |     | 250 |     | ns   |

| Latched spike from overcurrent |                 |     | 500 |     | ns   |

#### 3.3 V AUX and PME

| PARAMETER                        | TEST CONDITIONS                                                             | MIN  | TYP  | MAX  | UNIT |

|----------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| 3VAUXx overcurrent shutdown      |                                                                             | 0.95 | 1.15 | 1.40 | А    |

| 3VAUXI to 3VAUXx on-resistance   | $I_{3VAUXx} = -500 \text{ mA}$                                              |      | 300  | 425  | mΩ   |

| 3VAUXI undervoltage lockout      |                                                                             | 1.9  | 2.2  | 2.9  | V    |

| 3VAUXx turn-on slew rate         |                                                                             |      | 1.6  | 3.3  | V/ms |

| 3VAUXx turn-on time from SWx     | from SWx < 0.8 V,<br>C <sub>3VAUXx</sub> = 150 μF                           |      | 3    | 5    | ms   |

| 3VAUXx turn-off time from SWx    | from SWx > 2.0 V                                                            |      | 2.5  | 7.0  |      |

| 3VAUXx turn-off time from Faultx | from 3VAUXx overcurrent fault detected                                      |      | 5    | 10   | μs   |

| PMEx turn-on time from 3VAUXx    | from $3VAUXx > 3.0 V$ ,<br>C $_{3VAUXx} = 150 \mu F$                        | 6    | 10   | 17   | ms   |

| PMEx turn-off time from SWx      | from SWx > 2.0 V,                                                           |      | 2    | 4    | μs   |

| PMEx turn-off time from Faultx   | from 3VAUXx overcurrent fault detected                                      |      | 2    | 4    | μs   |

| PMEx switch on-resistance        | from SWx < 0.8 V, $I_D = 10 \text{ mA}$<br>$T_A = T_J = 25^{\circ}\text{C}$ |      | 5    | 10   | Ω    |

### ac switching characteristics

| PARAMETER                                     | TEST CONDITIONS                                                                              | MIN | TYP MAX | UNIT |

|-----------------------------------------------|----------------------------------------------------------------------------------------------|-----|---------|------|

| f <sub>MAX</sub> operating clock frequency    | $0 \le T_A \le 70^{\circ}C$                                                                  | 0   | 10      | MHz  |

| SIDO t <sub>CO</sub> clock to output time     | $C_L = 50 \text{ pF}, \qquad \qquad 0 \leq T_A \leq 70^\circ C$                              | 0   | 15      |      |

| SIDI, SIL t <sub>SU</sub> setup to clock time | $0 \le T_A \le 70^{\circ}C$                                                                  | 15  |         |      |

| SODI, t <sub>SU</sub> setup to clock time     | $0 \le T_A \le 70^{\circ}C$                                                                  | 15  |         |      |

| SODI, t <sub>H</sub> hold time                | $0 \le T_A \le 70^{\circ}C$                                                                  | 0   | 15      |      |

| All outputs $t_{CO}$ clock to output time     | $\label{eq:BUSENX} \begin{array}{ c c c c c c c c c c c c c c c c c c c$                     |     | 20      | ns   |

| Recommended input rise and fall times         | 10% to 90% of VCC, all digital inputs except<br>SWx, BUTTONx, PGOOD, PRSNT1x, and<br>PRSNT2x | 0.2 | 1       |      |

electrical characteristics over recommended operating temperature range, P12VINA = P12VINB = 12 V, V5IN = 5 V, DIGVCC = 3.3 V, M12VINA = M12VINB = -12 V, 3VAUXI = 3.3 V, all outputs unloaded, T<sub>A</sub> = T<sub>J</sub> (unless otherwise noted) (continued)

#### dc electrical characteristics

| PARAMETER                                                                                                        | TEST CONDITIONS                                | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|-----|-----|------|

| Input threshold voltage (SIL, SOC, SIDI, SORR, SORLC, TEST, M66EN, SOLC, SOR, SODI, SIC)                         |                                                | 0.8 | 1.4 | 2.0 |      |

| High–level input threshold voltage (SWA, SWB,<br>BUTTONA, BUTTONB, PRSNT1A, PRSNT2A,<br>PRSNT1B, PRSNT2B, PGOOD) |                                                | 2.0 | 2.4 | 2.8 |      |

| Low-level input threshold voltage (SWA, SWB,<br>BUTTONA, BUTTONB, PRSNT1A, PRSNT2A,<br>PRSNT1B, PRSNT2B)         |                                                | 0.8 | 1.2 | 1.6 |      |

| Low-level input threshold voltage (PGOOD)                                                                        |                                                | 0.1 | 0.4 | 0.8 | V    |

| Input hysteresis (SWA, SWB, BUTTONA, BUTTONB, PRSNT1A, PRSNT2A, PRSNT1B, PRSNT2B)                                |                                                | 0.4 | 1.0 | 1.6 | v    |

| Input hysteresis (PGOOD)                                                                                         |                                                | 1.5 | 2.0 | 2.5 |      |

| High-level output voltage (BUSENA, BUSENB)                                                                       | I <sub>L</sub> = -8 mA                         | 2.4 | 2.8 |     |      |

| Low-level output voltage (BUSENA, BUSENB)                                                                        | I <sub>L</sub> = 16 mA                         |     | 0.2 | 0.5 |      |

| Low-level output voltage (PWRLEDA, PWRLEDB, ATTLEDA, ATTLEDB)                                                    | I <sub>L</sub> = 24 mA                         |     | 0.4 | 0.8 |      |

| Low-level output voltage (all other outputs)                                                                     | IL = 4 mA                                      |     | 0.2 | 0.5 |      |

| 3.3 V pull-up resistor impedance<br>(inputs pulled up to 3.3 V)                                                  |                                                | 30  |     | 200 |      |

| 5 V pull-up resistor impedance (inputs pulled up to 5 V)                                                         |                                                | 30  |     | 200 |      |

| Pull-down resistor impedance (inputs with pull-down)                                                             |                                                | 30  |     | 200 | kΩ   |

| PCIXCAPA, PCIXCAPB resistor for 133 MHz                                                                          | Open circuit recommended                       | 30  |     |     |      |

| PCIXCAPA, PCIXCAPB resistor for 66 MHz                                                                           | 10 $k\Omega$ connection to DIGGND recommended  | 6   |     | 14  |      |

| PCIXCAPA, PCIXCAPB resistor for 33 MHz                                                                           | $0 \ k\Omega$ connection to DIGGND recommended |     |     | 1   |      |

## recommended operating conditions

|                                                  | MIN   | MAX   | UNIT |

|--------------------------------------------------|-------|-------|------|

| Input voltage, P12VINA, P12VINB                  | 10.8  | 13.2  |      |

| Input voltage, V5IN                              | 4.75  | 5.25  |      |

| Input voltage, DIGVCC                            | 3.1   | 3.5   | V    |

| Input voltage, M12VINA, M12VINB                  | -13.2 | -10.8 |      |

| Input voltage, 3VAUXI                            | 3.1   | 3.5   |      |

| Load current, PWRLEDA, PWRLEDB, ATTLEDA, ATTLEDB | 0     | 24    |      |

| Load current, P12VOA, P12VOB                     | 0     | 500   |      |

| Load current, M12VOA, M12VOB                     | 0     | 100   | mA   |

| Load current, 3VAUXA, 3VAUXB                     | 0     | 375   |      |

|          |     |     | Terminal Functions                                                                                                                                                                                                                                                                                                           |  |

|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TERMINAL |     |     |                                                                                                                                                                                                                                                                                                                              |  |

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |  |

| 3VAUXI   | 66  | I   | 3.3Vaux voltage supply input. A 0.1- $\mu$ F bypass capacitor to PWRGND is recommended.                                                                                                                                                                                                                                      |  |

| 3VAUXA   | 65  | 0   | $-$ 3.3Vaux voltage supply outputs. A 0.01- $\mu$ F bypass capacitor to PWRGND is recommended.                                                                                                                                                                                                                               |  |

| 3VAUXB   | 64  | 0   | 5.5 vaux voltage supply outputs. A 0.01-µF bypass capacitor to FWRGND is recommended.                                                                                                                                                                                                                                        |  |

| 3VISA    | 57  | I   | Connect to the load side of the sense resistor. See definition for $3VS$ . This pin has a switched FET to ground to discharge any output load capacitance when the output is turned off. A 0.01- $\mu$ F bypass ca-                                                                                                          |  |

| 3VISB    | 4   | I   | pacitor to ANAGND is recommended.                                                                                                                                                                                                                                                                                            |  |

| 3VSA     | 58  | I   | Connect to the source side of the 3.3-V FET switch. This pin in conjunction with the 3VIS pin sense                                                                                                                                                                                                                          |  |

| 3VSB     | 3   | I   | the current to the 3.3-V load by sensing the voltage drop across a sense resistor. A 0.01-μF bypass capacitor to ANAGND is recommended.                                                                                                                                                                                      |  |

| 5V3VGA   | 59  | 0   | Gate drive for the 5-V and 3.3-V FET switches. Ramp rate is programmed by external capacitance connected from this pin to PWRGND. The capacitor is charged with a 20-µA current source and dis-                                                                                                                              |  |

| 5V3VGB   | 2   | 0   | charged with a switch. The output UV circuitry is disabled until the voltage on this pin is greater than 11 V and the voltage on P12VGx is greater than 20 V.                                                                                                                                                                |  |

| 5VISA    | 56  | I   | Connect to the load side of the sense resistor. See definition for 5VS. 5VIS is also used to sense the output voltage for the 5-V UV circuit. This pin has a switched FET to ground to discharge any output                                                                                                                  |  |

| 5VISB    | 5   | I   | load capacitance when the output is turned off. A 0.01-µF bypass capacitor to ANAGND is recommended.                                                                                                                                                                                                                         |  |

| 5VSA     | 55  | I   | Connect to the source of the 5-V FET switch. This pin in conjunction with the 5VIS pin senses the current to the 5V load by sensing the voltage drop across the sense resistor. A $0.01_{\mu}$ F bypass capaci-                                                                                                              |  |

| 5VSB     | 6   | I   | tor to ANAGND is recommended.                                                                                                                                                                                                                                                                                                |  |

| ANAGND   | 54  | -   | Ground pin for the low level analog section                                                                                                                                                                                                                                                                                  |  |

| ATTLEDA  | 47  | 0   |                                                                                                                                                                                                                                                                                                                              |  |

| ATTLEDB  | 13  | 0   | ATTLEDx is a high-current, low-true, open-drain output with a 100-kΩ pull-up resistor to V5IN.                                                                                                                                                                                                                               |  |

| BUSENA   | 32  | 0   | Output-to-bus enable FET switches. These outputs typically enable PCI clocks to the PCI conne                                                                                                                                                                                                                                |  |

| BUSENB   | 29  | 0   |                                                                                                                                                                                                                                                                                                                              |  |

| BUTTONA  | 45  | I   | PCI hot-plut attention notification (momentary) button inputs. Low indicates attention. These input have hysteresis and a $100 \cdot k\Omega$ pull-up to DIGVCC, requiring only a capacitor to ground for debouncing me-                                                                                                     |  |

| BUTTONB  | 15  | I   | chanical noise.                                                                                                                                                                                                                                                                                                              |  |

| CLKENA   | 33  | 0   | Output-to-clock enable FET switches. These outputs typically enable PCI clocks to the PCI connector.                                                                                                                                                                                                                         |  |

| CLKENB   | 28  | 0   |                                                                                                                                                                                                                                                                                                                              |  |

| DIGVCC   | 30  | I   | Power pin for the digital section, connect to 3.3 V. A 0.1- $\mu$ F bypass capacitor from DIGVCC to DIGGND is recommended.                                                                                                                                                                                                   |  |

| DIGGND1  | 31  | -   |                                                                                                                                                                                                                                                                                                                              |  |

| DIGGND2  | 18  | -   | Ground pins for the digital section.                                                                                                                                                                                                                                                                                         |  |

| DIGGND3  | 43  | -   |                                                                                                                                                                                                                                                                                                                              |  |

| M12VGA   | 69  | 0   | A capacitor connected from this pin to M12VO programs the ramp rate of the 12-V switched output.                                                                                                                                                                                                                             |  |

| M12VGB   | 78  | 0   | The capacitor is charged with a 20-µA current source and discharged with a switch.                                                                                                                                                                                                                                           |  |

| M12VINA  | 68  | I   | -12-V input voltage to the device and the $-12-V$ power FET. M12VINA and M12VINB must be tied together and are internally connected by a high-resistance path. The tab on the back of the package is                                                                                                                         |  |

| M12VINB  | 79  | I   | also connected to M12VIN. A $0.1-\mu$ F bypass capacitor from M12VIN to PWRGND is recommended.                                                                                                                                                                                                                               |  |

| M12VOA   | 67  | 0   | -12-V Switched output. This pin has a switched FET to ground to discharge any output load capaci-                                                                                                                                                                                                                            |  |

| M12VOB   | 80  | 0   | tance when the output is turned off. A 0.01-µF bypass capacitor to PWRGND is recommended.                                                                                                                                                                                                                                    |  |

| M66ENA   | 34  | I   | PCI 66MHz–capable bit for slot A. This pin has a 100-k $\Omega$ pull-up to 3VISA. This pin is typically tied to the PCI connector.                                                                                                                                                                                           |  |

| M66ENB   | 27  | I   | PCI 66MHz–capable bit for slot B. This pin has a 100-k $\Omega$ pull-up to 3VISB. This pin is typically tied to the PCI connector.                                                                                                                                                                                           |  |

| OCSET    | 7   | I   | A resistor connected between this pin and ANAGND sets the overcurrent threshold of the 4 FET switches. The +12-V and –12-V switches are set for the maximum permissible currents per the PCI specification when a 1%, 6.04-k $\Omega$ resistor is used. A 0.1- $\mu$ F bypass capacitor from OCSET to ANAGND is recommended. |  |

| Terminal Functions |     |     |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TERMINAL           |     |     | DECODIDION                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| NAME               | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| P12VGA             | 70  | ο   | Gate drive for the 12-V internal N-channel MOSFET for slot A. Connect a capacitor from this pin to PWRGND to program the ramp rate. The capacitor is charged with a 5– $\mu$ A current source and discharged with a switch. The output undervoltage circuitry is disabled until the voltage on this pin is greater than 20 V and the voltage on 5V3VGA is greater than 11 V.                            |  |  |  |

| P12VGB             | 77  | 0   | Gate drive for the 12-V internal N-channel MOSFET for slot B. Connect a capacitor from this pin to PWRGND to program the ramp rate. The capacitor is charged with a 5- $\mu$ A current source and discharged with a switch. The output undervoltage circuitry is disabled until the voltage on this pin is greater than 20 V and the voltage on 5V3VGB is greater than 11 V.                            |  |  |  |

|                    | 72  | I   | 12-V input to the device and the 12-V power FET for slot A. A 0.1-µF bypass capacitor from P12VINA                                                                                                                                                                                                                                                                                                      |  |  |  |

| P12VINA            | 73  | I   | to PWRGND is recommended.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 75  | I   | 12-V input to the device and the 12-V power FET for slot B. A 0.1-µF bypass capacitor from P12VINB                                                                                                                                                                                                                                                                                                      |  |  |  |

| P12VINB            | 74  | I   | to PWRGND is recommended.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| P12VOA             | 71  | 0   | 12-V switched output for slot A. This pin has a switched FET to ground to discharge any output load capacitance when the output is turned off. A 0.01-µF bypass capacitor to PWRGND is recommended.                                                                                                                                                                                                     |  |  |  |

| P12VOB             | 76  | 0   | 12-V switched output fo rslot B. This pin has a switched FET to ground to discharge any output load capacitance when the output is turned off. A 0.01-µF bypass capacitor to PWRGND is recommended.                                                                                                                                                                                                     |  |  |  |

| PCIXCAPA           | 50  | I   | PCI–X capable bit. To select 133-MHz PCI–X mode, leave PCIXCAPx floating. For 66-MHz PCI–X mode, pull down PCIXCAPx with one or two $10$ -k $\Omega$ resistors. For 33-MHz PCI 2.2 mode, ground                                                                                                                                                                                                         |  |  |  |

| PCIXCAPB           | 11  | I   | PCIXCAPx. This pin has a 10-k $\Omega$ pull–up resistor to DIGVCC. This pin is typically tied to the PCI connector.                                                                                                                                                                                                                                                                                     |  |  |  |

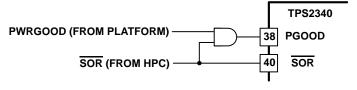

| PGOOD              | 38  | I   | Power good input. PGOOD has hysteresis so that it can be used as a power-on reset, driven from a slow-rising RC. PGOOD also has a 100-k $\Omega$ pull-up to DIGVCC. A logic path in the TPS2340A prevents the input data state machine from being reset when SOR asserts. This can be corrected with an external AND gate, which causes PGOOD to be de-asserted whenever SOR is asserted. (See Note 1.) |  |  |  |

| PMEA               | 62  | I   | $\overrightarrow{PME}$ input from slot A. These signals comply with PCI Power Management Spec 1.1. $\overrightarrow{PMEA}$ has a 200-k $\Omega$ pull-up to the appropriate switched 3VAUX for precharging. This pin is typically tied to the PCI connector.                                                                                                                                             |  |  |  |

| PMEB               | 63  | I   | $\overrightarrow{PME}$ input from slot B. These signals comply with PCI Power Management Spec 1.1. $\overrightarrow{PMEB}$ has a 200-k $\Omega$ pull-up to the appropriate switched 3VAUX for precharging. This pin is typically tied to the PCI connector.                                                                                                                                             |  |  |  |

| PMEO               | 61  | 0   | PME output from the device. This signal is an open-drain output and complies with PCI Power Man-<br>agement Specification 1.1 PME definition.                                                                                                                                                                                                                                                           |  |  |  |

| PRSNT1A            | 37  | I   | PCI presence detect bit 1. This input has hysteresis and a 100-k $\Omega$ pull-up to DIGVCC, requiring only a                                                                                                                                                                                                                                                                                           |  |  |  |

| PRSNT1B            | 24  | I   | capacitor to ground for debouncing mechanical noise. This pin is typically tied to the PCI connector.                                                                                                                                                                                                                                                                                                   |  |  |  |

| PRSNT2A            | 36  | I   | PCI-presence detect bit 2. This input has hysteresis and a 100-k $\Omega$ pull-up to DIGVCC, requiring only                                                                                                                                                                                                                                                                                             |  |  |  |

| PRSNT2B            | 25  | I   | a capacitor to ground for debouncing mechanical noise. This pin is typically tied to the PCI connector.                                                                                                                                                                                                                                                                                                 |  |  |  |

| PWRGND1            | 1   | _   |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PWRGND2            | 60  | _   | Ground pin for the power analog section.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| PWRLEDA            | 48  | 0   | In normal operation, output-to-power indicator PCI hot-plug status LED. In test mode, indicates the state of the internal signal PWRENx, the power FET control signal. PWRLEDx is a high-current, low-                                                                                                                                                                                                  |  |  |  |

| PWRLEDB            | 12  | 0   | true open-drain output with a 100-k $\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

NOTE 1: PGOOD input: diagram:

UDG-01126

| Terminal Functions |     |     |                                                                                                                                                                                                                                                                                                                                                              |  |  |

|--------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TERMINAL           |     |     |                                                                                                                                                                                                                                                                                                                                                              |  |  |

| NAME               | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RESETA             | 35  | 0   | PCI RESET signal to slot A. Conforms to PCI 2.2 local bus specification for 3.3-V signaling. This pin is typically tied to the PCI connector.                                                                                                                                                                                                                |  |  |

| RESETB             | 26  | 0   | PCI RESET signal to slot B. Conforms to PCI 2.2 local bus specification for 3.3-V signaling. This pin is typically tied to the PCI connector.                                                                                                                                                                                                                |  |  |

| SIC                | 44  | I   | Serial input clock. Shift serial data into device one bit position on rising edge.                                                                                                                                                                                                                                                                           |  |  |

| SIDI               | 20  | I   | Serial input data Input. The serial shift register input from a down-stream TPS2340.                                                                                                                                                                                                                                                                         |  |  |

| SIDO               | 41  | I/O | Serial input data output. The serial shift register output to the PCI hot-plug controller or the up-stream TPS2340. When PGOOD is low, SIDO is undriven and pulled up to DIGVCC with a 100-k $\Omega$ resistor. During the rising edge of PGOOD, the TPS2340A latches SIDO as MODE0.                                                                         |  |  |

| SIL                | 16  | I   | Serial input load. Pulse low to synchronously parallel load external serial input shift registers on the next rising edge of SIC.                                                                                                                                                                                                                            |  |  |

| SOC                | 17  | I   | Serial output clock. Shift serial output data into parallel output registers one bit position on rising edge.                                                                                                                                                                                                                                                |  |  |

| SODI               | 42  | I   | Serial output data input. Serial output data shifted into parallel output registers.                                                                                                                                                                                                                                                                         |  |  |

| SODO               | 19  | I/O | Serial output data output. Serial output data shifted to the down-stream TPS2340. When PGOOD is low, SODO is undriven and pulled up to DIGVCC with a 100-k $\Omega$ resistor. During the rising edge of PGOOD, the TPS2340A latches SODO as MODE1.                                                                                                           |  |  |

| SOLC               | 39  | I   | Serial output latch clock. Latch parallel register data on rising edge.                                                                                                                                                                                                                                                                                      |  |  |

| SORLC              | 22  | I   | Serial output reset latch clock. Latch parallel register data on rising edge (PCI RESET latches only).                                                                                                                                                                                                                                                       |  |  |

| SOR                | 40  | I   | Serial output reset. Clears parallel register data.                                                                                                                                                                                                                                                                                                          |  |  |

| SORR               | 21  | I   | Serial output reset reset. Clears parallel register data (PCI RESET latches only).                                                                                                                                                                                                                                                                           |  |  |

| SWA                | 46  | 1   | Slot A switch input. Low indicates the slot is populated. This input has hysteresis and a $100$ -k $\Omega$ pull-up to 3VAUXI, requiring only a capacitor to ground for debouncing mechanical noise. For testing purposes, pulling SWA to 5 V enables the slot main power and disables the slot auxilliary power, bypassing the serial interface.            |  |  |

| SWB                | 14  | I   | Slot B switch input. Low indicates the slot is populated. This input has hysteresis and a 100-k $\Omega$ pull-up to 3VAUXI, requiring only a capacitor to ground for debouncing mechanical noise. For testing purposes, pulling SWB to 5 V enables the slot main power and disables the slot auxilliary power, bypassing the serial interface.               |  |  |

| TEST               | 23  | I   | When asserted on the rising edge of PGOOD, device enters test modes based on the states of the MODE pins. See <i>In–Circuit Test</i> section of the datasheet. When asserted after PGOOD is asserted, maps the Pwrenx and ANDed Faultx internal signals to PWRLED and ATTLED pins for test purposes. TEST has a 100-k $\Omega$ pull-down resistor to ground. |  |  |

| V5IN               | 49  | I   | 5-V input to the device. A 0.1- $\mu$ F bypass capacitor from V5IN to PWRGND is recommended.                                                                                                                                                                                                                                                                 |  |  |

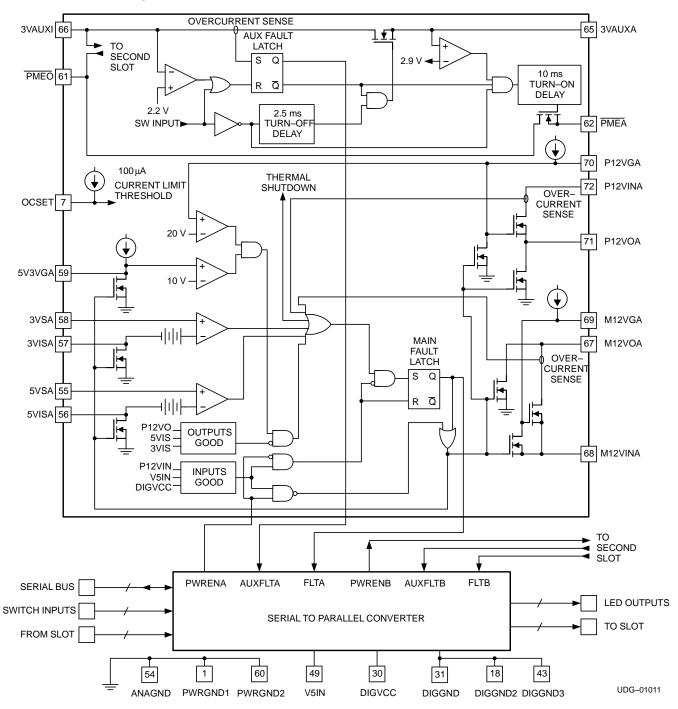

### functional block diagram

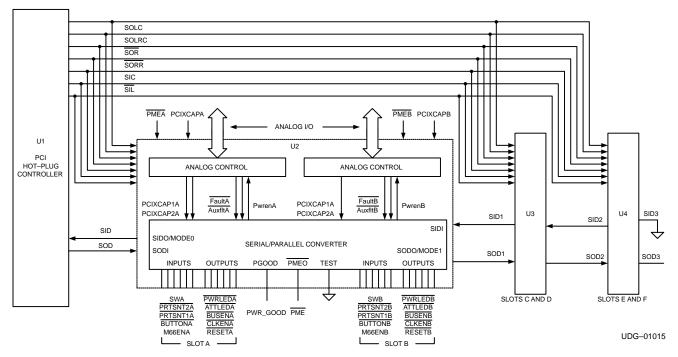

Figure 1 shows three TPS2340A devices cascaded in a system to control six PCI or PCI–X hot-plug slots. A hot-plug controller communicates with three TPS2340A devices over a nine-signal serial bus. Three signals are used to gather status information from the slots, and six signals are used to control the slots. In this bus, seven of the nine signals are connected in parallel. The remaining signals facilitate a cascaded bus and are comprised of the signal pair SIDI/SIDO and SODI/SODO. The SIDO signal drives the PCI hot-plug controller serial input data pin or the SIDI pin of another up–stream TPS2340A. The SODI signal is driven by the PCI hot-plug controller and is cascaded down to the next TPS2340A via the SODO signal.

The SIDO and SODO outputs are dual-function pins that also serve as mode-select pins upon the rising edge of PGOOD. See *Digital Circuits* section for more details.

Figure 1. Hot-Plug System Block Diagram

### analog circuits

#### power controller

The functional block diagram shows the TPS2340A with detailed information on the analog functions. For clarity, circuits for only one slot are shown in detail.

#### 3.3-V auxiliary supply (3.3-Vaux) support

In today's hot-plug systems, a 3.3Vaux rail remains live while the system power is shut down to allow implementation of the PCI Power Management Specification, version 1.1. The TPS2340A provides a 3.3-Vaux input pin that is monitored for undervoltage and generates a 3.3-Vaux supply pin for each hot-plug slot that is monitored for overcurrent. These supply pins are switched by the slot-specific SWx slot switch inputs. When the slot switch is opened, the slot-specific 3.3-Vaux supply is disabled to allow safe removal of the adapter card. When the slot switch is closed (SWx grounded), the slot-specific 3.3-Vaux supply is restored.

## **APPLICATION INFORMATION**

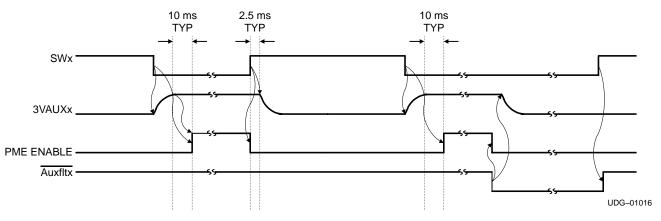

#### power cycling and PME

The PCI Power Management Specification defines a signal called PME (power management event) to allow power management events to be communicated back to the system. The TPS2340A provides a slot-specific PMEx input and a gated PMEO output pin that is monitored by the system. The gated PMEO output is controlled by the SWx slot switch similar to the 3.3-Vaux supply pins described above, but with a delay during connection as shown below. The purpose of the delay is to ensure that 3.3-Vaux power is stable to the slot before connecting the PMEx signal. (If the device were to observe the PMEx signal while 3.3-Vaux power was still ramping up, a false trigger could result.)

The 3.3-Vaux circuitry provides short-circuit fault detection. In the event of a fault, the slot 3.3-Vaux and PME signals are immediately disconnected. The fault state is latched internally in the TPS2340A and is cleared by opening the SWx slot switch or by the removal of the 3.3-Vaux power supplying the TPS2340.

Figure 2. 3.3Vaux and PME Gating

When SWx is closed, 3VAUXx power is immediately applied to the slot with controlled slew rate, minimizing inrush current into 3VAUXx bypass capacitors. After 3VAUXx power is above threshold, a delay timer starts. At the end of the delay timer cycle, the PMEx switches close, allowing connection of the PMEx signal to the PMEO output. When multiple TPS2340A devices are used in a system, the PMEO output pins can be connected to the same node, creating a *wired–OR* PME bus that can be connected to a system interrupt input.

When SWx is opened or if there is a power fault on channel x, the  $\overline{PMEx}$  switch for that channel is immediately opened and the 3VAUXx power for that channel is removed. Although these events happen at approximately the same time, the 3VAUXx power should remain high until the  $\overline{PMEx}$  switch is open so that falling 3VAUXx power doesn't cause a nuisance  $\overline{PMEx}$  interrupt. To insure that 3VAUXx remains high during a power fault, 3VAUXx should have a bypass capacitance of at least 20  $\mu$ F. If the capacitor is not available on the inserted card, it should be provided on the system board.

### fault handling

When PGOOD is asserted (main power is valid), the serial interface is available for use. At this time,  $\overline{Auxflt}$  and  $\overline{Faultx}$  (i.e.  $\overline{Faultx} = \overline{Pwrfltx} \bullet \overline{Auxflt}$ ) signals are present in the registers and can be read back over the serial interface.

When PGOOD is deasserted (main power is not valid), the serial interface is inactive, so the TPS2340A provides an alternate path for observing the Auxfltx signals. In this case, Auxfltx is presented on the ATTLEDx open-drain output, so 3Vaux faults can be observed. Systems that do not require Auxfltx indications when main power is off should use main power to supply current to the attention LEDs.

In addition, when TEST is asserted after PGOOD has changed from 0 to 1, the AND of Pwrfltx and Auxfltx is present on the ATTLEDx open-drain output, so the attention LEDs can be used to report any faults on each channel.

After PGOOD is asserted with TEST deasserted and the voltage on the SWx pin is greater than  $V_{DIGVCC}$  but less than  $V_{V5IN}$ , ATTLEDx follows the fault status of the main power fault (Pwrfltx). If the SWx input is pulled to  $V_{V5IN}$  potential, that slot becomes immediately enabled independent of serial interface status and ATTLEDx follows the fault status of the main power fault (Pwrfltx).

| SWx                                         | PGOOD | TEST | ATTLEDx           |

|---------------------------------------------|-------|------|-------------------|

| < VDIGVCC                                   | 0     | х    | Auxfltx           |

| < VDIGVCC                                   | 1     | 1    | Pwrfltx • Auxfltx |

| > V <sub>DIGVCC</sub> , < V <sub>V5IN</sub> | 1     | 0    | Pwrfltx           |

| = V <sub>V5IN</sub>                         | х     | х    | Pwrfltx           |

Table 1. Fault Reporting Using ATTLED

#### PCI–XCAP resolution

Add-in cards indicate their PCI-X mode and frequency capabilities by connection of the PCI-XCAP pin. The TPS2340A utilizes a three-level comparator to resolve the PCI-XCAP input so as to decode operating mode and generate the PCI-XCAP2 and PCI-XCAP1 internal signals. With PCI-XCAP open, the TPS2340A selects PCI-X 133-MHz operation. PCI-X 66-MHz operation is selected by a 10-k $\Omega$  pull-down resistor on PCI-XCAP. With PCI-XCAP grounded, conventional PCI-2.2 operation is selected. This decoding conforms to the standard PCI-X specification for PCI-XCAP resolution.

| PCI-XCAP                 | PCI-XCAP2 | PCI-XCAP1 | DESCRIPTION                    |

|--------------------------|-----------|-----------|--------------------------------|

| GND                      | 0         | 0         | Conventional PCI 2.2 operation |

| 10-kΩ Pull-down Resistor | 0         | 1         | PCI-X 66-MHz operation         |

| Open Circuit             | 1         | 1         | PCI-X 133-MHz operation        |

#### Table 2. PCI-XCAP Pin State Resolution

## **APPLICATION INFORMATION**

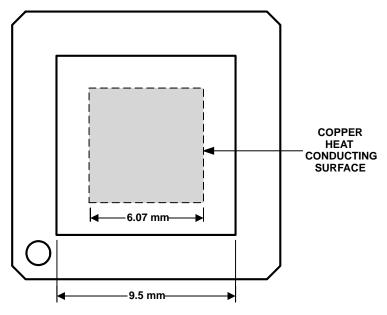

#### thermal shutdown

Under normal operating conditions, the power dissipation in the TPS2340A is low enough that junction temperature (T<sub>J</sub>) is not more than 15°C above air temperature. However, in the case of a load that exceeds PCI specifications but remains under the TPS2340A current-limit threshold, power dissipation can be higher. To prevent any damage from an out-of-specification load or severe rise in ambient temperature, the TPS2340A contains two independent thermal shutdown circuits, one for each slot's main supplies.

The highest power dissipation in the TPS2340A is from the 12-V power FET so the TPS2340A temperature sense elements are integrated closely with these FETs. These sensors indicate when the temperature at these transistors exceeds approximately 150°C, either due to average TPS2340A power dissipation, 12-V power FET power dissipation, or a combination of both.

When excessive junction temperature is detected on one slot, that slot fault latch is set and remains set until junction temperature drops by approximately 10°C and the slot is turned off, then on again through the serial interface. The other slot is not affected by this event. Also, 3.3-Vaux is not affected by thermal events.

#### digital circuits

The TPS2340A implements two independent slots of hot-plug power management. In addition, the TPS2340A contains digital circuits to allow communication between these two slots and the system's hot-plug controller. Also, the TPS2340A contains inputs for connection to mechanical switches and outputs for driving indicator LEDs to directly communicate with users and service.

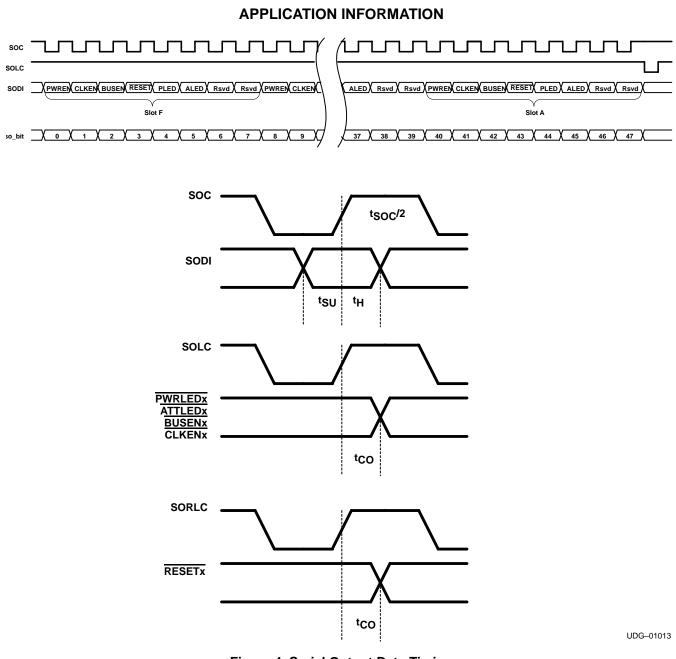

This digital logic implements a serial-to-parallel converter that accepts data from the serial interface and presents that data to each slot. Data from the serial interface drives the Pwrenx internal main power control signal. Additional data from the serial interface includes BUSENx and CLKENx outputs to activate bus switches, RESETx outputs to allow reset to each slot, and ATTLEDx and PWRLEDx outputs to indicate slot status to users.

The serial-to-parallel converter also accepts data from the slot and sends that data back on the serial interface. Data to the serial interface includes SWx and BUTTONx switch state, PRSNTnx bits, M66ENx and PCI–XCAPx bits to indicate board type, and internal fault signals Auxfltx and Faultx.

When the digital circuits are operating in *normal* mode, the serial interface is enabled and controls the slots. The TPS2340A also operates in various test modes, allowing board testing and system development.

Each TPS2340A controls two PCI/PCI–X slots. For systems requiring more than two slots, additional TPS2340A devices can be cascaded without requiring an additional hot-plug controller. To maintain system reliability and data integrity at full speed, bus length is often limited to six PCI slots. When higher speed PCI–X protocols are active, bus length may be limited to even fewer active slots. However, the TPS2340A is not limited in cascade capability or bus length.

#### power on configuration

Table 3. lists the various modes of operation and the proper pin states that are necessary to achieve these modes. The shaded rows indicate test modes.

| PGOOD      | TEST | SODO/MODE1 | SIDO/MODE0 | OPERATING MODE                                                            |

|------------|------|------------|------------|---------------------------------------------------------------------------|

| $\uparrow$ | 0    | 1          | 1          | Operational mode                                                          |

| $\uparrow$ | 1    | 0          | 0          | NAND tree test mode                                                       |

| $\uparrow$ | 1    | 0          | 1          | Tri-state test mode (all pins tri-stated)                                 |

| ↑          | 1    | 1          | Х          | Reserved                                                                  |

| ↑          | 0    | 0          | Х          | Reserved                                                                  |

| ↑          | 0    | Х          | 0          | Reserved                                                                  |

| 1          | 1    | SODO       | SIDO       | Normal operation, but Pwrenx driven on PWRLEDx, Faultx driven on ATTLEDx. |

| 1          | 0    | SODO       | SIDO       | Normal operation                                                          |

NOTE: X = Don't care, x = slot A or B

#### operational mode functional description

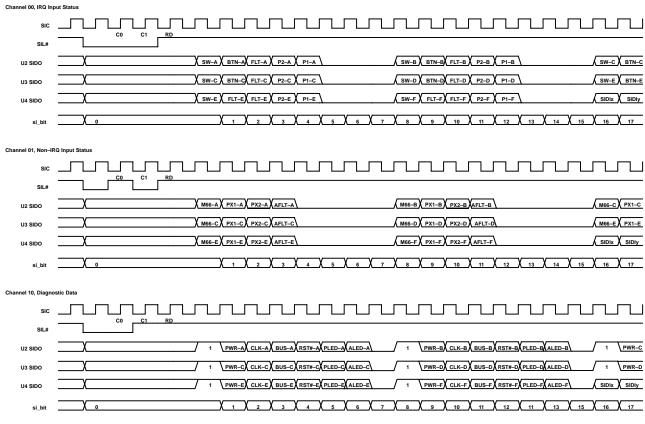

When both mode pins are 1 and the test pin is 0, on the rising edge of PGOOD, the TPS2340A enters operational mode. In this mode, the PCI hot-plug controller is able to address multiple TPS2340A ICs and multiple slots. Input status for all slots is grouped into four channels that can be requested by the PCI hot-plug controller.

#### channel selection

The PCI hot-plug controller indicates to the TPS2340A which channel to read back via signaling on the SIL pin. The SIL pin asserts low for one SIC clock to indicate a *start* bit, followed by three SIC clocks of channel address information in the order of channel address LSB followed by channel address MSB and a reserved bit. So as an example, if the hot-plug controller desires to read non-interrupt capable input data from the TPS2340A (channel 01 binary), the SIL sequence is shown in Table 3.

| CLOCK  | SIL STATUS                 |

|--------|----------------------------|

| 0      | Start bit (low)            |

| 1      | Channel address LSB (high) |

| 2      | Channel address MSB (low)  |

| 3      | Reserved (high)            |

| 4 – 47 | High                       |

#### operational mode input channel address grouping

Table 5. lists the functions assigned to the channel addresses.

#### Table 5. Operational Mode Channel Address Grouping

| CHANNEL<br>ADDRESS | FUNCTIONAL CHANNEL GROUP     |

|--------------------|------------------------------|

| 00                 | Interrupt capable inputs     |

| 01                 | Non-interrupt capable inputs |

| 10                 | Diagnostic data #1           |

| 11                 | Diagnostic data #2           |

As devices are cascaded, SIDI pin data is received from devices down-stream and passes through the device, shift-register style, to eventually reach the SIDO pin and the PCI hot-plug controller. The data contained in each input channel group is described in Tables 6, 7, 8, and 9.

| BIT<br>NUMBER | FUNCTION                                      |

|---------------|-----------------------------------------------|

| 0             | Slot A SW (1 = interlock A open)              |

| 1             | Slot A button state (1 = button A pushed)     |

| 2             | Slot A power fault state (PwrfltA & AuxfltA)  |

| 3             | Slot A PRSNT2                                 |

| 4             | Slot A PRSNT1                                 |

| 5             | Reserved                                      |

| 6             | Reserved                                      |

| 7             | Reserved                                      |

| 8             | Slot B SW                                     |

| 9             | Slot B button state                           |

| 10            | Slot B power fault state (PwrfltB & AuxfltB)  |

| 11            | Slot B PRSNT2                                 |

| 12            | Slot B PRSNT1                                 |

| 13            | Reserved                                      |

| 14            | Reserved                                      |

| 15            | Reserved                                      |

| 1647          | SIDI pin data for slots C, D, E and F follows |

#### Table 6. Channel 00 Data Group – Interrupt Capable Inputs

| BIT<br>NUMBER | FUNCTION                                      |

|---------------|-----------------------------------------------|

| 0             | Slot A M66EN                                  |

| 1             | Slot A PCI–XCAP1                              |

| 2             | Slot A PCI–XCAP2                              |

| 3             | Slot A Aux Power Fault state (AuxfltA)        |

| 4             | Reserved                                      |

| 5             | Reserved                                      |

| 6             | Reserved                                      |

| 7             | Reserved                                      |

| 8             | Slot B M66EN                                  |

| 9             | Slot B PCI–XCAP1                              |

| 10            | Slot B PCI–XCAP2                              |

| 11            | Slot B Aux Power Fault state (AuxfltB)        |

| 12            | Reserved                                      |

| 13            | Reserved                                      |

| 14            | Reserved                                      |

| 15            | Reserved                                      |

| 1647          | SIDI pin data for slots C, D, E and F follows |

## Table 8. Channel 10 Data Group – Diagnostic Channel #1

| BIT<br>NUMBER | FUNCTION                                                                                   |

|---------------|--------------------------------------------------------------------------------------------|

| 0             | Device Present<br>1 = Power controller is present<br>0 = Power controller is not installed |

| 1             | Slot A Pwren state                                                                         |

| 2             | Slot A CLKEN state (0 = clock enabled)                                                     |

| 3             | Slot A BUSEN state (0 = bus enabled)                                                       |

| 4             | Slot A PCIRST state (0 = reset asserted)                                                   |

| 5             | Slot A PWRLED state (1 = power LED on)                                                     |

| 6             | Slot A ATTLED state (1 = attention LED on)                                                 |

| 7             | Reserved                                                                                   |

| 8             | Device Present<br>1 = Power controller is present<br>0 = Power controller is not installed |

| 9             | Slot B Pwren state                                                                         |

| 10            | Slot B CLKEN state                                                                         |

| 11            | Slot B BUSEN state                                                                         |

| 12            | Slot B PCIRST state                                                                        |

| 13            | Slot B PWRLED state                                                                        |

| 14            | Slot B ATTLED state                                                                        |

| 15            | Reserved                                                                                   |

| 1647          | SIDI pin data for slots C, D, E and F follows                                              |

| BIT<br>NUMBER | FUNCTION                                                       |

|---------------|----------------------------------------------------------------|

| 0             | Slot A latched Mode 0 bit state. This bit is latched at PGOOD  |

| 1             | Slot A latched Mode 1 bit state. This bit is latched at PGOOD. |

| 2             | Must be set to 1.                                              |

| 3             | Reserved                                                       |

| 4             | Reserved                                                       |

| 5             | Reserved                                                       |

| 6             | Reserved                                                       |

| 7             | Reserved                                                       |

| 8             | Slot B latched Mode 0 bit state. This bit is latched at PGOOD. |

| 9             | Slot B latched Mode 1 bit state. This bit is latched at PGOOD. |

| 10            | Must be set to 1.                                              |

| 11            | Reserved                                                       |

| 12            | Reserved                                                       |

| 13            | Reserved                                                       |

| 14            | Reserved                                                       |

| 15            | Reserved                                                       |

| 1647          | SIDI pin data for slots C, D, E and F follows                  |

#### Table 9. Channel 11 Data Group – Diagnostic Channel #2

Figure 3. illustrates the input scan chain timing for operational mode.

Figure 3. Serial Input Data Timing

TEXAS INSTRUMENTS www.ti.com

Similar to input data, serial output data has been ordered to facilitate cascading TPS2340A devices. Assuming a six-slot implementation, as input data arrives in the order of slot A first, followed by data for slots B through F, output data is delivered in reverse order, slot F data first, then data for slots E through A. For a PCI hot-plug controller that supports 6 slots, 48 bits (8 per slot) are shifted out by the controller any time a slot control state needs to be changed. At the conclusion of a shift-out process, output data for slots A and B is contained in the device (electrically) closest to the PCI hot-plug controller. Output data for each slot is delivered in the bit order described in Table 10.

| BIT<br>NUMBER | FUNCTION                                        |

|---------------|-------------------------------------------------|

| 0             | Slot F Pwren state (1 = turn on power)          |

| 1             | Slot F CLKEN state (1 = enable the clock)       |

| 2             | Slot F BUSEN state (1 = enable the bus)         |

| 3             | Slot F PCIRST state (0 = assert PCIRST)         |

| 4             | Slot F PWRLED state (1 = turn on power LED)     |

| 5             | Slot F ATTLED state (1 = turn on attention LED) |

| 6             | Reserved                                        |

| 7             | Reserved                                        |

| 8             | Slot E Pwren state                              |

| 9             | Slot E CLKEN state                              |

| 10            | Slot E BUSEN state                              |

| 11            | Slot E PCIRST state                             |

| 12            | Slot E PWRLED state                             |

| 13            | Slot E ATTLED state                             |

| 14            | Reserved                                        |

| 15            | Reserved                                        |