# μPD7810/11 8-BIT, SINGLE-CHIP NMOS MICROCOMPUTERS WITH A/D CONVERTER

## Description

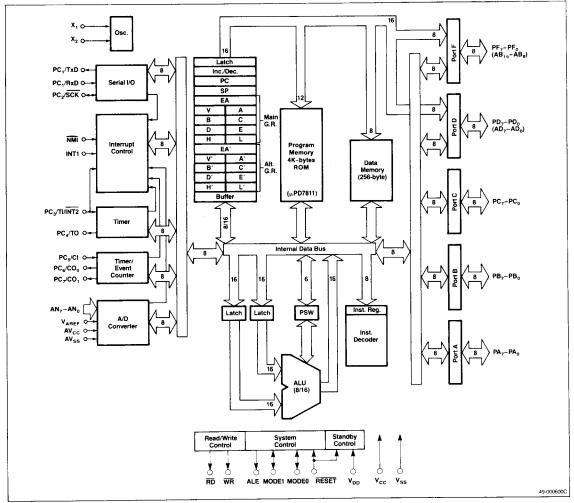

The  $\mu$ PD7810 and  $\mu$ PD7811 single-chip microcomputers integrate sophisticated on-chip peripheral functionality normally provided by external components. The device's internal 16-bit ALU and data paths, combined with a powerful instruction set and addressing, make the  $\mu$ PD7810/11 appropriate in data processing as well as control applications. The devices integrate a 16-bit ALU, 4K-ROM, 256-byte RAM with an 8-channel A/D converter, a multifunction 16-bit timer/ event counter, two 8-bit timers, a USART, and two zero-cross detect inputs on a single die, allowing their use in fast, high end processing applications. This involves analog signal interface and processing.

The  $\mu$ PD7811 is the mask-ROM high volume production device embedded with custom customer program. The  $\mu$ PD7810 is a ROM-less version for prototyping and small volume production. The  $\mu$ PD78PG11E is a piggy-back EPROM version for design development.

### Features

- NMOS silicon gate technology requiring +5 V power supply

- Complete single-chip microcomputer

- 16-bit ALU

- 4K x 8 ROM

- 256-byte RAM

- 44 I/O lines

- Two zero-cross detect inputs

- Two 8-bit timers

- □ Expansion capabilities

- 8085A bus-compatible

- 60K-byte external memory address range

- 8-channel, 8-bit A/D converter

- Autoscan mode

- Channel select mode

- Full duplex USART

- Synchronous and asynchronous

- 153 instructions

- 16-bit arithmetic, multiply and divide

- $\Box$  1  $\mu$ s instruction cycle time (12 MHz operation)

- Prioritized interrupt structure

3 external

- 8 internal

- □ Standby function

- □ On-chip clock generator

- □ 64-pin plastic QUIP or shrink DIP

#### **Pin Configuration**

| PA <sub>o</sub> [ | 1   | $\sim$     | 64 🛛 V <sub>cc</sub>  |                |

|-------------------|-----|------------|-----------------------|----------------|

| PA, [             |     |            | 63 🗖 V <sub>DD</sub>  |                |

| PA <sub>2</sub>   | 3   |            | 62 🖸 PD,              |                |

| PA3 [             | 4   |            | 61 🗖 PD <sub>6</sub>  |                |

| PA. [             | 5   |            | 60 ] PD₅              |                |

| PA <sub>s</sub>   | 6   |            | 59 D PD₄              |                |

| PA <sub>6</sub>   | 7   |            | 58 🖸 PD3              |                |

| PA, [             | 8   |            | 57 🗍 PD2              |                |

| РВ, С             | 9   |            | 56 D PD1              |                |

| РВ, 🗖             |     |            | 55 D PD。              |                |

| PB <sub>2</sub>   | 11  |            | 54 🗇 PF7              |                |

| PB <sub>3</sub>   | 12  |            | 53 🗋 PF6              |                |

| PB4 C             | 13  |            | 52 PFs                |                |

| PB₅ □             | 14  |            | 51 🔁 PF4              |                |

| PB <sub>6</sub>   |     | 11         | 50 🗗 PF3              |                |

| PB, [             |     | нРD7810/11 | 49 🗖 PF2              |                |

| PC, [             |     | PD7        | 48 PF,                |                |

|                   |     | a          | 47 D PFo              |                |

| PC <sub>2</sub>   |     |            | 46 🗋 ALE              |                |

| PC <sub>3</sub>   |     |            | 45 🖸 WR               |                |

| PC <sub>4</sub>   |     |            | 44 🗋 RD               |                |

| PC <sub>s</sub> _ |     |            | 43 AV <sub>cc</sub>   |                |

| PC <sub>6</sub> _ |     |            | 42 VAREF              |                |

| PC <sub>7</sub>   | t i |            | 41 AN7                |                |

| NMI C             |     |            | 40 🛛 AN <sub>6</sub>  |                |

|                   |     |            | 39 🗋 AN <sub>5</sub>  |                |

| MODE1             |     |            | 38 🗋 AN4              |                |

| RESET             |     |            | 37 AN3                |                |

|                   | 1   |            | 36 AN <sub>2</sub>    |                |

| X <sub>2</sub>    | 1   |            | 35 AN1                |                |

| ,×,□              |     |            | 34 AN                 |                |

| V <sub>ss</sub> [ | 32  |            | 33 🗍 AV <sub>SS</sub> |                |

|                   |     |            |                       | <br>49-000601A |

# **Ordering Information**

| Part Number                | Package Type              | Max Frequency<br>of Operation |  |  |

|----------------------------|---------------------------|-------------------------------|--|--|

| μPD7810G-36<br>μPD7811G-36 | 64-pin plastic QUIP       | 12 MHz                        |  |  |

| μPD7810CW<br>μPD7811CW     | 64-pin plastic shrink DIP | 12 MHz                        |  |  |

#### Pin Identification

| No.    | Symbol                                                                   | Function                                                   |

|--------|--------------------------------------------------------------------------|------------------------------------------------------------|

| 1-8    | PA0-PA7                                                                  | Port A I/O                                                 |

| 9-16   | PB0-PB7                                                                  | Port B I/O                                                 |

| 17     | PC <sub>0</sub> /TxD                                                     | Port C I/O line O/Transmit data output                     |

| 18     | PC <sub>1</sub> /RxD                                                     | Port C I/O line 1/Receive data input                       |

| 19     | PC <sub>2</sub> /SCK                                                     | Port C I/O line 2/Serial clock I/O                         |

| 20     | PC3/TI/<br>INT2                                                          | Port C I/O line 3/Timer input/Interrupt<br>request 2 input |

| 21     | PC <sub>4</sub> /TO                                                      | Port C I/O line 4/Timer output                             |

| 22     | PC5/CI                                                                   | Port C I/O line 5/Counter input                            |

| 23, 24 | PC <sub>6</sub> , PC <sub>7</sub> /<br>CO <sub>0</sub> , CO <sub>1</sub> | Port C I/O lines 6, 7/Counter outputs 0, 1                 |

| 25     | NMI                                                                      | Nonmaskable interrupt input                                |

| 26     | INT1                                                                     | Interrupt request 1 input                                  |

| 27     | MODE1/M1                                                                 | Mode 1 input/Memory cycle 1 output                         |

| 28     | RESET                                                                    | Reset input                                                |

| 29     | MODEO/<br>IO/M                                                           | Mode 0 input/I/O/Memory output                             |

| 30, 31 | X2, X1                                                                   | Crystal connections 1, 2                                   |

| 32     | V <sub>SS</sub>                                                          | Ground                                                     |

| 33     | AVSS                                                                     | Port T threshold voltage input                             |

| 34-41  | AN0-AN7                                                                  | A/D converter analog inputs 0-7                            |

| 42     | VAREF                                                                    | A/D converter reference voltage                            |

| 43     | AVCC                                                                     | A/D converter power supply                                 |

| 44     | RD                                                                       | Read strobe output                                         |

| 45     | WR                                                                       | Write strobe output                                        |

| 46     | ALE                                                                      | Address latch enable output                                |

| 47-54  | PF <sub>0</sub> -PF <sub>7</sub>                                         | Port F I/O/Expansiom memory address bu<br>(bits 8-15)      |

| 55-62  | PD <sub>0</sub> -PD <sub>7</sub>                                         | Port D I/O/Expansion memory address/<br>data bus           |

| 63     | V <sub>DD</sub>                                                          | RAM backup power supply                                    |

| 64     | V <sub>CC</sub>                                                          | 5 V power supply                                           |

## **Pin Functions**

#### PA0-PA7 [Port A]

Port A is an 8-bit three-state port. Each bit is independently programmable as either input or output. Reset makes all lines of port A inputs.

## PB0-PB7 [Port B]

Port B is an 8-bit three-state port. Each bit is independently programmable as either input or output. Reset makes all lines of port B inputs.

## PC0-PC7 [Port C]

Port C is an 8-bit three-state port. Each bit is independently programmable as either input or output. Alternatively, the lines of port C can be used as control lines for the USART and timer. Reset puts all lines of port C in port mode, input.

TxD [Transmit Data]. Serial data output terminal.

RxD [Receive Data]. Serial data input terminal.

**SCK** [Serial Clock]. Output for the serial clock when internal clock is used. Input for serial clock when external clock is used.

TI [Timer Input]. Timer input terminal.

**INT2** [Interrupt Request 2]. Falling-edge-triggered, maskable interrupt input terminal and AC-input, zero-cross detection terminal.

**TO** [**Timer Output**]. The output of TO is a square wave with a frequency determined by the timer/counter.

CI [Counter Input]. External pulse input to timer/event counter.

$CO_0$ ,  $CO_1$  [Counter Outputs 0, 1]. Programmable rectangular wave outputs based on timer/event counter.

## PD<sub>0</sub>-PD<sub>7</sub> [Port D]

Port D is an 8-bit three-state port. It can be programmed as either 8 bits of input or 8 bits of output. When external expansion memory is used, port D acts as the multiplexed address/data bus.

#### PF0-PF7 [Port F]

Port F is an 8-bit three-state port. Each bit is independently programmable as an input or output. When external expansion memory is used, port F outputs the high-order address bits.

#### AN0-AN7

These are the eight analog inputs to the A/D converter.  $AN_4$ - $AN_7$  can also be used as a digital input for falling edge detection.

#### AV<sub>SS</sub> [A/D Converter Power Ground]

$\mathrm{AV}_{\mathrm{SS}}$  is the ground potential for the A/D converter power supply.

#### NMI [Nonmaskable Interrupt]

Falling-edge-triggered nonmaskable interrupt input.

#### INT1 [Interrupt Request 1]

INT1 is a rising-edge-triggered, maskable interrupt input. It is also an AC-input, zero-cross detection terminal.

# RESET [Reset]

When the  $\overrightarrow{\text{RESET}}$  input is brought low, it initializes the  $\mu$ PD7810/11.

#### MODE1, MODE0 [Mode 1, 0]

The MODE1 and MODE0 inputs select the memory expansion mode. MODE1 also outputs the M1 signal during each opcode fetch. MODE0 outputs the IO/M signal.

#### VAREF [A/D Converter Reference]

$V_{\mbox{\scriptsize AREF}}$  set the upper limit for the A/D converter's conversion range.

### AV<sub>CC</sub> [A/D Converter Power]

This is the power supply voltage for the A/D converter.

### **RD** [Read Strobe]

The RD output goes low to gate data from external devices onto the data bus. RD goes high during reset.

#### WR [Write Strobe]

The WR output goes low to indicate that the data bus holds valid data. It is a strobe signal for external memory or I/O write operations. WR goes high during reset.

#### ALE [Address Latch Enable]

The ALE output latches the address signal to the output of PD<sub>0</sub>-PD<sub>7</sub>.

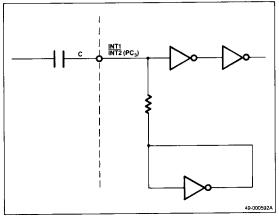

#### X1, X2 [Crystal Connections 1, 2]

X1 and X2 are the system clock crystal oscillator terminals. X1 is the input for an external clock.

#### V<sub>SS</sub> [Ground]

Ground potential.

#### V<sub>DD</sub> [Backup Power]

Backup power for on-chip RAM.

#### V<sub>CC</sub> [Power Supply]

+5 V power supply.

# **Block Diagram**

Ň

# **Functional Description**

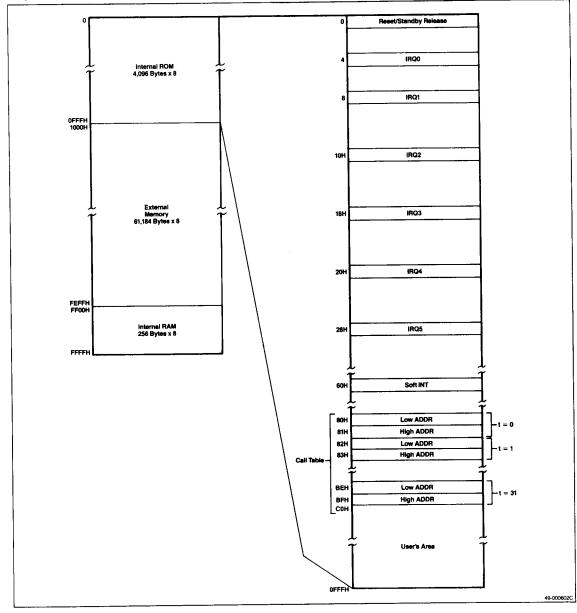

#### Memory Map

The  $\mu$ PD7811 can directly address up to 64K bytes of memory. Except for the on-chip ROM (0-4095) and RAM (65280-65535), any memory location can be used as ROM or RAM. The memory map, figure 1, defines the 0 to 64K byte memory space for the  $\mu$ PD7811.

### Input/Output

The  $\mu$ PD7810/11 has 8 analog input lines (AN<sub>0</sub>-AN<sub>7</sub>), 44 digital I/O lines, five 8-bit ports (port A, port B, port C, port D, port F), and 4 input lines (AN<sub>4</sub>-AN<sub>7</sub>).

Analog Input Lines.  $AN_0-AN_7$  are configured as analog input lines for on-chip A/D converter.

**Port A, Port B, Port C, Port F.** Each line of these ports can be individually programmed as an input or output. When used as I/O ports, all have latched outputs and high-impedance inputs.

**Port D.** Port D can be programmed as a byte input or a byte output.

$AN_4$ - $AN_7$ . The high order analog input lines,  $AN_4$ - $AN_7$ , can be used as digital input lines for falling edge detection.

**Control Lines.** Under software control, each line of port C can be configured individually to provide control lines for the serial interface, timer, and timer/counter.

**Memory Expansion.** In addition to the single-chip operation mode, the  $\mu$ PD7811 has four memory expansion modes. Under software control, port D can provide a multiplexed low-order address and data bus; port F can provide a high-order address bus. Table 1 shows the relation between memory expansion modes and the pin configurations of port D and port F.

#### Table 1. Memory Expansion Modes and Port Configurations

| Memory<br>Expansion |                                     | Port Configuration           |

|---------------------|-------------------------------------|------------------------------|

| None                | Port D                              | I/O port                     |

|                     | Port F                              | I/O port                     |

| 256 Bytes           | Port D                              | Multiplexed address/data bus |

|                     | Port F                              | I/O port                     |

| 4K Bytes            | Port D                              | Multiplexed address/data bus |

|                     | Port F <sub>0</sub> -F <sub>3</sub> | Address bus                  |

|                     | Port F <sub>4</sub> -F <sub>7</sub> | I/O port                     |

| 16K Bytes           | Port D                              | Multiplexed address/data bus |

|                     | Port F <sub>0</sub> -F <sub>5</sub> | Address bus                  |

|                     | Port F <sub>6</sub> -F <sub>7</sub> | I/O port                     |

| 60K Bytes           | Port D                              | Multiplexed address/data bus |

| -                   | Port F                              | Address bus                  |

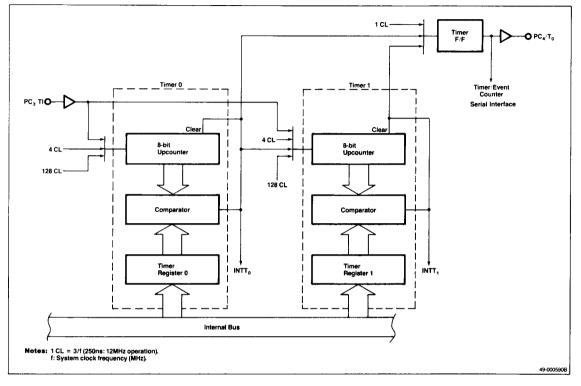

#### Timers

There are two 8-bit timers. The timers may be programmed independently or may be cascaded and used as an 8-bit timer with 8-bit prescaler. The timer can be software set to increment at intervals of four machine cycles (1  $\mu$ s at 12 MHz operation) or 128 machine cycles (32 $\mu$ s at 12 MHz), or to increment on receipt of a pulse at TI. Figure 2 shows the block diagram for the timer.

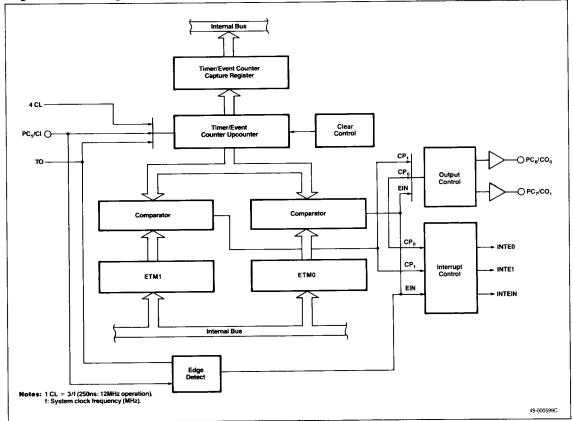

#### **Timer/Event Counter**

The 16-bit multifunctional timer/event counter (figure

- 3) can be used for the following operations:

- Interval timer

- External event counter

- Frequency measurement

- Pulse width measurement

- Programmable square-wave output

Figure 1. Memory Map

#### Figure 2. Timer Block Diagram

#### 8-Bit A/D Converter

- 8 input channels

- 4 conversion result registers

- 2 powerful operation modes

- Autoscan mode

- Channel select mode

- Successive approximation technique

- Absolute accuracy: ±1.5 LSB (±0.6%)

- Conversion range: 0 to 5 V

- Conversion time: 48 µs

- Interrupt generation

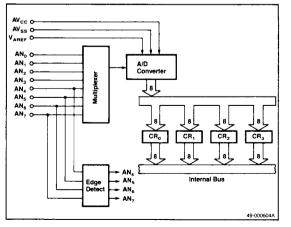

#### Analog/Digital Converter

The  $\mu$ PD7810/11 features an 8-bit, high speed, high accuracy A/D converter. The A/D converter is made up of a 256-resistor ladder and a successive approximation register (SAR). There are four conversion result registers (CR<sub>0</sub>-CR<sub>3</sub>). The 8-channel analog input may be operated in either of two modes. In the select mode, the conversion value of one analog input is sequentially stored in CR<sub>0</sub>-CR<sub>3</sub>. In the scan mode, the upper four channels or the lower four channels may be specified. Then those four channels will be consecutively selected and the conversion result stored sequentially in the four conversion result registers. Figure 4 shows the block diagram for the A/D converter.

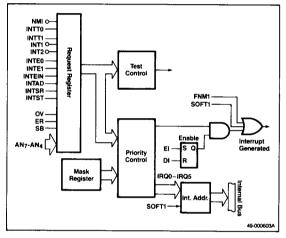

### Interrupt Structure

There are 11 interrupt sources. Three are external interrupts and eight are internal. The following, table 2, shows 11 interrupt sources divided into six priority levels. See figure 5.

### Standby Function

The standby function saves the top 32 bytes of RAM with backup power ( $V_{DD}$ ) if the main power ( $V_{CC}$ ) fails. On power-up, you can check the standby flag (SB) to determine whether recovery was made from standby mode or from a cold start.

| Interrupt<br>Request | Interrupt<br>Address | Type of Interrupt                                   | internal/<br>External |

|----------------------|----------------------|-----------------------------------------------------|-----------------------|

| IRQO 4               |                      | NMI (Nonmaskable interrupt)                         | Ext                   |

| IRQ1                 | 8                    | INTTO (Coincidence signal from timer 0)             | Int                   |

|                      |                      | INTT1 (Coincidence signal from timer 1)             |                       |

| IRQ2                 | 16                   | INT1 (Maskable interrupt)                           | Ext                   |

|                      |                      | INT2 (Maskable interrupt)                           |                       |

| IRQ3                 | 24                   | INTEO (Coincidence signal from timer/event counter) | Int                   |

|                      |                      | INTE1 (Coincidence signal from timer/event counter) |                       |

| IRQ4                 | 32                   | INTEIN (Falling signal of CI and TO counter)        | int/Ext               |

|                      |                      | INTAD (A/D converter interrupt)                     |                       |

| IRQ5                 | 40                   | INTSR (Serial receive interrupt)                    | Int                   |

|                      |                      | INST (Serial send interrupt)                        |                       |

#### Table 2. Interrupt Sources

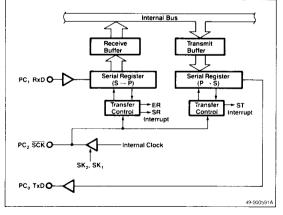

#### **Universal Serial Interface**

The serial interface can operate in one of three modes: synchronous, asynchronous, and I/O interface. The I/O interface mode transfers data MSB first, for easy interfacing to certain NEC peripheral devices. Synchronous and asynchronous modes transfer data LSB first. Synchronous operation offers two modes of data reception: search and nonsearch. In the search mode, data is transferred one bit at a time from the serial register to the receive buffer. This allows a software search for a sync character. In the nonsearch mode, data transfer from the serial register to the transmit buffer occurs eight bits at a time. Figure 6 shows the universal serial interface block diagram.

#### Figure 6. Universal Signal Interface Block Diagram

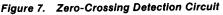

#### **Zero-Crossing Detector**

The INT1 and  $\overline{\text{INT2}}$  terminals (used common to TI and PC<sub>3</sub>) can detect the zero-crossing point of low-frequency AC signals. When driven directly, these pins respond as a normal digital input. Figure 7 shows the zero-crossing detection circuitry.

The zero-crossing detection capability allows you to make the 50-60 Hz power signal the basis for system timing and to control voltage phase-sensitive devices.

To use the zero-cross detection mode, an AC signal of approximately 1-3 VAC (peak-to-peak) and a maximum frequency of 1 kHz is coupled through an external capacitor to the INT1 and INT2 pins.

For the INT1 pin, the internal digital state is sensed as a 0 until the rising edge crosses the average DC level, when it becomes a 1 and INT1 interrupt is generated.

For the  $\overline{INT2}$  pin, the state is sensed as a 1 until the falling edge crosses the average DC level, when it becomes a 0 and  $\overline{INT2}$  interrupt is generated.

## **Absolute Maximum Ratings**

| Power supply volta                                                     | iges, V <sub>CC</sub> | -0.5 V to +7.0 V          |

|------------------------------------------------------------------------|-----------------------|---------------------------|

| V <sub>DD</sub>                                                        |                       | -0.5 V to +7.0 V          |

|                                                                        | AV <sub>CC</sub>      | -0.5 V to +7.0 V          |

|                                                                        | AV <sub>SS</sub>      | -0.5 V to +0.5 V          |

| Input voltage, V <sub>I</sub>                                          |                       | -0.5 V to +7.0 V          |

| Output voltage, V <sub>0</sub>                                         |                       | -0.5 V to +7.0 V          |

| Reference input voltage, V <sub>AREF</sub>                             |                       | -0.5 V to V <sub>CC</sub> |

| Operating temperature, $T_{OPR}$<br>10 MHz $\leq f_{XTAL} \leq$ 12 MHz |                       | -10°C to +70°C            |

| $f_{XTAL} \le 10 \text{ MHz}$                                          | <u></u>               | _40 °C to _85 °C          |

| Storage temperatu                                                      | re, T <sub>STG</sub>  | -65°C to +150°C           |

|                                                                        |                       |                           |

**Comment:** Exposing the device to stresses above those listed in absolute maximum ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum, rating conditions for extended periods may affect device reliability.

## **Operating Conditions**

| Oscillating Frequency                                   | TA               | V <sub>CC</sub> , AV <sub>CC</sub> |  |

|---------------------------------------------------------|------------------|------------------------------------|--|

| $f_{XTAL} \le 10 \text{ MHz}$                           | -40 °C to +85 °C | +5.0 V ±10%                        |  |

| $10 \text{ MHz} \le f_{\text{XTAL}} \le 12 \text{ MHz}$ | -10°C to +70°C   | $+5.0$ V $\pm 5\%$                 |  |

#### Capacitance

| -  |         | v _          | v - | $V_{SS} = 0 V$ |

|----|---------|--------------|-----|----------------|

| 1. | =25 °C: | $V \cap C =$ |     | V C C - U V    |

|    |         |              |     |                |

|                       |                | Limits |     |     |      | Test                                   |

|-----------------------|----------------|--------|-----|-----|------|----------------------------------------|

| Parameter             | Symbol         | Min    | Тур | Max | Unit | Conditions                             |

| Capacitance           | CI             |        |     | 10  | pF   | $Af_{c} = 1 MHz.$                      |

| Output<br>capacitance | C <sub>O</sub> |        |     | 20  | pF   | Unmeasured<br>pins returned<br>to 0 V. |

| I/O capacitance       | CIO            |        |     | 20  | pF   |                                        |

### **Recommended XTAL Oscillation Circuit**

#### **DC Characteristics**

$T_{A} = -10^{\circ}C \text{ to } +70^{\circ}C; V_{CC} = +5.0 \text{ V} \pm 5\%; V_{SS} = 0 \text{ V}; V_{DD} = V_{CC}$ - 0.8 V to V<sub>CC</sub>

|                                   |                   | L                   | imits |                 |      | Test                                                                                                                                              |

|-----------------------------------|-------------------|---------------------|-------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                         | Symbol            | Min                 | Тур   | Max             | Unit | Conditions                                                                                                                                        |

| Input low<br>voltage              | VIL               | 0                   |       | 0.8             | ۷    |                                                                                                                                                   |

| Input high<br>voltage             | V <sub>IH1</sub>  | 2.0                 |       | V <sub>CC</sub> | ۷    | All except SCK,<br>RESET, X1 and<br>X2                                                                                                            |

|                                   | V <sub>IH2</sub>  | 0.8 V <sub>CC</sub> |       | V <sub>CC</sub> | ۷    | SCK, X1, X2                                                                                                                                       |

|                                   | V <sub>IH3</sub>  | 0.8 V <sub>DD</sub> |       | V <sub>CC</sub> | ۷    | RESET                                                                                                                                             |

| Output low<br>voltage             | V <sub>OL</sub>   |                     |       | 0.45            | ۷    | $I_{OL} = 2.0 \text{ mA}$                                                                                                                         |

| Output high<br>voltage            | V <sub>OH</sub>   | 2.4                 |       |                 | ۷    | $I_{0H} = -200 \mu A$                                                                                                                             |

| Data<br>retention<br>voltage      | V <sub>DDDR</sub> | 3.2                 |       |                 | ۷    | $V_{CC} = 0 V;$<br>RESET = $V_{1L}$                                                                                                               |

| Input current                     | l <sub>i</sub>    |                     |       | ±200            | μA   | $\begin{array}{l} \text{INT1, TI(PC_3); +} \\ \text{0.45 V} \leq \text{V}_{\text{I}} < \\ \text{V}_{\text{CC}} \end{array}$                       |

| Input leakage<br>current          | ILI               |                     |       | ±10             | μA   | $\begin{array}{l} \text{All except} \\ \text{INT, TI(PC_3)} \\ \text{0 } \text{V} \leq \text{V}_{\text{I}} \leq \text{V}_{\text{CC}} \end{array}$ |

| Output leakage<br>current         | ILO               |                     |       | ±10             | μA   | $\begin{array}{l} +0.45 \text{ V} \leq \text{V}_0 \\ \leq \text{V}_{CC} \end{array}$                                                              |

| AV <sub>CC</sub> supply current   | AI <sub>CC</sub>  |                     | 6     | 12              | mΑ   |                                                                                                                                                   |

| V <sub>DD</sub> supply<br>current | IDD               |                     | 1.5   | 3.5             | mΑ   | T <sub>A</sub> = −40 to<br>+85°C                                                                                                                  |

|                                   |                   |                     |       | 3.2             | mA   | $V_{CC} = V_{DD} =$<br>5 V T <sub>A</sub> = -10 to<br>+70 °C                                                                                      |

| V <sub>CC</sub> supply<br>current | lcc               |                     | 150   | 220             | mA   | $T_A = -40 \text{ to} +85 \text{ °C}; V_{CC} = V_{DD} = 5 \text{ V}$                                                                              |

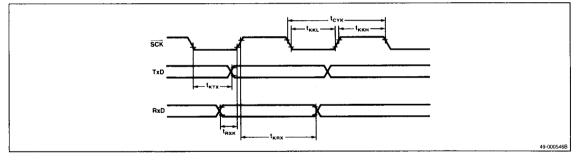

# **Serial Operation**

|                          |                  | Lin | nits |      | Test          |

|--------------------------|------------------|-----|------|------|---------------|

| Parameter                | Symbol           | Min | Max  | Unit | Conditions    |

| SCK cycle time           | t <sub>CYK</sub> | 1   |      | μS   | SCK input (1) |

|                          |                  | 500 |      | ns   | (2)           |

|                          |                  | 2   |      | μS   | SCK output    |

| SCK width low            | t <sub>KKL</sub> | 750 |      | ns   | SCK input(1)  |

|                          |                  | 200 |      | ns   | SCK input (2) |

|                          |                  | 900 |      | ns   | SCK output    |

| SCK width high           | <sup>t</sup> ккн | 750 |      | ns   | SCK input (1) |

|                          |                  | 200 |      | ns   | SCK input (2) |

|                          |                  | 900 |      | пs   | SCK output    |

| RxD set-up time to SCK 1 | t <sub>RXK</sub> | 80  |      | ns   | (1)           |

| RxD hold time after      | t <sub>KRX</sub> |     | 80   | ns   | (1)           |

| SCK↓TxD delay time       | t <sub>KTX</sub> |     | 210  | ns   | (1)           |

#### Note:

(1) 1x baud rate in asynchronous, synchronous, or I/O interface mode.

(2) 16x baud rate or 64x baud rate in asynchronous mode.

## **Zero-Cross Characteristics**

|                                      |                 | Limits |      |           | Test               |  |

|--------------------------------------|-----------------|--------|------|-----------|--------------------|--|

| Parameter                            | Symbol          | Min    | Max  | Unit      | Conditions         |  |

| Zero-cross detection<br>input        | V <sub>ZX</sub> | 1      | 3    | V ac, p-p | Ac coupled         |  |

| Zero-cross accuracy                  | A <sub>ZX</sub> |        | ±135 | mV        | 60-Hz sine<br>wave |  |

| Zero-cross detection input frequency | fzx             | 0.05   | 1    | kHz       |                    |  |

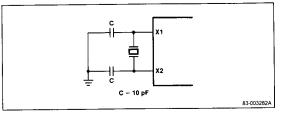

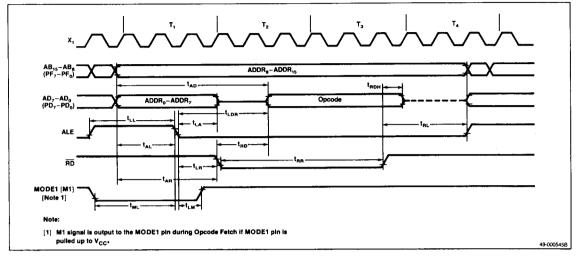

# **AC Characteristics**

**Read/Write Operation**  $V_{SS} = 0 V, V_{CC} - 0.8 V \le V_{DD} \le V_{CC}$

|                            |                  |         | Lim    |         |        |      |                              |

|----------------------------|------------------|---------|--------|---------|--------|------|------------------------------|

|                            |                  | fxtal = | 10 MHz | fxtal = | 12 MHz |      | Test                         |

| Parameter                  | Symbol           | Min     | Max    | Min     | Max    | Unit | Conditions (1)               |

| RESET pulse width          | t <sub>RP</sub>  | 6.0     |        | 5.0     |        | μS   |                              |

| Interrupt pulse width      | t <sub>IP</sub>  | 3.6     |        | 3.0     |        | μS   |                              |

| Counter input pulse width  | t <sub>CI</sub>  | 600     |        | 500     |        | ns   | Event counter mode           |

|                            | t <sub>Ci</sub>  | 4.8     |        | 4.0     |        | μS   | Pulse width measurement mode |

| Timer input pulse width    | t <sub>TI</sub>  | 600     |        | 500     |        | ns   |                              |

| X1 Input cycle time        | tCYC             | 100     | 250    | 83      | 250    | ns   |                              |

| Address set-up to ALE ↓    | t <sub>AL</sub>  | 100     |        | 65      |        | ns   |                              |

| Address hold after ALE     | tLA              | 70      |        | 50      |        | ns   |                              |

| Address to RD ↓ delay time | t <sub>AR</sub>  | 200     |        | 150     |        | ns   |                              |

| RD ↓ to address floating   | tAFR             |         | 20     |         | 20     | ns   |                              |

| Address to data input      | t <sub>AD</sub>  |         | 480    |         | 360    | ns   |                              |

| ALE↓ to data input         | tLDR             |         | 300    |         | 215    | ns   |                              |

| RD ↓ to data input         | t <sub>RD</sub>  |         | 250    |         | 180    | ns   |                              |

| ALE 1 to RD 1 delay time   | t <sub>LR</sub>  | 50      |        | 35      |        | ns   |                              |

| Data hold time to RD 1     | t <sub>RDH</sub> | 0       |        | 0       |        | ns   |                              |

| RD 1 to ALE 1 delay time   | t <sub>RL</sub>  | 150     |        | 115     |        | ns   |                              |

| RD width low               | t <sub>RR</sub>  | 350     |        | 280     |        | ns   | Data read                    |

|                            |                  | 650     |        | 530     |        | ns   | Opcode fetch                 |

| ALE width high             | tLL              | 160     |        | 125     | _      | ns   |                              |

| M1 setup time to ALE       | t <sub>ML</sub>  | 100     |        | 65      |        | ns   |                              |

| M1 hold time after ALE     | tLM              | 70      |        | 50      |        | ns   |                              |

| IO/M setup time to ALE     | tıL              | 100     |        | 65      |        | ns   |                              |

| IO/M hold time after ALE   | tLI              | 70      |        | 50      |        | ns   |                              |

| Address to ₩R ↓ delay      | t <sub>AW</sub>  | 200     |        | 150     |        | ns   |                              |

| ALE I to data output       | tLDW             |         | 210    |         | 195    | ns   |                              |

| WR↓ to data output         | twp              |         | 100    |         | 100    | ns   |                              |

| ALE I to WR I delay        | tLW              | 50      |        | 35      |        | ns   |                              |

| Data set-up time to WR 1   | t <sub>DW</sub>  | 300     |        | 230     |        | ns   |                              |

| Data hold time to WR 1     | twDH             | 130     |        | 95      |        | ns   |                              |

| WR 1 to ALE 1 delay time   | twi              | 150     |        | 115     |        | ns   |                              |

| WR width low               | tww              | 350     |        | 280     |        | ns   |                              |

#### Note:

(1) Load capacitance:  $C_L = 150 \text{ pF}.$

### **A/D** Converter Characteristics

$T_A = -10$  °C to +70 °C;  $V_{CC} = AV_{CC} = 5.0 V \pm 5\%$ ;  $V_{SS} = AV_{SS} = 0 V$ ;  $V_{AREF} = AV_{CC} - 0.5 V \text{ to } AV_{CC}$

|                                |                 |     | Limits |               |      | Test                                                                                               |

|--------------------------------|-----------------|-----|--------|---------------|------|----------------------------------------------------------------------------------------------------|

| Parameter                      | Symbol          | Min | Тур    | Max           | Unit | Conditions                                                                                         |

| Resolution                     |                 | 8   |        |               | Bits |                                                                                                    |

| Absolute<br>accuracy           |                 |     |        | 0.4%<br>± 1/2 | LSB  | T <sub>A</sub> = −10 °C to<br>+50 °C                                                               |

|                                |                 |     |        | 0.6%<br>±1/2  | LSB  | $T_{A} = -10 \text{ °C to} +70 \text{ °C (Note 1)}$                                                |

| Conversion<br>time             | tCONV           | 576 |        |               | tcyc | $\begin{array}{l} \textbf{83 ns} \leq \textbf{t}_{\text{CYC}} \leq \\ \textbf{110 ns} \end{array}$ |

|                                |                 | 432 |        |               | tcyc | $\begin{array}{l} \text{110 ns} \leq t_{\text{CYC}} \leq \\ \text{170 ns} \end{array}$             |

| Sampling<br>time               | tsamp           | 96  |        |               | tcyc | $\begin{array}{l} \text{83 ns} \leq t_{\text{CYC}} \leq \\ \text{110 ns} \end{array}$              |

|                                |                 | 72  |        |               | tcyc | $\begin{array}{l} 110 \text{ ns} \leq t_{\text{CYC}} \leq \\ 170 \text{ ns} \end{array}$           |

| Analog<br>input voltage        | VIA             | 0   |        | VAREF         | ۷    |                                                                                                    |

| Analog<br>resistance           | R <sub>AN</sub> |     | 1000   |               | MΩ   |                                                                                                    |

| Analog<br>reference<br>current | AREF            | 0.2 | 0.5    | 1.5           | mA   |                                                                                                    |

#### Note:

(1) In case of  $f_{XTAL} \le 10$  MHz,  $T_A = -40$  °C to +85 °C.

## **Bus Timing Depending on t<sub>CYC</sub>**

| Symbol              | <b>Calculating Expression</b> | Min/Max |

|---------------------|-------------------------------|---------|

| t <sub>RP</sub>     | 60T                           | Min     |

| t <sub>TI</sub>     | 6T                            | Min     |

| t <sub>CI</sub> (2) | 6T                            | Min     |

| t <sub>CI</sub> (3) | 48T                           | Min     |

| t <sub>IP</sub>     | 36T                           | Min     |

| t <sub>AL</sub>     | 2T — 100                      | Min     |

| t <sub>LA</sub>     | T — 30                        | Min     |

| t <sub>AR</sub>     | 3T — 100                      | Min     |

| t <sub>ad</sub>     | 7T — 220                      | Мах     |

| tldr                | 5T — 200                      | Max     |

| t <sub>RD</sub>     | 4T - 150                      | Max     |

| tLR                 | T — 50                        | Min     |

| t <sub>RL</sub>     | 2T 50                         | Min     |

| t <sub>RR</sub>     | 4T – 50 (Data Read)           | Min     |

|                     | 7T – 50 (Opcode Fetch)        |         |

| t <sub>LL</sub>     | 2T - 40                       | Min     |

| t <sub>AW</sub>     | 3T -100                       | Min     |

| tldw                | T + 110                       | Мах     |

| tLW                 | T — 50                        | Min     |

| tow                 | 4T — 100                      | Min     |

| twoh                | 2T — 70                       | Min     |

| twL                 | 2T - 50                       | Min     |

| tww                 | 4T — 50                       | Min     |

| tсүк                | 20T (SCK input)(1)            | Min     |

|                     | 24T (SCK output)              |         |

| t <sub>KKL</sub>    | 10T - 80 (SCK input)(1)       | Min     |

|                     | 12T — 100 (SCK output)        | *       |

| t <sub>KKH</sub>    | 10T - 80 (SCK input)(1)       | Min     |

|                     | 12T — 100 (SCK output)        |         |

#### Note:

(1) 1x Baud rate in asynchronous, synchronous, or I/O interface mode.

$T = t_{CYC} = 1/f_{XTAL}.$  The items not included in this list are independent of oscillator frequency (f<sub>XTAL</sub>).

(2) Event counter mode.

(3) Pulse width measurement mode.

# **Timing Waveforms**

#### **Read Operation**

## Write Operation

1.1

# **Timing Waveforms (cont)**

# **Opcode Fetch Operation**

## Serial Operation Transmit/Receive Timing

# **Operand Format/Description**

| Format                      | Description                                                                                                                                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r<br>r1<br>r2               | V, A, B, C, D, E, H, L<br>EAH, EAL, B, C, D, E, H, L<br>A, B, C                                                                                                                                    |

| sr1                         | PA, PB, PC, PD, PF, MKH, MKL, ANM, SMH, SML, EOM,<br>ETMM, TMM, MM, MCC, MA, MB, MC,<br>MF, TxB, TM <sub>0</sub> , TM <sub>1</sub><br>PA, PB, PC, PD, PF, MKH, MKL, ANM, SMH, EOM, TMM, RXB,       |

| sr2<br>sr3<br>sr4           | CR0, CR1, CR2, CR3<br>PA, PB, PC, PD, PF, MKH, ANM, MKL, SMH, EOM, TMM<br>ETM <sub>0</sub> , ETM <sub>1</sub><br>ECNT, ECPT                                                                        |

| rp<br>rp1<br>rp2<br>rp3     | SP, B, D, H<br>V, B, D, H, EA<br>SP, B, D, H, EA<br>B, D, H                                                                                                                                        |

| rpa<br>rpa1<br>rpa2<br>rpa3 | B, D, H, D+ , H + , D -, H -<br>B, D, H<br>B, D, H<br>B, D, H, D +, H + , D -, H -, D + byte, H + A, H + B,<br>H + EA, H + byte<br>D, H, D + +, H + +, D + byte, H + A, H + B, H + EA,<br>H + byte |

| wa                          | 8-Bit immediate data                                                                                                                                                                               |

| word<br>byte<br>bit         | 16-Bit immediate data<br>8-Bit immediate data<br>3-Bit immediate data                                                                                                                              |

| f                           | CY, HC, Z                                                                                                                                                                                          |

| irf                         | FNMI, FT0, FT1, F1, F2, FE0, FE1, FEIN, FAD, FSR, FST, ER, OV, AN4, AN5, AN6, AN7, SB                                                                                                              |

## Instruction Set Symbol Definitions

| Symbol | Description                   |

|--------|-------------------------------|

| -      | Transfer direction, result    |

| ٨      | Logical product (logical AND) |

| V      | Logical sum (logical OR)      |

| +      | Exclusive OR                  |

|        | Complement                    |

| •      | Concatenation                 |

#### Remarks

| 1. sr-sr4 (special register)           |                                     |

|----------------------------------------|-------------------------------------|

| PA = Port A                            | ECNT = Timer/Event                  |

| PB = Port B                            | Counter Upcounter                   |

| PC = Port C                            | ECPT = Timer/Event                  |

| PD = Port D                            | Counter Capture                     |

| PF = Port F                            | obulitor ouplairo                   |

| MA = Mode A                            | ETMM = Timer/Event                  |

| MB = Mode B                            | Counter Mode                        |

| MC = Mode C                            | EOM = Timer/Event                   |

| MCC = Mode Control C                   | Counter Output Mode                 |

| MF = Mode F                            | oblitter output mode                |

|                                        | TxB = TX Buffer                     |

| MM = Memory Mapping                    | $R_{XB} = RX Buffer$                |

|                                        | SMH = Serial Mode High              |

| $TM_0 = Timer Register 0$              | SML = Serial Mode Low               |

| TM <sub>1</sub> = Timer Register 1     | MKH = Mask High                     |

| TMM = Timer Mode                       |                                     |

| $ETM_0 = Timer/Event$                  | MKL = Mask Low                      |

| Counter Register 0                     | ANM = A/D Channel Mode              |

| ETM <sub>1</sub> = Timer/Event Counter | $CR_0 = A/D$ Conversion Result 0-3  |

| Register 1                             | to CR <sub>3</sub>                  |

| 2. rp-rp3 (register pair)              |                                     |

| SP = Stack Pointer                     | H = HL                              |

| B = BC                                 | V = VA                              |

| D=DE                                   | EA = Extended Accumulator           |

| 3. rpa-rpa3 (rp addressing)            |                                     |

| B = (BC)                               | D + + = (DE) + +                    |

| $\mathbf{D} = (\mathbf{D}\mathbf{E})$  | H + + = (HL) + +                    |

| H = (HL)                               | D + byte = (DE) + byte              |

| D + = (DE) +                           | H + A = (HL) + (A)                  |

| H - = (HL) +                           | H + B = (HL) + (B)                  |

| D - = (DE) -                           | H + EA = (HL) + (EA)                |

| H - = (HL) -                           | H + byte = (HL) + byte              |

| 4. f (flag)                            |                                     |

|                                        | lalf Carry Z = Zero                 |

| 5. irf (interrupt flag)                |                                     |

| NMI = NMi* Input                       | FEIN = INTFEIN                      |

| nam – nam mpar                         | FAD = INTFAD                        |

| FT0 = INTFT0                           | FSR = INTFSR                        |

|                                        | FST = INTFST                        |

| FT1 = INTFT1                           | FST = INTFST<br>ER = Error          |

| F1 = INTF1                             |                                     |

| F2 = INTF2                             | OV = Overflow                       |

| FE0 = INTFE0                           | $AN_4$ to $AN_7 = Analog Input 4-7$ |

| FE1 = INTFE1                           | SB = Standby                        |

|                                        |                                     |

| Set   |  |

|-------|--|

| ction |  |

| istru |  |

| -     |  |

|                             |                  |                                                                                                                                | 18                                                                  | 83                                                                                            |                 |          |                                      |

|-----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------|----------|--------------------------------------|

| Mnemonic                    | Mnemonic Operand | Operation                                                                                                                      | 83<br>76543210                                                      | B4<br>76543210                                                                                | State(1)        | Bytes    | Skip<br>Condition                    |

| 8-Bit Data Transfer         | ansfer           |                                                                                                                                |                                                                     |                                                                                               | -<br>-          |          |                                      |

| MOV                         | r1,A             | (r1) ← (A)                                                                                                                     | 0 0 0 1 1 1 <sub>2</sub> 1 <sub>1</sub> 1 <sub>0</sub>              |                                                                                               | 4               | -        |                                      |

|                             | A, r1            | (A) ← (r1)                                                                                                                     | 0 0 0 0 1 T <sub>2</sub> T <sub>1</sub> T <sub>0</sub>              |                                                                                               | 4               | -        |                                      |

|                             | *sr,A            | $(sr) \leftarrow (A)$                                                                                                          | 0 1 0 0 1 1 0 1                                                     | 1 1 S <sub>5</sub> S <sub>4</sub> S <sub>3</sub> S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | ₽               | 2        |                                      |

|                             | *A,Sr1           | (A) ← (sr1)                                                                                                                    | 0 1 0 0 1 1 0 0                                                     | 1 1 S <sub>5</sub> S <sub>4</sub> S <sub>3</sub> S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | ₽               | 2        |                                      |

|                             | r,word           | (r) (word)                                                                                                                     | 0 1 1 1 0 0 0 0                                                     | 0 1 1 0 1 R <sub>2</sub> R <sub>1</sub> R <sub>0</sub>                                        | 17              | 4        |                                      |

|                             |                  |                                                                                                                                | Low addr                                                            | High addr                                                                                     |                 |          |                                      |

|                             | word,r           | word,r (word) 🗝 (r)                                                                                                            | 0 1 1 1 0 0 0 0                                                     | 0 1 1 1 1 R <sub>2</sub> R <sub>1</sub> R <sub>0</sub>                                        | 17              | 4        |                                      |

|                             |                  |                                                                                                                                | Low addr                                                            | High addr                                                                                     |                 |          |                                      |

| MVI                         | *r,byte          | (r) ← byte                                                                                                                     | 0 1 1 0 1 R <sub>2</sub> R <sub>1</sub> R <sub>0</sub>              | Data                                                                                          | 7               | 2        |                                      |

|                             |                  | set L1 if r = A<br>set L0 if r = L                                                                                             |                                                                     |                                                                                               |                 |          | L1 = 1 and $r = AL0 = 1$ and $r = L$ |

|                             | sr2,byte         | sr2,byte (sr2) ← byte                                                                                                          | 0 1 1 0 0 1 0 0                                                     | S <sub>3</sub> 0 0 0 0 S <sub>2</sub> S <sub>1</sub> S <sub>0</sub>                           | 14              | e        |                                      |

|                             |                  |                                                                                                                                | Data                                                                |                                                                                               |                 |          |                                      |

| MVIW                        | *wa, byte        | *wa, byte ((V)•(wa)) ← byte                                                                                                    | 0 1 1 1 0 0 0 1                                                     | Offset                                                                                        | t               | e        |                                      |

|                             |                  |                                                                                                                                | Data                                                                |                                                                                               |                 |          |                                      |

| MVIX                        | *rpa1,byte       | *rpa1,byte (rpa1) byte                                                                                                         | 0 1 0 0 1 0 A <sub>1</sub> A <sub>0</sub>                           | Data                                                                                          | 10              | 2        |                                      |

| STAW                        | *wa              | ((V)•(wa)) → A                                                                                                                 | 0 1 1 0 0 0 1 1                                                     | Offset                                                                                        | 10              | 2        |                                      |

| LDAW                        | *wa              | (A) ← ((V)•(wa))                                                                                                               | 0 0 0 0 0 0 1                                                       | Offset                                                                                        | 9               | 2        |                                      |

| STAX                        | *rpa2            | (rpa2) $\leftarrow$ (A)                                                                                                        | A <sub>3</sub> 0 1 1 1 A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | Data (2)                                                                                      | 7/13(3)         | 2        |                                      |

| LDAX                        | *rpa2            | (A) ← ((rpa2))                                                                                                                 | A <sub>3</sub> 0 1 0 1 A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | Data (2)                                                                                      | 7/13(3)         | 2        |                                      |

| EXX                         |                  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                           | 0 0 0 1 0 0 0 1                                                     |                                                                                               | 4               | -        |                                      |

| EXA                         |                  | $(V) \leftrightarrow (V'), (A) \leftrightarrow (A'), (EA) \leftrightarrow (EA')$                                               | 0 0 0 1 0 0 0 0                                                     |                                                                                               | 4               | -        |                                      |

| EXH                         |                  | $(H) \leftrightarrow (H), (L) \leftrightarrow (L)$                                                                             | 0 1 0 1 0 0 0 0                                                     |                                                                                               | 4               | -        |                                      |

| <b>16-Bit Data Transfer</b> | fransfer         |                                                                                                                                |                                                                     |                                                                                               |                 |          |                                      |

| BLOCK                       | Q                | ((DE) $\leftarrow$ ((HL)),(DE) $\leftarrow$ (DE + 1),<br>(HL) $\leftarrow$ (HL) + 1, (C) $\leftarrow$ (C) - 1<br>End if borrow | 0 0 1 1 0 0 0 1                                                     |                                                                                               | 13 ×<br>(C + 1) | <b>F</b> |                                      |

| DMOV                        | rp3, EA          | $(rp3_{L}) \leftarrow (EAL), (rp3_{H}) \leftarrow (EAH)$                                                                       | 1 0 1 1 0 1 P <sub>1</sub> P <sub>0</sub>                           |                                                                                               | 4               | -        |                                      |

|                             | EA ro3           | /EAL) + //m3-//EAU) + //m3-/                                                                                                   |                                                                     |                                                                                               |                 | Ŧ        |                                      |

4

|               |                             |                                                                                             | <b>=</b>   1                                                        | 2 1                                                                 |          |       | Skin                  |

|---------------|-----------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|----------|-------|-----------------------|

| Mnemonic      | Mnemonic Operand            | Operation                                                                                   | 7 6 5 4 3 2 1 0                                                     | 76543210                                                            | State(1) | Bytes | Condition             |

| 16-Bit Data 1 | 16-Bit Data Transfer (cont) |                                                                                             |                                                                     |                                                                     |          |       |                       |

| DMOV          | sr3, EA                     | (sr3) (EA)                                                                                  | 0 1 0 0 1 0 0 0                                                     | 1 1 0 1 0 0 1 U <sub>0</sub>                                        | 14       | 2     |                       |

|               |                             | (EA) +- (Sr4)                                                                               | 0 1 0 0 1 0 0 0                                                     | 1 1 0 0 0 0 V <sub>1</sub> V <sub>0</sub>                           | 14       | 2     |                       |

| SBCD          |                             |                                                                                             | 0 1 1 1 0 0 0 0                                                     | 0 0 0 1 1 1 1 0                                                     | 20       | 4     |                       |

|               |                             |                                                                                             | Low addr                                                            | addr                                                                |          |       |                       |

| SDED          | word                        | $(word) \leftarrow (E), (word + 1) \leftarrow (D)$                                          | 0 1 1 1 0 0 0 0 0                                                   | 0 0 1 0 1 1 1 0<br>Hinh addr                                        | 20       | 4     |                       |

| SHLD          | word                        | (word) $\leftarrow$ (L), (word + 1) $\leftarrow$ (H)                                        | 0 1 1 1 0 0 0 0                                                     | 0 0 1 1 1 1 0                                                       | 20       | 4     |                       |

|               |                             |                                                                                             | Low addr                                                            | High addr                                                           |          |       |                       |

| SSPD          | word                        | $(word) \leftarrow (SP_L).(word + 1) \leftarrow (SP_H)$                                     | 0 1 1 1 0 0 0 0                                                     | 0 0 0 0 1 1 1 0                                                     | 20       | 4     |                       |

|               |                             |                                                                                             | Low addr                                                            | High addr                                                           |          |       |                       |

| STEAX         | гра3                        | ((rpa3)) ← (EAL),((rpa3) + 1 ← (EAH)                                                        |                                                                     | 1 0 0 1 C <sub>3</sub> C <sub>2</sub> C <sub>1</sub> C <sub>0</sub> | 14/20(3) | e,    |                       |

|               | word                        | $(C) \leftarrow (mord) (R) \leftarrow (mord + 1)$                                           | 0 1 1 1 0 0 0 0                                                     | 0 0 0 1 1 1 1 1                                                     | 20       | 4     |                       |

|               |                             |                                                                                             | Low addr                                                            |                                                                     |          |       |                       |

| LDED          | word                        | $(E) \leftarrow (word), (D) \leftarrow (word + 1)$                                          | 0 1 1 1 0 0 0 0                                                     | 0 0 1 0 1 1 1 1                                                     | 20       | 4     |                       |

|               |                             |                                                                                             | Low addr                                                            | High addr                                                           |          |       |                       |

| LHLD          | word                        | $(L) \leftarrow (word), (H) \leftarrow (word + 1)$                                          | 0 1 1 1 0 0 0 0                                                     | 0 0 1 1 1 1 1 1 1                                                   | 20       | 4     |                       |

|               |                             |                                                                                             | Low addr                                                            | High addr                                                           |          |       |                       |

| LSPD          | word                        | $(SP_L) \leftarrow (word), (SP_H) \leftarrow ((word) + 1)$                                  | 0 1 1 1 0 0 0 0                                                     | 0 0 0 0 1 1 1 1                                                     | 20       | 4     |                       |

|               |                             |                                                                                             | Low addr                                                            | High addr                                                           |          |       |                       |

| LDEAX         | rpa3                        | (EAL)                                                                                       | 0 1 0 0 1 0 0 0                                                     | 1 0 0 0 C <sub>3</sub> C <sub>2</sub> C <sub>1</sub> C <sub>0</sub> | 14/20(3) | ო     |                       |

|               |                             |                                                                                             | Data(4)                                                             |                                                                     | Ş        | ,     |                       |

| PUSH          | rp1                         | $((SP) - 1) \leftarrow (rp1_H) ((SP) - 2) \leftarrow (rp1_L)$<br>$(SP) \leftarrow (SP) - 2$ | $1 0 1 1 0 0_2 0_1 0_0$                                             |                                                                     | <u>5</u> | -     |                       |

| POP           | rp1                         |                                                                                             | 1 0 1 0 0 0 <sub>2</sub> 0 <sub>1</sub> 0 <sub>0</sub>              |                                                                     | 9        | -     | 1                     |

| LXI           | *rp2,worc                   | *rp2,word (rp2) $\leftarrow$ (word)<br>set ±0 if rp2 = H                                    | 0 P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> 0 1 0 0<br>High byte | Low byte                                                            | 10       | e     | L0 = 1 and<br>rp2 = H |

| TABLE         |                             | $(C) \leftarrow ((PC)+3+(A)), B \leftarrow ((PC)+3+(A)+1)$                                  | 0 1 0 0 1 0 0 0                                                     | 10101000                                                            | 17       | 2     |                       |

| 8-Bit Arithn  | 8-Bit Arithmetic [Register] | ]                                                                                           |                                                                     |                                                                     |          |       |                       |

| ADD           | A,r                         | $(A) \leftarrow (A) + (r)$                                                                  | 0 1 1 0 0 0 0 0                                                     |                                                                     | 8        | 2     |                       |

|               | L'A                         | $(r) \leftarrow (r) + (A)$                                                                  | 0 1 1 0 0 0 0 0                                                     | 0 0 R <sub>2</sub> R <sub>1</sub>                                   | 8        | 2     |                       |

| ADC           | A,r                         | $(A) \leftarrow (A) + (r) + (CY)$                                                           | 0 1 1 0 0 0 0 0                                                     | æ                                                                   | 8        | 5     |                       |

|               |                             |                                                                                             |                                                                     |                                                                     |          |       |                       |

| -        |

|----------|

|          |

| ~        |

|          |

|          |

| •        |

| •        |

|          |

|          |

|          |

| -        |

|          |

|          |

|          |

| -        |

| - 63     |

|          |

|          |

| -        |

|          |

|          |

|          |

| ~        |

| -        |

| -        |

| 0        |

| _        |

|          |

| 12       |

| -        |

| -        |

| 2        |

| ~        |

| -        |

| 3        |

|          |

| <u> </u> |

| _        |

| -        |

|          |

|          |

| •        |

| <b></b>  |

|          |

|          |

|          |

| -        |

|          |

|                                    |                  |                                       |   |   |   |        |            |   |   |   |   |   |          |                  |                                             | Ì              |           |       |                   |

|------------------------------------|------------------|---------------------------------------|---|---|---|--------|------------|---|---|---|---|---|----------|------------------|---------------------------------------------|----------------|-----------|-------|-------------------|

|                                    |                  |                                       |   |   |   | 8      |            |   |   |   |   |   | 8        |                  |                                             |                |           |       |                   |

| Mnemonic                           | Mnemonic Operand | Operation                             | 7 | ø | ß | 4<br>1 | יי<br>ה פי | - | • | 2 | ø | D |          | 3                | -                                           | •              | State[1]  | Bytes | Skip<br>Condition |

| 8-Bit Arithmetic [Register] (cont) | netic [Registe   | er] (cont)                            |   |   |   |        | ł          |   |   |   |   |   |          |                  |                                             |                |           |       |                   |

| ADDNC                              | A,r              | $(A) \leftarrow (A) + (r)$            | 0 | - |   | 6      | 0          | 0 | 0 | - | 6 | - |          | 0<br>R2          | 2 B1                                        | æ              | œ         | 2     | No carry          |

|                                    | r,A              | $(r) \leftarrow (r) + (A)$            | 0 | - | - | 0      | 0          | 0 | 0 | 0 | 0 | - | 0        | 0 R <sub>2</sub> | 2 R1                                        | &              | œ         | 2     | No carry          |

| SUB                                | A,r              | $(A) \leftarrow (A) - (r)$            | 0 | - | - | 0      | 0          | 0 | 0 | - | - | - | 0        | 0 R <sub>2</sub> | 2<br>13                                     | æ              | œ         | 2     |                   |

|                                    | Γ,Α              | $(r) \leftarrow (r) - (A)$            | 0 | - | - | 0      | 0          | 0 | 0 | 0 | - | - | 0        | 0<br>R2          | 2<br>12                                     | 2              | 8         | 2     |                   |

| SBB                                | A,r              | $(A) \leftarrow (A) - (r) - (CY)$     | 0 | - |   | 0      | 0          | 0 | 0 | - | - | - | -        | 0 R <sub>2</sub> | 2 R1                                        | æ              | æ         | 2     |                   |

|                                    | r,A              | $(r) \leftarrow (r) - (A) - (CY)$     | 0 | - |   | 6      | 0          | 0 | 0 | 0 |   | - |          | 0<br>R2          | 2<br>- B-                                   | æ              | 80        | 2     |                   |

| SUBNB                              | A,r              | $(A) \leftarrow (A) - (r)$            | 0 | - | - | 0      | 0 0        | 0 | 0 | - | 0 | - | -        | 0 R <sub>2</sub> | 2 B1                                        | в0             | 80        | 2     | No borrow         |

|                                    | r,A              | $(r) \leftarrow (r) - (A)$            | 0 | - | - | 0      | 0          | 0 | 0 | 0 | 0 | - | +        | 0 R <sub>2</sub> | 2 R1                                        | B <sub>0</sub> | 8         | 2     | No borrow         |

| ANA                                | A,r              | $(A) \leftarrow (A) \land (r)$        | 0 | - | - | 0      | 0          | 0 | 0 | - | 0 | 0 | 0        | R2               | 2<br>1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1- | e<br>6         | œ         | 2     |                   |

|                                    | r,A              | $(r) \leftarrow (r) \land (A)$        | 0 | - |   | 0      | 0          | 0 | 0 | 0 | 0 | 0 | 0        | -B2              | 2 B1                                        | æ              | œ         | 2     |                   |