# FAIRCHILD

SEMICONDUCTOR

October 1991 Revised November 1999 00310 Low Skew 2:8 Differential Clock Driver

# 100310 Low Skew 2:8 Differential Clock Driver

#### **General Description**

The 100310 is a low skew 8-bit differential clock driver which is designed to select between two separate differential clock inputs. The low output to output skew (< 50 ps) is maintained for either clock input. A LOW on the select pin (SEL) selects CLKINA, <u>CLKINA</u> and a HIGH on the SEL pin selects the CLKINB, <u>CLKINB</u> inputs.

The 100310 is ideal for those applications that need the ability to freely select between two clocks, or to maintain the ability to switch to an alternate or backup clock should a problem arise with the primary clock source.

A V<sub>BB</sub> output is provided for single-ended operation.

#### **Features**

- Low output to output skew

- Differential inputs and outputs

- Allows multiplexing between two clock inputs

- Voltage compensated operating range: -4.2V to -5.7V

- Available to industrial grade temperature range (PLCC package only)

### **Ordering Code:**

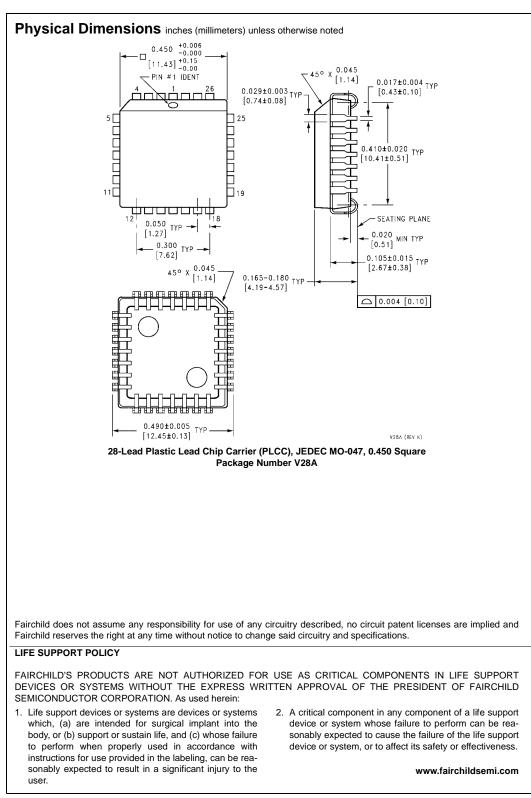

| Order Number           | Package Number | Package Description                                                                                                   |

|------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------|

| 100310QC               | V28A           | 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square                                                  |

| 1 <mark>00310QI</mark> |                | 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square<br>Industrial Temperature Range (–40°C to +85°C) |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

#### Logic Symbol CLK<sub>r</sub> CLK\_ CLK. CLK<sub>1</sub> CLK2 CLK<sub>2</sub> CLK3 CLKINA CLK<sub>3</sub> CLKINA CLK4 CLK4 CLKINB CLK5 CLK. SEL CLK<sub>6</sub> CLK<sub>6</sub> CLK7 CL K-

#### Connection Diagram 28-Pin PLCC UK & CK V VCA CKF, NC CKNRB 1 10 2 8 2 6 5 CK & 14 CK &

#### Pin Descriptions

| Pin Names                               | Description                          |

|-----------------------------------------|--------------------------------------|

| CLKIN <sub>n</sub> , CLKIN <sub>n</sub> | Differential Clock Inputs            |

| SEL                                     | Select                               |

| CLK0-7, CLK0-8                          | Differential Clock Outputs           |

| V <sub>BB</sub>                         | V <sub>BB</sub> Output               |

| NC                                      | V <sub>BB</sub> Output<br>No Connect |

| CLKINA | CLKINA | CLKINB | CLKINB | SEL | CLKn | CLK |

|--------|--------|--------|--------|-----|------|-----|

| Н      | L      | Х      | Х      | L   | Н    | L   |

| L      | н      | Х      | Х      | L   | L    | н   |

| Х      | Х      | н      | L      | Н   | н    | L   |

| Х      | Х      | L      | Н      | н   | L    | н   |

**Truth Table**

#### www.fairchildsemi.com

#### Absolute Maximum Ratings(Note 1)

Storage Temperature (T<sub>STG</sub>) -65°C to +150°C Maximum Junction Temperature (T<sub>J</sub>) Pin Potential to Ground Pin (V<sub>EE</sub>) -7.0V to +0.5V Input Voltage (DC) V<sub>EE</sub> to +0.5V Output Current (DC Output HIGH) ESD (Note 2)

#### **Recommended Operating** Conditions

| Case Temperature (T <sub>C</sub> )   |                |

|--------------------------------------|----------------|

| Commercial                           | 0°C to +85°C   |

| Industrial                           | -40°C to +85°C |

| Supply Voltage (V <sub>EE</sub> )    | -5.7V to -4.2V |

| Note 1: The "Absolute Maximum Rating |                |

the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 2: ESD testing conforms to MIL-STD-883, Method 3015.

#### **Commercial Version**

#### DC Electrical Characteristics (Note 3)

$V_{FF} = -4.2V$  to -5.7V,  $V_{CC} = V_{CCA} = GND$ ,  $T_C = 0^{\circ}C$  to  $+85^{\circ}C$

| Symbol            | Parameter                  | Min                   | Тур   | Max                   | Units | Con                                     | ditions              |  |

|-------------------|----------------------------|-----------------------|-------|-----------------------|-------|-----------------------------------------|----------------------|--|

| V <sub>OH</sub>   | Output HIGH Voltage        | -1025                 | -955  | -870                  | mV    | V <sub>IN</sub> = V <sub>IH</sub> (Max) | Loading with         |  |

| V <sub>OL</sub>   | Output LOW Voltage         | -1830                 | -1705 | -1620                 | mV    | or V <sub>IL</sub> (Min)                | 50 $\Omega$ to –2.0V |  |

| VOHC              | Output HIGH Voltage        | -1035                 |       |                       | mV    | $V_{IN} = V_{IH}$                       | Loading with         |  |

| V <sub>OLC</sub>  | Output LOW Voltage         |                       |       | -1610                 | mV    | or V <sub>IL</sub> (Max)                | 50 $\Omega$ to –2.0V |  |

| V <sub>BB</sub>   | Output Reference Voltage   | -1380                 | -1320 | -1260                 | mV    | $I_{VBB} = -250 \ \mu A$                | •                    |  |

| V <sub>DIFF</sub> | Input Voltage Differential | 150                   |       |                       | mV    | Required for Full Output Swing          |                      |  |

| V <sub>CM</sub>   | Common Mode Voltage        | V <sub>CC</sub> - 2.0 |       | V <sub>CC</sub> - 0.5 | V     |                                         |                      |  |

| V <sub>IH</sub>   | Input HIGH Voltage         | -1165                 |       | -870                  | mV    | Guaranteed HIGH S                       | ignal for All Inputs |  |

| V <sub>IL</sub>   | Input LOW Voltage          | -1830                 |       | -1475                 | mV    | Guaranteed LOW S                        | ignal for All Inputs |  |

| I <sub>IL</sub>   | Input LOW Current          | 0.50                  |       |                       | μΑ    | $V_{IN} = V_{IL}$ (Min)                 |                      |  |

| I <sub>IH</sub>   | Input HIGH Current         |                       |       | 240                   | μA    | $V_{IN} = V_{IH}$ (Max)                 |                      |  |

| I <sub>CBO</sub>  | Input Leakage Current      | -10                   |       |                       | μA    | $V_{IN} = V_{EE}$                       |                      |  |

| I <sub>EE</sub>   | Power Supply Current       | -100                  |       | -40                   | mA    | Inputs Open                             |                      |  |

+150°C

-50 mA

≥2000V

Note 3: The specified limits represent the "worst case" value for the parameter. Since these values normally occur at the temperature extremes, additional noise immunity and guardbanding can be achieved by decreasing the allowable system operating ranges. Conditions for testing shown in the tables are cho-sen to guarantee operation under "worst case" conditions.

www.fairchildsemi.com

#### Commercial Version (Continued) AC Electrical Characteristics

100310

| Symbol            | Parameter                              | $\mathbf{T_C} = 0^{\circ}\mathbf{C}$ |      |      | $T_C = +25^{\circ}C$ |      |      | $T_C = +85^{\circ}C$ |      |      | Units | Conditions       |

|-------------------|----------------------------------------|--------------------------------------|------|------|----------------------|------|------|----------------------|------|------|-------|------------------|

| Cymbol            | i arameter                             | Min                                  | Тур  | Max  | Min                  | Тур  | Max  | Min                  | Тур  | Max  | onits | Conditions       |

| f <sub>MAX</sub>  | Max Toggle Frequency                   |                                      |      |      |                      |      |      |                      |      |      |       |                  |

|                   | CLKIN A/B to Q <sub>n</sub>            | 750                                  |      |      | 750                  |      |      | 750                  |      |      | MHz   |                  |

|                   | SEL to Q <sub>n</sub>                  | 575                                  |      |      | 575                  |      |      | 575                  |      |      | MHz   |                  |

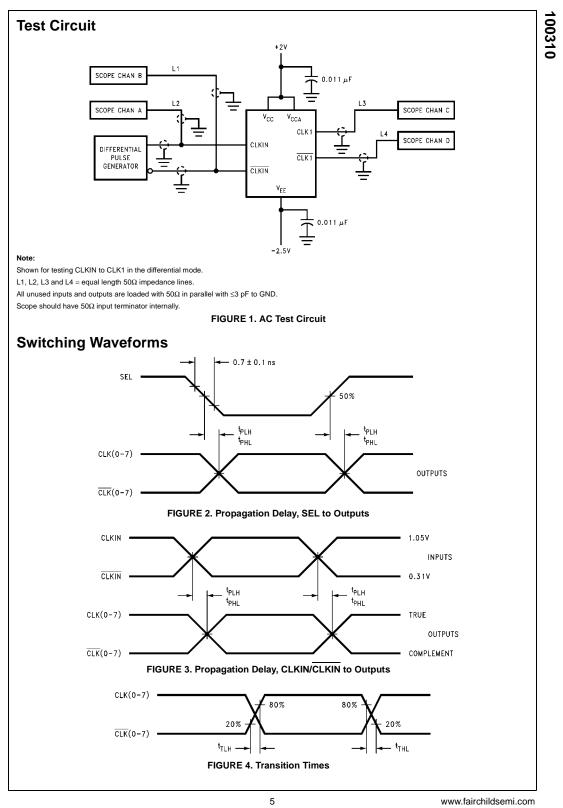

| t <sub>PLH</sub>  | Propagation Delay,                     |                                      |      |      |                      |      |      |                      |      |      |       |                  |

| t <sub>PHL</sub>  | CLKIN <sub>n</sub> to CLK <sub>n</sub> |                                      |      |      |                      |      |      |                      |      |      |       |                  |

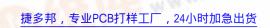

|                   | Differential                           | 0.80                                 | 0.90 | 1.00 | 0.82                 | 0.92 | 1.02 | 0.89                 | 1.01 | 1.09 | ns    | Figure 3         |

|                   | Single-Ended                           | 0.80                                 | 0.96 | 1.20 | 0.82                 | 0.98 | 1.22 | 0.89                 | 1.06 | 1.29 |       |                  |

| t <sub>PLH</sub>  | Propagation Delay,                     | 0.75                                 | 0.99 | 1.20 | 0.80                 | 1.02 | 1.25 | 0.85                 | 1.10 | 1.35 | ns    | Figure 2         |

| t <sub>PHL</sub>  | SEL to Output                          | 0.75                                 | 0.99 | 1.20 | 0.80                 | 1.02 | 1.25 | 0.05                 | 1.10 | 1.55 | 115   | i igule z        |

| t <sub>PS</sub>   | LH-HL Skew                             |                                      | 10   | 30   |                      | 10   | 30   |                      | 10   | 30   |       | (Note 4)(Note 7) |

| t <sub>OSLH</sub> | Gate-Gate Skew LH                      |                                      | 20   | 30   |                      | 20   | 50   |                      | 20   | 50   | ps    | (Note 5)(Note 7) |

| t <sub>OSHL</sub> | Gate-Gate Skew HL                      |                                      | 20   | 50   |                      | 20   | 50   |                      | 20   | 50   | μs    | (Note 5)(Note 7) |

| t <sub>OST</sub>  | Gate-Gate LH-HL Skew                   |                                      | 30   | 60   |                      | 30   | 60   |                      | 30   | 60   |       | (Note 6)(Note 7) |

| t <sub>S</sub>    | Setup Time                             | 300                                  |      |      | 300                  |      |      | 300                  |      |      | ps    |                  |

|                   | SEL to CLKINn                          | 500                                  |      |      | 500                  |      |      | 500                  |      |      | μs    |                  |

| t <sub>H</sub>    | Setup Time                             | 0                                    |      |      | 0                    |      |      | 0                    |      |      | ps    |                  |

|                   | SEL to CLKINn                          | 0                                    |      |      | 0                    |      |      | 0                    |      |      | hs    |                  |

| t <sub>TLH</sub>  | Transition Time                        | 275                                  | 510  | 750  | 275                  | 500  | 750  | 275                  | 480  | 750  |       | Figure 4         |

| t <sub>THL</sub>  | 20% to 80%, 80% to 20%                 | 275                                  | 510  | 730  | 215                  | 500  | 730  | 215                  | 400  | 130  | ps    | i igule 4        |

Note 4: tps describes opposite edge skews, i.e. the difference between the delay of a differential output signal pair's LOW-to-HIGH and HIGH-to-LOW propagation delays. With differential signal pairs, a LOW-to-HIGH or HIGH-to-LOW transition is defined as the transition of the true output or input pin.

Note 5: t<sub>OSLH</sub> describes in-phase gate-to-gate differential propagation skews with all differential outputs going LOW-to-HIGH; t<sub>OSHL</sub> describes the same conditions except with the outputs going HIGH-to-LOW.

Note 6:  $t_{OST}$  describes the maximum worst case difference in any of the  $t_{PS}$ ,  $t_{OSLH}$  or  $t_{OST}$  delay paths combined.

Note 7: The skew specifications pertain to differential I/O paths.

## Industrial Version

100310

## DC Electrical Characteristics (Note 8)

$V_{EE} = -4.2 V$  to  $-5.7 V, V_{CC} = V_{CCA} = GND$

| Symbol            | Parameter                  | T <sub>C</sub> = -    | –40°C          | $T_{C} = 0^{\circ}C$ | to +85°C       | Units | Conditions               |                       |  |  |

|-------------------|----------------------------|-----------------------|----------------|----------------------|----------------|-------|--------------------------|-----------------------|--|--|

| Cymbol            | i urumeter                 | Min                   | Max            | Min                  | Max            | onito | Conditions               |                       |  |  |

| V <sub>OH</sub>   | Output HIGH Voltage        | -1085                 | -870           | -1025                | -870           | mV    | $V_{IN} = V_{IH}$ (Max)  | Loading with          |  |  |

| V <sub>OL</sub>   | Output LOW Voltage         | -1830                 | -1575          | -1830                | -1620          | mV    | or V <sub>IL</sub> (Min) | 50 $\Omega$ to –2.0V  |  |  |

| V <sub>OHC</sub>  | Output HIGH Voltage        | -1095                 |                | -1035                |                | mV    | $V_{IN} = V_{IH}$        | Loading with          |  |  |

| V <sub>OLC</sub>  | Output LOW Voltage         |                       | -1565          |                      | -1610          | mV    | or V <sub>IL</sub> (Min) | $50\Omega$ to $-2.0V$ |  |  |

| V <sub>BB</sub>   | Output Reference Voltage   | -1395                 | -1255          | -1380                | -1260          | mV    | $I_{VBB} = -250 \ \mu A$ | •                     |  |  |

| V <sub>DIFF</sub> | Input Voltage Differential | 150                   |                | 150                  |                | mV    | Required for Full        | Output Swing          |  |  |

| V <sub>CM</sub>   | Common Mode Voltage        | V <sub>CC</sub> - 2.0 | $V_{CC} - 0.5$ | $V_{CC} - 2.0$       | $V_{CC} - 0.5$ | V     |                          |                       |  |  |

| VIH               | Input HIGH Voltage         | -1170                 | -870           | -1165                | -870           | mV    | Guaranteed HIGH          | I Signal for          |  |  |

|                   |                            |                       |                |                      |                |       | All Inputs               |                       |  |  |

| VIL               | Input LOW Voltage          | -1830                 | -1480          | -1830                | -1475          | mV    | Guaranteed LOW           | Signal for            |  |  |

|                   |                            |                       |                |                      |                |       | All Inputs               |                       |  |  |

| I <sub>IL</sub>   | Input LOW Current          | 0.50                  |                | 0.50                 |                | μA    | $V_{IN} = V_{IL}$ (Min)  |                       |  |  |

| IIH               | Input HIGH Current         |                       | 240            |                      | 240            | μA    | $V_{IN} = V_{IH}$ (Max)  |                       |  |  |

| I <sub>CBO</sub>  | Input Leakage Current      | -10                   |                | -10                  |                | μA    | $V_{IN} = V_{EE}$        |                       |  |  |

| I <sub>EE</sub>   | Power Supply Current       | -100                  | -40            | -100                 | -40            | mA    | Inputs Open              |                       |  |  |

Note 8: The specified limits represent the "worst case" value for the parameter. Since these values normally occur at the temperature extremes, additional noise immunity and guardbanding can be achieved by decreasing the allowable system operating ranges. Conditions for testing shown in the tables are chosen to guarantee operation under "worst case" conditions.

#### **AC Electrical Characteristics**

$V_{EE} = -4.2V$  to -5.7V,  $V_{CC} = V_{CCA} = GND$

| Symbol            | Parameter                                | Т    | c = −40° | C    | т    | c = +25° | С    | $T_C = +85^{\circ}C$ |      |      | Units | Conditions         |

|-------------------|------------------------------------------|------|----------|------|------|----------|------|----------------------|------|------|-------|--------------------|

| Symbol            | Falaneter                                | Min  | Тур      | Max  | Min  | Тур      | Max  | Min                  | Тур  | Max  | Units | Conditions         |

| f <sub>MAX</sub>  | Max Toggle Frequency                     |      |          |      |      |          |      |                      |      |      |       |                    |

|                   | CLKIN A/B to Q <sub>n</sub>              | 750  |          |      | 750  |          |      | 750                  |      |      | MHz   |                    |

|                   | SEL to Q <sub>n</sub>                    | 575  |          |      | 575  |          |      | 575                  |      |      | MHz   |                    |

| t <sub>PLH</sub>  | Propagation Delay,                       |      |          |      |      |          |      |                      |      |      |       |                    |

| t <sub>PHL</sub>  | CLKIN <sub>n</sub> , to CLK <sub>n</sub> |      |          |      |      |          |      |                      |      |      |       |                    |

|                   | Differential                             | 0.78 | 0.88     | 0.98 | 0.82 | 0.92     | 1.02 | 0.89                 | 1.01 | 1.09 | ns    | Figure 3           |

|                   | Single-Ended                             | 0.78 | 0.95     | 1.18 | 0.82 | 0.98     | 1.22 | 0.89                 | 1.06 | 1.29 |       |                    |

| t <sub>PLH</sub>  | Propagation Delay                        | 0.70 | 0.99     | 1.20 | 0.80 | 1.02     | 1.25 | 0.85                 | 1.10 | 1.35 | ns    | Figure 2           |

| t <sub>PHL</sub>  | SEL to Output                            | 0.70 | 0.99     | 1.20 | 0.80 | 1.02     | 1.20 | 0.05                 | 1.10 | 1.55 | 115   | i igule z          |

| t <sub>PS</sub>   | LH-HL Skew                               |      | 10       | 30   |      | 10       | 30   |                      | 10   | 30   |       | (Note 9)(Note 12)  |

| t <sub>OSLH</sub> | Gate-Gate Skew LH                        |      | 20       | 50   |      | 20       | 50   |                      | 20   | 50   | ps    | (Note 10)(Note 12) |

| t <sub>OSHL</sub> | Gate-Gate Skew HL                        |      | 20       | 50   |      | 20       | 50   |                      | 20   | 50   |       | (Note 10)(Note 12) |

| t <sub>OST</sub>  | Gate-Gate LH-HL Skew                     |      | 30       | 60   |      | 30       | 60   |                      | 30   | 60   |       | (Note 11)(Note 12) |

| t <sub>S</sub>    | Setup Time                               | 300  |          |      | 300  |          |      | 300                  |      |      | ne    |                    |

|                   | SEL to CLKIN <sub>n</sub>                | 300  |          |      | 300  |          |      | 300                  |      |      | ps    |                    |

| t <sub>H</sub>    | Setup Time                               | 0    |          |      | 0    |          |      | 0                    |      |      | ps    |                    |

|                   | SEL to CLKIN <sub>n</sub>                | 0    |          |      | 0    |          |      | 0                    |      |      | he    |                    |

| t <sub>TLH</sub>  | Transition Time                          | 275  | 510      | 750  | 275  | 500      | 750  | 275                  | 480  | 750  | -     | Figure 4           |

| t <sub>THL</sub>  | 20% to 80%, 80% to 20%                   | 2/5  | 510      | 100  | 215  | 500      | 100  | 215                  | 400  | 100  | ps    | Figure 4           |

Note 9: t<sub>PS</sub> describes opposite edge skews, i.e. the difference between the delay of a differential output signal pair's LOW-to-HIGH and HIGH-to-LOW propagation delays. With differential signal pairs, a LOW-to-HIGH or HIGH-to-LOW transition is defined as the transition of the true output or input pin. Note 10: t<sub>OSLH</sub> describes in-phase gate-to-gate differential propagation skews with all differential outputs going LOW-to-HIGH; t<sub>OSHL</sub> describes the same

Note 10: t<sub>OSLH</sub> describes in-phase gate-to-gate dimerential propagation skews with all dimerential outputs going LOW-to-HIGH; t<sub>OSHL</sub> describes the same conditions except with the outputs going HIGH-to-LOW.

Note 11:  $t_{OST}$  describes the maximum worst case difference in any of the  $t_{PS}$ ,  $t_{OSLH}$  or  $t_{OST}$  delay paths combined.

Note 12: The skew specifications pertain to differential I/O paths.

www.fairchildsemi.com