# =AIRCHIL

SEMICONDUCTOR

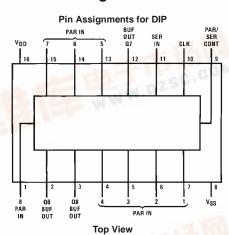

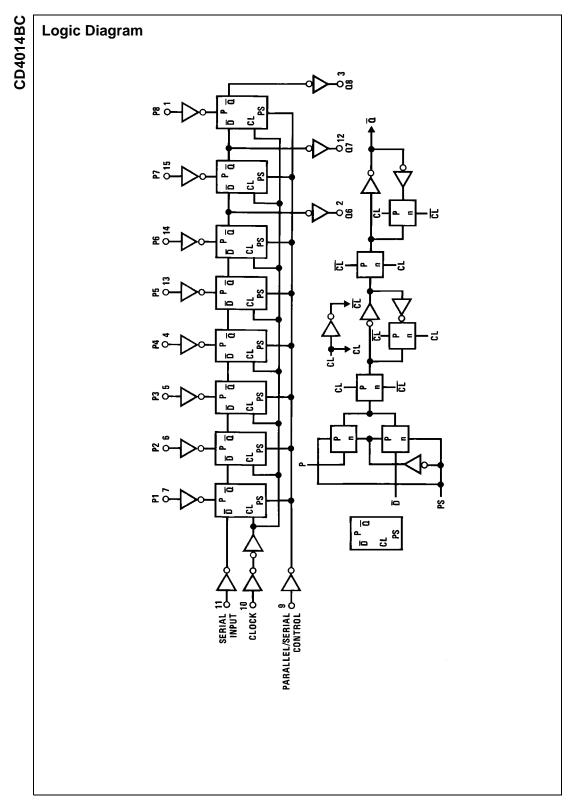

## **CD4014BC** 8-Stage Static Shift Register

#### **General Description**

The CD4014BC is an 8-stage parallel input/serial output shift register. A parallel/serial control input enables individual JAM inputs to each of 8 stages. Q outputs are available from the sixth, seventh and eighth stages. All outputs have equal source and sink current capabilities and conform to standard "B" series output drive.

When the parallel/serial control input is in the logical "0" state, data is serially shifted into the register synchronously with the positive transition of the clock. When the parallel/ serial control input is in the logical "1" state, data is jammed into each stage of the register synchronously with the positive transition of the clock.

October 1987 Revised January 1999

All inputs are protected against static discharge with diodes to V<sub>DD</sub> and V<sub>SS</sub>.

#### **Features**

- Wide supply voltage range: 3.0V to 15V

- High noise immunity: 0.45 V<sub>DD</sub> (typ.)

- Low power TTL compatibility: Fan out of 2 driving 74L or 1 driving 74LS

- 5V–10V–15V parametric ratings

- Symmetrical output characteristics

- Maximum input leakage:

- 1 μA at 15V over full temperature range

## **Ordering Code:**

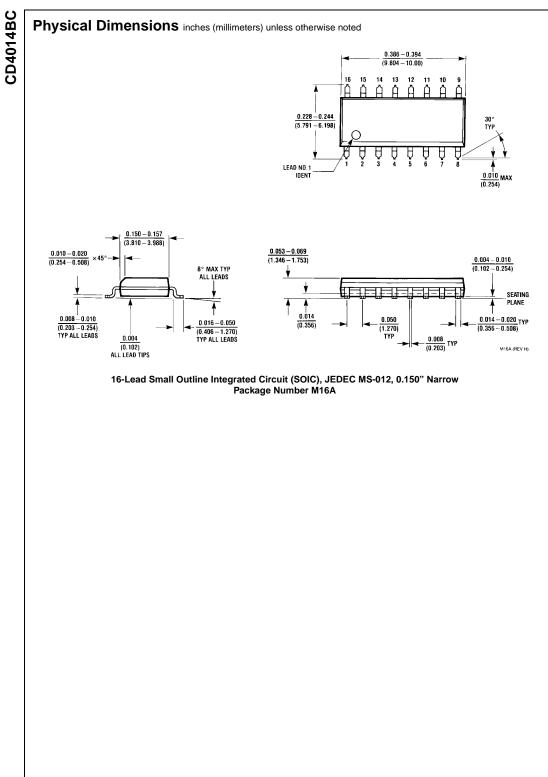

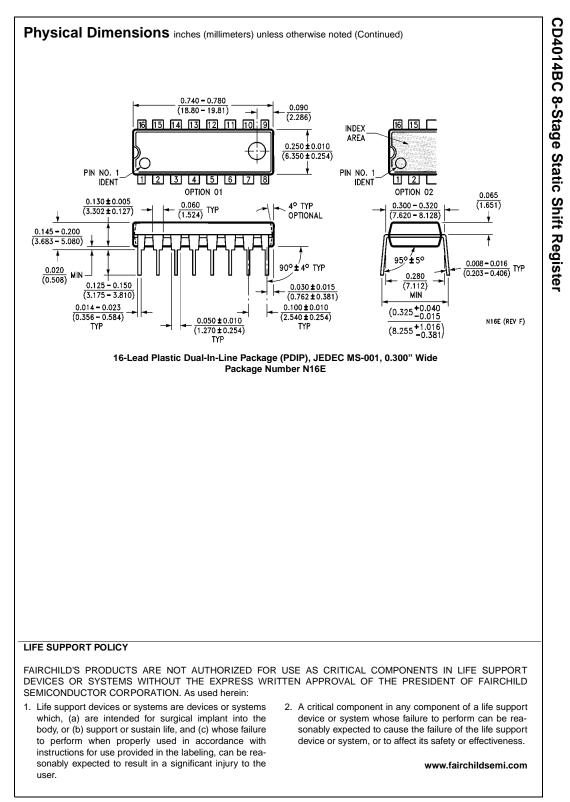

| Order Number              | Package Number            | age Number Package Description                                               |  |  |  |  |  |

|---------------------------|---------------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| CD4014BCM                 | M16A                      | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |  |  |  |  |  |

| CD4014BCN                 | N16E                      | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300" Wide       |  |  |  |  |  |

| Devices also available in | Tape and Reel. Specify by | / appending the suffix letter "x" to the ordering code.                      |  |  |  |  |  |

## **Connection Diagram**

## **Truth Table**

| Serial<br>Input | Parallel/<br>Serial<br>Control  | PI 1                                                                                                                                                                               | Pl n                                                                                                                                                                                           | Q1<br>(Internal)                                                                         | Qn                                                                                                                  |

|-----------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Х               | 1                               | 0                                                                                                                                                                                  | 0                                                                                                                                                                                              | 0                                                                                        | 0                                                                                                                   |

| Х               | 1                               | 1                                                                                                                                                                                  | 0                                                                                                                                                                                              | 1                                                                                        | 0                                                                                                                   |

| Х               | 1                               | 0                                                                                                                                                                                  | 1                                                                                                                                                                                              | 0                                                                                        | 1                                                                                                                   |

| Х               | 1                               | 1                                                                                                                                                                                  | 1                                                                                                                                                                                              | 1                                                                                        | 1                                                                                                                   |

| 0               | 0                               | Х                                                                                                                                                                                  | Х                                                                                                                                                                                              | 0                                                                                        | $Q_{n-1}$                                                                                                           |

| 1               | 0                               | Х                                                                                                                                                                                  | Х                                                                                                                                                                                              | 1                                                                                        | Q <sub>n-1</sub>                                                                                                    |

| Х               | Х                               | Х                                                                                                                                                                                  | Х                                                                                                                                                                                              | Q1                                                                                       | Q <sub>n</sub>                                                                                                      |

| case            | ^                               | ~                                                                                                                                                                                  | ^                                                                                                                                                                                              |                                                                                          | Qn                                                                                                                  |

|                 | X<br>X<br>X<br>X<br>0<br>1<br>X | X     1       X     1       X     1       X     1       X     1       X     1       X     1       X     1       X     1       X     X       X     X       X     X       Case     X | X     1     0       X     1     1       X     1     0       X     1     1       X     1     0       X     1     1       0     0     X       1     0     X       X     X     X       Case     X | X 1 0 0   X 1 1 0   X 1 0 1   X 1 1 1   0 0 X X   1 0 X X   1 0 X X   X X X X   case X X | Control Control   X 1 0 0   X 1 1 0   X 1 0 1   X 1 1 1   X 1 1 1   X 1 1 1   X 1 X X   1 0 X X   1 0 X X   X X X X |

Note 1: Level change

dzsc.com

## Absolute Maximum Ratings(Note 2)

| (N | ote | 3) |

|----|-----|----|

|    |     |    |

| (                                           |                                                               |

|---------------------------------------------|---------------------------------------------------------------|

| Supply Voltage (V <sub>DD</sub> )           | -0.5V to +18V                                                 |

| Input Voltage (V <sub>IN</sub> )            | $-0.5$ to $V_{\mbox{\scriptsize DD}}+0.5\mbox{\scriptsize V}$ |

| Storage Temperature Range (T <sub>S</sub> ) | $-65^{\circ}C$ to $+150^{\circ}C$                             |

| Power Dissipation (P <sub>D</sub> )         |                                                               |

| Dual-In-Line                                | 700 mW                                                        |

| Small Outline                               | 500 mW                                                        |

| Lead Temperature (T <sub>L</sub> )          |                                                               |

| (Soldering, 10 seconds)                     | 260°C                                                         |

|                                             |                                                               |

### **Recommended Operating** Conditions (Note 3)

Supply Voltage (V<sub>DD</sub>) Input Voltage (V<sub>IN</sub>) Operating Temperature Range (T<sub>A</sub>) 3.0V to 15V 0 to  $\mathrm{V}_{\mathrm{DD}}$

-40°C to +85°C

CD4014BC

Note 2: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Tempera-ture Range" they are not meant to imply that the devices should be oper-ated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 3:  $V_{SS} = 0V$  unless otherwise specified.

| Symbol          | Parameter         | Conditions                                    |                                      | <b>−40°C</b> |      | +25°C |                   |      | +85°C |      | Units |

|-----------------|-------------------|-----------------------------------------------|--------------------------------------|--------------|------|-------|-------------------|------|-------|------|-------|

| Symbol          | Farameter         |                                               | nutions                              | Min          | Max  | Min   | Тур               | Max  | Min   | Max  | Units |

| I <sub>DD</sub> | Quiescent Device  | $V_{DD} = 5V, V_{IN} =$                       | V <sub>DD</sub> or V <sub>SS</sub>   |              | 20   |       | 0.1               | 20   |       | 150  | μΑ    |

|                 | Current           | $V_{DD} = 10V, V_{IN}$                        | = V <sub>DD</sub> or V <sub>SS</sub> |              | 40   |       | 0.2               | 40   |       | 300  | μΑ    |

|                 |                   | $V_{DD} = 15V, V_{IN}$                        | = V <sub>DD</sub> or V <sub>SS</sub> |              | 80   |       | 0.3               | 80   |       | 600  | μΑ    |

| V <sub>OL</sub> | LOW Level         | $V_{DD} = 5V$                                 |                                      |              | 0.05 |       | 0                 | 0.05 |       | 0.05 | V     |

|                 | Output Voltage    | $V_{DD} = 10V$                                | I <sub>O</sub>   < 1 μA              |              | 0.05 |       | 0                 | 0.05 |       | 0.05 | V     |

|                 |                   | $V_{DD} = 15V$                                |                                      |              | 0.05 |       | 0                 | 0.05 |       | 0.05 | V     |

| V <sub>OH</sub> | HIGH Level        | $V_{DD} = 5V$                                 |                                      | 4.95         |      | 4.95  | 5                 |      | 4.95  |      | V     |

|                 | Output Voltage    | $V_{DD} = 10V$                                | I <sub>O</sub>   < 1 μA              | 9.95         |      | 9.95  | 10                |      | 9.95  |      | V     |

|                 |                   | $V_{DD} = 15V$                                |                                      | 14.95        |      | 14.95 | 15                |      | 14.95 |      | V     |

| V <sub>IL</sub> | LOW Level         | $V_{DD} = 5V, V_{O} =$                        | 0.5V or 4.5V                         |              | 1.5  |       | 2                 | 1.5  |       | 1.5  | V     |

|                 | Input Voltage     | $V_{DD} = 10V, V_{O} = 1.0V \text{ or } 9.0V$ |                                      |              | 3.0  |       | 4                 | 3.0  |       | 3.0  | V     |

|                 |                   | $V_{DD} = 15V, V_O =$                         | = 1.5V or 13.5V                      |              | 4.0  |       | 6                 | 4.0  |       | 4.0  | V     |

| VIH             | HIGH Level        | $V_{DD} = 5V, V_{O} =$                        | 0.5V or 4.5V                         | 3.5          |      | 3.5   | 3                 |      | 3.5   |      | V     |

|                 | Input Voltage     | $V_{DD} = 10V, V_O =$                         | = 1.0V or 9.0V                       | 7.0          |      | 7.0   | 6                 |      | 7.0   |      | V     |

|                 |                   | $V_{DD} = 15V, V_O$                           | = 1.5V or 13.5V                      | 11.0         |      | 11.0  | 9                 |      | 11.0  |      | V     |

| I <sub>OL</sub> | LOW Level Output  | $V_{DD} = 5V, V_{O} =$                        | 0.4V                                 | 0.52         |      | 0.44  | 0.88              |      | 0.36  |      | mA    |

|                 | Current (Note 4)  | $V_{DD} = 10V, V_{O} = 0.5V$                  |                                      | 1.3          |      | 1.1   | 2.2               |      | 0.9   |      | mA    |

|                 |                   | $V_{DD} = 15V, V_{O} = 1.5V$                  |                                      | 3.6          |      | 3.0   | 8                 |      | 2.4   |      | mA    |

| I <sub>OH</sub> | HIGH Level Output | $V_{DD} = 5V, V_{O} = 4.6V$                   |                                      | -0.52        |      | -0.44 | -0.88             |      | -0.36 |      | mA    |

|                 | Current (Note 4)  | $V_{DD} = 10V, V_{O} = 9.5V$                  |                                      | -1.3         |      | -1.1  | -2.2              |      | -0.90 |      | mA    |

|                 |                   | $V_{DD} = 15V, V_O$                           | = 13.5V                              | -3.6         |      | -3.0  | -8                |      | -2.4  |      | mA    |

| I <sub>IN</sub> | Input Current     | $V_{DD} = 15V, V_{IN}$                        | = 0V                                 |              | -0.3 |       | -10 <sup>-5</sup> | -0.3 |       | -1.0 | μΑ    |

|                 |                   | $V_{DD} = 15V, V_{IN}$                        | = 15V                                |              | 0.3  |       | 10 <sup>-5</sup>  | 0.3  |       | 1.0  | μΑ    |

#### DC Electrical Characteristics (Note 3)

Note 4:  $I_{OL}$  and  $I_{OH}$  are tested one output at a time.

# CD4014BC

| Symbol                              | Parameter                                | Conditions     | Min | Тур | Max | Units |

|-------------------------------------|------------------------------------------|----------------|-----|-----|-----|-------|

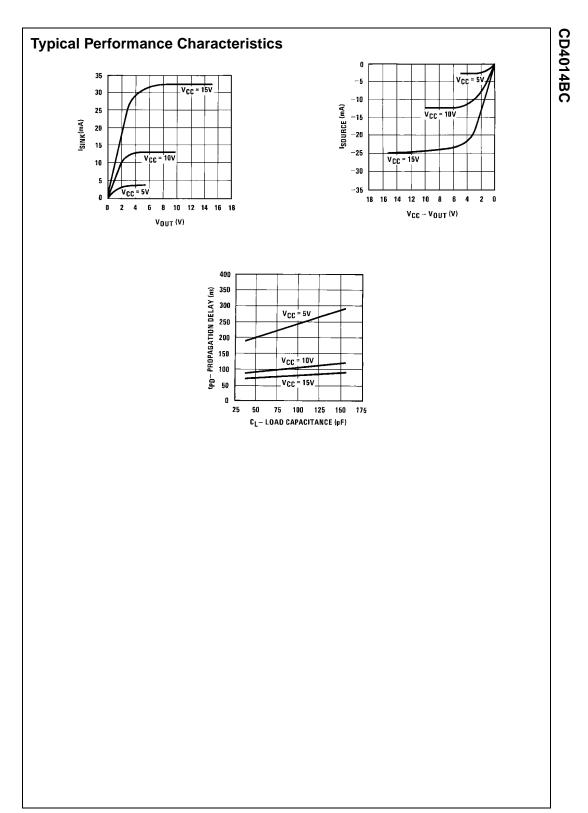

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Time                   | $V_{DD} = 5V$  |     | 200 | 320 | ns    |

|                                     |                                          | $V_{DD} = 10V$ |     | 80  | 160 | ns    |

|                                     |                                          | $V_{DD} = 15V$ |     | 60  | 120 | ns    |

| THL, <sup>t</sup> TLH               | Transition Time                          | $V_{DD} = 5V$  |     | 100 | 200 | ns    |

|                                     |                                          | $V_{DD} = 10V$ |     | 50  | 100 | ns    |

|                                     |                                          | $V_{DD} = 15V$ |     | 40  | 80  | ns    |

| CL                                  | Maximum Clock                            | $V_{DD} = 5V$  | 2.8 | 4   |     | MHz   |

|                                     | Input Frequency                          | $V_{DD} = 10V$ | 6   | 12  |     | MHz   |

|                                     |                                          | $V_{DD} = 15V$ | 8   | 16  |     | MHz   |

| W                                   | Minimum Clock                            | $V_{DD} = 5V$  |     | 90  | 180 | ns    |

|                                     | Pulse Width                              | $V_{DD} = 10V$ |     | 40  | 80  | ns    |

|                                     |                                          | $V_{DD} = 15V$ |     | 25  | 50  | ns    |

| rCL <sup>, t</sup> fCL              | Clock Rise and                           | $V_{DD} = 5V$  |     |     | 15  | μs    |

|                                     | Fall Time (Note 6)                       | $V_{DD} = 10V$ |     |     | 15  | μs    |

|                                     |                                          | $V_{DD} = 15V$ |     |     | 15  | μs    |

| S                                   | Minimum Set-Up Time                      | $V_{DD} = 5V$  |     | 60  | 120 | ns    |

|                                     | (Note 7) Serial Input                    | $V_{DD} = 10V$ |     | 40  | 80  | ns    |

|                                     | t <sub>H</sub> ≥ 200 ns                  | $V_{DD} = 15V$ |     | 30  | 60  | ns    |

|                                     | Parallel Inputs                          | $V_{DD} = 5V$  |     | 80  | 160 | ns    |

|                                     | t <sub>H</sub> ≥ 200 ns                  | $V_{DD} = 10V$ |     | 40  | 80  | ns    |

|                                     |                                          | $V_{DD} = 15V$ |     | 30  | 60  | ns    |

|                                     | Parallel/Serial Control                  | $V_{DD} = 5V$  |     | 100 | 200 | ns    |

|                                     | t <sub>H</sub> ≥ 200 ns                  | $V_{DD} = 10V$ |     | 50  | 100 | ns    |

|                                     |                                          | $V_{DD} = 15V$ |     | 40  | 80  | ns    |

| н                                   | Minimum Hold Time                        | $V_{DD} = 5V$  |     |     | 0   | ns    |

|                                     | Serial In, Parallel In, $t_S \ge 400$ ns | $V_{DD} = 10V$ |     |     | 10  | ns    |

|                                     | Parallel/Serial Control                  | $V_{DD} = 15V$ |     |     | 15  | ns    |

| 2                                   | Average Input Capacitance                | Any Input      |     | 5   | 7.5 | pF    |

|                                     | (Note 8)                                 |                |     |     |     |       |

| CPD                                 | Power Dissipation Capacitance            |                |     | 110 |     | pF    |

|                                     | (Note 8)                                 |                |     |     |     |       |

Note 5: AC Parameters are guaranteed by DC correlated testing.

Note 6: If more than one unit is cascaded t<sub>rCL</sub> should be made less than or equal to the fixed propagation delay of the output of the driving stage for the estimated capacitive load.

Note 7: Setup times are measured with reference to clock and a fixed hold time  $(\mathrm{t}_{\mathrm{H}})$  as specified.

Note 8: C<sub>PD</sub> determines the no load AC power consumption of any CMOS device. For complete explanation, see 74C family characteristics application note AN-90.

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.