### MB86961A

# **FUJITSU**

#### UNIVERSAL INTERFACE FOR 10BASE -T

DECEMBER 1999

#### DATASHEET

#### **FEATURES**

- Full-duplex capability

- Combines Manchester encoder/decoder and twisted pair transceiver functions

- Direct interface to all popular Ethernet controllers

- Direct interface to AUI and 10BASE-T outputs

- Manual or automatic AUI /10BASE-T selection

- Integrated pulse shaper and Tx/Rx filters

- Selectable  $100 \Omega/150 \Omega$  termination permits operation with shielded or unshielded twisted pair cable

- Reverse-polarity detection for receiver with automatic correction

- On-chip jabber logic, SQE test and link test with enable/disable option

- Remote signaling of link down and jabber conditions

- Programmable receive threshold for extended range

- Output drivers for receive, transmit, collision and link test pass LED indicators

- TP loopback enable/disable for external loopback testing

- Power down mode for minimum power dissipation

- Automatic shut-down of unused port to reduce power consumption

- Low power CMOS technology, single 5 volt power supply

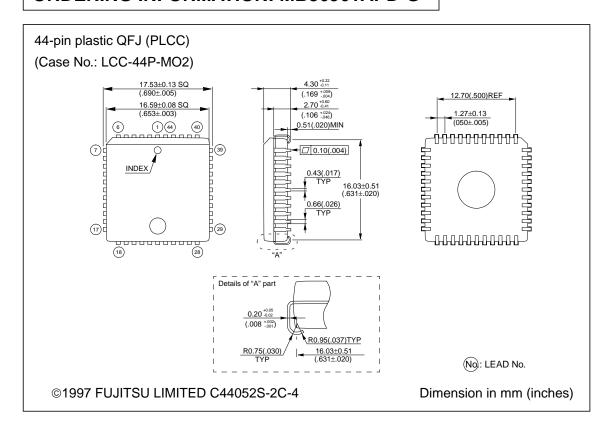

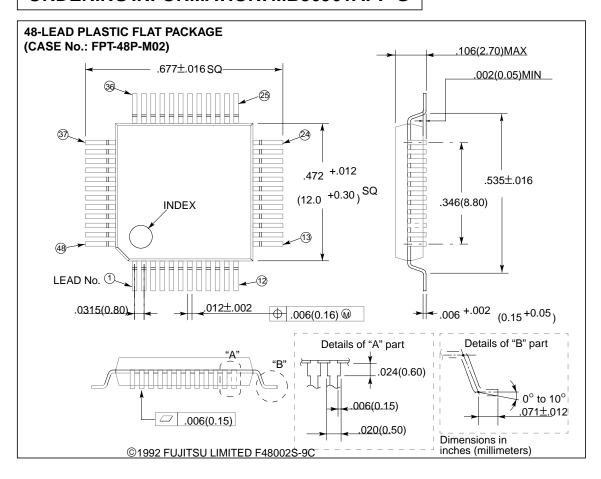

- 44-pin PLCC and 48-pin PQFP packages

#### **GENERAL DESCRIPTION**

The MB86961A Universal Interface for 10BASE-T (Twisted-Pair) Ethernet is fully compliant with the IEEE 802.3 specifications for AUI (Attachment Unit Interface) and 10BASE-T (Twisted-Pair) interfaces and provides the electrical interface between an Ethernet controller and the DB15 (AUI) and RJ45 (10BASE-T) connections to an Ethernet local area network. Functions provided by the MB86961A include Manchester encoding and decoding of the serial data stream, level conversion, collision detection, signal quality error (SQE) and link integrity testing, jabber control, loopback, and automatic correction of

polarity reversal on the twisted-pair input.

Pulse shaping and filtering functions are performed by the MB86961A to eliminate the need for external filtering components and thus reduce overall system cost. The device also provides outputs for receive, transmit, collision and link test LEDs and provides compatibility with both shielded and unshielded twisted pair cables. The receive threshold can be reduced to allow an extended range between nodes in low noise environments. Its wide range of features and its ability to interface to virtually all popular controllers make the MB86961A the ideal device for twisted pair Ethernet applications.

The MB86961A is part of a complete family of Ethernet devices available from Fujitsu. It is fabricated in a low-power CMOS technology and is supplied in a 44-pin PLCC and 48-pin PQFP packages.

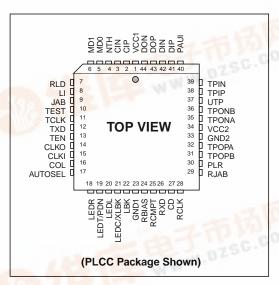

#### **PIN CONFIGURATION**

#### PIN ASSIGNMENT - 44-PIN PLCC

| PIN |      |   | PIN |           |     | PIN |       |   | PIN |       |   |

|-----|------|---|-----|-----------|-----|-----|-------|---|-----|-------|---|

| 1   | VCC1 |   | 12  | TXD       | 1   | 22  | GND1  |   | 24  | VCC2  |   |

| 1   | CIP  | _ | 13  | TEN       | :   |     | RBIAS | _ | 35  | TPONA | 0 |

| 1   |      | ı |     |           | ı   |     | _     | I |     |       |   |

| 3   | CIN  | ı | 14  | CLKO      | 0   | 25  | RCMPT | 0 | 36  | TPONB | 0 |

| 4   | NTH  | I | 15  | CLKI      | 1   | 26  | RXD   | 0 | 37  | UTP   | I |

| 5   | MD0  | I | 16  | COL       | 0   | 27  | CD    | 0 | 38  | TPIP  | 1 |

| 6   | MD1  | I | 17  | AUTOSEL   | 1   | 28  | RCLK  | 0 | 39  | TPIN  | 1 |

| 7   | RLD  | 0 | 18  | LEDR      | 0   | 29  | RJAB  | 0 | 40  | PAUI  | 1 |

| 8   | LI   | I | 19  | LEDT/PDN  | O/I | 30  | PLR   | 0 | 41  | DIP   | 1 |

| 9   | JAB  | 0 | 20  | LEDL      | O/I | 31  | TPOPB | 0 | 42  | DIN   | 1 |

| 10  | TEST | 1 | 21  | LEDC/XLBK | O/I | 32  | TPOPA | 0 | 43  | DOP   | 0 |

| 11  | TCLK | 0 | 22  | LBK       | I   | 33  | GND2  | _ | 44  | DON   | 0 |

| ı   |      |   |     |           |     | I   |       |   |     |       |   |

#### PIN ASSIGNMENT - 48-PIN PQFP

| PIN |      |   | PIN |         |   | PIN |           |     | PIN |       |   |

|-----|------|---|-----|---------|---|-----|-----------|-----|-----|-------|---|

|     |      |   |     |         |   |     |           |     |     |       |   |

| 1   | PAUI | I | 13  | RLD     | 0 | 25  | LEDR      | 0   | 37  | RJAB  | 0 |

| 2   | DIP  | I | 14  | LI      | I | 26  | LEDT/PDN  | O/I | 38  | PLR   | 0 |

| 3   | DIN  | I | 15  | JAB     | 0 | 27  | LEDL      | O/I | 39  | TPOPB | 0 |

| 4   | DOP  | 0 | 16  | TEST    | I | 28  | LEDC/XLBK | O/I | 40  | TPOPA | 0 |

| 5   | DON  | 0 | 17  | TCLK    | 0 | 29  | LBK       | I   | 41  | GND   | _ |

| 6   | NC   | _ | 18  | TXD     | I | 30  | GND       | _   | 42  | VCC   | _ |

| 7   | VCC  | _ | 19  | VCC     | _ | 31  | NC        | _   | 43  | VCC   | _ |

| 8   | CIP  | I | 20  | TEN     | I | 32  | RBIAS     | I   | 44  | TPONA | 0 |

| 9   | CIN  | 1 | 21  | CLKO    | 0 | 33  | RCMPT     | 0   | 45  | TPONB | 0 |

| 10  | NTH  | I | 22  | CLKI    | 1 | 34  | RXD       | 0   | 46  | UTP   | I |

| 11  | MD0  | 1 | 23  | COL     | 0 | 35  | CD        | 0   | 47  | TPIP  | I |

| 12  | MD1  | I | 24  | AUTOSEL | I | 36  | RCLK      | 0   | 48  | TPIN  | I |

#### ORDERING CODE

| PACKAGE STYLE                      | PACKAGE CODE | $V_{CC}$ = +V $\pm$ 5% |

|------------------------------------|--------------|------------------------|

| 44-Pin Plastic Leaded Chip Carrier | LCC-44P-M02  | MB86961APD-G           |

| 48-Pin Plastic Quad Flat Package   | FPT-48P-M02  | MB86961APF-G           |

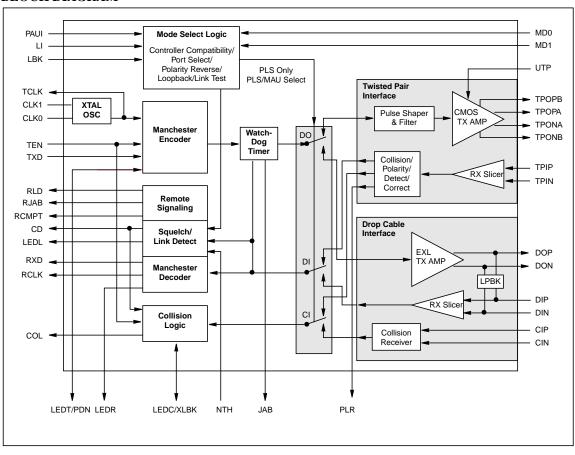

#### **BLOCK DIAGRAM**

# MB86961A

#### SIGNAL DESCRIPTIONS

| Symbol       | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUTOSEL      | I      | AUTOMATIC PORT SELECT: When AUTOSEL=1, automatic port selection is enabled (The MB86981A defaults to the AUI port only if TP link integrity=Fail). When AUTOSEL=0, manual port selection is enabled (the PAUI pin determines the active port).                                                                                                                                                                     |

| CD           | 0      | CARRIER DETECT: An output to notify the controller of activity on the network.                                                                                                                                                                                                                                                                                                                                     |

| CIP<br>CIN   | l<br>I | <b>AUI COLLISION PAIR:</b> Differential input pair connected to the AUI transceiver CI circuit. The input is collision signaling or SQE.                                                                                                                                                                                                                                                                           |

| CLKO<br>CLKI | 0      | CRYSTAL OSCILLATOR: A 20MHz crystal must be connected across these pins, or a 20 MHz clock applied at CLKI.                                                                                                                                                                                                                                                                                                        |

| COL          | 0      | COLLISION DETECT: Output which drives the collision detect input of the controller.                                                                                                                                                                                                                                                                                                                                |

| DIP<br>DIN   | I      | AUI RECEIVE PAIR: Differential input pair from the AUI transceiver DI circuit. The input is Manchester encoded.                                                                                                                                                                                                                                                                                                    |

| DOP<br>DON   | 0      | AUI TRANSMIT PAIR: A differential output driver pair for the AUI transceiver cable. The output is Manchester encoded.                                                                                                                                                                                                                                                                                              |

| JAB          | 0      | JABBER INDICATION: Output goes high to indicate Jabber state.                                                                                                                                                                                                                                                                                                                                                      |

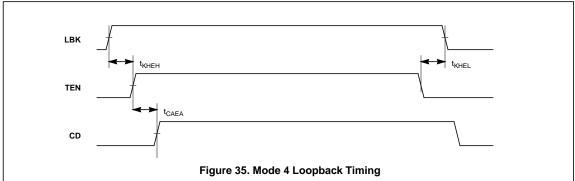

| LBK          | I      | LOOPBACK: When LBK=1, forced loopback is enabled. When LBK=0, normal loopback is enabled.                                                                                                                                                                                                                                                                                                                          |

| LEDC/XLBK    | O/I    | COLLISION LED: Open drain driver for the collision indicator. Output is pulled low during collision (half-duplex mode). If externally tied low, the MB86961A disables the internal TP loopback and collision detection circuits in anticipation of external TP loopback or full-duplex operation. MB86961A is ready for loopback testing 16 ms after this pin goes low. No delay is needed when the pin goes high. |

| LEDL         | O/I    | <b>LINK LED:</b> Open drain driver for link integrity indicator. Output pulled low during link test pass. If externally tied low, internal circuitry is forced to "Link Pass' state and the MB86961A will continue to transmit link test pulses.                                                                                                                                                                   |

| LEDR         | 0      | <b>RECEIVE LED:</b> Open drain driver for the receive indicator LED. Output is pulled low during receive.                                                                                                                                                                                                                                                                                                          |

| LEDT/<br>PDN | O/I    | <b>TRANSMIT LED/POWER DOWN:</b> Open drain driver for the transmit indicator. Output is pulled low during transmit. If externally tied low, the MB86961A goes to power down state.                                                                                                                                                                                                                                 |

| LI           | I      | LINK TEST ENABLE: When LI=0, the Link Integrity Test function is disabled. When LI=1, the Link Integrity Test function is enabled.                                                                                                                                                                                                                                                                                 |

| MD0<br>MD1   | I      | MODE SELECT: Mode select pins which determine controller compatibility mode. See Table 1.                                                                                                                                                                                                                                                                                                                          |

| NTH          | I      | NORMAL THRESHOLD: When NTH=1, the normal TP squelch threshold is in effect. When NTH=0, the normal TP squelch threshold is reduced by 4.5 dB.                                                                                                                                                                                                                                                                      |

| PAUI         | 1      | PORT/AUI SELECT: In Manual Port Select mode (AUTOSEL=0), PAUI selects the active port. When PAUI=1, the AUI port is selected, When PAUI=0, the TP port is selected. In Auto Port Select mode, PAUI is ignored.                                                                                                                                                                                                     |

| PLR          | 0      | POLARITY REVERSE: Output goes high to indicate reversed polarity.                                                                                                                                                                                                                                                                                                                                                  |

| RBIAS        | ı      | BIAS CONTROL: A bias resistor at this pin controls the bias of the operating circuit.                                                                                                                                                                                                                                                                                                                              |

| RCLK         | 0      | RECEIVE CLOCK: A recovered 10 MHz clock which is synchronous with the received data and connected to the controller receive clock input.                                                                                                                                                                                                                                                                           |

# MB86961A

#### SIGNAL DESCRIPTIONS (Continued)

| Symbol             | Туре   | Description                                                                                                                                                                                                                                                                     |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCMPT              | 0      | <b>REMOTE COMPATIBILITY:</b> Output goes high to signal the controller that the remote port is compatible with the MB86961A remote signaling features.                                                                                                                          |

| RJAB               | 0      | <b>REMOTE JABBER:</b> Output goes high to signal the controller that the remote port is in Jabber condition.                                                                                                                                                                    |

| RLD                | 0      | <b>REMOTE LINK DOWN:</b> Output goes high to signal to the controller that the remote port is in link down condition.                                                                                                                                                           |

| RXD                | 0      | <b>RECEIVE DATA:</b> Output signal connected directly to the receive data input of the controller.                                                                                                                                                                              |

| TCLK               | 0      | <b>TRANSMIT CLOCK:</b> A 10 MHz clock output. This clock signal is directly connected to the transmit clock input of the controller.                                                                                                                                            |

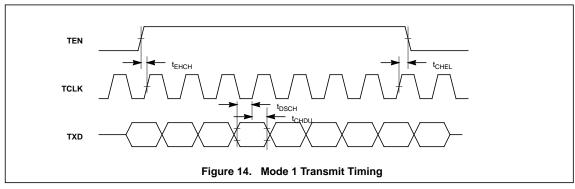

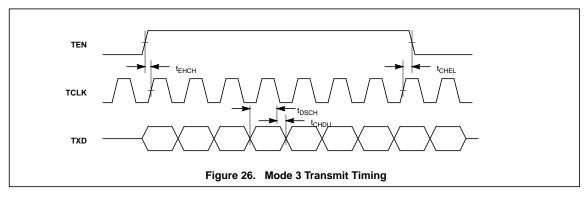

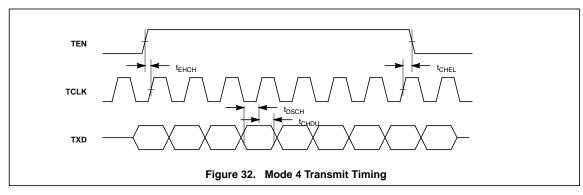

| TEN                | I      | <b>TRANSMIT ENABLE:</b> Enables data transmission and starts the watchdog timer. Synchronous with TCLK (see Figures 14, 20, 26, and 32 for details).                                                                                                                            |

| TEST               | 1      | TEST: Input for factory test of the device. Leave open for normal operation.                                                                                                                                                                                                    |

| TPIP<br>TPIN       | 0      | RECEIVE TWISTED-PAIR: A differential input pair from the twisted-pair cable. Receive filter is integrated in-chip. No external filters are required.                                                                                                                            |

| TPOPA/B<br>TPONA/B | 0      | <b>TRANSMIT TWISTED PAIR:</b> Two differential driver pair outputs (A and B) to the twisted-pair cable. The output is pre-equalized, no external filter is required. Two pairs are used to provide compatibility with both 100 $\Omega$ load cable and 150 $\Omega$ load cable. |

| TXD                | I      | <b>TRANSMIT DATA:</b> Input signal containing NRZ data to be transmitted on the network. TXD is connected directly to the transmit data output of the controller.                                                                                                               |

| UTP                | I      | <b>UTP/STP:</b> When UTP=0, 150 $\Omega$ termination for shielded TP is selected. When UTP=1,100 $\Omega$ termination for unshielded TP is selected.                                                                                                                            |

| VCC1, VCC2         | _      | POWER INPUTS: +5V power supply inputs.                                                                                                                                                                                                                                          |

| GND1<br>GND2       | _<br>_ | GROUND RETURNS 1 & 2: Grounds                                                                                                                                                                                                                                                   |

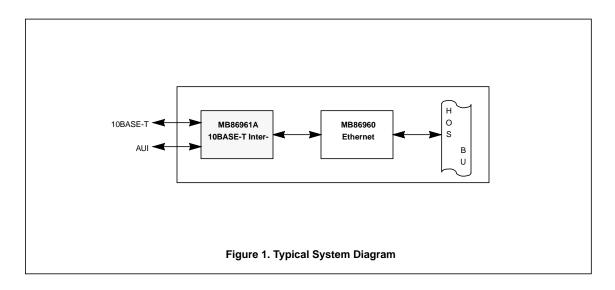

#### **APPLICATIONS**

Figure 1 shows the MB86961A in a typical application, interfacing between a controller and the RJ45 connector of the twisted-pair network. Figures 2 through 5 show detailed diagrams of various MB86961A applications.

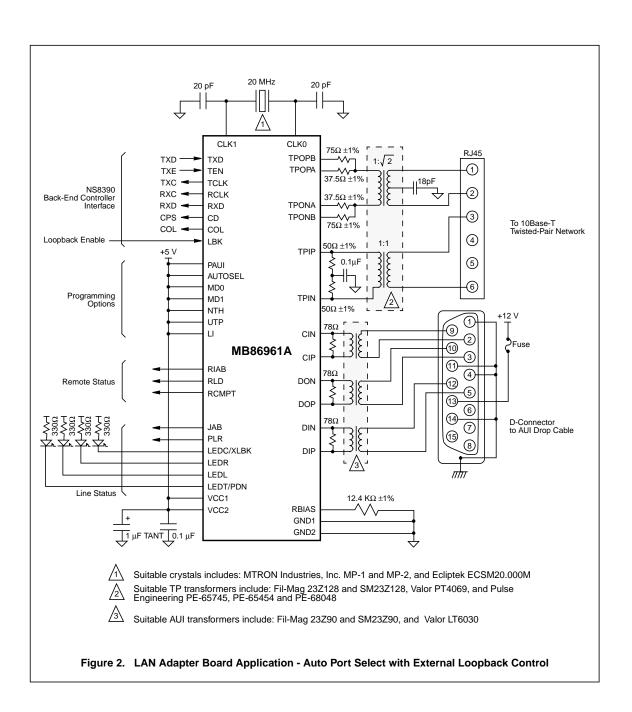

# AUTO PORT SELECT LOOPBACK CONTROL PIN

With MD0 and MD1 both tied high, the MB86961A logic and framing are set to Mode 4 (compatible with National NS8390 controllers).

The AUTOSEL pin is tied high, allowing the MB86961A to automatically select the active port. The high at LI enables Link Testing.

The UTP and NTH pins are both tied high selecting the standard receiver threshold and  $100~\Omega$  termination for unshielded TP cable. (See Figure 2.)

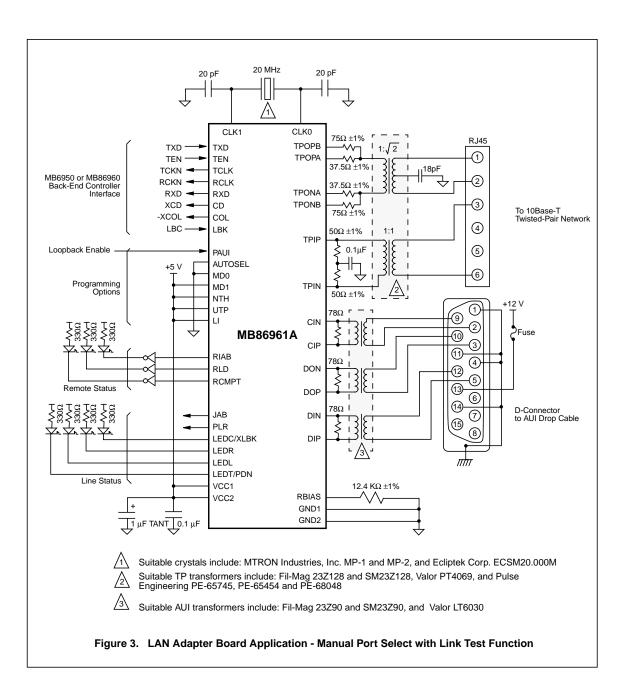

# MANUAL PORT SELECT LINK TEST FUNCTION

With MD0 low and MD1 tied high, the MB86961A logic and framing are set to Mode 3 (compatible with Fujitsu's MB86960 controller). As in Figure 3, the LI pin is tied high, enabling Link Testing, and the UTP and NTH pins are both tied high, selecting the standard receiver threshold and 100  $\Omega$  termination for unshielded TP cable. However, in this application AUTOSEL is tied low, allowing

external port selection through the PAUI pin. The remote status output are inverted and used to drive LED indicators. (See Figure 3.)

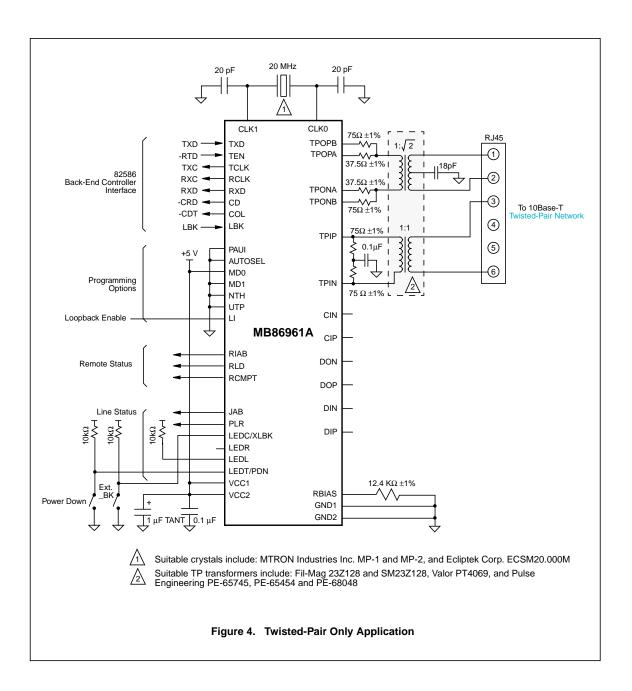

#### TWISTED-PAIR ONLY

Figure 4 shows the MB86961A is a typical twisted-pair only application. The DTE is connected to a 10BASE-T network through the twisted-pair RJ45 connector. (The AUI port is not used.) With MD0 tied high and MD1 grounded, the MB86961A logic and framing are set to Mode 2 (compatible with Intel 82586 controllers). The LI pin externally controls the link test function. The UTP and NTH pins are both tied low, selecting the reduced receiver threshold and 150  $\Omega$  termination for shielded TP cable. The switch at LEDT/PDN manually controls the power down mode. (See Figure 4.)

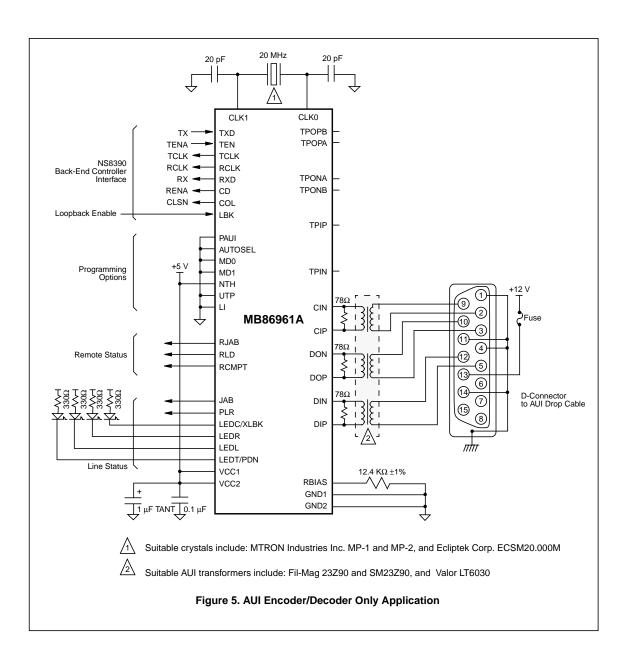

#### AUI ENCODER/DECODER ONLY

In this application, the DTE is connected to the coaxial network through the AUI. AUTOSEL and PAUI are both tied to ground, manually selecting the AUI port. The twisted-pair port is not used. With MD1 and MD0 both grounded, the MB86961A logic and framing are set to Mode 1 (compatible with AMD AM7990 controllers). The LI pin is tied low, disabling the link test function. The LBK input controls loopback. A 20 MHz crystal connected across CLKI and CLK0 provides the required clock signal. (See Figure 5.)

#### **FUNCTIONAL DESCRIPTION**

The MB86961A Universal Ethernet Interface Transceiver performs the physical layer signaling (PLS) and Media Attachment Unit (MAU) functions as defined by the IEEE 802.3 specification. It functions as a PLS-only device (for use with 10BASE2 or 10BASE5 coaxial cable networks) or as an Integrated PLS/MAU (for use with 10BASE-T twisted-pair networks).

The MB86961A interfaces a back-end controller to either an AUI drop cable or twisted-pair (TP) cable. The controller interface includes transmit and receive clock and NRZ data channels, as well as mode control logic and signaling. The AUI interface comprises three circuits: Data output (DO), Data Input (DI) and Collision (CI). The twisted-pair interface comprises two circuits: Twisted-Pair Input (TPI) and Twisted-Pair Output (TPO). In addition to the three basic interfaces, the MB86961A contains an internal crystal oscillator and four LED drivers for visual status reporting.

Functions are defined from the back end controller side of the interface. The MB86961A Transmit function refers to data transmitted by the back end to the AUI cable (PLS-Only mode) or to the twisted-pair network (Integrated PLS/MAU mode). The MB86961A Receive function refers to data received by the back end from the AUI cable (PLS-Only) or from the twisted-pair network (Integrated PLS/MAU mode). In the integrated PLS/MAU mode, the MB86961A performs all required MAU functions defined by the IEEE 802.3 10BASE-T specification such as collision detection, link integrity testing, signal quality error messaging, jabber control and loopback. In the PLS-Only mode, the MB86961A receives incoming signals from the AUI DI circuit with up to 18ns of jitter and drives the AUI DO circuit.

#### **CONTROLLER COMPATIBILITY MODES**

The MB86961A is compatible with most industry standard controllers including devices produced by Advanced Micro Devices (AMD), Intel, Fujitsu and National Semiconductor. Four different control signal timing and polarity schemes (Modes 1 through 4) are required to achieve this compatibility. Mode select pins MD0 and MD1 determine controller compatibility modes as listed in Table 1.

Table 1. MB86961A Compatibility Modes

| MD1 | MD0 |         | Mode                                                            |

|-----|-----|---------|-----------------------------------------------------------------|

| 0   | 0   | Mode 1: | Compatible with Advanced Micro Devices AM7990 controllers       |

| 0   | 1   | Mode 2: | Compatible with Intel 82586 controllers                         |

| 1   | 0   | Mode 3: | Compatible with Fujitsu's MB86960 controller                    |

| 1   | 1   | Mode 4: | Compatible with National<br>Semiconductor 8390 control-<br>lers |

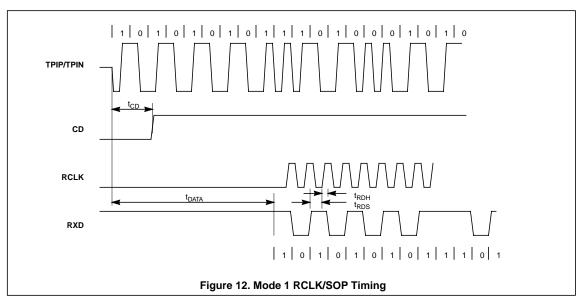

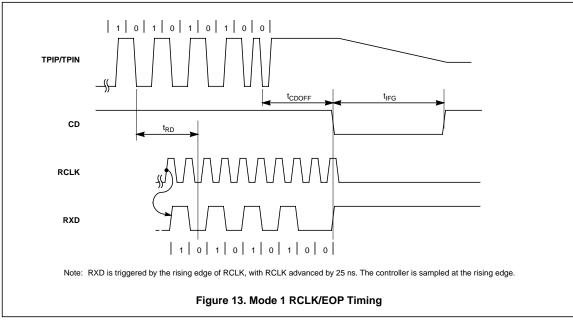

Mode 1: Figures 12-17

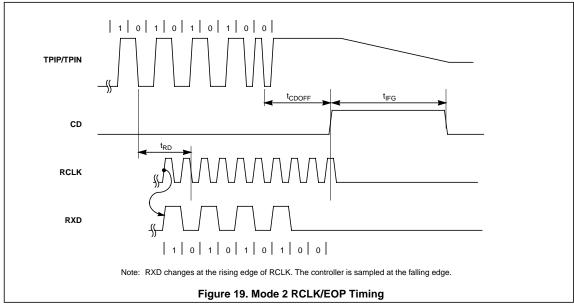

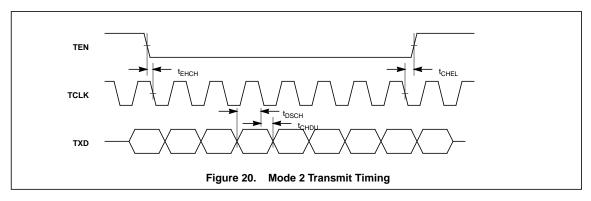

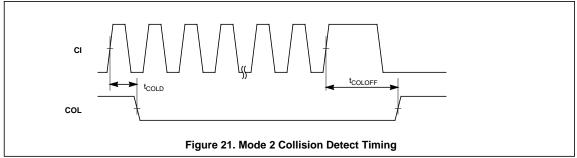

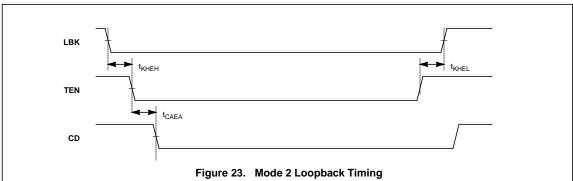

• Mode 2: Figures 18-23

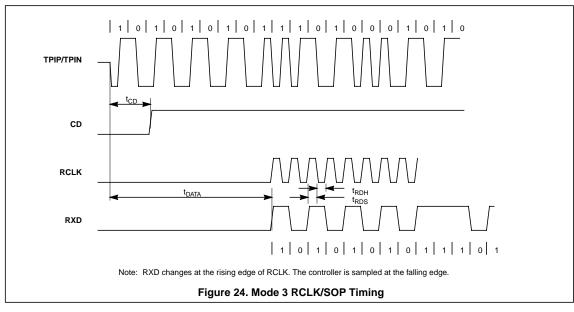

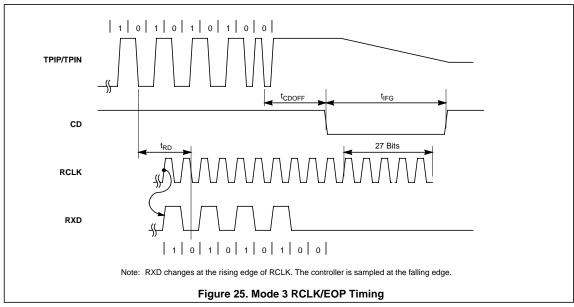

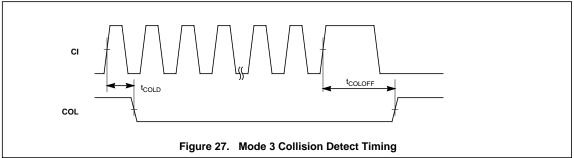

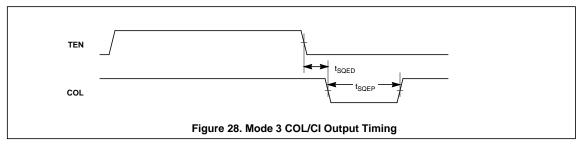

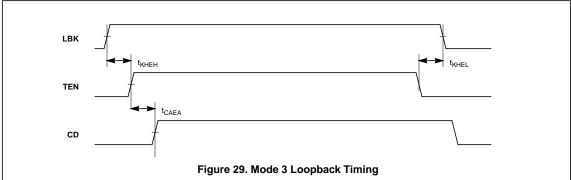

• Mode 3: Figures 24-29

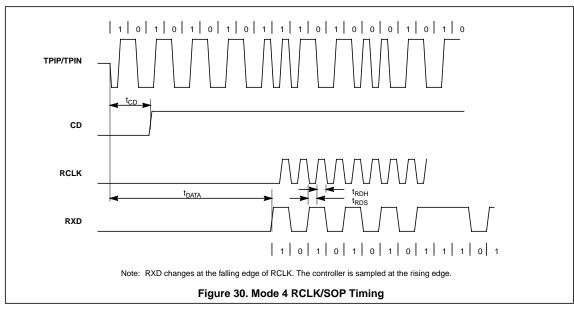

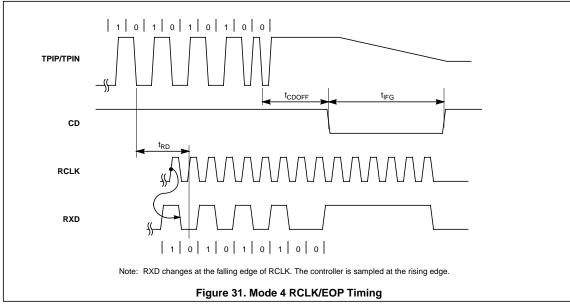

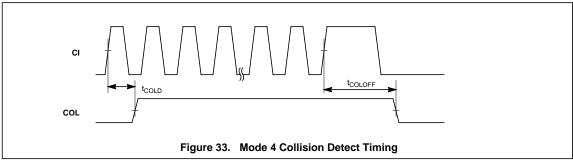

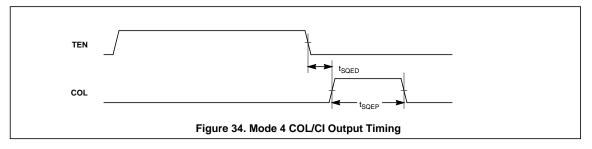

• Mode 4: Figures 30-35

The related timing specifications are provided in the electrical characteristics section of this data sheet.

#### TRANSMIT FUNCTION

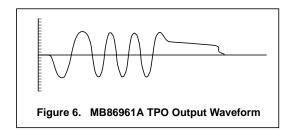

The MB86961A receives NRZ data from the controller at the TXD input (see MB86961A block diagram), and passes it through a Manchester encoder. The encoded data is then transferred to either the AUI cable (the DO circuit) or the twisted-pair network (the TPO circuit). The advanced integrated pulse shaping and filtering network produces the output signal on TPON and TPOP, shown in Figure 6. The TPO output is pre-distorted and prefiltered to meet the 10BASE-T jitter template. No external filters are required. During idle periods, the MB86961A transmits link integrity test pulses on the TPO circuit if LI is enabled and integrated PLS/MAU mode is selected. The MB86961A can be programmed for either shielded TP (150  $\Omega$ ) or unshielded TP (100  $\Omega$ ) through the UTP pin.

#### **JABBER CONTROL FUNCTION**

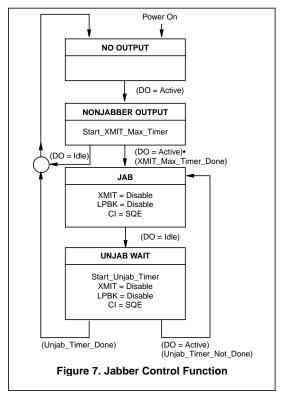

Figure 7 is a state diagram of the MB86961A Jabber control function. The MB86961A on-chip watchdog timer prevents the DTE from locking into a continuous transmit mode. When a transmission exceeds the time limit, the watchdog timer disables the transmit and loopback functions, and activates the JAB pin. Once the MB86961A is in the jabber state, the TXD circuit must remain idle for a period of 0.25 to 0.75 seconds before it will exit the jabber state.

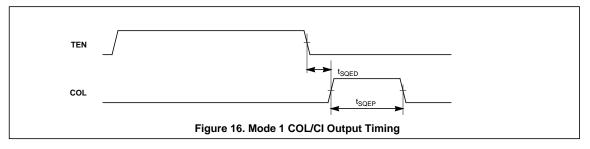

#### **SQE FUNCTION**

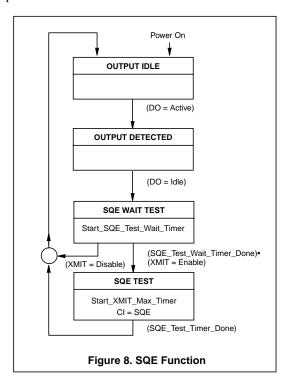

In the integrated PLS/MAU mode, the MB86961A supports the signal quality error (SQE) function as shown in Figure 8. After every successful transmission on the 10BASE-T network, the MB86961A transmits the SQE signal to the DTE for  $10\pm5$  bit times over the internal CI Circuit.

#### RECEIVE FUNCTION

The MB86961A receive function acquires timing and data from the twisted-pair network (the TPI circuit) or from the AUI (the DI Circuit). Valid received signals are passed through the on-chip filters and Manchester

decoder and output as decoded NRZ data and receive timing on the RXD and RCLK pins, respectively. No external filters are required.

An internal intelligent squelch function discriminates noise from link test pulses and valid data streams. The receive function is activated only by valid data streams above the squelch level and with proper timing. If the differential signal at the TPI or the DI circuit inputs falls below 75% of the threshold level (unsquelched) for eight bit times (typical), the MB86961A receive function enters the idle state. If the polarity of the TPI circuit is reversed, the MB86961A detects the polarity reversal and reports it via the PLR output. The MB86961A automatically corrects reversed polarity.

#### **POLARITY REVERSE FUNCTION**

The MB86961A polarity reverse function uses both link pulses and end-of-frame data to determine the polarity of the received signal. A reversed polarity condition is detected when eight opposite receive link pulses are detected without receipt of a link pulse of the expected polarity. Reversed polarity is also detected if four frames are received with a reversed start-of-idle. Whenever polarity is reversed, these two counters are reset to zero. If the MB86961A enters the link fail state and no valid

data or link pulses are received within 96 to 128 ms, the polarity is reset to the default non-flipped condition. If Link Integrity Testing is disabled, polarity detection is based only on received data. Polarity correction is always enabled.

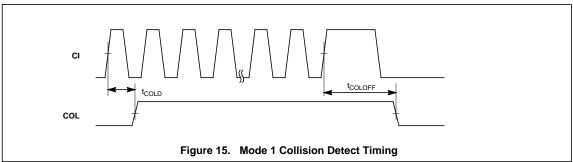

#### **COLLISION DETECTION FUNCTION**

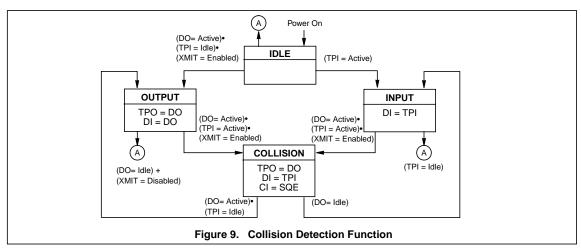

The collision detection function operates on the twistedpair side of the interface. A collision is defined as the

simultaneous presence of valid signals on both the TPI circuit and the TPO circuit. The MB86961A reports collisions to the back-end via the COL pin. If the TPI circuit becomes active while there is activity on the TPO circuit, the TPI data is passed to the back-end over the RXD circuit, disabling normal loopback. Figure 9 is a state diagram of the MB86961A collision detection function. Refer to Electrical Characteristics for collision detection and COL/CI output timing.

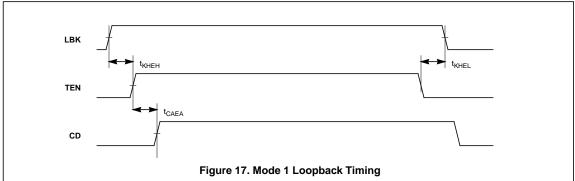

#### LOOPBACK FUNCTION

The MB86961A provides the normal loopback function specified by the 10BASE-T standard for the twisted-pair port. The loopback function operates in conjunction with the transmit function. Data transmitted by the back-end is internally looped back within the MB86961A from the TXD pin through the Manchester encoder/decoder to the RXD pin and returned to the back-end. The "normal" loopback function is disabled when a data collision occurs, clearing the RXD circuit for the TPI data. Normal loopback is also disabled during link fail and jabber states.

The MB86961A also provides additional loopback functions. An external loopback mode, useful for system-level testing, is controlled by pin 21 (LEDC). When LEDC is tied low, the MB86961A disables the collision detection and internal loopback circuits to allow external loopback or full-duplex operation. The MB86961A provides loopback functions controlled by pin 22 (LBK). When the TP port is selected and LBK=1, TP loopback is "forced," overriding collisions on the TP circuit. When LBK=0, normal loopback is in effect.

When the AUI port is selected and LBK=1, data transmitted by the back-end controller is internally looped back from the TXD pin through the Manchester encoder/decoder to the RXD pin. When LBK=0, no AUI loopback occurs.

#### LINK INTEGRITY TEST

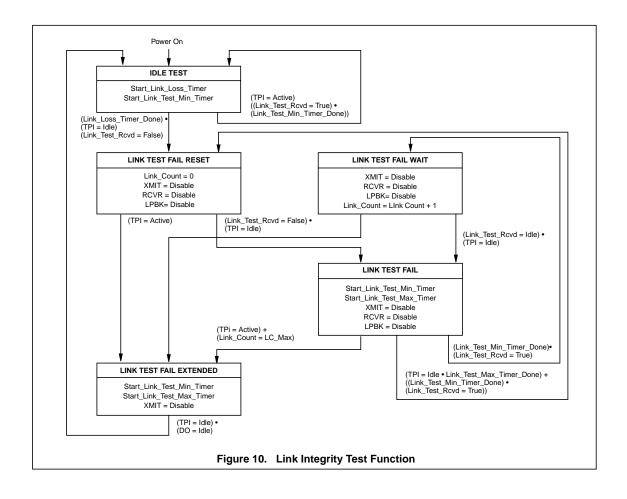

Figure 10 is a state diagram of the MB86961A Link Integrity test function. The link integrity test is used to determine the status of the receive side twisted-pair cable. Link integrity testing is enabled when pin 8 (LI) is tied

high. When enabled, the receiver recognizes link integrity pulses which are transmitted in the absence of receive traffic. If no serial data stream or link integrity pulses are detected within 50-150 ms, the chip enters a link fail state and disables the transmit and normal loopback functions. The MB86961A ignores any link integrity pulse with an interval less than 2-7 ms. The MB86961A will remain in the link fail state until it detects either a serial data packet or two or more link integrity pulses.

#### **REMOTE SIGNALING**

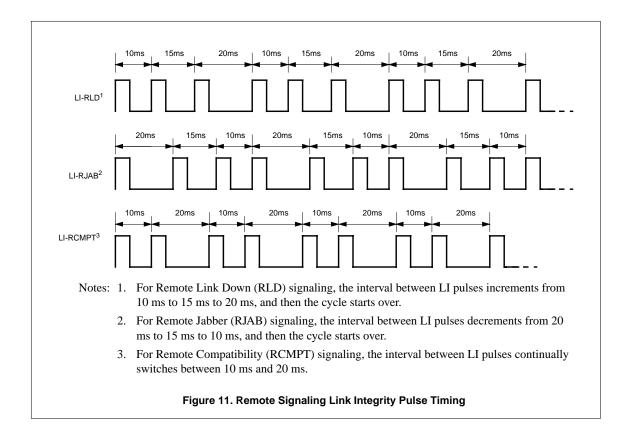

The MB86961A transmits standard link pulses which meet the 10BASE-T specification. However, the MB86961A encodes additional status information into the link pulse by varying the link pulse timing. This is referred to as remote signaling. Using alternate pulse intervals, the MB86961A can signal three local condi-

tions: link down, jabber, and remote signaling capability. Figure 11 shows the interval variations used to signal local status to the other end of the line. The MB86961A also recognizes these alternate pulse intervals when received from a remote unit. Remote status conditions are reported to the controller over the RLD, RJAB and RCMPT output pins.

#### **ELECTRICAL CHARACTERISTICS**

Table 2. ABSOLUTE MAXIMUM RATINGS

| Symbol          | Rating                | Conditions | Min. | Max. | Units |

|-----------------|-----------------------|------------|------|------|-------|

| V <sub>CC</sub> | Supply voltage        |            | -0.3 | 6    | V     |

| T <sub>OP</sub> | Operating temperature |            | 0    | 70   | °C    |

| T <sub>ST</sub> | Storage temperature   |            | -65  | 150  | °C    |

Note: Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 3. INPUT/OUTPUT CHARACTERISTICS ( $T_A = 0$ °C to +70°C,  $V_{CC} = 5 \text{ V} \pm 5\%$ )

| Symbol          | Parame                          | eter | Condition               | Min. | Typ. <sup>1</sup> | Max. | Units            |

|-----------------|---------------------------------|------|-------------------------|------|-------------------|------|------------------|

| V <sub>IL</sub> | Input low voltage <sup>1</sup>  |      |                         |      | _                 | 0.8  | V                |

| V <sub>IH</sub> | Input high voltage <sup>2</sup> |      |                         | 2.0  | _                 | _    | V                |

| V <sub>OL</sub> | Output low voltage              |      | I <sub>OL</sub> =3.2 mA | _    | _                 | 0.4  | V                |

|                 |                                 |      | I <sub>OL</sub> < 10 mA | _    | _                 | 10   | %V <sub>CC</sub> |

| V <sub>OH</sub> | Output high voltage             |      | I <sub>OH</sub> = 40 mA | 2.4  | _                 | _    | V                |

|                 |                                 |      | I <sub>OH</sub> < 10 mA | 90   | _                 | _    | %V <sub>CC</sub> |

| ICC             | Supply current                  |      | Normal mode             | _    | 90                | _    | mA               |

|                 |                                 |      | Power-down mode         |      | 5                 | _    | mA               |

| t <sub>R</sub>  | Output rise time                | CMOS | TCLK and RCLK           | _    | 3                 | _    | ns               |

|                 |                                 | TTL  | TCLK and RCLK           | _    | 2                 | _    | ns               |

| t <sub>F</sub>  | Output fall time                | CMOS | TCLK and RCLK           | _    | 3                 | _    | ns               |

|                 |                                 | TTL  | TCLK and RCLK           | _    | 2                 | _    | ns               |

Notes: 1. Typical figures are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

2. Limited functional test patterns are performed at these input levels. The majority of functional tests are performed at levels 0V and 3 V.

Table 4. AUI ELECTRICAL CHARACTERISTICS (T<sub>A</sub> =  $0^{\circ}$ C to + $70^{\circ}$ C, V<sub>CC</sub> = 5 V  $\pm 5\%$ )

| Symbol          | Parameter                      | Condition | Min. | Typ. <sup>1</sup> | Max.  | Units |

|-----------------|--------------------------------|-----------|------|-------------------|-------|-------|

| I <sub>IL</sub> | Input low current              |           | _    | _                 | -700  | μΑ    |

| I <sub>IH</sub> | Input high current             |           | _    | _                 | 500   | μΑ    |

| V <sub>OD</sub> | Differential output voltage    |           | ±550 | _                 | ±1200 | mV    |

| V <sub>DS</sub> | Differential squelch threshold |           | _    | 220               | _     | mV    |

Note: Typical figures are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

Table 5. TP ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 0°C to +70°C, V<sub>CC</sub> = 5 V  $\pm 5\%$ )

| Symbol           | Parameter                        | Condition                                                   | Min. | Typ. <sup>1</sup> | Max. | Units |

|------------------|----------------------------------|-------------------------------------------------------------|------|-------------------|------|-------|

| Z <sub>OUT</sub> | Transmit output impedance        |                                                             | _    | 5                 | _    |       |

| V <sub>OD</sub>  | Peak differential output voltage | Load=100 $\Omega$ at TPOP and TPON                          | _    | 3.5               | _    | V     |

| t <sub>JIT</sub> | Transmit timing jitter addition  | 0 line length <sup>1</sup>                                  | _    | _                 | ±8   | ns    |

| t <sub>JIT</sub> | Transmit timing jitter addition  | After line model specified<br>by IEEE 802.3 for<br>10BASE-T | _    | _                 | ±3.5 | ns    |

| Z <sub>IN</sub>  | Receive input impedance          | Between TPIP/TPIN,<br>CIP/CIN and DIP/DIN                   | _    | 20                | _    | kΩ    |

| V <sub>DS</sub>  | Differential squelch threshold   |                                                             | _    | 420               | _    | mV    |

| V <sub>DSL</sub> | Lower squelch threshold          |                                                             |      | 250               | _    | mV    |

Notes: 1. Typical figures are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

2. Parameter is guaranteed by design, not subject to production testing.

Table 6. SWITCHING CHARACTERISTICS ( $T_A = 0$ °C to +70°C,  $V_{CC} = 5 \text{ V} \pm 5\%$ )

| Symbol            | Parameter                                        | Condition | Min. | Тур. | Max. | Units |

|-------------------|--------------------------------------------------|-----------|------|------|------|-------|

| Jabber Tim        | ing                                              |           |      |      |      |       |

| t <sub>JAB</sub>  | Maximum transmit time                            |           | 20   | _    | 150  | ms    |

| t <sub>UJAB</sub> | Unjab time                                       |           | 250  | _    | 750  | ms    |

| Link Integrit     | ty Timing                                        |           |      |      |      |       |

| t <sub>LL</sub>   | Time link loss                                   |           | 55   | _    | 66   | ms    |

| t <sub>LP1</sub>  | Time between Link Integrity Pulses               |           | 8    | _    | 24   | ms    |

| t <sub>LP2</sub>  | Interval for valid receive Link integrity Pulses |           | 4.1  | _    | 65   | ms    |

| General           |                                                  |           |      |      |      |       |

| t <sub>RST</sub>  | Receive start-up delay <sup>1</sup>              |           | 0    | _    | 500  | ns    |

| t <sub>TST</sub>  | Transmit start-up delay <sup>1</sup>             |           | 0    | _    | 200  | ns    |

| t <sub>LST</sub>  | Loopback start-up delay <sup>1</sup>             |           | 0    | _    | 500  | ns    |

Note: Parameter is guaranteed by design; not subject to production testing.

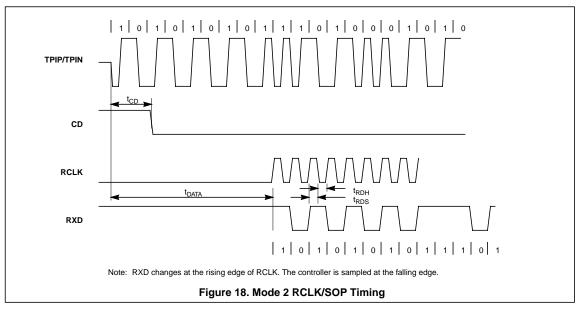

Table 7. RCLK/Start-of-Packet Timing

| Symbol            | Parameter                    |                  | Min. | Typ. <sup>1</sup> | Max. | Units |

|-------------------|------------------------------|------------------|------|-------------------|------|-------|

| t <sub>DATA</sub> | Decoder acquisition time     | AUI              | _    | 900               | _    | ns    |

|                   |                              | TP               | _    | 1300              | _    | ns    |

| t <sub>CD</sub>   | CD turn-on delay             | AUI              | _    | 50                | _    | ns    |

|                   |                              | TP               | _    | 400               | _    | ns    |

| t <sub>RDS</sub>  | Receive data setup from RCLK | Mode 1           | 40   | _                 | _    | ns    |

|                   |                              | Modes 2, 3 and 4 | 30   | _                 | _    | ns    |

| t <sub>RDH</sub>  | Receive data hold from RCLK  | Mode 1           | 10   | _                 | _    | ns    |

|                   |                              | Modes 2, 3 and 4 | 30   | _                 | _    | ns    |

Note: Typical figures are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

Table 8. RCLK/End-of-Packet Timing

| Symbol             | Parameter                 | Туре | Mode 1 | Mode 2 | Mode 3 | Mode 4 | Units |

|--------------------|---------------------------|------|--------|--------|--------|--------|-------|

| t <sub>RCH</sub>   | RCLK hold after CD low    | Min. | 0      | 1      | 27     | 5      | bt    |

| t <sub>RD</sub>    | RCV data throughput delay | Тур. | 300    | 275    | 275    | 275    | ns    |

| t <sub>CDOFF</sub> | CD turn off delay         | Тур. | 400    | 375    | 375    | 375    | ns    |

| t <sub>IFG</sub>   | Receive block out         | Тур. | 2      | 50     | 27     | 5      | bt    |

Notes: 1. Typical figures are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

2. CD Turn off delay measured from middle of last bit, so timing specification is unaffected by the value of the last bit.

Table 9. Transmit Timing

| Symbol            | Parameter           | Min. | Typ. <sup>1</sup> | Max. | Units |

|-------------------|---------------------|------|-------------------|------|-------|

| t <sub>EHCH</sub> | TEN setup from TCLK | _    | 30                | _    | ns    |

| t <sub>DSCH</sub> | TXD setup from TCLK | _    | 30                | _    | ns    |

| t <sub>CHEL</sub> | TEN hold after TCLK | _    | 5                 | _    | ns    |

| t <sub>CHDU</sub> | TXD hold after TCLK | _    | 5                 | _    | ns    |

Note: Typical figures are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

Table 10. Collision Detection, COL/CI Output and Loopback Timing

| Symbol              | Parameter          | Min. | Typ. <sup>1</sup> | Max. | Units |

|---------------------|--------------------|------|-------------------|------|-------|

| t <sub>COLD</sub>   | COL turn on delay  | _    | 50                | _    | ns    |

| t <sub>COLOFF</sub> | COL turn off delay | _    | 160               | _    | ns    |

| t <sub>SQED</sub>   | SQE Delay          | 0.65 | _                 | 1.6  | ms    |

| t <sub>SQEP</sub>   | SQE Pulse Duration | 500  | _                 | 1500 | ns    |

| t <sub>KHEH</sub>   | LBK setup from TEN | _    | 25                | _    | ns    |

| t <sub>KHEL</sub>   | LBK hold after TEN | _    | 0                 | _    | ns    |

Note: Typical figures are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

# MODE 1 (MD1=0, MD0=0) TIMING DIAGRAMS — FIGURES 12 - 17

# MODE 2 (MD1=0, MD0=1) TIMING DIAGRAMS — FIGURES 18 - 23

# MODE 3 (MD1=1, MD0=0) TIMING DIAGRAMS — FIGURES 24 - 29

# MODE 4 (MD1=1, MD0=1) TIMING DIAGRAMS — FIGURES 30 - 35

# **ORDERING INFORMATION: MB86961APD-G**

# **ORDERING INFORMATION: MB86961APF-G**

# **Worldwide Headquarters**

Japan

+81 44 754 3753 +81 44 754 3332

Japan

**Fujitsu Limited**

1015 Kamiodanaka

Nakaharaku Kawasaki 211

http://www.fujitsu.co.jp/

**USA**

Tel: +1 408 922 9000 +1 408 922 9179

Fujitsu Microelectronics Inc 3545 North First Street San Jose CA 95134-1804

Tel: +1 800 866 8608 +1 408 922 9179

Customer Response Center Mon-Fri: 7am-5pm (PST)

http://www.fujitsumicro.com/

**Asia**

Tel: +65 281 0770 Fax: +65 281 0220

http://www.fsl.com.sg/

Europe

Tel: +49 6103 6900 Fax: +49 6103 69012

Fujitsu Microelectronics Asia PTE

#05-08, 151 Lorong Chuan New Tech Park Singapore 556741

Fujitsu Mikroelektronik GmbH

Am Siebenstein 6-10 D-63303 Dreieich-Buchschlag Germany

http://www.fujitsu.ede.com/

All Right Reserved.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu Microelectronics, Inc. assumes no responsibility for inaccuracies.

The information conveyed in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu Limited, its subsidiaries, or Fujitsu Microelectronics, Inc.

Fujitsu Microelectronics, Inc. reserves the right to change products or specifications without notice.

No part of the publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu Microelectronics, Inc.

LAN-DS-20638-12/97