# Ultra High Speed Operational Amplifier

### **FEATURES**

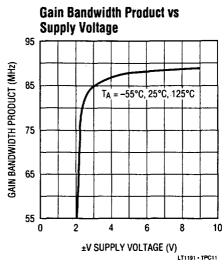

90MHz ■ Gain Bandwidth Product, A<sub>V</sub> = +1 Slew Rate 450V/us

Low Cost

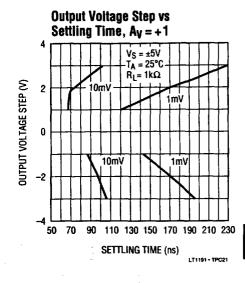

Output Current ±50mA 110ns to 0.1% Settling Time Differential Gain Error 0.07%, (R<sub>L</sub> = 1k)

$0.02^{\circ}$ ,  $(R_L = 1k)$

25V/mV Min

Differential Phase Error High Open Loop Gain

■ Single Supply +5V Operation

Output Shutdown

### **APPLICATIONS**

- Video Cable Drivers

- Video Signal Processing

LINEAR

- Fast Integrators

- Pulse Amplifiers

- D/A Current to Voltage Conversion

### DESCRIPTION

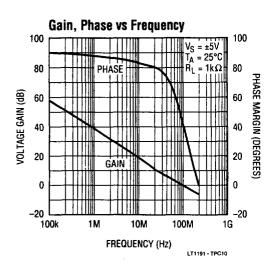

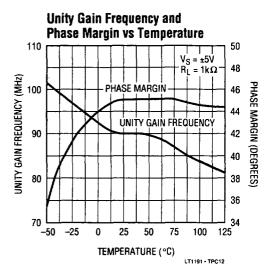

The LT1191 is a video operational amplifier optimized for operation on ±5V, and a single +5V supply. Unlike many high speed amplifiers, this amplifier features high open loop gain, over 90dB, and the ability to drive heavy loads to a full power bandwidth of 20MHz at 7Vp-p. In addition to its very fast slew rate, the LT1191 features a unity gain stable bandwidth of 90MHz.

Because the LT1191 is a true operational amplifier, it is an ideal choice for wideband signal conditioning, fast integrators, active filters, and applications requiring speed. accuracy, and low cost.

The LT1191 is available in 8-pin miniDIPs and SO packages with standard pinouts. The normally unused pin 5 is used for a shutdown feature that shuts off the output and reduces power dissipation to a mere 15mW.

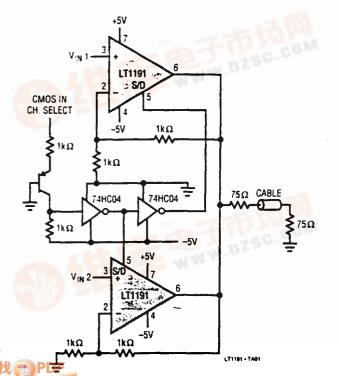

### Video MUX Cable Driver

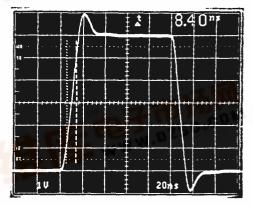

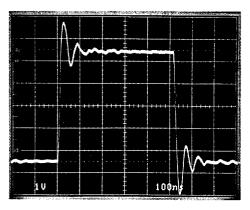

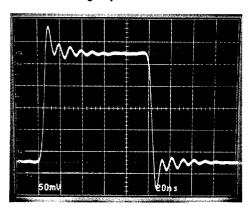

#### Inverter Pulse Response

$A_V = -1$ ,  $C_1 = 10pF$  SCOPE PROBE

LT1191 • TAG2

# **ABSOLUTE MAXIMUM RATINGS**

###

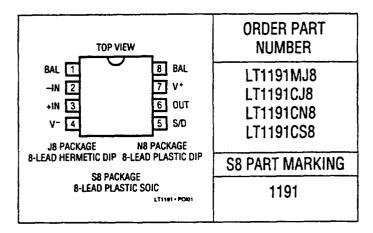

## PACKAGE/ORDER INFORMATION

# **ELECTRICAL CHARACTERISTICS** $v_s = \pm 5v$ , $T_A = 25^{\circ}C$ , $C_L \le 10 pF$ , pin 5 open circuit unless otherwise noted.

|                                   |                           |                   |                                                       | LT1191M/C |      |      |          |  |

|-----------------------------------|---------------------------|-------------------|-------------------------------------------------------|-----------|------|------|----------|--|

| SYMBOL                            | PARAMETER                 |                   | CONDITIONS                                            | MIN       | TYP  | MAX  | UNITS    |  |

| V <sub>OS</sub>                   | Input Offset Volta        | ge                |                                                       |           | 1.0  | 5.0  | mV       |  |

| los                               | Input Offset Curre        | ent               |                                                       |           | 0.2  | 1.7  | μΑ       |  |

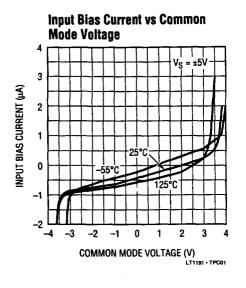

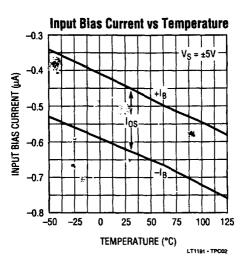

| lβ                                | Input Bias Curren         | t                 |                                                       |           | ±0.5 | ±2.5 | μΑ       |  |

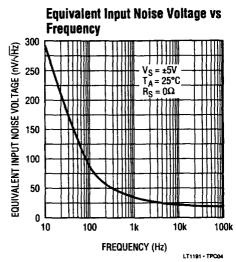

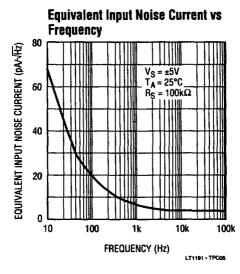

| en                                | Input Noise Volta         | ge                | f <sub>O</sub> = 10kHz                                |           | 25   |      | nV/√Hz   |  |

| in                                | Input Noise Curre         | ent               | f <sub>O</sub> = 10kHz                                |           | 4.0  |      | pA/√Hz   |  |

| R <sub>IN</sub>                   | Input Resistance          | Differential Mode |                                                       |           | 70   |      | kΩ       |  |

|                                   |                           | Common Mode       |                                                       |           | 5.0  |      | MΩ       |  |

| CiN                               | Input Capacitance         |                   | A <sub>V</sub> = +1                                   |           | 2.0  |      | pF       |  |

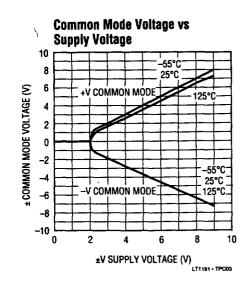

|                                   | Input Voltage Rar         | nge               | (Note 2)                                              | -2.5      |      | +3.5 | V        |  |

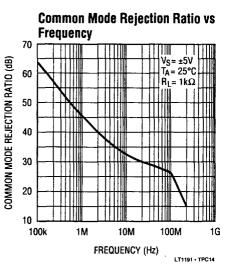

| CMRR                              | Common Mode R             | ejection Ratio    | V <sub>CM</sub> = -2.5V to + 3.5V                     | 60        | 75   |      | dB       |  |

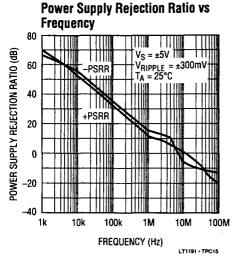

| PSRR                              | Power Supply Re           | jection Ratio     | $V_S = \pm 2.375V \text{ to } \pm 8.0V$               | 60        | 75   |      | dB       |  |

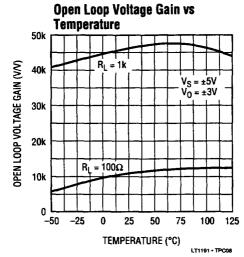

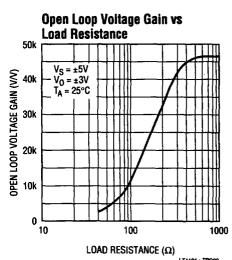

| A <sub>VOL</sub>                  | Large Signal Voltage Gain |                   | $R_L = 1k$ , $V_0 = \pm 3.0V$                         | 20        | 45   |      | V/mV     |  |

|                                   |                           | [                 | $R_L = 100\Omega$ , $V_0 = \pm 3.0V$                  | 6.0       | 12   |      | 1        |  |

|                                   |                           | Γ                 | $V_S = \pm 8V$ , $R_L = 100\Omega$ , $V_0 = \pm 5V$   | 9.0       | 17   |      | 1        |  |

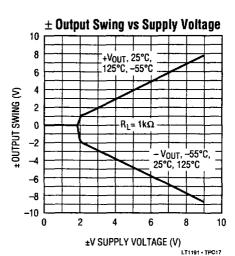

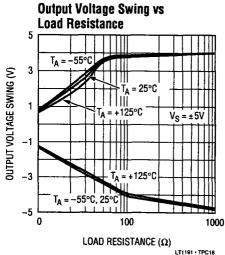

| Vout                              | Output Voltage St         | wing              | V <sub>S</sub> = ±5V, R <sub>L</sub> = 1k             | ±3.7      | ±4.0 |      | V        |  |

|                                   |                           | Ī                 | $V_S = \pm 8V, R_L = 1k$                              | ±6.7      | ±7.0 |      | 1        |  |

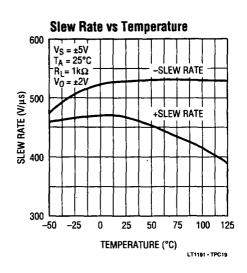

| SR                                | Slew Rate                 |                   | $A_V = -2$ , $R_L = 1k$ , (Note 3, 8)                 | 325       | 450  |      | V/µs     |  |

| FPBW                              | Full Power Bandwidth      |                   | V <sub>O</sub> = 6Vp-p, (Note 4)                      | 17.2      | 23.9 |      | MHz      |  |

| GBW                               | Gain Bandwidth Product    |                   |                                                       |           | 90   |      | MHz      |  |

| t <sub>r1</sub> , t <sub>f1</sub> | Rise Time, Fall Time      |                   | $A_V = +50$ , $V_0 = \pm 1.5V$ , 20% to 80%, (Note 8) | 100       | 130  | 160  | ns       |  |

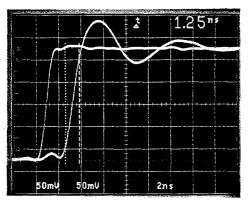

| t <sub>r2</sub> , t <sub>f2</sub> | Rise Time, Fall Time      |                   | $A_V = +1$ , $V_0 = \pm 125$ mV, 10% to 90%           |           | 1.25 |      | ns       |  |

| t <sub>PD</sub>                   | Propagation Delay         |                   | $A_V = +1$ , $V_0 = \pm 125$ mV, 50% to 50%           |           | 2.2  |      | ns       |  |

|                                   | Overshoot                 |                   | $A_V = +1, V_0 = \pm 125 \text{mV}$                   |           | 25   |      | %        |  |

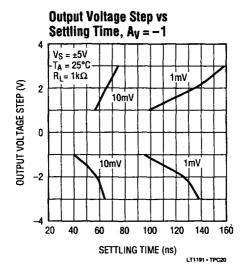

| t <sub>s</sub>                    | Settling Time             |                   | 3V Step, 0.1%, (Note 5)                               |           | 110  |      | пѕ       |  |

| Diff A <sub>V</sub>               | Differential Gain         |                   | $R_L = 150\Omega$ , $A_V = +2$ , (Note 6)             | 0.15      |      | %    |          |  |

| Diff Ph                           | Differential Phase        |                   | $R_L = 150\Omega$ , $A_V = +2$ , (Note 6)             |           | 0.09 |      | Deg. p-p |  |

# **ELECTRICAL CHARACTERISTICS** $v_8 = \pm 5 V$ , $T_A = 25 ^{\circ} C$ , $C_L \le 10 pF$ , pin 5 open circuit unless otherwise noted.

| SYMBOL           | 1 .                     | CONDITIONS                                                | LT1191M/C |     |     |       |

|------------------|-------------------------|-----------------------------------------------------------|-----------|-----|-----|-------|

|                  | PARAMETER               |                                                           | MIN       | TYP | MAX | UNITS |

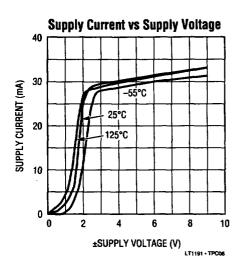

| Is               | Supply Current          |                                                           |           | 32  | 38  | mA    |

|                  | Shutdown Supply Current | Pin 5 at V <sup>-</sup>                                   |           | 1.3 | 2.0 | mA    |

| I <sub>S/D</sub> | Shutdown Pin Current    | Pin 5 at V <sup>-</sup>                                   |           | 20  | 50  | μА    |

| t <sub>on</sub>  | Turn On Time            | Pin 5 from V <sup>-</sup> to Ground, R <sub>L</sub> = 1k  |           | 100 |     | ns    |

| t <sub>off</sub> | Turn Off Time           | Pin 5 from Ground to V <sup>-</sup> , R <sub>L</sub> = 1k |           | 400 |     | ns    |

**ELECTRICAL CHARACTERISTICS**  $V_{S^+}=+5V,\ V_{S^-}=0V,\ V_{CM}=+2.5V,\ T_A=25^\circ C,\ C_L\le 10pF,\ pin\ 5$  open circuit unless otherwise noted.

|                  |                             |                                                          |                       |      | LT1191M | /C   |       |

|------------------|-----------------------------|----------------------------------------------------------|-----------------------|------|---------|------|-------|

| SYMBOL           | PARAMETER                   | CONDITIONS                                               |                       | MIN  | TYP     | MAX  | UNITS |

| Vos              | Input Offset Voltage        |                                                          |                       |      | 2.0     | 7.0  | mV    |

| I <sub>OS</sub>  | Input Offset Current        |                                                          |                       |      | 0.2     | 1.2  | μА    |

| l <sub>B</sub>   | Input Bias Current          |                                                          |                       |      | ±0.5    | ±1.5 | μΑ    |

|                  | Input Voltage Range         | (Note 2)                                                 |                       | +2.0 |         | +3.5 | V     |

| CMRR             | Common Mode Rejection Ratio | $V_{CM} = +2.0V \text{ to } +3.5V$                       | <del> </del>          |      | 70      |      | · dB  |

| A <sub>VOL</sub> | Large Signal Voltage Gain   | $R_L = 100\Omega$ to Ground,<br>$V_0 = +1.0V$ to $+3.0V$ |                       | 6.0  | 9.0     |      | V/mV  |

| V <sub>OUT</sub> | Output Voltage Swing        | $R_L = 100\Omega$ to Ground                              | V <sub>OUT</sub> High | 3.6  | 3.8     |      | V     |

|                  |                             |                                                          | V <sub>OUT</sub> Low  |      | 0.25    | 0.4  | ]     |

| SR               | Slew Rate                   | $A_V = -1$ , $V_0 = +1V$ to $+3V$                        |                       |      | 250     |      | V/µs  |

| GBW              | Gain Bandwidth Product      |                                                          |                       |      | 80      |      | MHz   |

| Is               | Supply Current              |                                                          |                       |      | 29      | 36   | mA    |

|                  | Shutdown Supply Current     | Pin 5 at V                                               |                       |      | 1.2     | 2.0  | mA    |

| I <sub>S/D</sub> | Shutdown Pin Current        | Pin 5 at V                                               |                       |      | 20      | 50   | μА    |

# **ELECTRICAL CHARACTERISTICS** $v_8 = \pm 5V$ , $-55^{\circ}C \le T_A \le 125^{\circ}C$ , pin 5 open circuit unless otherwise noted.

| SYMBOL                   |                              | CONDITIONS                              |   | LT1191M |      |      | T     |

|--------------------------|------------------------------|-----------------------------------------|---|---------|------|------|-------|

|                          | PARAMETER                    |                                         |   | MIN     | TYP  | MAX  | UNITS |

| Vos                      | Input Offset Voltage         |                                         | • |         | 2.0  | 8.0  | mV    |

| $\Delta V_{0S}/\Delta T$ | Input V <sub>OS</sub> Drift  |                                         | • |         | 8.0  |      | μV/°C |

| los                      | Input Offset Current         |                                         | • |         | 0.2  | 2.0  | μА    |

| I <sub>B</sub>           | Input Bias Current           |                                         | • |         | ±0.5 | ±2.5 | μА    |

| CMRR                     | Common Mode Rejection Ratio  | $V_{CM} = -2.5V \text{ to } +3.5V$      | • | 55      | 70   |      | dB    |

| PSRR                     | Power Supply Rejection Ratio | $V_S = \pm 2.375V \text{ to } \pm 5.0V$ | • | 55      | 70   |      | dB    |

| A <sub>VOL</sub>         | Large Signal Voltage Gain    | $R_L = 1k, V_0 = \pm 3.0V$              | • | 16      | 32   |      | V/mV  |

|                          |                              | $R_L = 100, V_0 = \pm 3.0V$             | • | 2.0     | 5.0  |      |       |

| V <sub>OUT</sub>         | Output Voltage Swing         | R <sub>L</sub> = 1k                     | • | ±3.7    | ±3.9 |      | V     |

| Is                       | Supply Current               |                                         | • |         | 32   | 38   | mA    |

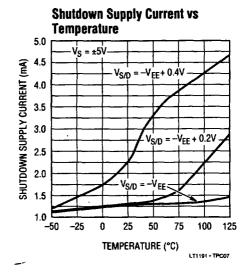

|                          | Shutdown Supply Current      | Pin 5 at V <sup>-</sup> , (Note 7)      | • |         | 1.5  | 2.5  | mA    |

| I <sub>S/D</sub>         | Shutdown Pin Current         | Pin 5 at V                              | • |         | 20   |      | μА    |

# **ELECTRICAL CHARACTERISTICS** $V_S = \pm 5V, \ 0^{\circ}C \le T_A \le 70^{\circ}C, \ pin \ 5$ open circuit unless otherwise noted.

| SYMBOL                   | PARAMETER                    | CONCITIONS                              |   | MIN  | LT11910<br>TYP | , MAX | UNITS |

|--------------------------|------------------------------|-----------------------------------------|---|------|----------------|-------|-------|

| V <sub>os</sub>          | Input Offset Voltage         |                                         | • |      | 2.0            | 6.0   | mV    |

| $\Delta V_{0S}/\Delta T$ | Input V <sub>OS</sub> Drift  |                                         | • |      | 8.0            |       | μV/°C |

| los                      | Input Offset Current         |                                         | • |      | 0.2            | 1.7   | μА    |

| l <sub>B</sub>           | Input Bias Current           |                                         | • |      | ±0.5           | ±2.5  | μА    |

| CMRR                     | Common Mode Rejection Ratio  | $V_{CM} = -2.5V \text{ to } +3.5V$      | • | 58   | 70             |       | dB    |

| PSRR                     | Power Supply Rejection Ratio | $V_S = \pm 2.375V \text{ to } \pm 5.0V$ | • | 58   | 70             |       | dB    |

| A <sub>VOL</sub>         | Large Signal Voltage Gain    | $R_L = 1k, V_0 = \pm 3.0V$              | • | 20   | 40             |       | V/mV  |

|                          |                              | $R_L = 100, V_0 = \pm 3.0V$             | • | 5.0  | 9.0            |       |       |

| V <sub>OUT</sub>         | Output Voltage Swing         | R <sub>L</sub> = 1k                     | • | ±3.7 | ±3.9           |       | V     |

| Is                       | Supply Current               |                                         | • |      | 32             | 38    | mA    |

|                          | Shutdown Supply Current      | Pin 5 at V <sup>-</sup> , (Note 7)      | • |      | 1.4            | 2.1   | mA    |

| I <sub>S/D</sub>         | Shutdown Pin Current         | Pin 5 at V                              | • |      | 20             |       | μΑ    |

The ● denotes the specifications which apply over the full operating temperature range.

**Note 1:** A heat sink is required to keep the junction temperature below absolute maximum when the output is shorted.

Note 2: Exceeding the input common mode range may cause the output to invert.

**Note 3:** Slew rate is measured between  $\pm 1V$  on the output, with a  $\pm 1.5V$  input step.

**Note 4:** Full power bandwidth is calculated from the slew rate measurement: FPBW =  $SR/2\pi Vp$ .

**Note 5:** Settling time measurement techniques are shown in "Take the Guesswork Out of Settling Time Measurements," EDN, September 19, 1985.  $A_V = -1$ ,  $R_L = 1k$ .

Note 6: NTSC (3.58MHz). For  $R_L = 1k$ , Diff  $A_V = 0.07\%$ , Diff  $Ph = 0.02^\circ$ .

**Note 7:** See Applications section for shutdown at elevated temperatures. Do not operate the shutdown above  $T_{\rm d} > 125\,^{\circ}\text{C}$ .

**Note 8**: AC parameters are 100% tested on the ceramic and plastic DIP packaged parts (J and N suffix) and are sample tested on every lot of the SO packaged parts (S suffix).

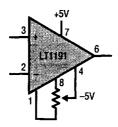

#### **Optional Offset Nulling Circuit**

INPUT OFFSET VOLTAGE CAN BE ADJUSTED OVER A  $\pm 100$ mV RANGE WITH A 1k $\Omega$  TO 10k $\Omega$  POTENTIOMETER.

LT1191 • TA03

# TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

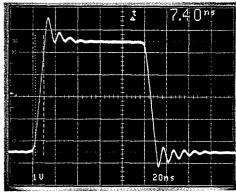

### **Large Signal Transient Response**

A<sub>V</sub> = +1, C<sub>L</sub> = 10pF SCOPE PROBE

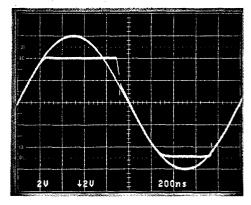

### **Output Overload**

A<sub>V</sub> = -1, V<sub>IN</sub> = 12Vp-p

LT1191 • TPC23

### **Small Signal Transient Response**

$A_V = +1$ , SMALL SIGNAL RISE TIME, WITH FET PROBES

LT1191 • TPC2

### APPLICATIONS INFORMATION

### **Power Supply Bypassing**

The LT1191 is quite tolerant of power supply bypassing. In \* some applications a 0.1µF ceramic disc capacitor placed 1/2 inch from the amplifier is all that is required. A scope photo of the amplifier output with no supply bypassing is used to demonstrate this bypassing tolerance,  $R_L = 1k\Omega$ .

### **No Supply Bypass Capacitors**

$A_V = -1$ , IN DEMO BOARD,  $R_L = 1k\Omega$

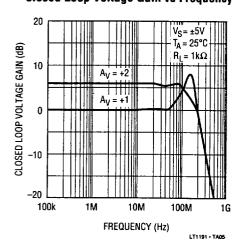

Supply bypassing can also affect the response in the frequency domain. It is possible to see a slight rise in the frequency response at 130MHz depending on the gain configuration, supply bypass, inductance in the supply leads, and printed circuit board layout. This can be further minimized by not using a socket.

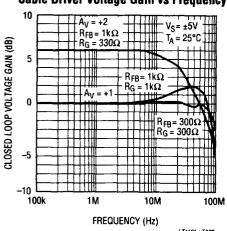

#### **Closed Loop Voltage Gain vs Frequency**

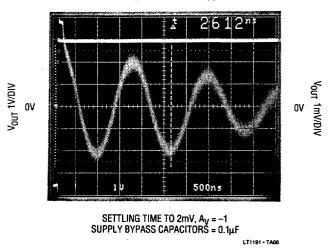

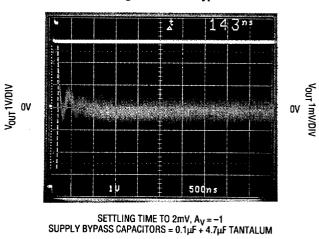

In most applications, and those requiring good settling time, it is important to use multiple bypass capacitors. A 0.1uF ceramic disc in parallel with a 4.7uF tantalum is recommended. Two oscilloscope photos with different bypass conditions are used to illustrate the settling time characteristics of the amplifier. Note that although the output waveform looks acceptable at 1V/div, when amplified to 1mV/div the settling time to 2mV is 2.61µs for the 0.1µF bypass; the time drops to 143ns with multiple bypass capacitors.

#### **Settling Time Poor Bypass**

#### **Settling Time Good Bypass**

LT1191 - TA07

### APPLICATIONS INFORMATION

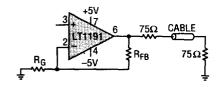

### **Cable Terminations**

The LT1191 operational amplifier has been optimized as a low cost video cable driver. The  $\pm 50$ mA guaranteed output current enables the LT1191 to easily deliver 7.5Vp-p into  $100\Omega$ , while operating on  $\pm 5$ V supplies, or 2.6Vp-p on a single 5V supply.

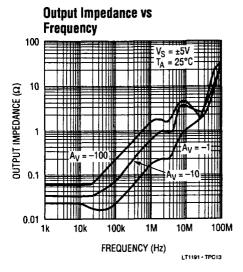

When driving a cable it is important to terminate the cable to avoid unwanted reflections. This can be done in one of two ways: single termination or double termination. With single termination, the cable must be terminated at the receiving end (75 $\Omega$  to ground) to absorb unwanted energy. The best performance can be obtained by double termination (75 $\Omega$  in series with the output of the amplifier. and 75 $\Omega$  to ground at the other end of the cable). This termination is preferred because reflected energy is absorbed at each end of the cable. When using the double termination technique it is important to note that the signal is attenuated by a factor of 2, or 6dB. This can be compensated for by taking a gain of 2, or 6dB in the amplifier. The cable driver has a -3dB bandwidth of 100MHz while driving the  $150\Omega$  load. Note the response can be improved by lowering the impedance of the feedback elements.

### **Double Terminated Cable Driver**

### Cable Driver Voltage Gain vs Frequency

### **Using the Shutdown Feature**

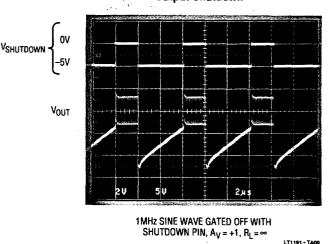

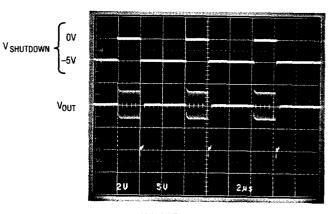

The LT1191 has a unique feature that allows the amplifier to be shutdown for conserving power, or for multiplexing several amplifiers onto a common cable. The amplifier will shutdown by taking pin 5 to V $^-$ . In shutdown, the amplifier dissipates 15mW while maintaining a true high impedance output state of 15k $\Omega$  in parallel with the feedback resistors. The amplifiers must be used in a non-inverting configuration for MUX applications. In inverting configurations the input signal is fed to the output through the feedback components. The following scope photos show that with very high  $R_L$ , the output is truly high impedance; the output slowly decays toward ground. Additionally, when the output is loaded with as little as  $1 k \Omega$  the amplifier shuts off in 400ns. This shutoff can be under the control of HC CMOS operating between 0V and -5V.

#### **Output Shutdown**

### **Output Shutdown**

1MHz SINE WAVE GATED OFF WITH SHUTDOWN PIN,  $A_V = +1$ ,  $R_L = 1 k\Omega$

LT1191 - TA10

### APPLICATIONS INFORMATION

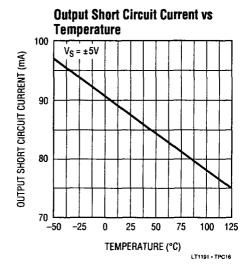

The ability to maintain shutoff is shown on the curve Shutdown Supply Current vs Temperature in the Typical Performance Characteristics section. At very high elevated temperatures it is important to hold the shutdown pin close to the negative supply to keep the supply current from increasing.

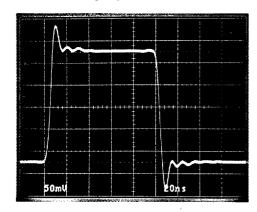

### **Murphy Circuits**

There are several precautions the user should take when using the LT1191 in order to realize its full capability. Although the LT1191 can drive a 30pF load, isolating the capacitance with  $10\Omega$  can be helpful. Precautions primarily have to do with driving large capacitive loads.

Other precautions include:

- 1. Use a ground plane (see Design Note 50, High Frequency Amplifier Evaluation Board).

- 2. Do not use high source impedances. The input capacitance of 2pF, and  $R_S$  = 10k $\Omega$  for instance, will give an 8MHz -3dB bandwidth.

- 3. PC board socket may reduce stability.

- 4. A feedback resistor of  $1k\Omega$  or lower reduces the effects of stray capacitance at the inverting input. (For instance, closed loop gain of +2 can use  $R_{FB} = 300\Omega$  and  $R_G = 300\Omega$ .)

#### **Driving Capacitive Load**

$A_V = -1$ , IN DEMO BOARD,  $C_L = 30pF$

LT1191 • TA11

#### **Driving Capacitive Load**

$A_V = -1$ , in Demo Board,  $C_L = 30$ pf with  $10\Omega$  isolating resistor

#### **Murphy Circuits**

An Unterminated Cable Is a Large Capacitive Load

A 1X Scope Probe Is a Large Capacitive Load

A Scope Probe on the Inverting Input Reduces Phase Margin

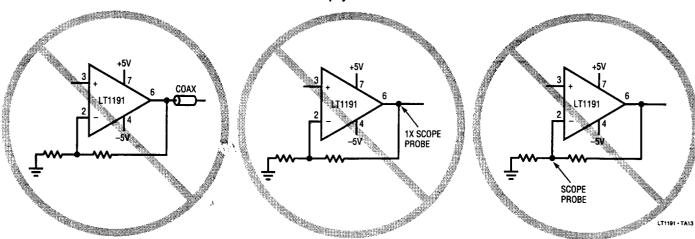

# SIMPLIFIED SCHEMATIC

\* SUBSTRATE DIODE, DO NOT FORWARD BIAS