November 1988 Revised November 1999

#### 74AC191

## **Up/Down Counter with Preset and Ripple Clock**

#### **General Description**

The AC191 is a reversible modulo 16 binary counter. It features synchronous counting and asynchronous presetting. The preset feature allows the AC191 to be used in programmable dividers. The Count Enable input, the Terminal Count output and the Ripple Clock output make possible a variety of methods of implementing multistage counters. In the counting modes, state changes are initiated by the rising edge of the clock.

#### **Features**

- I<sub>CC</sub> reduced by 50%

- High speed—133 MHz typical count frequency

- Synchronous counting

- Asynchronous parallel load

- Cascadable

- Outputs source/sink 24 mA

#### **Ordering Code:**

| Order Number | Package Number | Package Description                                                               |

|--------------|----------------|-----------------------------------------------------------------------------------|

| 74AC191SC    | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Body |

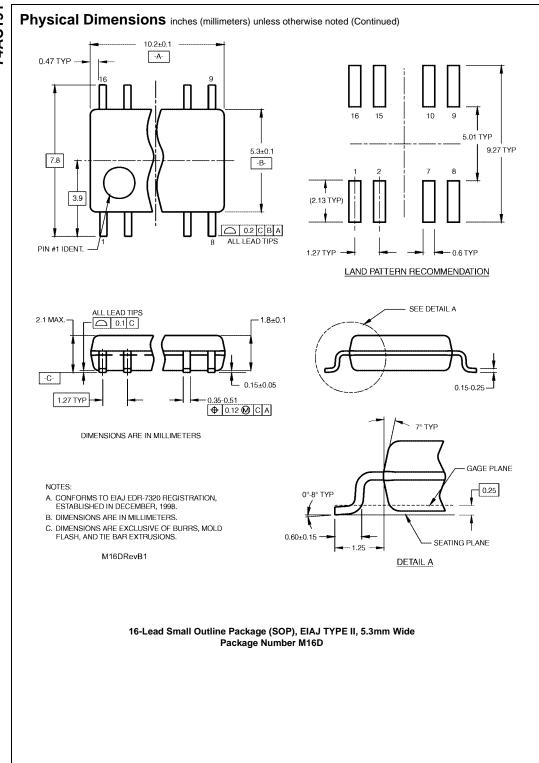

| 74AC191SJ    | M16D           | 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide                     |

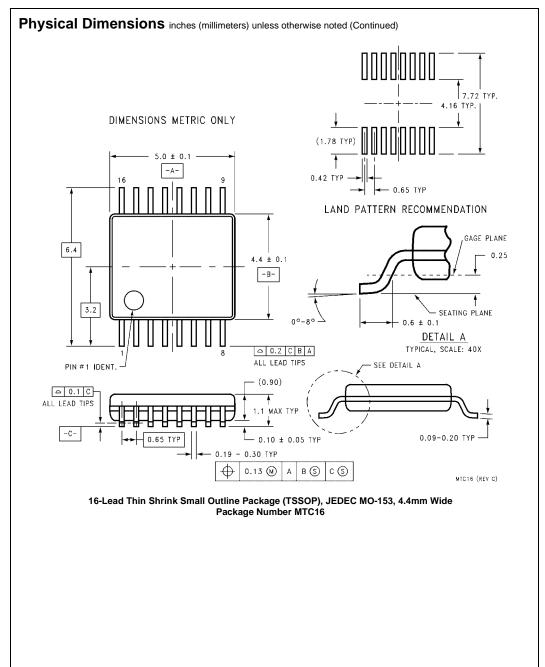

| 74AC191MTC   | MTC16          | 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide       |

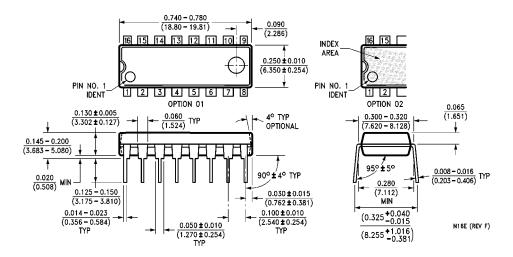

| 74AC191PC    | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide            |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

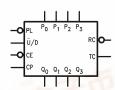

### **Logic Symbols**

#### **Connection Diagram**

#### **Pin Descriptions**

| Pin Names                      | Description                      |  |  |  |  |

|--------------------------------|----------------------------------|--|--|--|--|

| CE                             | Count Enable Input               |  |  |  |  |

| CP                             | Clock Pulse Input                |  |  |  |  |

| P <sub>0</sub> -P <sub>3</sub> | Parallel Data Inputs             |  |  |  |  |

| PL                             | Asynchronous Parallel Load Input |  |  |  |  |

| Ū /D                           | Up/Down Count Control Input      |  |  |  |  |

| Q <sub>0</sub> –Q <sub>3</sub> | Flip-Flop Outputs                |  |  |  |  |

| RC                             | Ripple Clock Output              |  |  |  |  |

| TC                             | Terminal Count Output            |  |  |  |  |

|                                |                                  |  |  |  |  |

FACT™ is a trademark of Fairchild Semiconductor Corporation.

#### **RC Truth Table**

|    | Inputs |                |    |    |  |  |  |

|----|--------|----------------|----|----|--|--|--|

| PL | CE     | TC<br>(Note 1) | СР | RC |  |  |  |

| Н  | L      | Н              | ъ  | 7- |  |  |  |

| Н  | Н      | Х              | Х  | Н  |  |  |  |

| Н  | Х      | L              | Х  | Н  |  |  |  |

| L  | Х      | Х              | Х  | Н  |  |  |  |

H = HIGH Voltage Level L = LOW Voltage Level

L = LOW Voltage X = Immaterial

X = Immaterial

∠ = LOW-to-HIGH Transition

¬∟r = Clock Pulse

Note 1: TC is generated internally

#### **Functional Description**

The AC191 is a synchronous up/down counter. The AC191 is organized as a 4-bit binary counter. It contains four edge-triggered flip-flops with internal gating and steering logic to provide individual preset, count-up and count-down operations.

Each circuit has an asynchronous parallel load capability permitting the counter to be preset to any desired number. When the Parallel Load (PL) input is LOW, information present on the Parallel Load inputs ( $P_0$ – $P_3$ ) is loaded into the counter and appears on the Q outputs. This operation overrides the counting functions, as indicated in the Mode Select Table.

A HIGH signal on the  $\overline{\text{CE}}$  input inhibits counting. When  $\overline{\text{CE}}$  is LOW, internal state changes are initiated synchronously by the LOW-to-HIGH transition of the clock input. The direction of counting is determined by the  $\overline{\text{U}}/\text{D}$  input signal, as indicated in the Mode Select Table.  $\overline{\text{CE}}$  and  $\overline{\text{U}}/\text{D}$  can be changed with the clock in either state, provided only that the recommended setup and hold times are observed.

Two types of outputs are provided as overflow/underflow indicators. The terminal count (TC) output is normally LOW. It goes HIGH when the circuits reach zero in the count down mode or 15 in the count up mode. The TC output will then remain HIGH until a state change occurs, whether by counting or presetting or until  $\overline{\rm U}/{\rm D}$  is changed. The TC output should not be used as a clock signal because it is subject to decoding spikes.

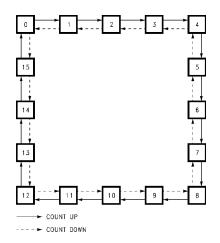

The TC signal is also used internally to enable the Ripple Clock  $(\overline{RC})$  output. The  $\overline{RC}$  output is normally HIGH. When CE is LOW and TC is HIGH, RC output will go LOW when the clock next goes LOW and will stay LOW until the clock goes HIGH again. This feature simplifies the design of multistage counters, as indicated in Figure 1 and Figure 2. In Figure 1, each RC output is used as the clock input for the next higher stage. This configuration is particularly advantageous when the clock source has a limited drive capability, since it drives only the first stage. To prevent counting in all stages it is only  $\underline{\text{necessary}}$  to  $\underline{\text{in\underline{hib}}}$  it the first stage, since a HIGH signal on  $\overline{\text{CE}}$  inhibits the  $\overline{\text{RC}}$  output pulse, as indicated in the RC Truth Table. A disadvantage of this configuration, in some applications, is the timing skew between state changes in the first and last stages. This represents the cumulative delay of the clock as it ripples through the

A method of causing state changes to occur simultaneously in all stages is shown in Figure 2. All clock inputs are driven in parallel and the  $\overline{\text{RC}}$  outputs propagate the carry/borrow signals in ripple fashion. In this configuration the LOW state duration of the clock must be long enough to allow the negative-going edge of the carry/borrow signal to

ripple through to the last stage before the clock goes HIGH. There is no such restriction on the HIGH state duration of the clock, since the  $\overline{RC}$  output of any device goes HIGH shortly after its CP input goes HIGH.

The configuration shown in Figure 3 avoids ripple delays and their associated restrictions. The  $\overline{CE}$  input for a given stage is formed by combining the TC signals from all the preceding stages. Note that in order to inhibit counting an enable signal must be included in each carry gate. The simple inhibit scheme of Figure 1 and Figure 2 doesn't apply, because the TC output of a given stage is not affected by its own  $\overline{CE}$ .

#### **Mode Select Table**

|   |    | Inj | outs | Mode |                  |

|---|----|-----|------|------|------------------|

| i | PL | CE  | U/D  | СР   |                  |

|   | Н  | L   | L    | ~    | Count Up         |

|   | Н  | L   | Н    | ~    | Count Down       |

|   | L  | Х   | Х    | Х    | Preset (Asyn.)   |

|   | Н  | Н   | X    | Х    | No Change (Hold) |

#### **State Diagram**

#### Absolute Maximum Ratings(Note 2)

# Recommended Operating Conditions

DC Input Voltage ( $V_I$ ) -0.5V to  $V_{CC} + 0.5V$

DC Output Diode Current  $(I_{OK})$

DC Output Voltage ( $V_O$ ) -0.5V to  $V_{CC} + 0.5V$

DC Output Source

or Sink Current ( $I_O$ )  $\pm 50$  mA

DC V<sub>CC</sub> or Ground Current

per Output Pin ( $I_{CC}$  or  $I_{GND}$ )  $\pm 50 \text{ mA}$

Storage Temperature ( $T_{STG}$ )  $-65^{\circ}C$  to  $+150^{\circ}C$

Junction Temperature (T<sub>J</sub>)

PDIP 140°C

Minimum Input Edge Rate ( $\Delta V/\Delta t$ )

$V_{\mbox{\footnotesize{IN}}}$  from 30% to 70% of  $V_{\mbox{\footnotesize{CC}}}$

$V_{CC} @ 3.3V 4.5V, 5.5V$  125 mV/ns

Note 2: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, output/input loading variables. Fairchild does not recommend operation of FACT<sup>TML</sup> circuits outside databook specifica-

#### **DC Electrical Characteristics**

| Symbol           | Parameter               | V <sub>cc</sub> | $V_{CC}$ $T_A = +25^{\circ}C$ |      | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | Units  | Conditions                         |  |

|------------------|-------------------------|-----------------|-------------------------------|------|-----------------------------------------------|--------|------------------------------------|--|

| Cymbol           | r arameter              | (V)             | Тур                           | Gu   | aranteed Limits                               | Oilles | Conditions                         |  |

| V <sub>IH</sub>  | Minimum HIGH Level      | 3.0             | 1.5                           | 2.1  | 2.1                                           |        | V <sub>OUT</sub> = 0.1V            |  |

|                  | Input Voltage           | 4.5             | 2.25                          | 3.15 | 3.15                                          | V      | or V <sub>CC</sub> – 0.1V          |  |

|                  |                         | 5.5             | 2.75                          | 3.85 | 3.85                                          |        |                                    |  |

| V <sub>IL</sub>  | Maximum LOW Level       | 3.0             | 1.5                           | 0.9  | 0.9                                           |        | V <sub>OUT</sub> = 0.1V            |  |

|                  | Input Voltage           | 4.5             | 2.25                          | 1.35 | 1.35                                          | V      | or V <sub>CC</sub> – 0.1V          |  |

|                  |                         | 5.5             | 2.75                          | 1.65 | 1.65                                          |        |                                    |  |

| V <sub>OH</sub>  | Minimum HIGH Level      | 3.0             | 2.99                          | 2.9  | 2.9                                           |        |                                    |  |

|                  | Output Voltage          | 4.5             | 4.49                          | 4.4  | 4.4                                           | V      | $I_{OUT} = -50 \mu A$              |  |

|                  |                         | 5.5             | 5.49                          | 5.4  | 5.4                                           |        |                                    |  |

|                  |                         | 3.0             |                               | 2.56 | 2.46                                          |        | $V_{IN} = V_{IL}$ or $V_{IH}$      |  |

|                  |                         | 4.5             |                               | 3.86 | 3.76                                          | V      | $I_{OH}$ $-12$ mA                  |  |

|                  |                         | 5.5             |                               | 4.86 | 4.76                                          |        | $I_{OH} = -24 \text{ mA}$          |  |

|                  |                         |                 |                               |      |                                               |        | I <sub>OH</sub> .= -24 mA (Note 3) |  |

| V <sub>OL</sub>  | Maximum LOW Level       | 3.0             | 0.002                         | 0.1  | 0.1                                           |        |                                    |  |

|                  | Output Voltage          | 4.5             | 0.001                         | 0.1  | 0.1                                           | V      | $I_{OUT} = 50 \mu A$               |  |

|                  |                         | 5.5             | 0.001                         | 0.1  | 0.1                                           |        |                                    |  |

|                  |                         | 3.0             |                               | 0.36 | 0.44                                          |        | $V_{IN} = V_{IL}$ or $V_{IH}$      |  |

|                  |                         | 4.5             |                               | 0.36 | 0.44                                          | V      | $I_{OL} = 12 \text{ mA}$           |  |

|                  |                         | 5.5             |                               | 0.36 | 0.44                                          |        | $I_{OL} = 24 \text{ mA}$           |  |

|                  |                         |                 |                               |      |                                               |        | I <sub>OL</sub> = 24 mA (Note 3)   |  |

| I <sub>IN</sub>  | Maximum Input           | 5.5             |                               | ±0.1 | ±1.0                                          | μА     | $V_I = V_{CC}$ , GND               |  |

| (Note 5)         | Leakage Current         | 5.5             |                               | ±0.1 | ±1.0                                          | μΑ     | VI = VCC, GIVD                     |  |

| I <sub>OLD</sub> | Minimum Dynamic         | 5.5             |                               |      | 75                                            | mA     | V <sub>OLD</sub> = 1.65V Max       |  |

| I <sub>OHD</sub> | Output Current (Note 4) | 5.5             |                               |      | -75                                           | mA     | V <sub>OHD</sub> = 3.85V Min       |  |

| I <sub>CC</sub>  | Maximum Quiescent       | 5.5             |                               | 4.0  | 40.0                                          | μА     | $V_{IN} = V_{CC}$                  |  |

| (Note 5)         | Supply Current          | 0.0             |                               |      | .5.0                                          | per t  | or GND                             |  |

Note 3: All outputs loaded; thresholds on input associated with output under test.

Note 4: Maximum test duration 2.0 ms, one output loaded at a time.

Note 5:  $I_{\rm IN}$  and  $I_{\rm CC}$  @ 3.0V are guaranteed to be less than or equal to the respective limit @ 5.5V  $V_{\rm CC}$ .

## **AC Electrical Characteristics**

|                  |                      | V <sub>cc</sub> |                                                   | C <sub>L</sub> = 50 pF |      | T <sub>A</sub> = -40°  | C to +85°C |       |

|------------------|----------------------|-----------------|---------------------------------------------------|------------------------|------|------------------------|------------|-------|

| Symbol           | Parameter            | (V)             | $\textbf{T}_{\textbf{A}} = +25^{\circ}\textbf{C}$ |                        |      | C <sub>L</sub> = 50 pF |            | Units |

|                  |                      | (Note 6)        | Min                                               | Тур                    | Max  | Min                    | Max        |       |

| f <sub>MAX</sub> | Maximum Count        | 3.3             | 70                                                | 105                    |      | 65                     |            |       |

|                  | Frequency            | 5.0             | 90                                                | 133                    |      | 85                     |            | MHz   |

| t <sub>PLH</sub> | Propagation Delay    | 3.3             | 2.0                                               | 8.5                    | 15.0 | 1.5                    | 16.0       |       |

|                  | CP to Q <sub>n</sub> | 5.0             | 1.5                                               | 6.0                    | 11.0 | 1.5                    | 12.0       | ns    |

| t <sub>PHL</sub> | Propagation Delay    | 3.3             | 2.5                                               | 8.5                    | 14.5 | 2.0                    | 16.0       |       |

|                  | CP to Q <sub>n</sub> | 5.0             | 1.5                                               | 6.0                    | 10.5 | 1.5                    | 11.5       | ns    |

| t <sub>PLH</sub> | Propagation Delay    | 3.3             | 3.5                                               | 10.5                   | 18.0 | 2.5                    | 20.0       |       |

|                  | CP to TC             | 5.0             | 2.5                                               | 7.5                    | 12.0 | 1.5                    | 14.0       | ns    |

| t <sub>PHL</sub> | Propagation Delay    | 3.3             | 4.0                                               | 10.5                   | 17.5 | 3.0                    | 19.0       |       |

|                  | CP to TC             | 5.0             | 2.5                                               | 7.5                    | 12.5 | 2.0                    | 13.5       | ns    |

| t <sub>PLH</sub> | Propagation Delay    | 3.3             | 2.5                                               | 7.5                    | 12.0 | 2.0                    | 13.5       |       |

|                  | CP to RC             | 5.0             | 2.0                                               | 5.5                    | 9.5  | 1.0                    | 10.5       | ns    |

| t <sub>PHL</sub> | Propagation Delay    | 3.3             | 2.5                                               | 7.0                    | 11.5 | 2.0                    | 12.5       |       |

|                  | CP to RC             | 5.0             | 1.5                                               | 5.0                    | 8.5  | 1.0                    | 9.5        | ns    |

| t <sub>PLH</sub> | Propagation Delay    | 3.3             | 2.5                                               | 7.0                    | 12.0 | 1.5                    | 13.5       |       |

|                  | CE to RC             | 5.0             | 1.5                                               | 5.0                    | 8.5  | 1.0                    | 9.5        | ns    |

| t <sub>PHL</sub> | Propagation Delay    | 3.3             | 2.0                                               | 6.5                    | 11.0 | 1.5                    | 12.5       | ns    |

|                  | CE to RC             | 5.0             | 1.5                                               | 5.0                    | 8.0  | 1.0                    | 9.0        |       |

| t <sub>PLH</sub> | Propagation Delay    | 3.3             | 2.5                                               | 6.5                    | 12.5 | 2.0                    | 14.5       |       |

|                  | U /D to RC           | 5.0             | 1.5                                               | 5.0                    | 9.0  | 1.0                    | 10.0       | ns    |

| t <sub>PHL</sub> | Propagation Delay    | 3.3             | 2.5                                               | 7.0                    | 12.0 | 2.0                    | 13.5       |       |

|                  | U /D to RC           | 5.0             | 1.5                                               | 5.0                    | 8.5  | 1.0                    | 10.0       | ns    |

| t <sub>PLH</sub> | Propagation Delay    | 3.3             | 2.0                                               | 7.0                    | 11.5 | 1.5                    | 13.5       | ns    |

|                  | U /D to TC           | 5.0             | 1.5                                               | 5.0                    | 8.5  | 1.0                    | 9.5        | 115   |

| t <sub>PHL</sub> | Propagation Delay    | 3.3             | 2.0                                               | 6.5                    | 11.0 | 1.5                    | 12.5       | ns    |

|                  | U /D to TC           | 5.0             | 1.5                                               | 5.0                    | 8.5  | 1.0                    | 9.5        | 115   |

| t <sub>PLH</sub> | Propagation Delay    | 3.3             | 2.5                                               | 8.0                    | 13.5 | 2.0                    | 15.5       | ns    |

|                  | $P_n$ to $Q_n$       | 5.0             | 2.0                                               | 5.5                    | 9.5  | 1.0                    | 10.5       | 115   |

| t <sub>PHL</sub> | Propagation Delay    | 3.3             | 2.5                                               | 7.5                    | 13.0 | 1.5                    | 14.5       | ns    |

|                  | $P_n$ to $Q_n$       | 5.0             | 1.5                                               | 5.5                    | 9.5  | 1.0                    | 10.5       | 113   |

| t <sub>PLH</sub> | Propagation Delay    | 3.3             | 3.5                                               | 9.5                    | 14.5 | 2.5                    | 17.5       | ne    |

|                  | PL to Q <sub>n</sub> | 5.0             | 2.0                                               | 5.5                    | 9.5  | 1.0                    | 10.5       | ns    |

| t <sub>PHL</sub> | Propagation Delay    | 3.3             | 3.0                                               | 8.0                    | 13.5 | 2.0                    | 15.5       | ns    |

|                  | PL to Q <sub>n</sub> | 5.0             | 2.0                                               | 6.0                    | 10.0 | 1.5                    | 11.0       |       |

Note 6: Voltage Range 3.3 is  $3.3V \pm 0.3V$ Voltage Range 5.0 is  $5.0V \pm 0.5V$

## **AC Operating Requirements**

|                  |                          | v <sub>cc</sub> | <b>T</b> <sub>A</sub> = - | +25°C | T <sub>A</sub> = -40°C to +85°C |       |  |

|------------------|--------------------------|-----------------|---------------------------|-------|---------------------------------|-------|--|

| Symbol           | Parameter                | (V)             | $C_L = 50 pF$             |       | C <sub>L</sub> = 50 pF          | Units |  |

|                  |                          | (Note 7)        | Тур                       | Gua   | ranteed Minimum                 |       |  |

| t <sub>S</sub>   | Setup Time, HIGH or LOW  | 3.3             | 1.0                       | 3.0   | 3.0                             | ns    |  |

|                  | P <sub>n</sub> to PL     | 5.0             | 0.5                       | 2.0   | 2.5                             | 115   |  |

| t <sub>H</sub>   | Hold Time, HIGH or LOW   | 3.3             | -1.5                      | 0.5   | 1.0                             |       |  |

|                  | $P_n$ to $\overline{PL}$ | 5.0             | -0.5                      | 1.0   | 1.0                             | ns    |  |

| t <sub>S</sub>   | Setup Time, LOW          | 3.3             | 3.0                       | 6.0   | 7.0                             |       |  |

|                  | CE to CP                 | 5.0             | 1.5                       | 4.0   | 4.5                             | ns    |  |

| t <sub>H</sub>   | Hold Time, LOW           | 3.3             | -4.0                      | -0.5  | -0.5                            | no    |  |

|                  | CE to CP                 | 5.0             | .0                        | ns    |                                 |       |  |

| t <sub>S</sub>   | Setup Time, HIGH or LOW  | 3.3             | 4.0                       | 8.0   | 9.0                             |       |  |

|                  | Ū/D to CP                | 5.0             | 2.5                       | 5.5   | 6.5                             | ns    |  |

| t <sub>H</sub>   | Hold Time, HIGH or LOW   | 3.3             | -5.0                      | 0     | 0                               |       |  |

|                  | U/D to CP                | 5.0             | -3.0                      | 0.5   | 0.5                             | ns    |  |

| t <sub>W</sub>   | PL Pulse Width, LOW      | 3.3             | 2.0                       | 3.5   | 4.0                             |       |  |

|                  |                          | 5.0             | 1.0                       | 1.0   | 1.0                             | ns    |  |

| t <sub>W</sub>   | CP Pulse Width, LOW      | 3.3             | 2.0                       | 3.5   | 4.0                             |       |  |

|                  |                          | 5.0             | 2.0                       | 3.0   | 4.0                             | ns    |  |

| t <sub>rec</sub> | Recovery Time            | 3.3             | -0.5                      | 0     | 0                               |       |  |

|                  | PL to CP                 | 5.0             | -1.0                      | 0     | 0                               | ns    |  |

Note 7: Voltage Range 3.3 is 3.3V ± 0.3V Voltage Range 5.0 is 5.0V ± 0.5V

## Capacitance

| Symbol          | Parameter                     | Тур  | Units | Conditions             |

|-----------------|-------------------------------|------|-------|------------------------|

| C <sub>IN</sub> | Input Capacitance             | 4.5  | pF    | V <sub>CC</sub> = OPEN |

| C <sub>PD</sub> | Power Dissipation Capacitance | 75.0 | pF    | V <sub>CC</sub> = 5.0V |

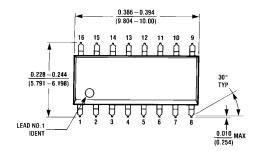

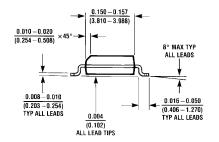

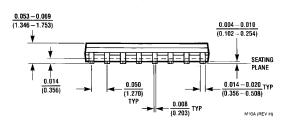

## Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Body Package Number M16A

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com