# HM530281R Series

331,776-word  $\times$  8-bit Frame Memory

# HITACHI

ADE-203-251B Rev. 1.0 June 6, 1997

### Description

The HM530281R series memory products provide completely asynchronous I/O and operate at the high speed of 50 MHz. The HM530281R series memory products provide reset, jump, and line increment/hold pointer control functions that can be used in synchronization with independent clocks on each of the I/O ports. Memory can be accessed immediately without any waiting period after the execution of these functions. In addition to the FIFO function, the 281R series products support an address structure that is compatible with HDTV, NTSC, and PAL standards, and can be used in a wide range of applications, such as noise reducers, TBC (time-based correction), inter-frame YC separation, and special function modes (e.g., multi-freeze, P-in-P) in the digital TV, VCR, and video camera application. They are also appropriate for use as inter-system speed conversion buffer memories in communications systems, as cache memories of HDD and MOD, and as frame buffer of VGA.

#### Features

- Organization: 331,776-word × 8-bit

- Completely asynchronous operation of the serial read port and write port.

- Internal generation of read and write addresses

- Internal memory operation control provided on-chip

- High speed read/write cycle time: 50 MHz

- Reset, jump functions

- Independent execution for read and write ports

- Can be executed with arbitrary timing

- Allow immediate access after execution (read/write) (for the jump function, when the address setup is complete)

- Jump address specifiable in 32-word units

- 2 dimensional address

- Line increment/hold address pointer control function

- Window scan function

- Can handle HDTV, NTSC, and PAL standards

- Line length: Up to 1152 bits (Arbitrary line lengths can also be handled by using the line reset function.)

- Line count: Up to 324 lines

- Built-in self-refresh eliminates the need for external refresh control.

- Power supply voltage:  $V_{cc} = 5.0 \text{ V} \pm 10\%$ .

### **Ordering Information**

| Type No.       | Cycle Time | Memory Organization                          | Package                |

|----------------|------------|----------------------------------------------|------------------------|

| HM530281RTT-20 | 20 ns      | 331,776 words × 8 bits <sup>-2</sup>         | 44-pin TSOP (TTP-44DB) |

| HM530281RTT-25 | 25 ns      | 1152 dots × 288 lines × 8 bits <sup>-3</sup> |                        |

| HM530281RTT-34 | 34 ns      | 1024 dots $\times$ 324 lines $\times$ 8 bits |                        |

| HM530281RTT-45 | 45 ns      |                                              |                        |

Notes: 1. Selectable following two kinds of addressing mode by mode pins

- 2. 1 dimensional addressing mode

- 3. 2 dimensional addressing mode

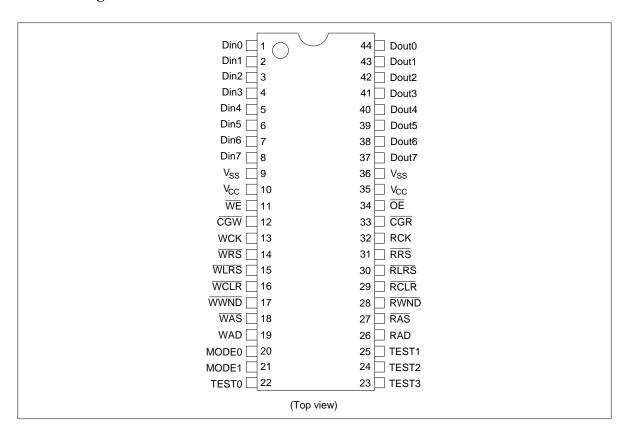

### **Pin Arrangement**

# **Pin Description**

### **Functions**

| Symbol          | 2 dimensional address | 1 dimensional address  |

|-----------------|-----------------------|------------------------|

| Din0 to Din7    | Data input            | Data input             |

| Dout0 to Dout7  | Data output           | Data output            |

| WCK             | Write clock           | Write clock            |

| RCK             | Read clock            | Read clock             |

| WRS             | Write reset           | Write reset            |

| RRS             | Read reset            | Read reset             |

| WE              | Write enable          | Write enable           |

| ŌĒ              | Output enable         | Output enable          |

| CGW             | Write clock gate      | Write clock gate       |

| CGR             | Read clock gate       | Read clock gate        |

| WAS             | Write address set     | Write address set      |

| WAD             | Write address         | Write address          |

| RAS             | Read address set      | Read address set       |

| RAD             | Read address          | Read address           |

| WLRS            | Write line reset      | V <sub>cc</sub> or GND |

| RLRS            | Read line reset       | V <sub>∞</sub> or GND  |

| WWND            | Write window mode     | V <sub>∞</sub> or GND  |

| RWND            | Read window mode      | V <sub>cc</sub> or GND |

| WCLR            | Write clear           | V <sub>∞</sub> or GND  |

| RCLR            | Read clear            | V <sub>∞</sub> or GND  |

| MODE 0 to 1     | Mode selection input  | Mode selection input   |

| V <sub>cc</sub> | Power supply          | Power supply           |

| V <sub>ss</sub> | Ground                | Ground                 |

| TEST0 to TEST3  | Connect to ground     | Connect to ground      |

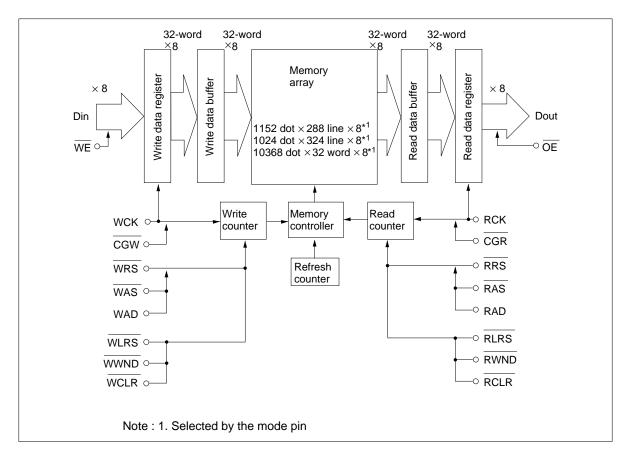

### **Block Diagram**

### **Absolute Maximum Ratings**

| Parameter                         | Symbol         | Value        | Unit |  |

|-----------------------------------|----------------|--------------|------|--|

| Pin voltage <sup>*1</sup>         | V <sub>T</sub> | -1.0 to +7.0 | V    |  |

| Power dissipation                 | P <sub>T</sub> | 1.0          | W    |  |

| Operating temperature             | Topr           | 0 to +70     | °C   |  |

| Storage temperature               | Tstg           | -55 to +125  | °C   |  |

| Storage temperature (when biased) | Tbias          | -10 to +85   | °C   |  |

Note: 1. The permissible values with respect to  $V_{ss}$ .

### **Recommended DC Operating Conditions** (Ta = $0 \text{ to } +70^{\circ}\text{C}$ )

| Parameter            | Symbol          | Min                | Тур | Max | Unit |  |

|----------------------|-----------------|--------------------|-----|-----|------|--|

| Power supply voltage | V <sub>cc</sub> | 4.5                | 5   | 5.5 | V    |  |

|                      | V <sub>ss</sub> | 0                  | 0   | 0   | V    |  |

| Input voltages       | V <sub>IH</sub> | 2.7                |     | 6.5 | V    |  |

|                      | V <sub>IL</sub> | -0.5 <sup>*1</sup> | _   | 0.6 | V    |  |

Note: 1. When the pulse width is under 10 ns,  $V_{\perp}$  min = -3.0 V.

# **DC Characteristics** ( $V_{cc} = 5.0 \text{ V} \pm 10\%$ , $V_{ss} = 0 \text{ V}$ , $Ta = 0 \text{ to } +70^{\circ}\text{C}$ )

|                                       |                  | HM5 | 3028 <sup>2</sup> | 1-20 | HM5 | 3028 | 1-25 | HM5 | 3028 <sup>2</sup> | 1-34 | HM5 | 30281 | 1-45 |      | Test                                                                                                   |

|---------------------------------------|------------------|-----|-------------------|------|-----|------|------|-----|-------------------|------|-----|-------|------|------|--------------------------------------------------------------------------------------------------------|

| Parameter                             | Symbol           | Min | Тур               | Max  | Min | Тур  | Max  | Min | Тур               | Max  | Min | Тур   | Max  | Unit | Conditions                                                                                             |

| Operating power supply current        | I <sub>CCA</sub> | _   | 110               | 135  | _   | 90   | 120  | _   | 70                | 95   | _   | 55    | 75   | mA   | $\begin{aligned} &\text{lout} = 0, \\ &t_{\text{WCC}} = t_{\text{RCC}} = \\ &\text{Min} \end{aligned}$ |

| Standby<br>power<br>supply<br>current | I <sub>ccs</sub> | _   | 15                | 25   | _   | 15   | 25   | _   | 15                | 25   | _   | 15    | 25   | mA   | V <sub>cc</sub> = 5.5 V<br>WCK, RCK =<br>"L" fix                                                       |

| Input<br>leakage<br>current           | I <sub>LI</sub>  | -10 | _                 | 10   | -10 | _    | 10   | -10 | _                 | 10   | -10 |       | 10   | mA   | $V_{CC} = 5.5 \text{ V},$ $Vin = V_{SS} \text{ to}$ $V_{CC}$                                           |

| Output<br>leakage<br>current          | I <sub>LO</sub>  | -10 | _                 | 10   | -10 |      | 10   | -10 | _                 | 10   | -10 | _     | 10   | mA   | OE = Vin  Vout = Vss to  Vcc                                                                           |

| Output voltages                       | V <sub>oL</sub>  |     | _                 | 0.4  | _   |      | 0.4  |     |                   | 0.4  | _   | _     | 0.4  | V    | I <sub>OL</sub> = 2.1 mA                                                                               |

|                                       | V <sub>OH</sub>  | 2.4 | _                 | _    | 2.4 |      | _    | 2.4 | _                 | _    | 2.4 | _     | _    | V    | $I_{OH} = -1.0 \text{ mA}$                                                                             |

### Capacitance\*1

| Parameter          | Symbol | Тур | Max | Units | Test<br>Conditions |

|--------------------|--------|-----|-----|-------|--------------------|

| Input capacitance  | Cin    | _   | 5   | pF    | Vin = 0 V          |

| Output capacitance | Cout   | _   | 7   | pF    | Vout = 0 V         |

Note: 1. These parameters are sampled values, not values measured for all units.

### **AC Characteristics**

### **Test Conditions**

$\bullet \quad \text{Input pulse level: } V_{ss} \text{ to } 3.0 \text{ V}$

• Input rise/fall time: 3 ns

• I/O timing reference level: 1.5 V

• Output load: 1 TTL + 50 pF (including jig and scope capacitances)

|                                |                  | HM5302 | 281R-20 | HM530 | 281R-25 | HM530 | 281R-34 | HM530 | 281R-45 |      |

|--------------------------------|------------------|--------|---------|-------|---------|-------|---------|-------|---------|------|

| Parameter                      | Symbol           | Min    | Max     | Min   | Max     | Min   | Max     | Min   | Max     | Unit |

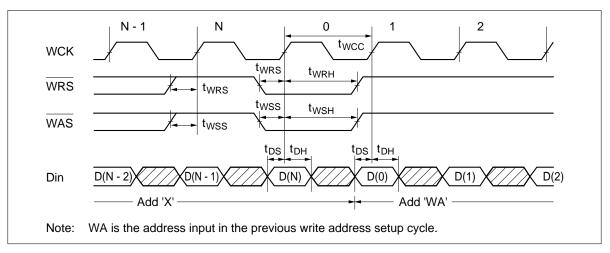

| Write clock cycle time         | t <sub>wcc</sub> | 20     | _       | 25    | _       | 34    | _       | 45    | _       | ns   |

| Write clock pulse width (high) | t <sub>wc</sub>  | 8      | _       | 10    | _       | 12    | _       | 15    | _       | ns   |

| Write clock pulse width (low)  | twcp             | 8      | _       | 10    | _       | 12    | _       | 15    | _       | ns   |

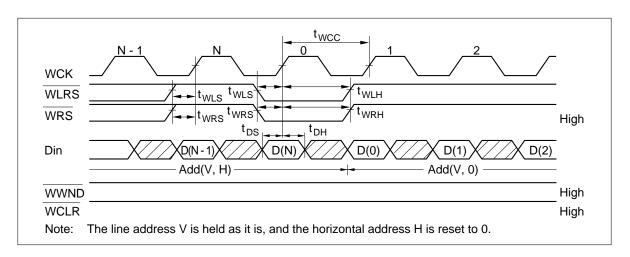

| WRS setup time                 | t <sub>wrs</sub> | 7      | _       | 8     | _       | 10    | _       | 10    | _       | ns   |

| WRS hold time                  | t <sub>wrh</sub> | 7      | _       | 8     | _       | 10    | _       | 10    | _       | ns   |

| Data input setup time          | t <sub>DS</sub>  | 5      | _       | 5     | _       | 5     | _       | 5     | _       | ns   |

| Data input hold time           | t <sub>DH</sub>  | 6      | _       | 6     | _       | 6     | _       | 6     | _       | ns   |

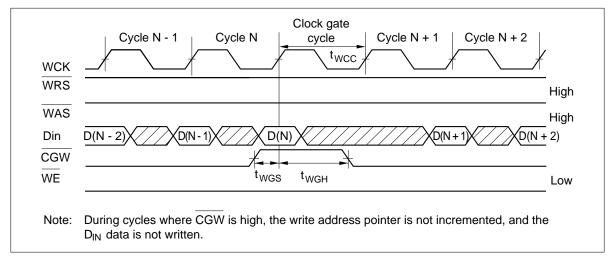

| CGW setup time                 | t <sub>wgs</sub> | 7      | _       | 8     |         | 10    | _       | 10    | _       | ns   |

| CGW hold time                  | t <sub>wgH</sub> | 7      | _       | 8     | _       | 10    | _       | 10    | _       | ns   |

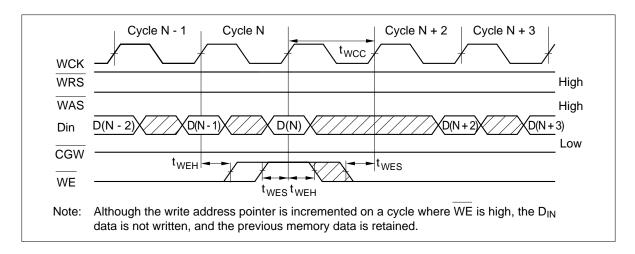

| WE setup time                  | t <sub>wes</sub> | 5      | _       | 5     | _       | 5     | _       | 5     | _       | ns   |

| WE hold time                   | t <sub>weh</sub> | 6      | _       | 6     |         | 6     | _       | 6     | _       | ns   |

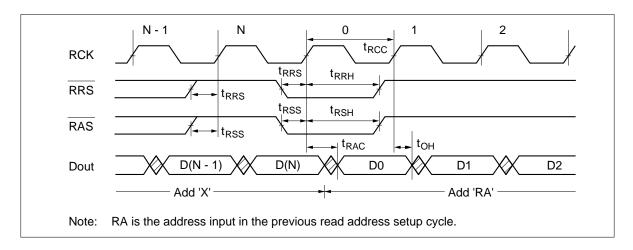

| Read clock cycle time          | t <sub>RCC</sub> | 20     | _       | 25    | _       | 34    | _       | 45    | _       | ns   |

| Read clock pulse width (high)  | t <sub>RC</sub>  | 8      | _       | 10    | _       | 12    | _       | 15    | _       | ns   |

| Read clock pulse width (low)   | t <sub>RCP</sub> | 8      | _       | 10    |         | 12    | _       | 15    |         | ns   |

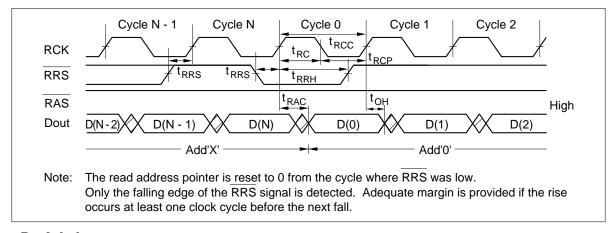

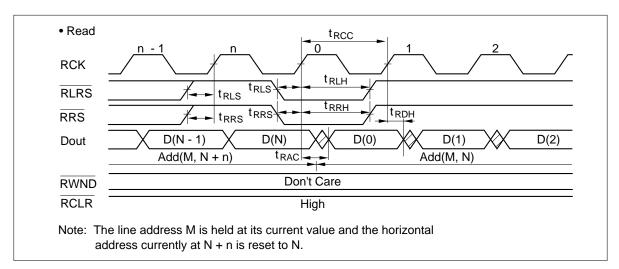

| RRS setup time                 | t <sub>rrs</sub> | 7      | _       | 8     | _       | 10    | _       | 10    | _       | ns   |

| RRS hold time                  | t <sub>rrh</sub> | 7      | _       | 8     | _       | 10    | _       | 10    | _       | ns   |

| Access time from RCK           | t <sub>RAC</sub> | _      | 18      | _     | 23      | _     | 25      | _     | 30      | ns   |

| Output hold time               | t <sub>oh</sub>  | 6      | _       | 6     | _       | 6     | _       | 6     | _       | ns   |

| Output enable time             | t <sub>oLZ</sub> | 0      | _       | 0     | _       | 0     | _       | 0     | _       | ns   |

| Output enable access time      | toAC             | _      | 18      | _     | 20      | _     | 25      | _     | 25      | ns   |

| Output disable time            | t <sub>oHZ</sub> | 0      | 15      | 0     | 18      | 0     | 20      | 0     | 20      | ns   |

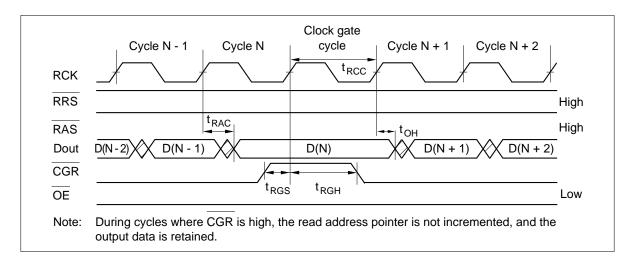

| CGR setup time                 | t <sub>RGS</sub> | 7      | _       | 8     |         | 10    | _       | 10    | _       | ns   |

| CGR hold time                  | t <sub>RGH</sub> | 7      | _       | 8     | _       | 10    | _       | 10    | _       | ns   |

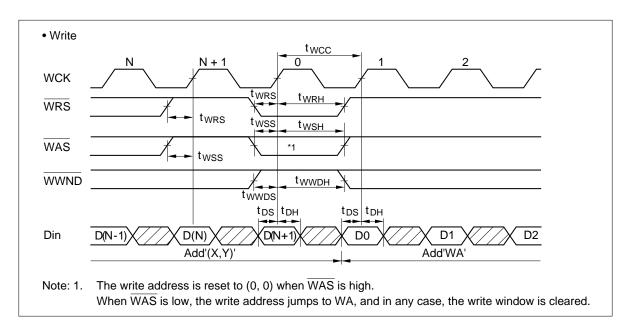

| WAS setup time                 | t <sub>wss</sub> | 7      | _       | 8     | _       | 10    | _       | 10    | _       | ns   |

| WAS hold time                  | t <sub>wsh</sub> | 7      | _       | 8     | _       | 10    | _       | 10    | _       | ns   |

# AC Characteristics (cont)

| HM530281R-20 | HM530281R-25 | HM530281R-34 | HM530281R-45 |

|--------------|--------------|--------------|--------------|

|              |              |              |              |

| Parameter                      | Symbol            | Min | Max | Min | Max | Min | Max | Min | Max | Unit |

|--------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| RAS setup time                 | t <sub>rss</sub>  | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| RAS hold time                  | t <sub>RSH</sub>  | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| Write address input setup time | t <sub>was</sub>  | 5   | _   | 5   | _   | 5   | _   | 5   | _   | ns   |

| Write address input hold time  | t <sub>wah</sub>  | 6   | _   | 6   | _   | 6   | _   | 6   | _   | ns   |

| Read address input setup time  | t <sub>RAS</sub>  | 5   | _   | 5   | _   | 5   | _   | 5   | _   | ns   |

| Read address input hold time   | t <sub>RAH</sub>  | 6   | _   | 6   | _   | 6   | _   | 6   | _   | ns   |

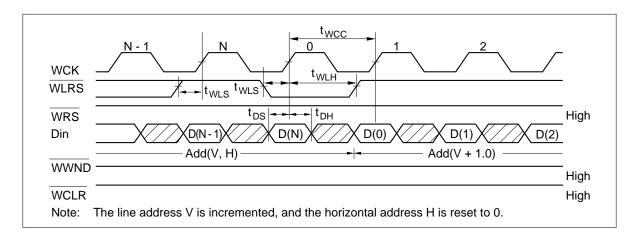

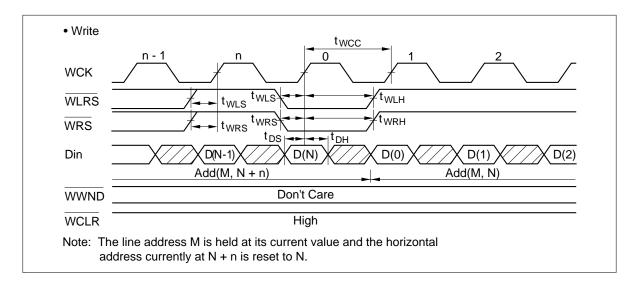

| WLRS setup time                | t <sub>wLS</sub>  | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| WLRS hold time                 | t <sub>wLH</sub>  | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

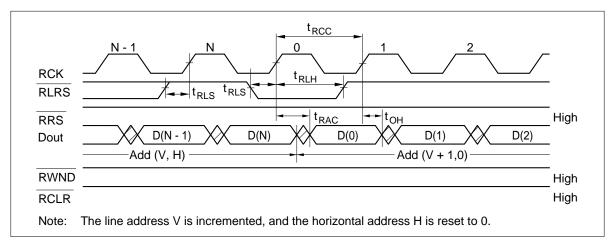

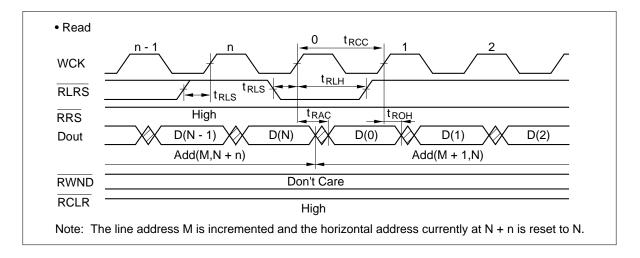

| RLRS setup time                | t <sub>RLS</sub>  | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| RLRS hold time                 | t <sub>rlh</sub>  | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| WCLR setup time                | twcls             | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| WCLR hold time                 | twclh             | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| RCLR setup time                | t <sub>RCLS</sub> | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| RCLR hold time                 | t <sub>RCLH</sub> | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| WWND setup time                | t <sub>wwDs</sub> | 7   | _   | 8   |     | 10  |     | 10  | _   | ns   |

| WWND hold time                 | t <sub>wwdh</sub> | 7   | _   | 8   | _   | 10  | _   | 10  | _   | ns   |

| RWND setup time                | t <sub>RWDS</sub> | 7   | _   | 8   | _   | 10  |     | 10  | _   | ns   |

| RWND hold time                 | t <sub>RWDH</sub> | 7   |     | 8   |     | 10  |     | 10  |     | ns   |

### **Input and Output Pin Functions**

$D_{IN}$ 0 to  $D_{IN}$ 7 (data input) Input: The  $D_{IN}$  pins input 8 bits of data. Data is input on the rising edge of the cycle of WCK that follows a low level on both  $\overline{CGW}$  and  $\overline{WE}$ .

$D_{out}$ 0 to  $D_{out}$ 7 (data output) Output: The  $D_{out}$  pins output 8 bits of data. Data output is synchronized with the RCK clock, and the access time is specified from the rising edge of the RCK cycle.

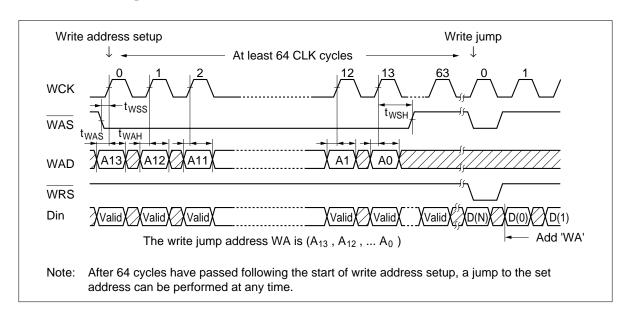

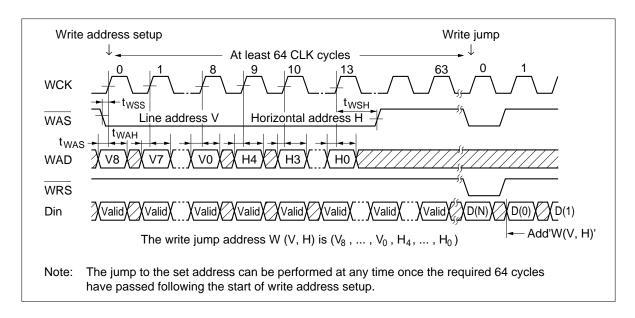

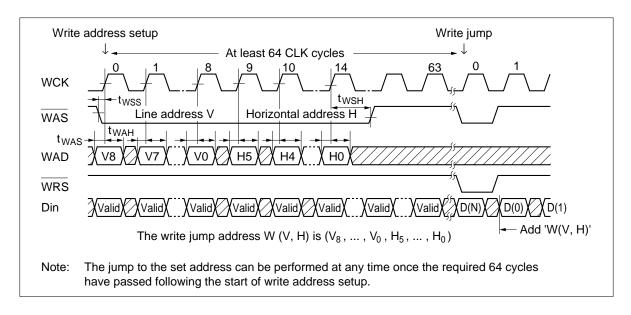

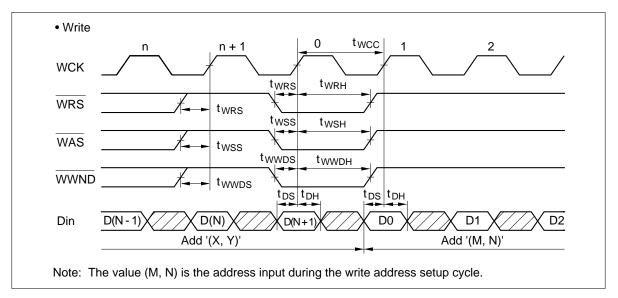

WCK (write clock) Input: WCK is the write clock input pin. The input of write data is synchronized with this clock. Write data is input on the rising edge of the cycle of WCK that follows a low level on both  $\overline{CGW}$  and  $\overline{WE}$ , and when  $\overline{CGW}$  is low, the internal write address pointer is incremented at the same time. Input of the write jump address is also synchronized with this clock. The 14 bits or 15 bits of the write jump address are read in sequentially from the WCK cycle that set  $\overline{WAS}$  low, irrespective of write data acquisition.

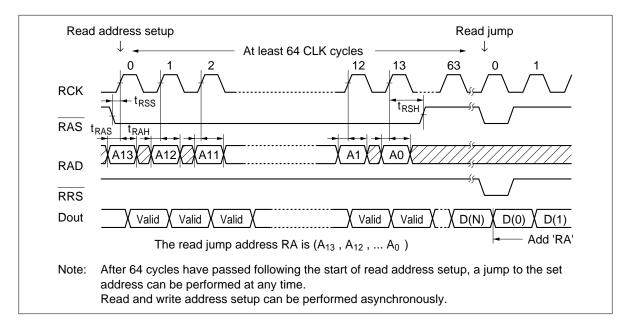

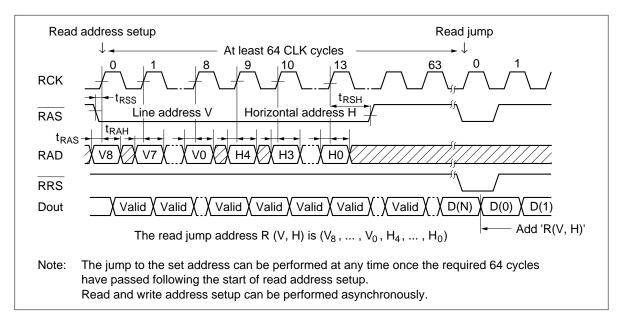

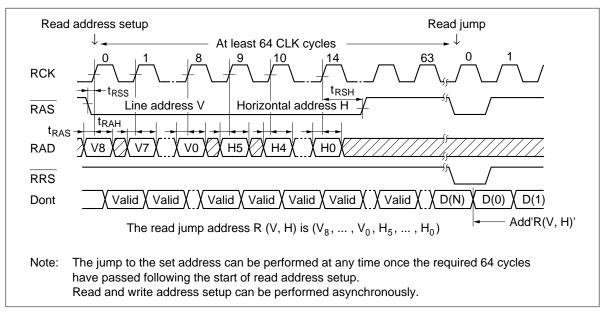

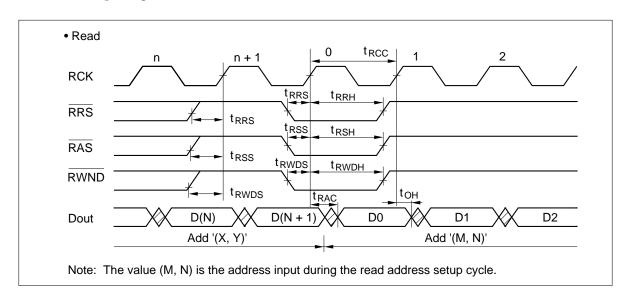

**RCK** (**read clock**) **Input:** RCK is the read clock input pin. Read data is output in synchronization with this clock when both  $\overline{CGR}$  and  $\overline{OE}$  are low, and when  $\overline{CGR}$  is low, the internal read address pointer is incremented at the same time. Input of the read jump address is also synchronized with this clock. The read jump address is read in sequentially starting at the RCK cycle in which  $\overline{RAS}$  was set low, independently of read data output.

$\overline{WRS}$  (write address pointer reset) Input:  $\overline{WRS}$  is a reset signal input that resets the write address pointer to 0 when  $\overline{WAS}$  and  $\overline{WLRS}$  are high, resets to the head of the line currently being written when  $\overline{WAS}$  is high and  $\overline{WLRS}$  is low, and jumps to the preset write jump address when  $\overline{WAS}$  is low. \*1 Only the falling edge of this reset input is detected, and, on the first WCK cycle following that falling edge, a write cycle to the set address is started immediately.

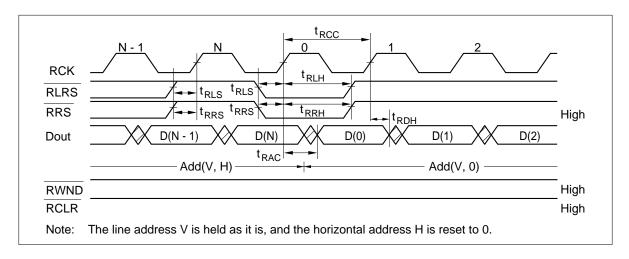

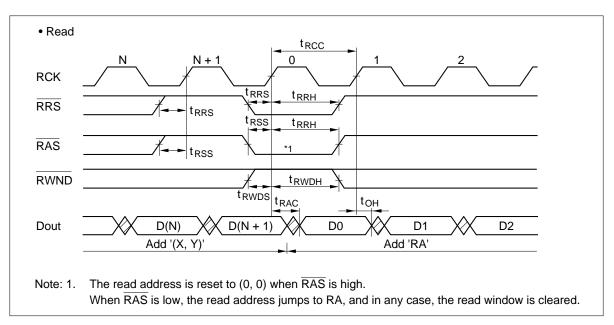

$\overline{RRS}$  (read address pointer reset) Input:  $\overline{RRS}$  is a reset signal input that resets the read address pointer to 0 when  $\overline{RAS}$  and  $\overline{RLRS}$  are high, resets to the start of the line currently being read when  $\overline{RAS}$  is high and  $\overline{RLRS}$  is low, and jumps to the read jump address when  $\overline{RAS}$  is low.\*1 Only the falling edge of this reset input is detected, and, on the first RCK cycle following that falling edge, a read cycle at the set address is started immediately.

$\overline{\text{WE}}$  (write enable) Input:  $\overline{\text{WE}}$  is an input signal that controls the enabling/disabling of the data input pins. When  $\overline{\text{WE}}$  is low, input data is acquired on the WCK cycle, and when  $\overline{\text{WE}}$  is high, data input is disabled and the previous memory data is maintained. Note that the write address pointer is incremented by the WCK write clock without regard for the level of  $\overline{\text{WE}}$ .

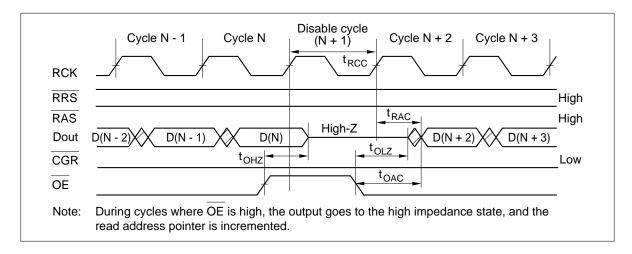

$\overline{OE}$  (output enable) Input:  $\overline{OE}$  is an input signal that enables/disables the data output pins. When  $\overline{OE}$  is low, data output is enabled, and when high, data output is disabled and the output pins go to the high impedance state. Note that the read address pointer is incremented by the RCK read clock without regard for the level of  $\overline{OE}$ . Therefore, data can be jumped over during read simply by disabling output with  $\overline{OE}$ .

$\overline{\text{CGW}}$  (clock gate for write) Input:  $\overline{\text{CGW}}$  is an input signal that enables/disables incrementing of the internal write address pointer. When  $\overline{\text{CGW}}$  is low, the write address pointer is incremented in synchronization with the WCK write clock, and when high, incrementing is stopped. Therefore time axis compression can be easily implemented without stopping the write clock by using  $\overline{\text{CGW}}$ .

$\overline{\text{CGR}}$  (clock gate for read) Input:  $\overline{\text{CGR}}$  is an input signal that enables/disables incrementing of the internal read address pointer. When  $\overline{\text{CGR}}$  is low, the read address pointer is incremented in synchronization with the RCK read clock, and when high, incrementing is stopped. Therefore time axis expansion can be easily implemented without stopping the read clock by using  $\overline{\text{CGR}}$ .

$\overline{\text{WAS}}$  (write address set and jump) Input:  $\overline{\text{WAS}}$  is an input signal that initiates write jump address input when  $\overline{\text{WRS}}$  is high and jumps to the previously input write jump address when  $\overline{\text{WRS}}$  is low. The falling edge of this input signal is detected, and either a write jump address input is initiated or a jump to the previously input write jump address is executed on the first WCK cycle following the fall of  $\overline{\text{WAS}}$ .

WAD (write jump address) Input: WAD is the input pin for the write jump address. The 14/15 bits of the write jump address are read in sequentially from the high order bit, starting at the WCK cycle (when  $\overline{\text{WRS}}$  was high) in which  $\overline{\text{WAS}}$  was set low.\*2

$\overline{RAS}$  (read address set and jump) Input:  $\overline{RAS}$  is an input signal that initiates read jump address input when  $\overline{RRS}$  is high and jumps to the previously input read jump address when  $\overline{RRS}$  is low. The falling edge of this input signal is detected, and either the read jump address input is initiated or the jump to the previously input read jump address is executed on the first WCK cycle following the fall on  $\overline{RAS}$ .

RAD (read jump address) Input: RAD is the input pin for the read jump address. The 14/15 bits of the write jump address are read in sequentially from the high order bit, starting at the RCK cycle (when  $\overline{RRS}$  was high) in which  $\overline{RAS}$  was set low.\*2

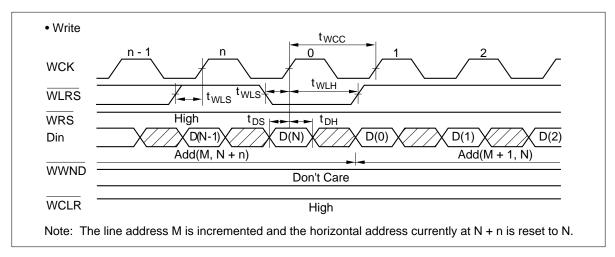

$\overline{\text{WLRS}}$  (write line reset) Input (in 2 dimensional addressing mode):  $\overline{\text{WLRS}}$  is an input pin for resetting the write address pointer to the start of the line from an arbitrary dot for each line.\*3 Only the falling edge of this signal is detected, and, on the first WCK cycle following that falling edge, the write address pointer is set to the head of the next line when  $\overline{\text{WRS}}$  is high, and to head of the current line when  $\overline{\text{WRS}}$  is low.\*3

$\overline{RLRS}$  (read line reset) Input (in 2 dimensional addressing mode):  $\overline{RLRS}$  is an input pin for resetting the read address pointer to the start of the line from an arbitrary dot for each line.\*3 Only the falling edge of this signal is detected, and, on the first  $\overline{RCK}$  cycle following that falling edge, the write address pointer is set to the head of the next line when  $\overline{RRS}$  is high, and to head of the current line when  $\overline{RRS}$  is low.\*3

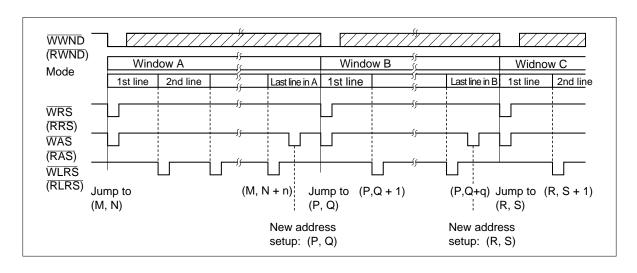

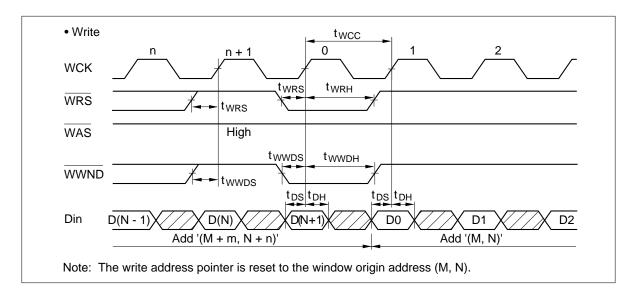

$\overline{\text{WWND}}$  (write window scan) Input (in 2 dimensional addressing mode):  $\overline{\text{WWND}}$  is an input signal that specifies the use of the window scan function. When executing a write jump with  $\overline{\text{WRS}}$  and  $\overline{\text{WAS}}$  low, if  $\overline{\text{WWND}}$  is set low at the same time, a scan of the window region that takes that write jump address as its starting point will begin (see note below).

$\overline{\text{RWND}}$  (read window scan) Input (in 2 dimensional addressing mode):  $\overline{\text{RWND}}$  is an input signal that specifies the use of the window scan function. when executing a read jump with  $\overline{\text{RRS}}$  and  $\overline{\text{RAS}}$  low, if  $\overline{\text{RWND}}$  is set low at the same time, a scan of the window region that takes that read jump address as its starting point will begin.\*4

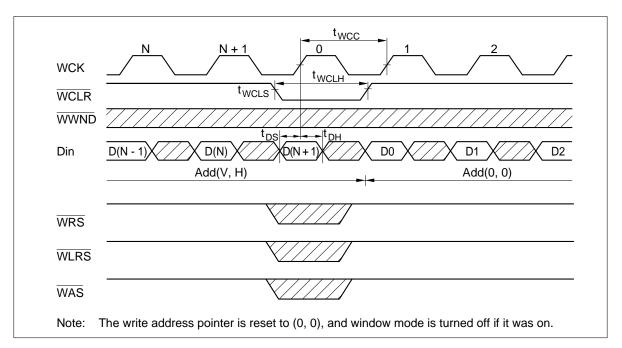

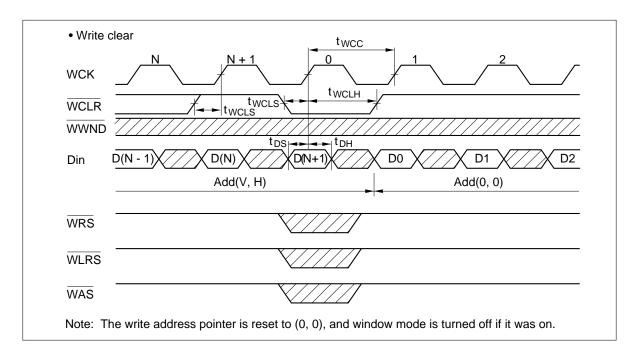

$\overline{\text{WCLR}}$  (write clear) Input:  $\overline{\text{WCLR}}$  is an input signal that, independently of the levels on  $\overline{\text{WRS}}$ ,  $\overline{\text{WAS}}$ ,  $\overline{\text{WLRS}}$  and  $\overline{\text{WWND}}$  resets the write address pointer to 0 and clears the window scan function. This function is executed immediately in the WCK cycle in which  $\overline{\text{WCLR}}$  was set low. This clear operation should also be performed after applying power to the HM530281R.

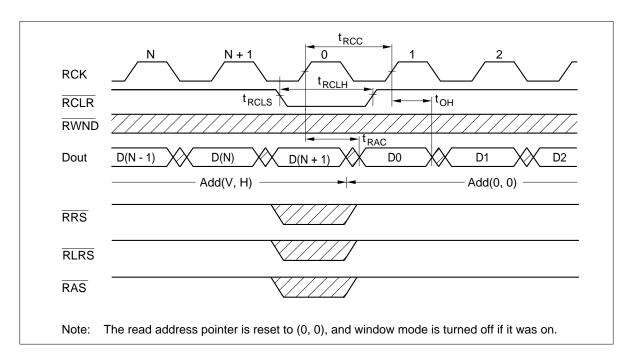

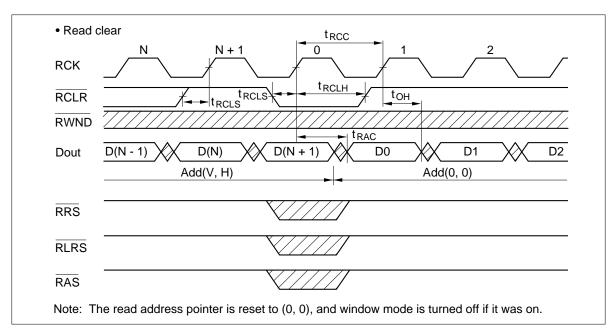

$\overline{RCLR}$  (read clear) Input:  $\overline{RCLR}$  is an input signal that, independently of the levels on  $\overline{RRS}$ ,  $\overline{RAS}$ ,  $\overline{RLRS}$  and  $\overline{RWND}$  resets the read address pointer to 0 and clears the window scan function. This function is executed immediately in the RCK cycle in which  $\overline{RCLR}$  was set low. This clear operation should also be performed after applying power to the HM530281R.

Notes: 1. The reset destination in window scan mode changes as follows.

Reset to 0: Reset to the window start.

Reset to line start: Reset to the point at the left edge of the window for the line

2.

| Addressing Mode    | Address Structure                           | Input Address                                                                                                 |

|--------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1 dim. add. (FIFO) | 0 to 10,367 blocks                          | Address bits A <sub>13</sub> to A <sub>0</sub>                                                                |

| 2 dim. add. (1)    | 32 horizontal blocks by 324 vertical lines  | Line address bits V <sub>8</sub> to V <sub>0</sub> , horizontal address bits H <sub>4</sub> to H <sub>0</sub> |

| 2 dim. add. (2)    | 36 horizontal blocks by 288 vertical lines. | Line address bits V <sub>8</sub> to V <sub>0</sub> , horizontal address bits H <sub>5</sub> to H <sub>0</sub> |

- 3. When window scan mode is set, the reset is to the point at the left edge of the window for the line.

- 4. When window scan is set, the horizontal address of the pointer reset destination when increment/hold is executed will be the left edge of the window. Also, when a reset is executed, the pointer will be reset to the starting point of the window.

Thus it is possible to scan arbitrary window regions within the screen independently for read and write by using these line reset and reset functions.

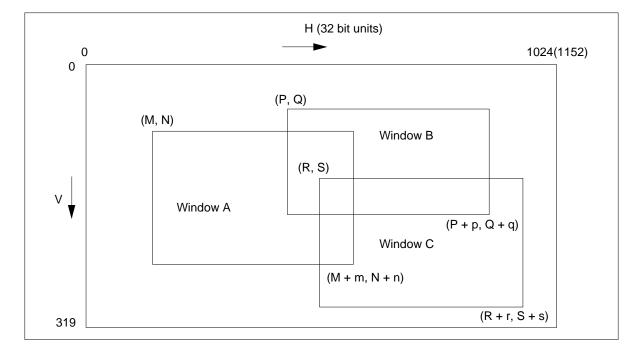

### **Memory Structure**

The memory is organized as 331,776-word of 8-bit each, and these words can be accessed sequentially, since the address pointer can be incremented by inputting a clock signal. Addresses are allocated corresponding to 32 word blocks.

The mode pins switch between the three addressing modes shown below.

| Mode 0 | Mode 1 | Addressing Mode    | Address Structure                          | Capacity               |

|--------|--------|--------------------|--------------------------------------------|------------------------|

| 0      | 0      | 1 dim. add. (FIFO) | 0 to 10,367 blocks                         | 331,776 words          |

| 1      | 0      | 2 dim. add. (1)    | 32 horizontal blocks by 324 vertical lines | 1024 dots by 324 lines |

| 0      | 1      | 2 dim. add. (2)    | 36 horizontal blocks by 288 vertical lines | 1152 dots by 288 lines |

Notes: 1. In 1 dimensional addressing mode, blocks 0 to 10367 are accessed cyclically.

2. In the 2 dimensional addressing modes, the line head can be reset at an arbitrary dot on each line.

### **Operations**

#### Write

**Write operation:** When the  $\overline{WE}$  and  $\overline{CGW}$  inputs are low, 8 bits of write data are input in synchronization with the WCK clock. The input data is read in to the word indicated by the address pointer on the next rising edge of the WCK cycle. This allows read data and write data to be handled with the same clock, and cascade connections to be easily implemented.

Write reset operations: When  $\overline{CGW}$  is low, by setting  $\overline{WRS}$  low, the write address pointer can be set immediately on that  $\overline{WCK}$  cycle to the address 0 block head. This operation can be executed independently of the input level of  $\overline{WE}$ . (See 'Notes on usage' 15 on the operation when  $\overline{CGW}$  is high.)

Write address pointer increment operations: The write address pointer is incremented in synchronization with WCK when  $\overline{CGW}$  is low. It is possible to apply a write mask in WCK clock units by setting the  $\overline{WE}$  input high. In this case, the previous memory data will be retained. The write address pointer increment function can be stopped by setting the  $\overline{CGW}$  input high. This allows time axis compression to be implemented easily. (See 'Notes on usage' 7, 9 and 10 for interval specifications of write system reset operations.\*1)

Note: 1. The write system reset operation stands for write reset, write jump, write window reset, write line reset and write clear.

#### $\overline{ m WE}$ and $\overline{ m CGW}$ Input Level, Write Address Pointer, and Data Input State Relationship

### **WCK Rising Edge**

| CGW | WE | Internal Write Address Pointer | Data Input                        |

|-----|----|--------------------------------|-----------------------------------|

| L   | L  | Incremented                    | enable                            |

| L   | Н  |                                | disable (memory data is retained) |

| Н   | _  | Stopped                        |                                   |

Note: Data is input when the  $\overline{WE}$  input is low.

#### Read

**Read operation:** 8 bits of read data are output in synchronization with the RCK clock when the  $\overline{OE}$  and  $\overline{CGR}$  inputs are low. The access time is stipulated from the rising edge of the RCK clock.

**Read reset operations:** When  $\overline{CGR}$  is low, by setting  $\overline{RRS}$  low, the read address pointer can be set immediately on that RCK cycle to address 0 and the data will then be output. This operation can be performed independently of the input level of  $\overline{OE}$ . (See 'Notes on usage' 14 on the operation when  $\overline{CGR}$  is high.)

**Read address pointer increment operations:** The read address pointer is incremented in synchronization with RCK when  $\overline{\text{CGR}}$  is low. Data outputs go to the high impedance state when the  $\overline{\text{OE}}$  input is set high. The reset address pointer increment function can be stopped by setting the  $\overline{\text{CGR}}$  input high. This allows time axis expansion to be implemented easily. (See 'Notes on usage' 7, 8 and 10 for interval specifications of read system reset operations.\*2)

Note: 2. The read system reset operations stands for read reset, read jump, read window reset, read line reset and read clear.

# Relation Between the $\overline{OE}$ and $\overline{CGR}$ Input Levels and the Read Address Pointer and Data Output States

#### **RCK Rising Edge**

| CGR | ŌĒ | Internal Read Address Pointer | Data Output      |

|-----|----|-------------------------------|------------------|

| L   | L  | Incremented                   | Output           |

| L   | Н  |                               | High impedance   |

| Н   | L  | Stopped                       | Output data held |

| Н   | Н  |                               | High impedance   |

Note: Data is input when the  $\overline{OE}$  input is low.

#### Line Reset (write line reset and read line reset, in 2 dimensional addressing modes)

When the 281R series products are used in 2 dimensional addressing modes, the line length can be set to be either 1024 dots (2 dimensional (1)) or 1152 dots (2 dimensional (2)). In these modes, after accessing the

data at the last dot (address) on each line, address pointer incrementing is stopped. Access is restarted at either the first dot at the head of the next line or at the first dot at the head of the current line by executing either a line increment or a line hold, respectively. Also, since these line reset operations can be executed at any arbitrary point in the middle of a line, an arbitrary line length (of between 64 dots and the actual line length) can be realized.

**Line increment operation:** In case clock gate signal  $(\overline{CGW}, \overline{CGR})$  is low, the read and write line increment operations are executed by setting  $\overline{RLRS}$  low and  $\overline{RRS}$  high, and setting  $\overline{WLRS}$  low and  $\overline{WRS}$  high respectively. When these operations are executed, the next access goes immediately to the starting dot of the next line.

Line hold operation: In case clock gate signal ( $\overline{CGW}$ ,  $\overline{CGR}$ ) is low, the read and write line hold operations are executed by setting  $\overline{RLRS}$  and  $\overline{RRS}$  low, and setting  $\overline{WLRS}$  and  $\overline{WRS}$  low respectively. When these operations are executed, the next access goes immediately to the starting dot of the current line. Note that the read line hold operation is invalid on the first line following a 0 reset or jump. In this case, the same effect can be achieved by re-executing the reset or jump operation (resetting only the H address to 0). If the reset interval specifications are met (see Notes on Usage 1 to 3), the line reset operation can be performed on an arbitrary RCK/WCK clock cycle without regard for the levels of the  $\overline{OE}$  and  $\overline{WE}$  inputs. (See 'Notes on usage' 15 and 16 on the operation when clock gate signal  $(\overline{CGW}, \overline{CGR})$  is high.)

#### Jump (independent functions for read and write)

It is possible to set the address pointer to the start address of an arbitrary block in 32 word units. After initializing a jump address setup for read and/or write, after 64 WCK or 64 RCK cycles, it is possible to execute a jump to that address (random access in 32 word by 8 bit units) independently for read and write. (See 'Notes on usage' 12 on the jump operation to '0' address and line end address.)

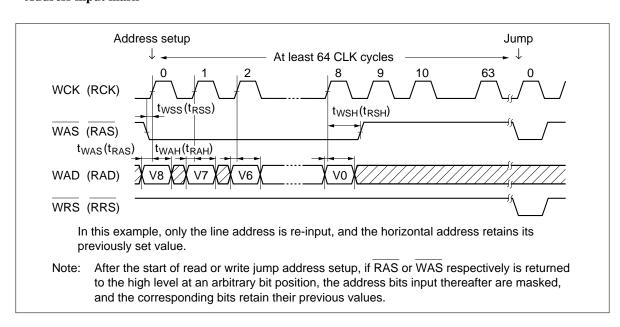

**Jump address setup:** The read and write jump addresses are serially input independently from the RAD and WAD pins in synchronization with the RCK and WCK clock inputs respectively. Address input start is enabled by setting the  $\overline{RAS}$  and/or  $\overline{WAS}$  inputs low for read and write respectively, and 14/15 bits of jump address are input sequentially starting with that cycle.\*<sup>10</sup> Note that the read and write operations can continue independently of this address input operation. Jump address setup is executed regardless of  $\overline{WE}$ ,  $\overline{CGW}$  and  $\overline{OE}$ ,  $\overline{CGR}$ . Following the start of address input, it is possible to mask the input of address bits below an arbitrary bit position by returning  $\overline{RAS}$  or  $\overline{WAS}$  to the high level at the desired bit position. This can be convenient in applications that need to jump a fixed interval, since the low order bits of the address will be fixed. When all 14 bits of an address are to be input, be sure to hold  $\overline{RAS}$  and  $\overline{WAS}$  low for the full 14-clock period.

Jump operation: In case clock gate signal  $(\overline{CGW}, \overline{CGR})$  is 'L', the jump operation is executed by setting  $\overline{RRS}$  and  $\overline{RAS}$  low for read, and by setting  $\overline{WRS}$  and  $\overline{WAS}$  low for write, and the address set is accessed immediately from that RCK or WCK cycle. Note that as long as the interval specifications listed in Notes 7 to 9 are met, the jump operation can be executed on any RCK or WCK cycle without regard for the values of  $\overline{OE}$  and  $\overline{WE}$ . (See 'Notes on usage' 14 and 15 on the operation, when clock gate signal  $(\overline{CGW}, \overline{CGR})$  is high.)

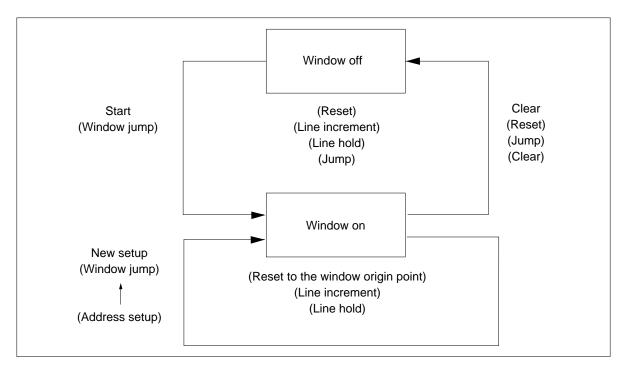

#### Window Scan (independent functions for read and write)

The window scan function can be used with either the 2 dimensional (1) or (2) addressing modes, and is a function which scans a rectangular region with an arbitrary starting point. The jump address setup function (see Jump address setup above) is used to specify the starting point

**Initiating window scan:** The window scan function is started by setting  $\overline{WWND}$  to low for read or  $\overline{RWND}$  low for write, and executing a read or write jump operation (see Jump operation above). Window scan will start immediately from that cycle.

**Window scan operation:** When the window scan function is started, one of the functions described below will be executed independently for read and write.\*<sup>11</sup> Also note that as long as the interval conditions listed in Notes 7 to 9 are met, these operations can be executed at arbitrary dots without regard for the address block organization.

Clearing window scan: The window scan function is turned off either by executing a reset or jump with  $\overline{RWND}$  (for read) or  $\overline{WWND}$  (for write) set high, or by executing the clear operation described in section Clear below. Note that both setting and clearing window scan mode are executed independently of  $\overline{OE}$  and  $\overline{WE}$ .

(See 'Notes on usage' 14 and 15 on the operation when clock gate signal ( $\overline{\text{CGW}}$ ,  $\overline{\text{CGR}}$ ) is high.)

| Operation      | Address Pointer Control                                                    |

|----------------|----------------------------------------------------------------------------|

| Reset          | Reset to the first dot at the start of the window.                         |

| Line increment | Reset to the first dot at the left edge of the window on the next line.    |

| Line hold      | Reset to the first dot at the left edge of the window on the current line. |

#### Overview of the window scan operation:

### Clear (independent functions for read and write)

The clear function both resets the address pointer to 0 without regard for the value on  $\overline{WRS}$ ,  $\overline{WAS}$ ,  $\overline{WLRS}$ ,  $\overline{WWND}$ ,  $\overline{RRS}$ ,  $\overline{RAS}$ ,  $\overline{RLRS}$  and  $\overline{RWND}$ , and if window mode is set, clears window mode.

**Clear Operation:** When clock gate signal  $(\overline{CGW}, \overline{CGR})$  is low, the clear operation can be executed on any cycle by setting the  $\overline{RCLR}$  pin low for read and the  $\overline{WCLR}$  pin low for write. When the interval conditions listed in Notes on usage 7 to 10 are met, clear operation is executed at any time without regard of the level on  $\overline{WE}$  and  $\overline{OE}$ . (See 'Notes on usage' 14 and 15 on the operation when clock gate signal  $(\overline{CGW}, \overline{CGR})$  is high)

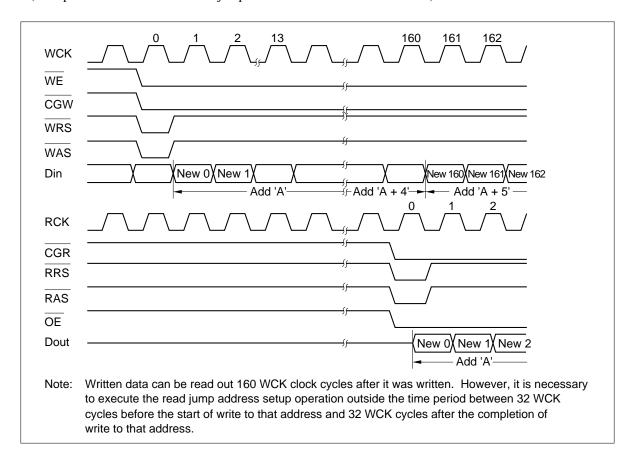

#### **Access of New and Previous Data**

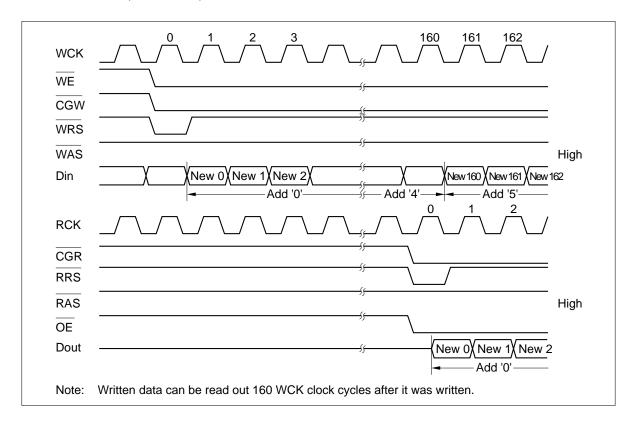

New data access (follow-up read out of data currently being written): Written data can be read out 160 WCK cycles after it is written. However, it is necessary to execute the read jump address setup operation outside the time period between 32 WCK cycles before write to that address is started and 32 WCK cycles after write to that address is completed.

- It is possible to read out the new data of 32 word block when jumping to an address at least 128 WCK clock cycles after write to that address was started. Note that in this case, there is more than enough time for the read jump address setup operation even if it is begun 32 or more clock cycles after the completion of the write operation.

- It is possible to read out the new data of less than 32 word block when 128 WCK clock after write system reset was input.

### Starting and clearing window scan:

At least 96 WCK clock are necessary between completion 32 word block data input and starting previous address of 32 word block data output. Generally this mean, 160 WCK clock separation between write and read address pointer.

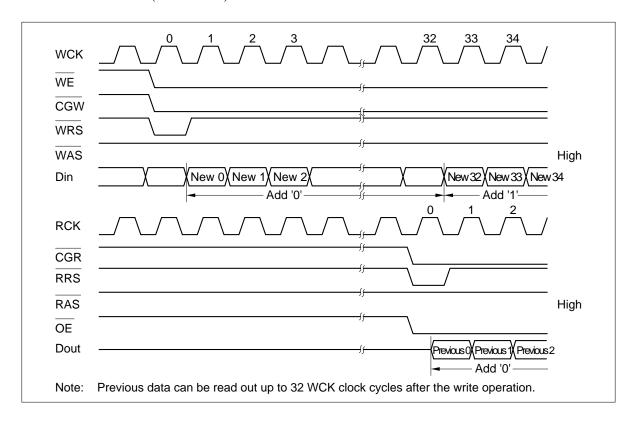

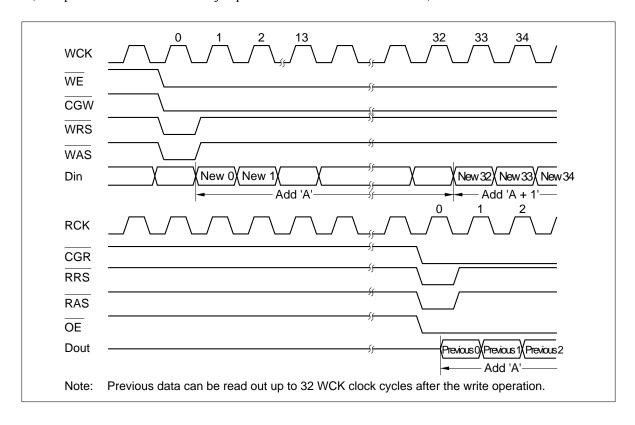

Previous data access (reading out data prior to that of the current write operation): The previous data can be read out up to 32 WCK clock cycles after the write operation. Therefore, these memories can be used to provide delay times of between 160 and 331,808 (331,776 + 32) clock cycles.

#### Power On

Wait at least  $100 \mu s$  after power-on to begin operation. At this time the write and read address pointers are undefined.

The following operation should be executed.

- $\overline{\text{CGW}}$  and  $\overline{\text{CGR}}$  should be hold low.

- Reset cycle when 1 dimensional addressing mode.

- Clear cycle when 2 dimensional addressing mode.

- Dummy cycle of over 64 WCK and 64 RCK clock cycle.

Then, initiate the desired operating mode by providing the signal input combination given by the truth tables below.

#### **Function Table**

Note: Description of operations of function table is based on the operation on condition  $\overline{CGW}$ ,  $\overline{WE}$  and  $\overline{CGR}$ ,  $\overline{OE}$  is low.

### 1 Dimensional Addressing Modes

### Write

#### **WCK Rising Edge**

| WRS | WAS | Operation     |                                                                                            |

|-----|-----|---------------|--------------------------------------------------------------------------------------------|

| Н   | Н   | Normal state  | In the normal state, the write address pointer is incremented in synchronization with WCK. |

| L   | Н   | Reset         | The write address pointer is reset to 0.                                                   |

| L   | L   | Jump          | Jump to the address A to which the write address pointer is set.                           |

| Н   | L   | Address setup | The write jump address is input.                                                           |

#### Read

### **RCK Rising Edge**

| RRS | RAS | Operation     |                                                                                           |

|-----|-----|---------------|-------------------------------------------------------------------------------------------|

| Н   | Н   | Normal state  | In the normal state, the read address pointer is incremented in synchronization with RCK. |

| L   | Н   | Reset         | The read address pointer is reset to 0.                                                   |

| L   | L   | Jump          | Jump to the address A to which the read address pointer is set.                           |

| Н   | L   | Address setup | The read jump address is input.                                                           |

2 Dimensional Addressing Modes (when window scan is not used)

Write  $^{*1}$

Operation

| Levels At The Rise Of WCK |     |      |      |      | Write Address Pointer | Write Jump                                 |         |       |

|---------------------------|-----|------|------|------|-----------------------|--------------------------------------------|---------|-------|

| WRS                       | WAS | WLRS | WWND | WCLR |                       | Control                                    | Address | Notes |

| Н                         | Н   | Н    | Н    | Н    | Normal state          | Incremented in synchronization with WCK    | _       | 2     |

| L                         | Н   | Н    | Н    | Н    | Reset                 | Reset to (0, 0)                            | _       |       |

| L                         | L   | Н    | Н    | Н    | Jump                  | Jump to the set address A                  | _       |       |

| Н                         | L   | Н    | Н    | Н    | Address set           | _                                          | Set     |       |

| Н                         | Н   | L    | Н    | Н    | Line increment        | Reset to the first bit of the next line    | _       | 2     |

| L                         | Н   | L    | Н    | Н    | Line hold             | Reset to the first bit of the current line | _       | 2     |

| _                         | _   | _    |      | L    | Clear                 | Reset to (0, 0)                            |         |       |

Note: (—: V<sub>IH</sub> or V<sub>IL</sub>)

Read\*1

| Levels At The Rise Of WCK |     |             |      |      |                   | Read Address Pointer                       | Read Jump |       |

|---------------------------|-----|-------------|------|------|-------------------|--------------------------------------------|-----------|-------|

| RRS                       | RAS | RLRS        | RWND | RCLR |                   | Control                                    | Address   | Notes |

| Н                         | Н   | Н           | Н    | Н    | Normal state      | Incremented in synchronization with RCK    | _         | 3     |

| L                         | Н   | Н           | Н    | Н    | Reset             | Reset to (0, 0)                            |           |       |

| L                         | L   | Н           | Н    | Н    | Jump              | Jump to the set address A                  |           |       |

| Н                         | L   | Н           | Н    | Н    | Address set       |                                            | Set       |       |

| Н                         | Н   | L           | Н    | Н    | Line<br>increment | Reset to the first bit of the next line    |           | 3     |

| L                         | Н   | L           | Н    | Н    | Line hold         | Reset to the first bit of the current line |           | 3     |

| _                         | _   | <del></del> | _    | L    | Clear             | Reset to (0, 0)                            | _         |       |

Note: (—: V<sub>IH</sub> or V<sub>IL</sub>)

### 2 Dimensional Address Modes (when window scan is not used)

### Write

### Operation

| Levels At The Rise Of WCK |     |      |      |      |                   | Write Add<br>Pointer C               |                                                                      | Write<br>Jump | Window<br>Mode After |       |

|---------------------------|-----|------|------|------|-------------------|--------------------------------------|----------------------------------------------------------------------|---------------|----------------------|-------|

| WRS                       | WAS | WLRS | WWND | WCLR |                   | Window<br>Mode Off                   | Window<br>Mode On                                                    | Address       | Execution            | Notes |

| L                         | Н   | Н    | Н    | Н    | Reset             | Reset to (0                          | 0, 0)                                                                | _             | Off                  |       |

| Н                         | Н   | Н    | _    | Н    | Normal state      | Incrementa<br>synchroniz<br>WCK      |                                                                      | _             | _                    | 4     |

| Н                         | Н   | L    | _    | Н    | Line<br>increment | To the first bit of the next line    | To the left<br>edge of<br>the<br>window<br>on the<br>next line       | _             | _                    |       |

| L                         | Н   | L    |      | Н    | Line hold         | To the first bit of the current line | To the left<br>edge of<br>the<br>window<br>on the<br>current<br>line | _             | _                    |       |

| Н                         | L   | Н    |      | Н    | Address set       |                                      |                                                                      | Set           |                      |       |

| L                         | L   | Н    | Н    | Н    | Jump              | Jump to the address A                |                                                                      | _             | Off                  |       |

| L                         | L   | Н    | L    | Н    | Window<br>jump    | Jump to the address A                |                                                                      | _             | On                   | 6     |

| L                         | Н   | Н    | L    | Н    | Reset             | Reset to the origin point            |                                                                      | _             | _                    |       |

|                           | _   |      |      | L    | Clear             | Reset to (0                          | 0, 0)                                                                |               | Off                  |       |

Note:  $(-: V_{H} \text{ or } V_{L})$

#### Read

#### Operation

| Level | s At Th | e Rise Of | WCK  |      |                   | Read Address Pointer Control         |                                                                      |                         |                                   |       |

|-------|---------|-----------|------|------|-------------------|--------------------------------------|----------------------------------------------------------------------|-------------------------|-----------------------------------|-------|

| RRS   | RAS     | RLRS      | RWND | RCLR |                   | Window<br>Mode Off                   | Window<br>Mode On                                                    | Read<br>Jump<br>Address | Window<br>Mode After<br>Execution | Notes |

| L     | Н       | Н         | Н    | Н    | Reset             | Reset to (0                          | 0, 0)                                                                | _                       | Off                               |       |

| Н     | Н       | Н         | _    | Н    | Normal state      | Incremente<br>synchroniz<br>RCK      |                                                                      | _                       | _                                 | 5     |

| Н     | Н       | L         |      | Н    | Line<br>increment | To the first bit of the next line    | To the left<br>edge of<br>the<br>window<br>on the<br>next line       | _                       | _                                 |       |

| L     | Н       | L         | _    | Н    | Line hold         | To the first bit of the current line | To the left<br>edge of<br>the<br>window<br>on the<br>current<br>line | _                       | _                                 |       |

| Н     | L       | Н         | _    | Н    | Address set       | _                                    |                                                                      | Set                     | _                                 |       |

| L     | L       | Н         | Н    | Н    | Jump              | Jump to th<br>address A              |                                                                      |                         | Off                               |       |

| L     | L       | Н         | L    | Н    | Window<br>jump    | Jump to th<br>address A              | e set                                                                | _                       | On                                | 6     |

| L     | Н       | Н         | L    | Н    | Reset             | Reset to the origin point            |                                                                      | _                       | _                                 |       |

|       |         |           |      | L    | Clear             | Reset to (0                          | 0, 0)                                                                | _                       | Off                               |       |

(—: V<sub>⊪</sub> or V<sub>□</sub>)

#### Notes on usage.

- 1. Hold the WWND and RWND pin high when window mode is not used.

- The write address pointer is incremented up to the last dot on the current line, and then stopped. Writing is started immediately from the first dot on the next line by execution of the line increment operation. Also, writing is started immediately from the first dot on the current line by execution of the line hold operation.

- 3. The read address pointer is incremented up to the last dot on the current line, and then stopped. Reading is started immediately from the first dot on the next line by execution of the line increment operation. Also, reading is started immediately from the first dot on the current line by execution of the line hold operation.

- 4. The write address pointer is incremented up to the last address on the line, and then stopped. Writing is started immediately from the first dot on the next line or the left edge of the window by execution of the line increment operation.

- 5. The read address pointer is incremented up to the last address on the line, and then stopped. Reading is started immediately from the first dot on the next line or the left edge of the window by execution of the line increment operation.

- 6. It is possible to move directly from an old window to a new window in window mode by setting up a new jump address and executing a window setup jump operation. However, the new jump address should be input after access to the last line of the old window.

- 7. Read system reset operations (read reset, read jump, read window reset, read line reset and read clear) and the read address set up operation cannot be executed for consecutive RCK clock cycles. Similarly write system reset operations (write reset, write jump, write window reset, write line reset and write clear) and the write jump address setup operation cannot be executed for consecutive WCK clock cycles.

- 8. Read system reset (read reset, read jump, read window reset, read line reset and read clear) operations and read jump address set operations must be performed at times separated by at least 64 RCK clock cycles. (There is no need to use only 32 word addressing units, and these operations can be performed on any clock cycle).

- Write system reset operations (write reset, write jump, write window reset, write line reset and write clear) must be performed at times separated by at least 64 WCK clock cycles. When address is input, write/read system reset can not be executed.

- 10. It is possible to input the write system reset in the middle of 32 word unit addressing. In this case, not only must the condition of note 8 be met, but furthermore, pairs of write system resets for units of less than 32 words must be separated by at least 160 WCK clock cycles. When the write system reset is executed at less than 32 words, the data up to the point to which the address pointer has advanced will be written, and the remaining data will retain the old values. (Note that after the completion of a write of less than 32 words, a write reset is required to write the data for the last address into the memory array.)

11.

| Addressing Mode    | Address Structure                          | Input Address                                                |

|--------------------|--------------------------------------------|--------------------------------------------------------------|

| 1 dim. add. (FIFO) | 0 to 10,367 blocks                         | Address bit A13 to A0                                        |

| 2 dim. add. (1)    | 32 horizontal blocks by 324 vertical lines | Line address bits V8 to V0, horizontal address bits H4 to H0 |

| 2 dim. add. (2)    | 36 horizontal blocks by 288 vertical lines | Line address bits V8 to V0, horizontal address bits H5 to H0 |

#### 12. Specifiable window sizes

Horizontal: Between 64 dots and the length of the line.

Vertical: Between 1 line and the maximum number of lines.

- 13. Location 0 and line end cannot be specified as a jump address. Use a reset to access location 0.

- 14. Any number of read system reset operations can be input when CGR is high but in this case the only first reset is effective. This read system reset operation (read reset, read jump, read window reset, read line reset and read clear) is executed at the rising edge of the RCK just after CGR is set low.

- 15. Any number of write system resets can be input when  $\overline{\text{CGW}}$  is high, but the only first reset is effective. This write system reset operation is executed at the rising edge of the WCK just after  $\overline{\text{CGW}}$  is set to low

- 16. When window scan mode is used any case after power on, WWND and WRS or RWND and RRS pins are should be input same signal.

### **Supplement**

If the read system reset interval (at least 64 RCK clock cycles) of note 7, or the write system reset interval for less than 32 word units (and at least 160 WCK clock cycles) are not provided (see note 9), it is possible for the 32 words of data of the first address after the reset to be invalid, or for the first write of less than 32 words following the write reset to fail to occur. However, even in this case, address pointer control will function correctly, and valid data will be output for the second and following addresses. (However, in this case the condition of note 8 and the 32 clock or longer read system reset/read jump address interval must be provided.)

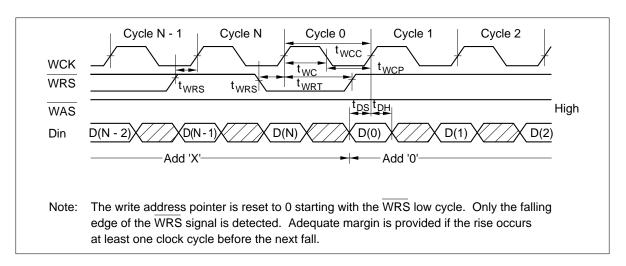

### **Timing Waveforms**

### Write Cycle

#### Write address reset

### Write clock gate

### Write enable

### **Read Cycle**

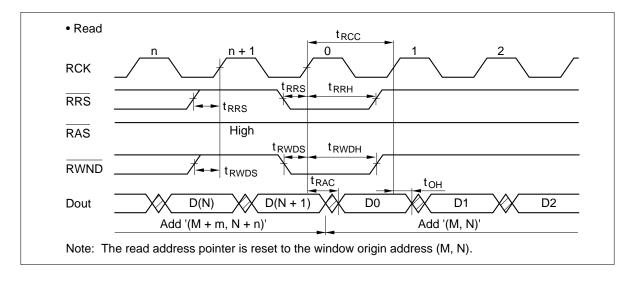

### Read address reset

### Read clock gate

### Output enable

### Line Reset

### Write line increment

### Read line increment

### Write line hold

#### Read line hold

### Jump Address Setup (1 Dimensional Addressing Mode)

### Write address setup

#### Read address setup

**Jump Address Setup** (2 Dimensional Addressing Mode 1)

Write address setup (2 dimensional addressing:  $324 \text{ line} \times 1024 \text{ dot mode}$ )

**Read address setup** (2 dimensional addressing: 324 line × 1024 dot mode)

**Jump Address Setup** (2 Dimensional Addressing Mode 2)

Write address setup (2 dimensional addressing:  $288 \text{ line} \times 1152 \text{ dot mode}$ )

**Read address setup** (2 dimensional addressing: 288 line × 1152 dot mode)

### Address input mask

### Jump

### Write jump

### Read jump

### **New/Previous Data Access**

New data access (address reset)

### Previous data access (address reset)

New data access (address jump)

(example where the read and write jump addresses are to the same location)

### Previous data access (address jump)

(example when the read and write jump addresses are to the same location)

### Clear

### Write clear

### Read clear

### **Window Scan Function**

### **Combined Window Scan Example**

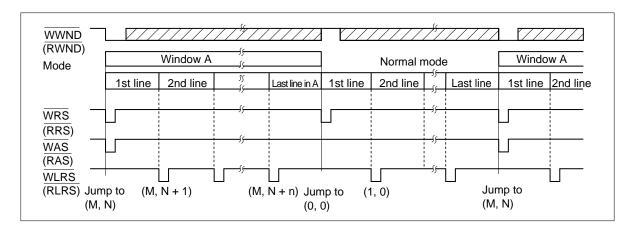

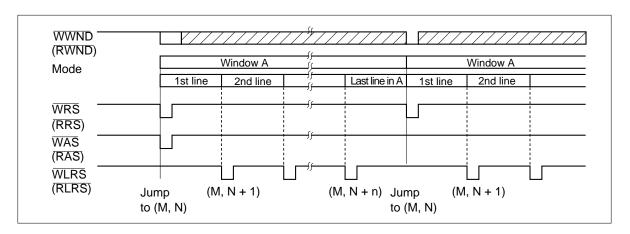

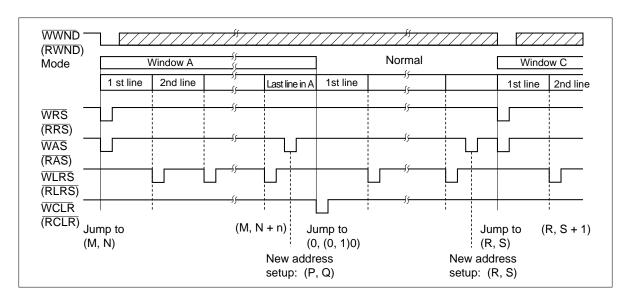

In window scan mode, the destination address of a jump will be the first point in the window region, and line reset and reset operate as follows.

Line reset: Resets to the left edge of the window on the next line.

Reset: Resets to the first point in the window.

In this mode, addresses are generated automatically internally, so this function is useful in applications that need to scan a window region.

Also, completely independent window regions can be scanned by the read and write systems.

Representative application examples are presented below.

Case 1: Switching Between Normal and Window A Scan

Case 2: Repeatedly Scanning Window A

Case 3: Switching from Window A Scan to Normal Scan to Window C Scan

Case 4: Switching from Window A Scan to Window B Scan to Window C Scan

### **Window Scan Timing Charts**

### Window Jump (setup)

### Window Jump (setup) (cont)

### Line Increment (in window mode)

### Line Increment (in window mode) (cont)

### Line Hold (in window mode)

### **Window Clear**

### Clear

### Reset to the Window Origin

These figures show the timing charts for resetting the address pointer to the window origin address (M, N) during window scan mode execution

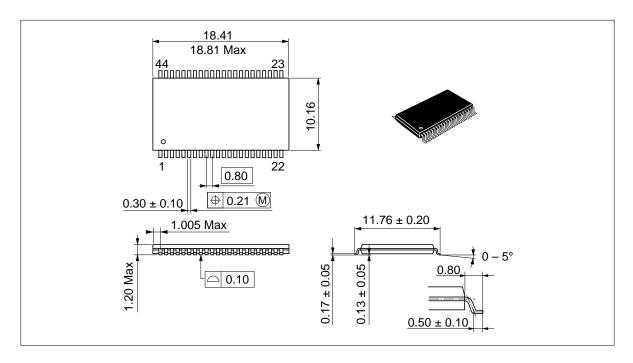

### **Package Dimensions**

### HM530281RTT Series (TTP-44DB)

Unit: mm

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi. Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# HITACHI

#### Hitachi, Ltd.

Semiconductor & IC Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100, Japan

Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

#### For further information write to:

Hitachi America, Ltd. Semiconductor & IC Div. 2000 Sierra Point Parkway Brisbane, CA. 94005-1835 U S A

Tel: 415-589-8300 Fax: 415-583-4207 Hitachi Europe GmbH Electronic Components Group Continental Europe Dornacher Straße 3 D-85622 Feldkirchen München Tel: 089-9 91 80-0

Fax: 089-9 29 30 00

Hitachi Europe Ltd.

Electronic Components Div.

Northern Europe Headquarters

Whitebrook Park

Lower Cookham Road

Maidenhead

Berkshire SL6 8YA

United Kingdom

Tel: 0628-585000

Fax: 0628-778322

Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 0104 Tel: 535-2100 Fax: 535-1533

Hitachi Asia (Hong Kong) Ltd. Unit 706, North Tower, World Finance Centre, Harbour City, Canton Road Tsim Sha Tsui, Kowloon Hong Kong Tel: 27359218

Fax: 27306071