## 捷多邦,专业PCB打样工厂,24小时 **Am8127** 加急出货

AmZ8000 Clock Generator

#### DISTINCTIVE CHARACTERISTICS

- High-drive high-level clock output

Special output provides clock signal matched to requirements of AmZ8000° CPU (4MHz and some 6MHz applications), MMU and DMA devices.

- Synchronized WAIT state and time-out controls

On-chip logic generates WAIT signal under control

of Halt, Single-step, Status and Ready signals. Automatic time-out of peripheral wait requests.

- Four TTL-level clocks

Generates synchronized TTL compatible clocks at

16MHz, 2MHz and 1MHz to drive memory circuits

and LSI peripheral devices. An additional TTL clock

is synchronized with the CPU high-level clock for

registers, latches and other peripherals.

#### **GENERAL DESCRIPTION**

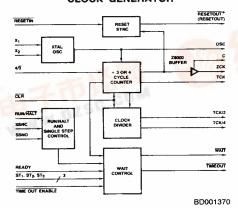

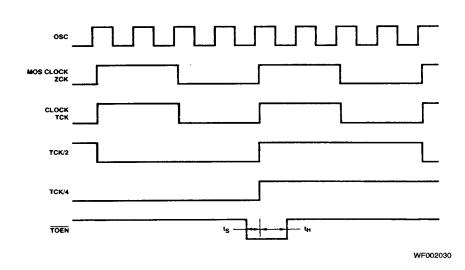

The Am8127 Clock Generator and Controller provides the clock oscillator, frequency dividers and clock drivers for the complete array of AmZ8000 CPUs, peripherals and memory system configurations. In addition to the special 4MHz output driver for the AmZ8001\* and AmZ8002\* CPUs, a standard buffered TTL 16MHz oscillator output is provided for a dynamic memory timing and control. In addition to 4MHz applications, the Am8127 will also function in some 6MHz Z8000 applications. The Am8127 forms an integral part of the dynamic memory support chip set including the Am8163 EDC and Refresh Controller, Am2964 Dynamic Memory Controller, Am2960 Error Detection and Correction Unit and Am2961/Am2962 EDC Bus Buffers. The oscillator is designed to operate with a 16MHz crystal or with external 16MHz drive. The Am8127 uses an internal divide-by-4 to provide 4MHz clock drive to the AmZ8001/AmZ8002 CPU. Additional dividers generate synchronous buffered 4, 2 and 1MHz clock outputs for use by peripheral devices. The clock divider counters are clearable to allow synchronization of the multiple clock outputs.

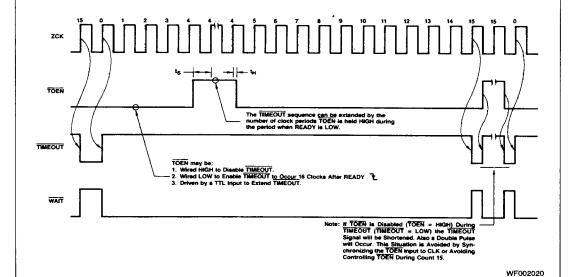

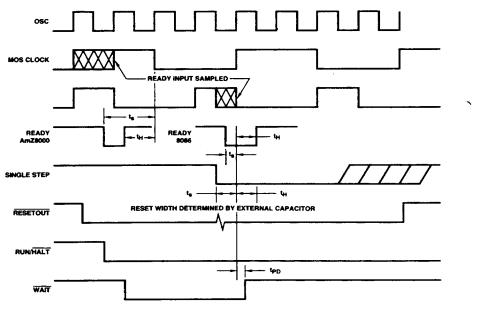

The controller functions include RESET, RUN/HALT, SIN-GLE-STEP, READY and a READY TIMEOUT counter which limits a peripheral's wait request to 16 clock cycles. The CPU's WAIT input is controlled by RUN/HALT, Single-Step, Status and READY. When RUN/HALT is LOW the Am8127 drives the WAIT output LOW causing the CPU to add wait states (TW). The READY input is used by peripherals to request wait states. The active LOW input timeout enable, TOEN, is used to force TIME-OUT LOW and WAIT HIGH 16 clock cycles after a peripheral has requested a wait but fails to release the request. The CPU status lines ST<sub>1</sub>, ST<sub>2</sub> and ST<sub>3</sub> are decoded in the Am8127 to disable the TIMEOUT counter during CPU "Internal Operations" and during refresh.

The 4/3 input controls the clock duty cycle. An internal pullup resistor pulls this input high for AmZ8000 CPUs. A LOW input causes the cycle counter to output a 33% duty cycle.

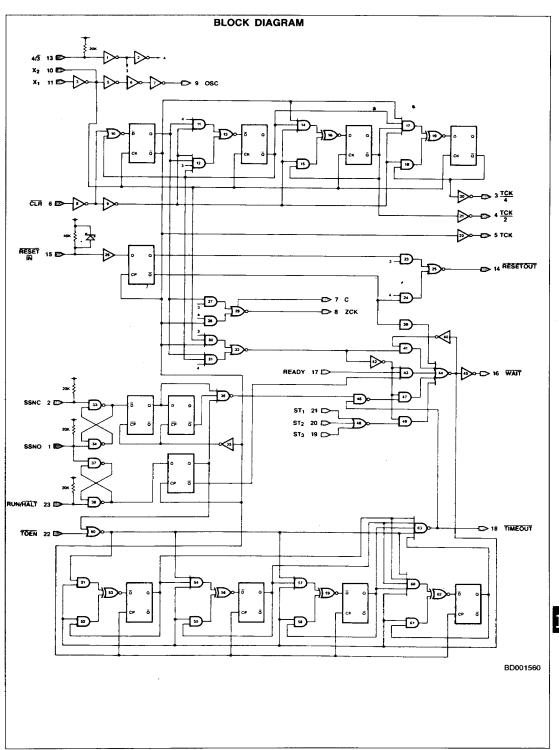

## BLOCK DIAGRAM CLOCK GENERATOR

\*RESETOUT is active LOW when 4/3 = HIGH

Z8001 and Z8002 are trademarks of Zilog, Inc.

03432C

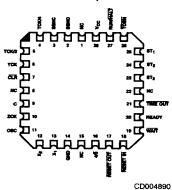

Leadless Chip Carrier

24 Pin 0.3" wide Pin 1 is marked for orientation

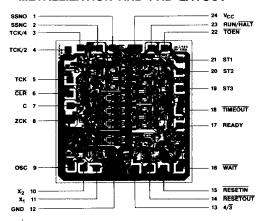

#### **METALLIZATION AND PAD LAYOUT**

DIE SIZE 0.098" x 0.088"

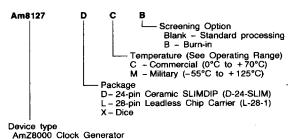

#### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

| Valid Con | nbinations                                           |

|-----------|------------------------------------------------------|

| Am8127    | DC, DCB, DM,<br>DMB<br>LC, LCB, LM,<br>LMB<br>XC, XM |

#### Valid Combinations

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

### PIN DESCRIPTION

| Pin No.    | Name                                                   | 1/0 | Description                                                                                                                                                                                                                                                                                                                                         |

|------------|--------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8          | ZCK                                                    | 0   | Buffered clock output for CPU and peripherals. This output has under/overshoot control and provides the high level output voltage required (VCC - 0.4V). This output is capable of driving multiple CPU clock inputs (or DMA, MMU, etc).                                                                                                            |

| 7          | С                                                      | 1   | Bootstrap input. The capacitor CB is connected from the ZCK clock output to C to provide faster ZCK risetime.                                                                                                                                                                                                                                       |

| 5          | TCK                                                    | 0   | TTL level buffered clock output. TCK is the same frequency as ZCK and is synchronized with ZCK. TCK is in phase with ZCK when the 4/3 duty cycle control input is HIGH (50% duty cycle) and out of phase with ZCK when 4/3 is LOW (33% ZCK duty cycle).                                                                                             |

| 3, 4       | TCK/2,<br>TCK/4                                        | 0   | TTL buffered clocks for peripherals. TCK/2 and TCK/4 are 1/2 and 1/4 the TCK frequency and are synchronized with the rising edge of TCK.                                                                                                                                                                                                            |

| 9          | osc                                                    | 0   | The clock oscillator TTL buffered output. This output provides a high speed clock for dynamic memory timing (e.g. AmZ8000 uses this output to generate RAS/MUX-Select/CAS timing for dynamic RAMs) or other system application. The ZCK and TCK outputs are synchronized to the OSC rising edge.                                                    |

| 13         | 4/3                                                    | 1   | Clock duty cycle control for ZCK and TCK. A HIGH input (no connection - input has internal pull-up) will result in a 50% duty cycle for AmZ8000 application. A LOW input will cause a 33% duty cycle ZCK output.                                                                                                                                    |

| 6          | CLR                                                    | ı   | The clear active LOW input for internal counters. A LOW input meeting set-up and hold time requirements will clear the internal clock counters on the rising edge of OSC.                                                                                                                                                                           |

| 16         | WAIT                                                   | 0   | The WAIT output for connection to the CPU WAIT input. This latched output controls when the CPU enters wait states in response to the READY, ST <sub>1</sub> , ST <sub>2</sub> , ST <sub>3</sub> , RUN/HALT and Single Step inputs.                                                                                                                 |

| 17         | READY                                                  | 1   | The active HIGH READY input is used by peripherals to request wait states. Ready inputs must meet the wait latch set-up and hold time requirements.                                                                                                                                                                                                 |

| 18         | TIMEOUT                                                | 0   | The Timeout Counter active LOW output. The Timeout Counter counts ZCK/TCK clock cycles and is used to force WAIT HIGH 15 clock cycles after a peripheral has requested a wait but has failed to release the request. This output is normally used to interrupt the CPU.                                                                             |

| 22         | TOEN                                                   |     | The Timeout Enable active LOW input. A LOW input allows the Timeout Counter to count, causes the TIMEOUT output to go LOW for one ZCK/TCK clock period after 15 cycles and forces WAIT HIGH at the rising edge of the 16th cycle. A HIGH input disables the counter and allows WAIT to be controlled by the READY, RUN/HALT and Single Step inputs. |

| 14         | RESET-<br>OUT<br>(RESET-<br>OUT)                       | 0   | The Reset Output to the CPU. It is active LOW when the 4/3 input is HIGH and active HIGH when the 4/3 input is LOW.                                                                                                                                                                                                                                 |

| 15         | RESETIN                                                | 1   | The active LOW Reset Input. A LOW input will cause RESETOUT to go LOW synchronous with ZCK Pushbutton reset is implemented by momentarily grounding RESETIN. Power-up reset is implemented by connecting a capacitor from RESETIN to ground. Capacitor values from 10µF to 22µF will provide a power-up of less than one second.                    |

| 23         | RUN/<br>HALT                                           | i   | A debounced input to allow halt and Single Step control modes. A HIGH input allows the CPU to run. A LOW input forces the WAIT output LOW causing the CPU to enter continuous wait states until the ZCK period after RUN/HALT is returned to HIGH.                                                                                                  |

| 1          | SSNO,<br>SSNC                                          | 1   | Single Step control inputs. These debounced input allow the CPU to Single Step from one wait state to the next by momentarily disconnecting SSNC from ground and grounding SSNO. RUN/HALT must be LOW for Single Step operation.                                                                                                                    |

| 19, 20, 21 | ST <sub>1</sub> , ST <sub>2</sub> ,<br>ST <sub>3</sub> | 1   | Status inputs from AmZ8000 CPU's and peripherals. Continuous LOW inputs indicate that the CPU is executing "internal operation" or "feresh." During this time the time out is disabled to avoid signaling an inappropriate interrupt. The status inputs are subject to the set-up and hold time requirements of the WAIT latch.                     |

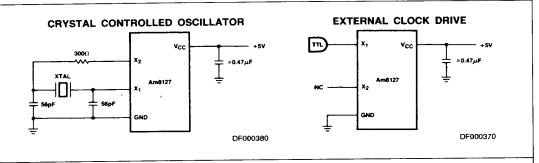

|            |                                                        |     | External crystal connections (see application section). X1 may be driven directly by a TTL input.                                                                                                                                                                                                                                                   |

\*RESETOUT is active LOW when  $4/\overline{3} = HIGH$ .

### TYPICAL CRYSTAL SPEC

| Mode      | Fundamental AT cut                        |

|-----------|-------------------------------------------|

| Resonance | Parallel or Series                        |

| Load      | 32pF<br>(Net of 56pF C's shown + stray C) |

| Stability | ±0.01%<br>(or to user requirement)        |

### WAIT, TIMEOUT FUNCTION TABLE

| SSNC                        | ST3 ST2 ST1 | READY                                 | TOEN                        | TIMEOUT<br>COUNTER   | TIMEOUT                                                                                                                  | WAIT                                                            |

|-----------------------------|-------------|---------------------------------------|-----------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                             | L L L       | н                                     | X                           | Cleared              | н                                                                                                                        | Н                                                               |

|                             | L L L       | L                                     | Х                           | Cleared              | Н                                                                                                                        | н                                                               |

|                             |             | н                                     | L                           | Cleared              | H                                                                                                                        | Н                                                               |

| H X Any ST <sub>i</sub> = H |             | L                                     | Н                           | Hold                 | Н                                                                                                                        | L                                                               |

|                             |             | L                                     | L                           | Count +1_on<br>ZCK _ | H until 16 clocks<br>after ready L, then<br>LOW one ZCK period                                                           | L until 16 clocks<br>after ready L, then<br>HIGH one ZCK period |

| L                           | ×           | ×                                     | ×                           | Hold                 | н                                                                                                                        | L<br>HIGH one<br>ZCK period                                     |

|                             | X           | L L L L L X Any ST <sub>i</sub> = H . | X Any ST <sub>i</sub> = H L | X                    | X Any ST <sub>i</sub> = H  L L X Cleared  H L Cleared  L H Cleared  L H Cleared  L H Cleared  L H Hold  Count +1_on  ZCK | SSNC   ST3   ST2   ST1   READY   TOEN   COUNTER   TIMEOUT       |

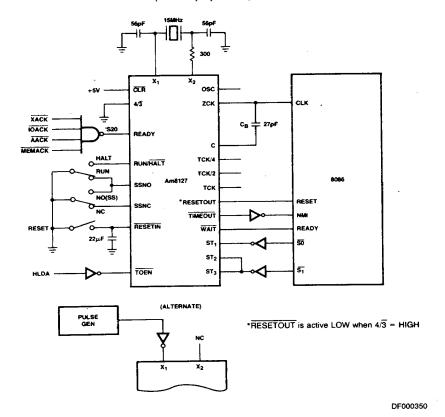

#### AmZ8000 APPLICATION

(50% Duty Cycle ZCK)

The typical operating configuration for Am8127 is shown above. The component values shown provide a 4MHz clock output for the AmZ8002 CPU. The 27pF capacitor from C to ZCK is a bootstrap to ensure clock rise to  $V_{\rm CC}$  -0.4V within

the specified rise time. The  $22\mu\dot{\Gamma}$  reset capacitor is chosen to guarantee reset, plus adequate delay for reset during power-up with a slowly rising VCC supply voltage. Ground SSNO if RUN/HALT or S-S isn't used.

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65°C to +150°C                                                |

|----------------------------------------------------------------------------------|

| Temperature (Ambient) Under Bias55°C to +125°C                                   |

| Supply Voltage to Ground Potential                                               |

| (Pin 24 to Pin 12) Continuous0.5V to +7.0V                                       |

| DC Voltage Applied to Outputs For                                                |

| High Output State0.5V to +V <sub>CC</sub> max                                    |

| DC Input Voltage                                                                 |

| $X_1,4/\overline{3}$ , SSNO, SSNC, RUN/ $\overline{HALT}$ 0.5V to $V_{CC}$ +0.5V |

| Other Inputs                                                                     |

| DC Voltage Applied to C0.5V to +8V                                               |

| DC Output Current, Into Outputs                                                  |

| DC Input Current30mA to +5.0mA                                                   |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices Temperature | 0°C to +70°C                       |

|------------------------------------|------------------------------------|

| Supply Voltage                     | +4.75V to +5.25V                   |

| Military (M) Devices               |                                    |

| Temperature                        | 55°C to +125°C                     |

| Supply Voltage                     | +4.5V to +5.5V                     |

| Operating ranges define thos       | se limits over which the function- |

| ality of the device is quarau      | nteed                              |

#### DC CHARACTERISTICS over operating range unless otherwise specified

| Parameter       | meter Description Test Conditions |                                                  | Test Conditions                                         | (Note 1)                                                                                   | Min         | Typ<br>(Note 2)      | Max                  | Units |        |

|-----------------|-----------------------------------|--------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------|----------------------|----------------------|-------|--------|

|                 |                                   |                                                  | ZCK                                                     | I <sub>OH</sub> = -0.1mA                                                                   |             | V <sub>CC</sub> -0.4 | V <sub>CC</sub> -0.1 |       | Volts  |

| VOH             | Output HIGH Voltage               | V <sub>CC</sub> = MIN                            | TTL                                                     | I <sub>OH</sub> = -1mA                                                                     | MIL         |                      |                      |       | 14.11. |

|                 |                                   |                                                  | Outputs                                                 | I <sub>OH</sub> = -2.6mA                                                                   | COMIL       | 2.4                  | 3.4                  |       | Volts  |

|                 | Output LOW Voltage                | V <sub>CC</sub> = MIN                            |                                                         | IOL = 0.1mA, ZCK Out                                                                       | out         |                      |                      | 0.4   | Volts  |

| VOL             | Output COW Voltage                | ACC - MILA                                       |                                                         | IOL = 16mA, TTL Outp                                                                       | ut          |                      |                      | 0.5   | Volts  |

|                 |                                   | Guaranteed                                       | innut                                                   | RESETIN                                                                                    |             | 2.8                  | 2.25                 |       | Volts  |

| V <sub>IH</sub> | Input HIGH Level                  | HIGH Voltag                                      |                                                         | ST <sub>1</sub> , ST <sub>2</sub> , ST <sub>3</sub> , CLA,<br>TOEN, X <sub>1</sub> , READY |             | 2.0                  |                      |       | Volts  |

| V <sub>IL</sub> | Input LOW Level                   | Guaranteed<br>LOW Voltage                        |                                                         | ST <sub>1</sub> , ST <sub>2</sub> , ST <sub>3</sub> , CLR,<br>TOEN, X <sub>1</sub> , READY |             |                      |                      | 0.8   | Volts  |

| $V_{I}$         | Input Clamp Voltage               | V <sub>CC</sub> = MIN,                           | V <sub>CC</sub> = MiN, I <sub>IN</sub> = -18mA (Note 3) |                                                                                            |             |                      |                      | - 1.5 | Volts  |

| VIN-VIL         | RESETIN Hysteresis                | V <sub>CC</sub> = MIN                            | V <sub>CC</sub> = MIN                                   |                                                                                            |             | 400                  | 650                  |       | mV     |

|                 | III Input LOW Current             | V <sub>CC</sub> = MAX,                           |                                                         | SSNO                                                                                       |             |                      |                      | - 1.6 | mA     |

|                 |                                   |                                                  |                                                         | SSNC, 4/3, RUN/HALT, READY                                                                 |             |                      |                      | - 1.2 | mA     |

| l <u>i</u> L    | Input LOW Current                 | V <sub>IN</sub> = 0.4V                           |                                                         | TOEN, CLR, X1                                                                              |             |                      |                      | -0.72 | mA     |

|                 |                                   |                                                  |                                                         | RESETIN, ST <sub>1</sub> , ST <sub>2</sub> , ST <sub>3</sub>                               |             |                      |                      | -0.36 | mA     |

|                 |                                   |                                                  |                                                         | 4/3, SSNC, SSNO<br>RUN/HALT                                                                |             |                      | (Note 4)             | -300  | μА     |

|                 |                                   | V <sub>CC</sub> = MAX,                           |                                                         | RESETIN                                                                                    |             |                      | (Note 4)             | -200  | μА     |

| lін             | Input HIGH Current                | V <sub>IN</sub> = 2.7V                           |                                                         | CLR, READY, TOEN<br>ST <sub>1</sub> , ST <sub>2</sub> , ST <sub>3</sub>                    |             |                      |                      | + 50  | μА     |

|                 |                                   | l ·                                              |                                                         | X <sub>1</sub>                                                                             |             |                      |                      | +600  | μА     |

| lį              | Input HIGH Current                | V <sub>CC</sub> = MAX,<br>V <sub>IN</sub> = 5.5V |                                                         | CLR, READY, TOEN<br>ST <sub>1</sub> , ST <sub>2</sub> , ST <sub>3</sub>                    |             |                      |                      | + 1.0 | mA     |

|                 | Output Short Circuit              |                                                  | · · · · · ·                                             | ZCK Output                                                                                 |             | -50                  |                      | -240  | mA     |

| Isc             | Current (Note 5)                  | V <sub>CC</sub> = MAX                            |                                                         | Others                                                                                     |             | -40                  |                      | -130  | mA     |

|                 | D                                 |                                                  |                                                         | X <sub>1</sub> = 2.4V, ZCK = TCK                                                           | s = LOW     |                      | 95                   | 140   |        |

| Icc             | Power Supply Current              | V <sub>CC</sub> = MAX                            |                                                         | Operating, f <sub>OSC</sub> ≤ 24MI                                                         | Iz (Note 6) |                      | 120                  | 180   | mA     |

Notes: 1. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Range for the applicable device type.

2. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

3. Not applicable to X<sub>1</sub>.

Specification is negative because of internal input pull-up resistors.

Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

For oscillator frequencies up to 24MHz, outputs open.

## STATIC INPUT ELECTRICAL CHARACTERISTICS

The static control inputs, SSNO, SSNC (Single Step), RUN/ $\overline{\text{HALT}}$  and  $4/\overline{3}$  (clock duty cycle control), are Low-Power Schottky TTI compatible inputs with internal pull-up resistors

to the +5V supply. They may be left open for a HIGH input (e.g.,  $4/\overline{3}$  is left open for operation with AmZ8001/8002), or grounded for a LOW input. SSNO, SSNC and RUN/HALT are intended to be grounded or opened by switches.  $4/\overline{3}$  is normally left open for AmZ8001/8002. These inputs are specified at 0.4V/2.4V for test convenience.

| Parameter | Description        | Test Condition                | Min               | Тур | Max | Units |       |

|-----------|--------------------|-------------------------------|-------------------|-----|-----|-------|-------|

| ViH       | Input HIGH Voltage | Guaranteed HIGH input voltage | RUN HALT,<br>SSNO | 2.4 |     |       | Volts |

| ViL       | Input LOW Voltage  | Guaranteed LOW input voltage  | SSNC,4/3          |     |     | 0.4   | Volts |

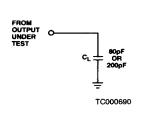

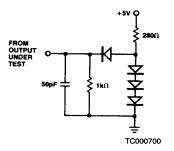

#### SWITCHING TEST CIRCUIT

**ZCK Output**

**TTL Outputs**

## SWITCHING TEST WAVEFORMS

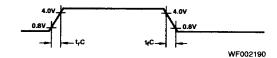

ZCK RISE AND FALL TIMES

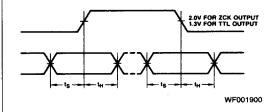

#### SET-UP AND HOLD TIMES

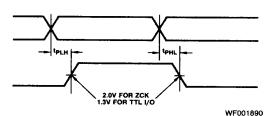

#### PROPAGATION DELAY TIMES

### SWITCHING CHARACTERISTICS —OSCILLATOR, WAIT AND ZCK OUTPUT $(T_A = +25^{\circ}C, V_{CC} = 5.0V)$

| <b>Parameters</b> | Descript                                                                                           | ion                    | Test Conditions               | Min | Тур  | Max | Units |

|-------------------|----------------------------------------------------------------------------------------------------|------------------------|-------------------------------|-----|------|-----|-------|

| f <sub>MAX</sub>  | Oscillator Frequency                                                                               |                        | See Test Circuits<br>(Note 7) | 24  |      |     | MHz   |

| ¹rC               | ZCK Rise Time                                                                                      |                        | ZCK C <sub>L</sub> = 80pF     |     | 9    | 14  | ns    |

| t <sub>fc</sub>   | ZCK Fall Time                                                                                      | C <sub>L</sub> = 80pF  | (Note 8)                      |     | 7.6  | 11  | ns    |

| tro               | ZCK Rise Time                                                                                      |                        | ZCK C <sub>L</sub> = 200pF    |     | 15.4 | 20  | ns    |

| t <sub>fc</sub>   | ZCK Fall time                                                                                      | C <sub>L</sub> = 200pF | (Note 8)                      |     | 14.0 | 20  | ns    |

| t <sub>PLH</sub>  |                                                                                                    |                        |                               |     | 8    | 14  | ns    |

| tPHL              | READY to WAIT                                                                                      |                        |                               |     | 11.5 | 16  | ns    |

| tplH              |                                                                                                    |                        |                               |     | 13   | 17  | ns    |

| t <sub>PHL</sub>  | Status ST <sub>i</sub> to WAIT                                                                     |                        | See Test Circuits             |     | 17.2 | 21  | ns    |

| ts                | CLR to OSC ( J ) Setup T                                                                           | ime                    |                               |     | 15   | 18  | ns    |

| tu                | READY to WAIT  Status ST <sub>i</sub> to WAIT  CLR to OSC ( ) Setup Time  CLR to OSC ( ) Hold Time |                        |                               |     | -11  | -6  | ns    |

Notes: 7. Specification is based on fundamental mode crystal. See application section.

8. ZCK rise and fall times are based on a bootstrap capacitor value of 27pF.

## SWITCHING CHARACTERISTICS — $4/\overline{3}$ = HIGH (AmZ8000 Mode)

$(T_A = +25^{\circ}C, V_{CC} = 5.0V)$

| Parameters     | Description                               |          | Test Conditions                                | Min      | Тур       | Max | Units |

|----------------|-------------------------------------------|----------|------------------------------------------------|----------|-----------|-----|-------|

| ts             | READY to ZCK Set-up Time                  |          |                                                | T/4 + 10 | T/4 + 4.5 |     | ns    |

| tH             | READY to ZCK Hold Time                    | (Note 9) |                                                | T/4 + 2  | T/4       |     | ns    |

| ts             | Status ST <sub>i</sub> to ZCK Set-up Time |          |                                                | T/4 + 12 | T/4 + 9.5 |     | ns    |

| t <sub>H</sub> | Status ST <sub>i</sub> to ZCK Hold Time   |          |                                                | T/4-3    | T/4 - 7.5 |     | ns    |

| ts             | TOEN to ZCK Set-up Time                   |          | See Test Circuits<br>ZCK C <sub>l</sub> = 80pF | 30       | 22        |     | ns    |

| t <sub>H</sub> | TOEN to ZCK Hold Time                     |          |                                                | -10      | -16       |     | ns    |

| ISKEW          | ZCK to OSC                                |          |                                                | 3        | 6         | 10  | пѕ    |

| tskew          | ZCK to TCK                                |          |                                                | 0        | 4.0       | 7   | ns    |

| tPLH           |                                           |          |                                                |          | 9.0       | 13  | ns    |

| трні           | ZCK to RESET OUT Propagation Delay        |          |                                                | <u> </u> | 4         | 8   | ns    |

Note: 9. T = ZCK period.

# SWITCHING CHARACTERISTICS OVER OPERATING RANGE — OSCILLATOR, WAIT AND ZCK OUTPUTS\*

| Parameters       |                                            |                        |                                    | COM | MERC      | IAL  | N   | Ι¥         |             |       |

|------------------|--------------------------------------------|------------------------|------------------------------------|-----|-----------|------|-----|------------|-------------|-------|

|                  | Description                                |                        | Test Conditions                    | Min | Ma<br>0°C | 70°C | Min | M<br>-55°C | ax<br>125°C | Units |

| tMAX             | Oscillator Frequency                       | Oscillator Frequency   |                                    | 24  |           |      | 24  |            |             | MHz   |

| tro              | ZCK Rise Time                              | C <sub>L</sub> = 80pF  | C <sub>L</sub> = 80pF              |     | 15        | 15   |     | 20         | 15          | ns    |

| tfC              | ZCK Fall Time                              |                        | (Note 8)                           |     | 14        | 14   |     | 20         | 14          | ns    |

| tc               | ZCK Rise Time                              |                        | C <sub>L</sub> = 200pF<br>(Note 8) | T . | 25        | 20   |     | 32         | 20          | ns    |

| t <sub>fC</sub>  | ZCK Fall time                              | C <sub>L</sub> = 200pF |                                    |     | 25        | 20   |     | 32         | 20          | ns    |

| t <sub>PLH</sub> |                                            |                        |                                    |     | 17        | 17   |     | 19         | 19          | ns    |

| t <sub>PHL</sub> | READY to WAIT Propagation De               | lay                    |                                    |     | 19        | 19   |     | 19         | 19          | ns    |

|                  | 1                                          |                        |                                    |     | 20        | 20   |     | 22         | 22          | ns    |

| t <sub>PLH</sub> | Status ST <sub>i</sub> to WAIT Propagation | Delay                  | See Test Circuits                  |     | 25        | 25   |     | 25         | 25          | ns    |

| t <sub>S</sub>   | CLR to OSC ( ) Setup Time                  | ,                      |                                    | 21  |           |      | 30  |            |             | ns    |

| t <sub>H</sub>   | CLR to OSC ( _ ) Hold Time                 |                        |                                    | -3  |           |      | 0   |            | Ĭ           | ns    |

<sup>\*</sup>AC performance over the operating temperature range is guaranteed by testing defined in Group A, Subgroup 9.

# SWITCHING CHARACTERISTICS OVER OPERATING RANGE — $4/\overline{3}$ = HIGH (AmZ8000 Mode)

| Parameters     |                                          |                                              | COMME    | RCIAL | MILIT    | ARY |       |

|----------------|------------------------------------------|----------------------------------------------|----------|-------|----------|-----|-------|

|                | Description                              | Test Conditions                              | Min      | Max   | Min      | Max | Units |

| ts             | READY to ZCK Setup Time                  |                                              | T/4 + 14 |       | T/4 + 17 |     | ns    |

| 1 <sub>H</sub> | READY to ZCK Hold Time                   | See Test Circuits ZCK, C <sub>L</sub> = 80pF | T/4 + 5  |       | T/4 + 5  |     | ns    |

| ts.            | Status ST <sub>i</sub> to ZCK Setup Time |                                              | T/4 + 15 |       | T/4 + 20 |     | ns    |

| t <sub>H</sub> | Status ST <sub>i</sub> to ZCK Hold Time  |                                              | T/4      |       | T/4 + 5  |     | ns    |

| ts ts          | TOEN to ZCK Setup Time                   |                                              | 35       | -     | 40       |     | ns    |

| t <sub>H</sub> | TOEN to ZCK Hold Time                    |                                              | -5       |       | 0        |     | ns    |

| tskew          | ZCK to OSC Skew                          |                                              | 2        | 14    | 2        | 17  | ns    |

|                | ZCK to TCK Skew                          |                                              | -2       | 10    | -2       | 14  | ns    |

| tskew          |                                          | -                                            |          | 16    |          | 20  | ns    |

| tplH<br>tpHL   | ZCK to RESETOUT Propagation Delay        |                                              |          | 16    |          | 20  | ns    |

# Am8127 CLOCK OUTPUTS DIVIDE BY 4 MODE (AmZ8000)

WF002010