## EZ-USB<sup>™</sup> Series 2100 USB Controller

### EZ-USB Series 2100 Family

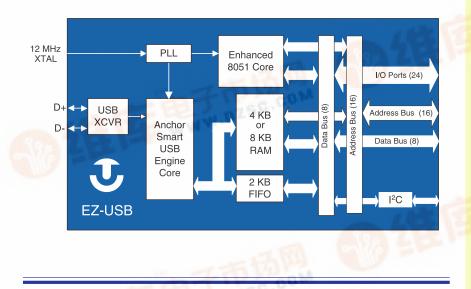

The Anchor Chips EZ-USB<sup>™</sup> family (AN21XX/AN23XX) provides significant improvements over other USB architectures including an enhanced 8051 core, 4 or 8 Kbytes of RAM, an intelligent USB core, and high-performance I/O ports. The family includes 16 different products to accommodate the needs of different systems.

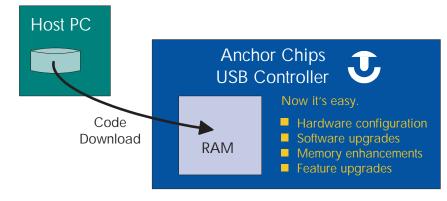

The enhanced 8051 core provides five times the performance of the standard 8051, while maintaining complete 8051 software compatibility. With on-chip RAM, firmware code can be downloaded from the host PC. This allows the peripheral manufacturer to easily modify and transfer new code to current and new users. This on-chip memory eliminates the need for external memory.

The EZ-USB family supports high-bandwidth transfers by providing an efficient mechanism to move data between external memory and the USB FIFOs. Using this "turbo mode," the 8051 core can transfer 1024 bytes of data in or out of an isochronous FIFO in 338 microseconds. This leaves a high percentage of the bandwidth for the processor to service the application. The EZ-USB family also supports an equivalent data transfer rate for bulk packets of over 2 Mbytes per second, which is more than the USB bandwidth.

The EZ-USB family conforms to the high-speed (12 Mbps) requirements of USB Specification version 1.0, including support for remote wake-up. The internal SRAM replaces Flash memory, EEPROM, EPROM, or masked ROM that is conventionally used in other USB solutions.

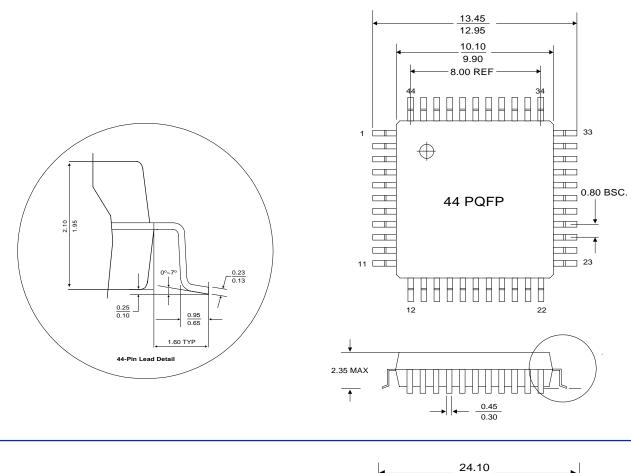

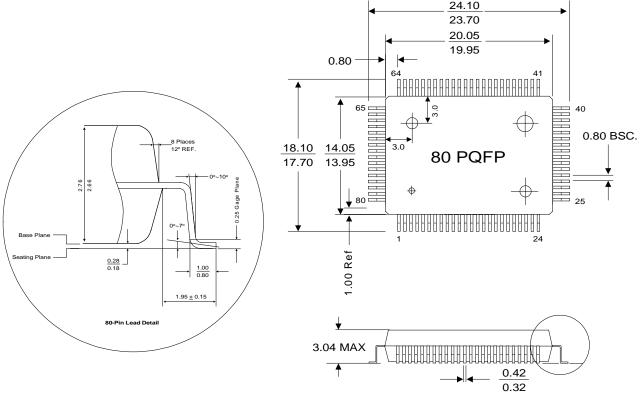

The EZ-USB family offers two packages, a 44 PQFP and an 80 PQFP. All EZ-USB devices are pin- and software-compatible. And, all RAM versions have ROM equivalents to allow easy migration for highvolume applications.

## **Features**

专业PCB打样工厂

捷多邦,

Single-chip, low-power solution for high-speed USB peripherals

,24小时加急出货

**ANCHOR**CHIPS

- · Firmware downloadable

- · High-performance I/O port

- Small board space (less than 1 square inch)

- 44 PQFP or 80 PQFP

- USB Specification 1.1

compliant

- Uses commercially-available 8051 software tools

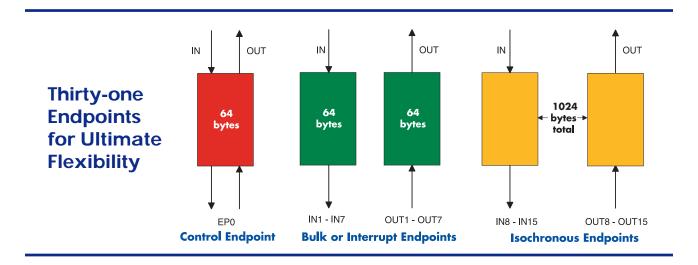

- · Thirty-one flexible endpoints

- All endpoints can be double buffered

- 4 or 8 Kbytes of memory

- Five times the speed of a standard 8051

- · Supports composite devices

- · I<sup>2</sup>C controller

- Supports isochronous, bulk, control, and interrupt data

- · On-chip PLL

## **EZ-USB Series 2100**

| AN2121SC | AN2321SC |

|----------|----------|

| AN2125SC | AN2325SC |

| AN2126SC | AN2326SC |

| AN2131SC | AN2331SC |

| AN2135SC | AN2335SC |

| AN2136SC | AN2336SC |

| AN2131QC | AN2331QC |

|          |          |

lf.dzsc.com

## **Complete USB Design Made Easy**

With the EZ-USB family, the peripheral designer gains two overall advantages: First, the design is much simpler because of the chip's significant integration and built-in flexibility. Second, the EZ-USB architecture reduces software code significantly over other USB solutions. This combination gives users a quick and easy path toward obtaining a working prototype.

Anchor Chips' EZ-USB family eliminates the need to become an expert in USB. It allows the designer to take advantage of the benefits of USB without investing large amounts of time and energy. With the EZ-USB family, peripheral designers can have USB traffic running within hours, instead of weeks as with other USB solutions.

The EZ-USB family of controllers simplifies the process of implementing USB hardware and software development for peripheral manufacturers. Lowlevel USB protocol requirements are automatically handled by the Anchor smart USB core and the included software utilities.

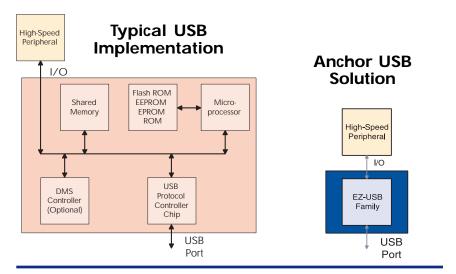

# How does Anchor Chips make USB easy?

A typical USB implementation uses nonvolatile memory (EPROM, EEPROM, Flash memory), a microprocessor, RAM, USB SIE and DMA. The EZ-USB family includes all the building blocks for a complete and lowcost USB solution in a single chip. The design is much simpler since timing and interface analysis are significantly reduced. The EZ-USB RAM architecture provides design and software flexibility. Its "soft" configuration enables peripheral manufacturers and designers to make changes to the USB device through software. This means complete flexibility with minimal design risks.

The EZ-USB family uses an intelligent USB core to simplify 8051 firmware code by as much as 80%. This reduces the firmware designer's need to develop code to handle the low-level nuances of the USB specification. The designer is free to concentrate on higher level functions. EZ-USB firmware development is quick, requiring less binary code and reducing the likelihood of errors.

With the EZ-USB family's software utilities and tools, firmware development is simplified and accelerated. Firmware can be tested independent of drivers, allowing the firmware developer and driver software developer to write code simultaneously. They do not need each other to verify and test code. This dual path decreases software development time.

| Features                                                 | Benefits                                                                                                                                                                                                                                                   |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-Chip Solution                                     | Lower overall system cost<br>Minimum board space with 44 PQFP and 80 PQFP packages<br>Quicker design and faster time to market than other USB solutions<br>Minimal design resources                                                                        |

| RAM Architecture                                         | Quick changes in firmware and driver code<br>Updates in the field via software downloads<br>Flexibility in multiple configurations<br>Dynamic changes in performance/properties based on user's needs                                                      |

| High-Performance I/O                                     | Transfers a full 1024-byte isochronous packet within one USB frame<br>Provides highest quality full-motion video or audio performance<br>Data I/O rate greater than 2 Mbyte/sec for bulk and isochronous packets<br>Fastest response time for the end user |

| 4- or 8-Kbyte<br>Pin- and Software-<br>Compatible Family | Easy transition from RAM to ROM for high-volume applications<br>Pin- and software-compatible options for program code growth<br>No change in hardware as needs change<br>Lowers system cost since only minimal memory size is needed                       |

| EZ-USB Firmware<br>Architecture                          | Significantly less 8051 USB code since core handles most USB activity<br>Shortened USB learning curve<br>Quicker working prototypes and final production models<br>More software development time to devote to the peripheral function                     |

| Enhanced 8051 Core                                       | Five times faster performance than 8051<br>No new 8051 software tools to learn                                                                                                                                                                             |

| Anchor USB Core/<br>ReNumeration<br>Capability           | External EPROM components eliminated<br>A quick path to working prototypes<br>User-selectable changes in peripheral properties without disconnecting                                                                                                       |

| EZ-USB Xcelerator<br>Development Kit                     | Speedier firmware and driver development<br>Independent development of firmware and driver<br>Fewer software errors<br>No custom Windows <sup>®</sup> driver needed to test USB traffic and firmware                                                       |

| Low 3.3V Power                                           | Meets the 100 mA power-up specification<br>Useful in bus-powered applications<br>Useful in power-sensitive applications such as battery-powered equipment                                                                                                  |

| Five External Interrupts                                 | Flexible without sacrificing standard 8051 interrupts                                                                                                                                                                                                      |

| Separate Memory<br>Expansion Port                        | Design flexibility in USB program code<br>No sacrifice in I/O capability for high-functionality peripheral devices<br>Non-multiplexed, requiring no external latch                                                                                         |

## **Unprecedented "Soft" Architecture**

# Soft Configuration

The focus of the EZ-USB family is to provide the peripheral designer a multitude of design configurations and migration paths. The "soft," programmable nature of the EZ-USB architecture provides flexibility while minimizing risks.

USB requires synchronization between four major technology suppliers: operating system, UHCI/OHCI interfaces, hub controllers, and peripheral devices. In a traditional hardware configuration, ensuring that a peripheral device will work with every combination of these technologies is a timeconsuming and expensive task.

Using the EZ-USB chip's "soft" configuration, the peripheral developer can easily devise workarounds or accommodate dynamic changes. At the same time, there is minimum risk to design implementation.

Peripheral manufacturers can provide firmware updates in conjunction with driver changes via a floppy disk or through Internet downloads. Thus, software device configurability provides easy field updates, last minute software code changes prior to production, or alterations due to ever-changing standards. In these ways, the EZ-USB chip makes development easier and guards against product obsolescence.

### **RAM Architecture**

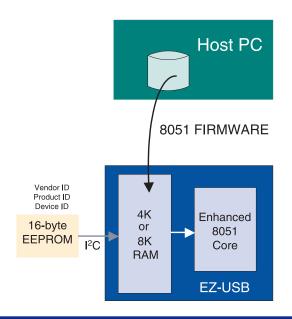

With an enhanced 8051 core combined with 4 or 8 Kbytes of SRAM in a single chip, users have a complete solution. The 8051's firmware can be stored in the hard disk (along with the driver) and downloaded into the peripheral during its initialization. That makes updates as easy as updating any other PC software.

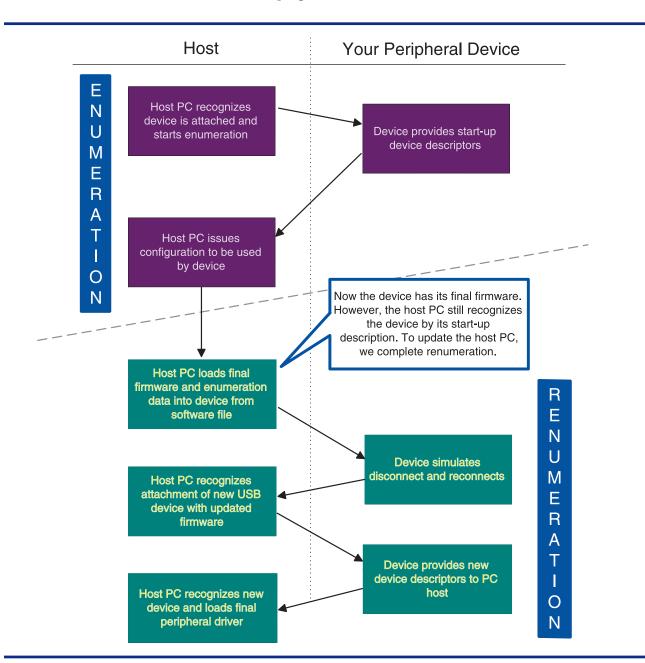

# Enumeration and ReNumeration

Anchor Chips' proprietary ReNumeration<sup>™</sup> function is the means by which the enhanced 8051 firmware is downloaded.

#### How It Works

Upon power-up or plug-in, the EZ-USB chip automatically enumerates as a default USB device. This allows the USB core to download 8051 code. The USB core logic inside EZ-USB performs this initial enumeration and code download while holding the 8051 in reset.

Once enumerated, the host PC downloads 8051 code into EZ-USB RAM over the USB interface. (Anchor Chips supplies the software tools to incorporate the loader into any application). The downloaded 8051 code contains program, data, and enumeration tables. Once loaded, the EZ-USB core performs a ReNumeration cycle to simulate a USB disconnect and reconnect to come back as a completely new USB device.

This entire sequence of enumeration, download and ReNumeration happens quickly (less than a quarter of a second) and is transparent to the user.

A USB hardware connection is simpler than current interface standards (ISA. PCI, serial, parallel, and SCSI). For example, there are no IRQs or DMAs to set. USB does not use direct connections like RS232 or **EPP** (Enhanced Parallel Port). Instead, USB is a packetized protocol similar to telecommunication standards such as X.25 or frame relay. This makes software development complex.

The EZ-USB chip family reduces the complexity of USB. It has a predefined default descriptor that causes it to function as a generic USB device. Very little code is required to operate the EZ-USB chip when configured in this default state. The default descriptor can be replaced as the peripheral manufacturer develops customized firmware.

### Four Major Benefits of Smart USB Core

The firmware code is smaller and more efficient than alternate USB solutions. In the EZ-USB family, the memory requirement is reduced by a factor of two to five times as compared to other solutions. And, since less memory is needed for firmware, board size and system cost are reduced. USB firmware development is faster since there is less code to write. This reduction in firmware allows the design team to concentrate more on software development for the peripheral function.

Fewer 8051 MIPs are dedicated to USB processing. With the EZ-USB family, as little as 10% of 8051 processing time is dedicated to USB. That makes 90% of the enhanced 8051 core's processing time available for peripheral functions. Alternate solutions dedicate more of their microcontroller bandwidth to USB processing.

The EZ-USB family handles most low-level USB overhead automatically. Therefore, the learning curve to understand all the nuances of USB is reduced, yielding fewer code errors and faster product development.

### **Efficient EZ-USB Code**

| Firmware<br>File Type | EZ-USB Family       | Alternate Solutions         |

|-----------------------|---------------------|-----------------------------|

| Source                | 730 lines of C code | 5445 lines of assembly code |

| Binary                | < 1 Kbyte           | > 5 Kbytes                  |

#### Test Code Supports:

- USB Chapter 9

- · String descriptors

- USB suspend/resume

- · Remote wake-up

- · Bulk endpoint loopback

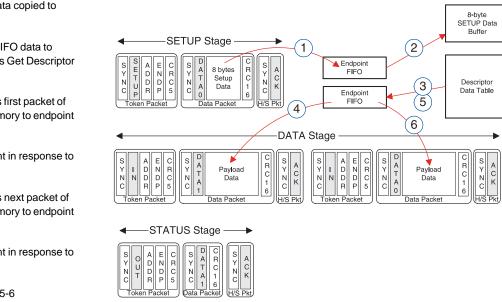

## Comparison of Standard USB Request "Get Descriptor"

**Conventional Method**

- (1) USB Setup data copied to FIFO

- (2) CPU copies FIFO data to RAM; decodes Get Descriptor request

- (3) CPU transfers first packet of data from memory to endpoint FIFO

- (4) FIFO data sent in response to USB IN token

- (5) CPU transfers next packet of data from memory to endpoint FIFO

- 6 FIFO data sent in response to USB IN token

- **7** Repeat steps 5-6

This diagram shows how conventional USB controllers handle a three-stage USB setup transaction called "Get Descriptor." The serial data flowing over the USB is shown as three stages: Setup, Data and Status. The numbered arrows indicate transfers between the USB, endpoint FIFOs, and microprocessor memory. Significant CPU overhead is required to transfer the data to and from the endpoint FIFOs (2,3,5) and to divide the descriptor table data into packets for transmission using multiple USB data packets (4,6).

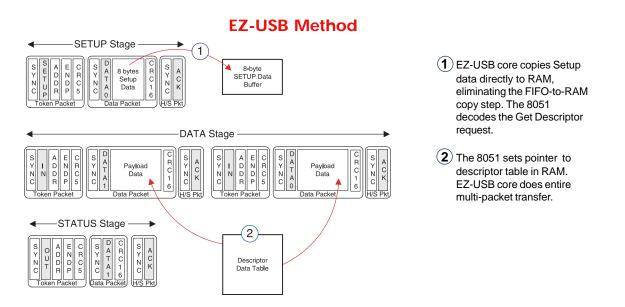

The EZ-USB core directly transfers setup packet data into a dedicated eight-byte Setup data buffer for CPU inspection (1). Then the 8051 loads an EZ-USB pointer with the start address of the requested descriptor data (2). The EZ-USB core does the rest. The EZ-USB core automatically takes care of error checking and retries, dividing the table into packets for the various IN transfers and responding to the Status stage.

The EZ-USB family provides the maximum performance specified for USB. This allows the peripheral manufacturer to take advantage of USB's full bandwidth in highspeed applications such as full-motion video, continuous audio, scanning, digital photography, and printing. To make full use of the USB bandwidth, the EZ-USB family has large endpoint buffers and a fast method for transferring data into and out of the buffers. With the EZ-USB architecture. bulk and isochronous endpoints can be configured as double-buffered with maximum packet sizes. With the 2-Kbyte FIFO, the EZ-USB family can transfer a 1024-byte isochronous packet within a single USB frame. Similarly for bulk endpoints, the EZ-USB can transfer data using the 64-byte double buffer capabilities at a data transfer rate of greater than 2 Mbytes per second.

Fast transfer rates can occur in and out of the internal FIFOs to external peripherals since the EZ-USB core automatically monitors 8051 transfers between the accumulator and the endpoint FIFO registers. When one of these transfers occurs, the EZ-USB core also reads or writes the FIFO data over the external data bus and provides external FIFO read and write strobes for the external interface.

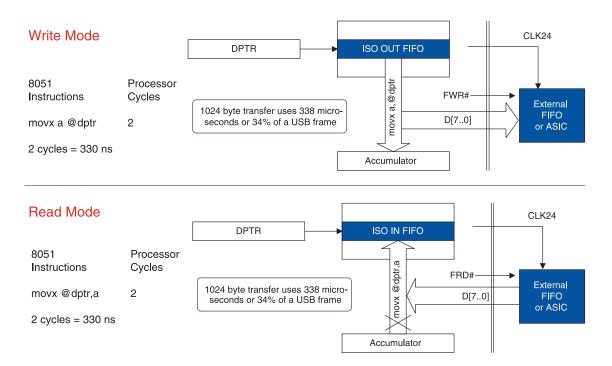

### Turbo Isochronous Capability

The EZ-USB family provides 1024 bytes of double-buffered FIFO memory (2048 bytes in all) which may be divided between 16 isochronous endpoints. During any one millisecond frame time, one of the FIFOs is connected to the USB and the other to the 8051. At every SOF (Start Of Frame), the buffers "ping-pong" so the 8051 can access the last frame's data while the other FIFO empties or fills with new USB data.

A single "movx" instruction transfers data between EZ-USB endpoint FIFOs and external logic in two cycles or 330 nano seconds.

Based on these connections a complete 1024-byte transfer can take 388 microseconds, less than 40% of the 1 ms USB frame time. This is an equivalent transfer rate of greater than 2 Mbytes per second.

### **Turbo Bulk Capability**

USB bulk endpoint data is available to the 8051 as 16 64-byte buffers in RAM. A special bulk data pointer allows this RAM data to also be accessed as a FIFO. The 8051 loads this sixteen-bit pointer with the address of a bulk buffer. Then, using a special data register, accesses the buffer data as if it were a FIFO. Every read or write to the data register increments the address pointer. This gives the 8051 a third data pointer: one that auto-increments.

As with the fast isochronous mode, the special data register uses the turbo mode that allows a byte of data to be transferred using a single "movx" instruction. Bulk transfers in and out of the 8051 therefore can be done with the speed of the isochronous transfers, one byte every two cycles (330 nanoseconds). This performance can generate well over the maximum allowable bulk packets within a USB frame.

## Data Flow for Turbo Performance

To write data to outside logic, the 8051 loads a data pointer with a USB FIFO register address, and then executes a "movx a,@dptr" instruction to move a byte from the FIFO to the 8051 accumulator. The EZ-USB core simultaneously broadcasts the FIFO data on the external data bus pins and generates the external write signal FWR# (Fast Write). A 24 MHz clock is provided for use as an external FIFO clock, if required. EZ-USB control bits allow the timing and polarity of the FWR# signal to be tailored for different external interface requirements.

To read data from outside logic, the 8051 loads a data pointer with a USB FIFO register address, and then executes a "movx @dptr,a" instruction to move a byte from the accumulator to the FIFO. The EZ-USB core discards the accumulator data and instead writes a byte from the external data bus pins to the FIFO. The EZ-USB core provides the external read signal FRD# (Fast Read) to strobe the data, and a 24 MHz clock. Like the FRW# signal, the FRD# signal may be tailored for different interface requirements.

#### A Leap in Performance with 8051 Compatibility

The enhanced 8051 processor increases performance by executing most instructions in four clock cycles instead of twelve, as in the standard 8051. The enhanced 8051 core also runs at 24 MHz; that's twice as fast as the standard part. These factors improve the execution rate for most instructions by a factor of five. The enhanced 8051 core contained in the EZ-USB family is binary-code compatible and performs the same functions as the industrystandard 8051. The effects of

instructions on bits, flags, and other status functions are identical to the standard 8051. The enhanced 8051 core also provides special function registers that support extra features such as a second data pointer, a second UART, cycle-stretched timing, an expanded interrupt system, and enhanced timers.

| Feature                         | Standard | Anchor |

|---------------------------------|----------|--------|

| Clocks per instruction cycle    | 12       | 4      |

| Data pointers                   | 1        | 2      |

| Serial ports (UARTs)            | 1        | 2      |

| 16-bit timers                   | 1        | 3      |

| Interrupt sources (int and ext) | 5        | 13     |

| Stretch memory cycles           | No       | Yes    |

| Nominal operating frequency     | 12 MHz   | 24 MHz |

| Nominal operating voltage       | 5 V      | 3.3 V  |

The EZ-USB architecture

includes features that give

the designer many options

tailored to the needs of an

effective design that is

application.

for creating an efficient and

### Options for Loading 8051 Firmware

The EZ-USB family provides the peripheral developer with four options for loading its 8051 firmware.

# Software file from the host system

Loading from a software file provides the maximum flexibility to the peripheral manufacturer. This configuration takes advantage of the internal 4K or 8K RAM to load 8051 code and data from the host system. Because of the ReNumeration capability of EZ-USB chips, a new set of descriptors can be loaded after the initial enumeration without physically disconnecting the device. This allows device descriptors and 8051 program code to be loaded from a driver disk. Only the vendor ID, product ID, and device ID need to be loaded during boot time in hardware through a 16byte EEPROM. Using this

configuration, users can implement a USB function in a tiny 44 PQFP package yielding a complete USB solution in less than one square inch of PC board space.

# EEPROM loaded through the I<sup>2</sup>C port

The EZ-USB architecture supports an external EEPROM load through the I<sup>2</sup>C bus. This gives designers the capability to load 8051 program code from hardware. Because of the flexibility of the external EEPROM and internal RAM, manufacturers have the option to make last-minute changes to a design/code without impacting production schedules.

# External memory through the memory expansion port

External memory may be added to EZ-USB family members in the 80-pin PQFP package. This memory is available through a memory expansion port. Separate 16-bit address and 8-bit data busses are also available to directly attach to a 64K EPROM, SRAM, or Flash memory. Unlike a standard 8051, the address and memory ports are not multiplexed, eliminating the need for glue logic for connection to external memory.

#### Internal ROM for peripheral manufacturers who migrate to the ROM-based EZ-USB chip

EZ-USB ROM options are software and pin compatible to RAM members of the family. Therefore, high-volume customers can move easily to ROM when their 8051 firmware code is solidified.

## Loading 8051 Firmware from the Host

### More Endpoint Buffer Memory

The EZ-USB chip supports more endpoints and provides more endpoint buffer memory than any other USB-device solution in the market. The USB specification describes an endpoint as a source or sink of data. In the EZ-USB chip, endpoints are constructed as RAM (bulk, control, interrupt endpoints) or FIFOs (isochronous endpoints). With support for 31 endpoints (the maximum in the USB specification), it gives the peripheral designer ultimate flexibility. Unlike other USB peripheral alternatives, the EZ-USB architecture also supports the maximum packet size for each endpoint. Thus 64-byte packets are available for all control, bulk, and interrupt endpoints. Isochronous endpoints are double buffered with a packet size of up to 1024 bytes, the maximum allowable under the USB specification.

#### Control

The EZ-USB family supports one control endpoint. To simplify firmware programming, the EZ-USB chip provides data from control transfers in two separate buffers. It also has a unique capability to manage the threephase transfer in hardware, relieving device firmware from this task.

#### **Bulk/Interrupt**

Bulk endpoints are used when data integrity must be guaranteed, but without critical delivery time. The EZ-USB family provides 14 bulk endpoints: seven IN and seven OUT. These endpoints can be programmed to be doublebuffered, which improves transfer bandwidth in some applications. Bulk data is accessible as RAM or FIFO data. The IN and OUT endpoints can also be used as interrupt endpoints.

#### Isochronous

These endpoints support streaming data such as audio or video. The EZ-USB family supports 16 isochronous endpoints: eight IN and eight OUT. A pool of FIFOs can be allocated among the endpoint to a maximum of 1 Kbyte. Isochronous endpoints are double-buffered, as required by the USB specification, so the actual size of iscochronous buffer memory is 2 Kbytes.

### Low Power—Even for Bus-Powered Devices

The EZ-USB family meets the tough power specifications of USB. Running off of a 3.3V power supply, it can accommodate buspowered devices and self-powered peripherals. In addition, with a 50 mA current draw under full operating conditions, the EZ-USB family provides current headroom for peripheral functions. This meets the USB requirement of 100 mA maximum current for attached peripherals prior to configuration. Total maximum power required by an EZ-USB chip under active conditions is 170 mW. Other solutions require five times more power.

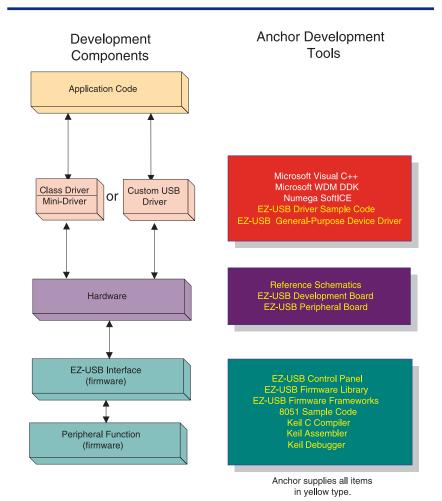

## **EZ-USB Series 2100 Xcelerator Development Kit**

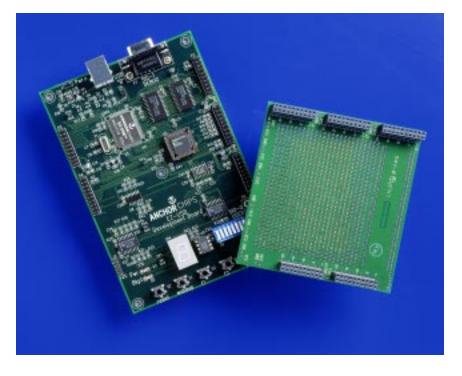

The EZ-USB Xcelerator<sup>™</sup> development kit provides a complete hardware and software solution for accelerating the firmware and device driver development for all the members of the EZ-USB family. Other USB development kits use emulation of the eventual USB device. The EZ-USB Xcelerator developer kit uses the actual device, the AN2131QC, during the entire development. Because of the simplicity of EZ-USB and Anchor's software utilities, users can be up and running USB code in hours, not weeks!

#### **Development Board**

The EZ-USB Xcelerator development board is compact and powerful. It provides an AN2131QC, 64 kilobytes of external RAM, two UARTS, and user-programmable seven segment display, LED indicators, and switches. One UART is used to communicate with the Windows-hosted debugger, and the other is free for application use. The indicators and switches are connected via the EZ-USB I2C port, leaving all AN2131QC I/O lines uncommitted for prototype development. The board can be USB bus powered, eliminating the need for an external power supply. A debug monitor loads either into internal EZ-USB RAM or the external RAM. The external RAM can be configured in various ways to allow seamless code development for EZ-USB ROM versions.

A matching plug-in breadboard eases the interface of custom circuitry to the AN2131. Headers bring out all interface signals, and provide a convenient interface to a logic analyzer.

### **C** Compiler from Keil

The C compiler from Keil Software lets the designer write 8051 microcontroller applications in C and still get the efficiency and speed of assembly language. Advanced features from Keil tools include the ability to single step through code. This makes it easy to detect errors, handle source level debugging and dual-data pointer support, and set breakpoints. With the ability to debug code one line at a time, quickly compile and one-step download new code, developers' have a more efficient means to complete firmware faster than using emulators.

### **Anchor Utilities**

Anchor Chips provides the best tools to accelerate the developer's firmware development. The USB Control Panel allows the developer to send and receive interrupt, bulk, and isochronous packets and standard USB device requests without first developing the hostbased driver for the specific application. The USB Control Panel provides manual control of USB host controller response. It can be used to test a multitude of operating conditions without first learning low-level USB programming. The user can quickly test different packet sizes and emulate USB host application responses. In addition, users can quickly test and adjust firmware based on immediate results from the USB Control Panel.

Also in the EZ-USB development kit is the EZ-USB 8051 firmware library and firmware frameworks. With this library of predefined function calls, developers can quickly develop their peripheral function. The firmware library includes functions such as ReNumeration, I<sup>2</sup>C programming, descriptor table parsing, USB initialization, device initialization, suspend/resume and complete USB standard device request processing.

### **Device Driver**

A general-purpose device driver is included in the Xcelerator development kit. It is a WDM driver for Windows 98 or OSR 2.1. With source code provided, peripheral driver developers can convert this code to a miniport driver to meet their unique needs.

The EZ-USB Series 2100

## Xcelerator Development Kit (AN2131-DK-001)

- · EZ-USB Development Board

- · EZ-USB Peripheral Board

- · EZ-USB Firmware Library and Firmware Frameworks

- · EZ-USB General-Purpose Device Driver

- EZ-USB Driver and Firmware Sample Code

- EZ-USB Control Panel

- EZ-USB Documentation

- Reference Schematics

- 8051 C Compiler from Keil Software

- 8051 Assembler from Keil Software

- · 8051 Custom Debugger from Keil Software

# Packages and Pin Definitions

| Input/Output                         |                         |        |             |

|--------------------------------------|-------------------------|--------|-------------|

| 2125SC<br>2126SC<br>2135SC<br>2136SC | <b>2121SC</b><br>2131SC | 2131QC | Name        |

|                                      |                         | 68     | PA0/T0out   |

|                                      |                         | 69     | PA1/T1out   |

|                                      |                         | 70     | PA2/OE#     |

|                                      |                         | 71     | PA3/CS#     |

| 39                                   | 39                      | 73     | PA4/FWR#    |

| 40                                   | 40                      | 74     | PA5/FRD#    |

|                                      |                         | 75     | PA6/RxD0out |

|                                      |                         | 76     | PA7/RxD1out |

|                                      | 24                      | 44     | PB0/T2      |

|                                      | 25                      | 45     | PB1/T2EX    |

|                                      | 26                      | 46     | PB2/RxD1    |

|                                      | 27                      | 47     | PB3/TxD1    |

|                                      | 28                      | 52     | PB4/INT4    |

|                                      | 29                      | 53     | PB5/INT5#   |

|                                      | 30                      | 54     | PB6/INT6    |

|                                      | 31                      | 55     | PB7/T2out   |

| 14                                   | 14                      | 30     | PC0/RxD0    |

| 15                                   | 15                      | 31     | PC1/TxD0    |

| 16                                   | 16                      | 32     | PC2/INT0#   |

| 17                                   | 17                      | 33     | PC3/INT1#   |

| 18                                   | 18                      | 38     | PC4/T0      |

| 19                                   | 19                      | 39     | PC5/T1      |

| 20                                   | 20                      | 40     | PC6/WR#     |

| 21                                   | 21                      | 41     | PC7/RD#     |

|   | Power and Ground                  |                                     |                                                      |      |

|---|-----------------------------------|-------------------------------------|------------------------------------------------------|------|

|   | 7                                 | 7                                   | 18                                                   | AGND |

|   | 10                                | 10                                  | 21                                                   | AVCC |

| 6 | , 3, 4, 5,<br>, 12, 23,<br>34, 38 | 1, 3, 4, 5,<br>6, 12, 23,<br>34, 38 | 3, 5, 6, 13,<br>14, 17, 23,<br>43, 56, 63,<br>72, 78 | GND  |

|   | 11, 22,<br>33, 44                 | 11, 22,<br>33, 44                   | 2, 22,<br>42, 62                                     | VCC  |

| Address                                     |                         |        |         |  |

|---------------------------------------------|-------------------------|--------|---------|--|

| <b>2125SC</b><br>2126SC<br>2135SC<br>2136SC | <b>2121SC</b><br>2131SC | 2131QC | Name    |  |

|                                             |                         | 7-12   | A0-A5   |  |

|                                             |                         | 15, 16 | A6, A7  |  |

|                                             |                         | 26-29  | A8-A11  |  |

|                                             |                         | 34-37  | A12-A15 |  |

| Databus |  |       |       |

|---------|--|-------|-------|

| 24-27   |  | 48-51 | DO-D3 |

| 28-31   |  | 57-60 | D4-D7 |

| Special |    |    |         |  |

|---------|----|----|---------|--|

| 32      | 32 | 61 | ВКРТ    |  |

| 2       | 2  | 4  | CLK24   |  |

| 43      | 43 | 1  | DISCON# |  |

|         |    | 80 | PSEN#   |  |

| 8       | 8  | 19 | XIN     |  |

| 9       | 9  | 20 | XOUT    |  |

|         |    | 24 | EA      |  |

| 13      | 13 | 25 | RESET   |  |

| 37      | 37 | 66 | WAKEUP# |  |

| USB I/O |    |    |       |

|---------|----|----|-------|

| 41      | 41 | 77 | USBD- |

| 42      | 42 | 79 | USBD+ |

|    |              | I <sup>2</sup> C |     |  |  |  |

|----|--------------|------------------|-----|--|--|--|

| 36 | 36 36 65 SCL |                  |     |  |  |  |

| 35 | 35           | 64               | SDA |  |  |  |

## **Ordering Information**

With the broadest family of USB solutions in the market, peripheral manufactures can find the right combination of features, board space, and price to fit their applications. All eight of EZ-USB family members with internal RAM can be converted to ROM equivalents with no changes in their design.

| EZ-USB Internal RAM Product Family |                 |             |                       |                |                  |                        |

|------------------------------------|-----------------|-------------|-----------------------|----------------|------------------|------------------------|

| Part<br>Number                     | Package<br>Type | RAM<br>Size | I/O Rate<br>Bytes/sec | # Prog<br>I/Os | 8-Bit<br>Databus | lsochronous<br>Support |

| AN2121SC                           | 44 PQFP         | 4K          | 600K                  | 16             | No               | Yes                    |

| AN2125SC                           | 44 PQFP         | 4K          | 2M                    | 8              | Yes              | Yes                    |

| AN2126SC                           | 44 PQFP         | 4K          | 2M                    | 8              | Yes              | No                     |

| AN2131SC                           | 44 PQFP         | 8K          | 600K                  | 16             | No               | Yes                    |

| AN2135SC                           | 44 PQFP         | 8K          | 2M                    | 8              | Yes              | Yes                    |

| AN2136SC                           | 44 PQFP         | 8K          | 2M                    | 8              | Yes              | No                     |

| AN2131QC                           | 80 PQFP         | 8K          | 2M                    | 24             | Yes+Addr         | Yes                    |

### **EZ-USB Internal ROM Product Family**

| Part<br>Number | Package<br>Type | RAM<br>Size | ROM<br>Size | I/O Rate<br>Bytes/sec | # Prog<br>I/Os | 8-Bit<br>Databus | Isochronous<br>Support |

|----------------|-----------------|-------------|-------------|-----------------------|----------------|------------------|------------------------|

| AN2321SC       | 44 PQFP         | 2K          | 4K          | 600K                  | 16             | No               | Yes                    |

| AN2325SC       | 44 PQFP         | 2K          | 4K          | 2M                    | 8              | Yes              | Yes                    |

| AN2326SC       | 44 PQFP         | 2K          | 4K          | 2M                    | 8              | Yes              | No                     |

| AN2331SC       | 44 PQFP         | 2K          | 8K          | 600K                  | 16             | No               | Yes                    |

| AN2335SC       | 44 PQFP         | 2K          | 8K          | 2M                    | 8              | Yes              | Yes                    |

| AN2336SC       | 44 PQFP         | 2K          | 8K          | 2M                    | 8              | Yes              | No                     |

| AN2331QC       | 80 PQFP         | 2K          | 8K          | 2M                    | 24             | Yes+Addr         | Yes                    |

"C" denotes commercial (0 - 70 degrees C) temperature range

All EZ-USB devices support up to 14 endpoints for bulk packets.

EZ-USB Xcelerator Development Kit

AN2131-DK-001

For more information about the EZ-USB controller chip, visit www.anchorchips.com.

Anchor Chips Incorporated 12396 World Trade Drive • M/S 212 • San Diego, CA 92128 Telephone (858) 613-7900 • Fax (858) 676-6896 www.anchorchips.com

**Cypress Semiconductor** 3901 North First Street • San Jose, CA 95134 Telephone (800) 858-1810 • Fax (408) 943-6848 www.cypress.com

EZ-USB, Xcelerator, and ReNumeration are trademarks of Anchor Chips Incorporated. The Anchor logo is a registered trademark of Anchor Chips Incorporated. Cypress and the Cypress logo are trademarks of Cypress Semiconductor. All other tradesmark are the property of their respective owners. Specifications are subject to change without notice. © 1999, Anchor Chips Incorporated All rights reserved. 2-799EZ21K