# SKÝWORKS"

#### **DATA SHEET**

# CX74063-3x: RF Transceiver with Power Ramping Controller and Integrated Crystal Oscillator with 13 MHz Output for Multi-Band GSM, GPRS, and EDGE Applications

#### **APPLICATIONS**

- GSM850, EGSM900, DCS1800, and PCS1900 handsets

- GPRS handsets and modules

- EDGE downlink support

#### **FEATURES**

- Direct down-conversion receiver eliminates the external image reject/IF filters

- Three separate LNAs with single-ended inputs

- RF gain range: GSM = 20 dB, DCS = 22 dB,

PCS = 20 dB. Baseband gain range = 100 dB

- Gain selectable in 2 dB steps

- Integrated receive baseband filters with tunable bandwidth

- Integrated DC offset correction sequencer

- Reduced filtering requirements with translational loop transmit architecture

- Integrated transmit VCOs

- · Wide RF range for quad band operation

- Integrated PAC loop

- Single integrated, fully programmable fractional-N synthesizer suitable for multi-slot GPRS operation

- Fully integrated wideband Ultra High Frequency (UHF) VCO

- Integrated crystal oscillator

- Separate enable lines for power management transmit, receive, and synthesizer modes

- Supply voltage down to 2.6 V

- Band select and front-end enable states may be exercised on output pins to control external circuitry.

- Low external component count

- Optional bypass of baseband filtering for use with high dynamic range Analog to Digital Converters (ADCs) for current savings

- Interfaces to low dynamic range ADC

- Meets AM suppression requirements without baseband interaction.

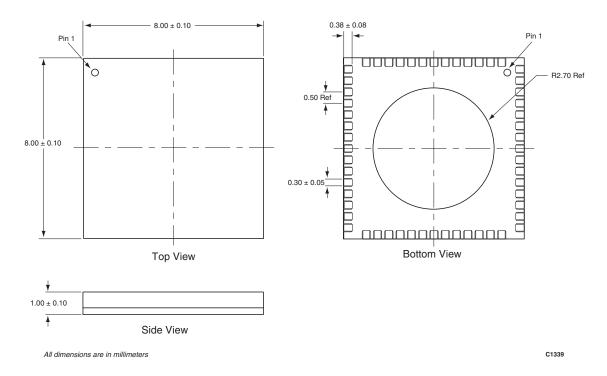

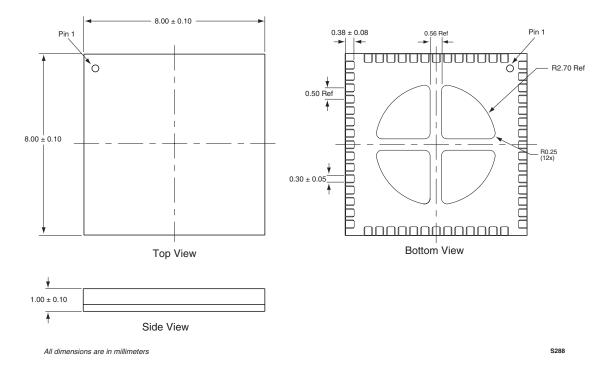

- 56-pin RFLGA 8x8 mm package (low temperature option, CX74063-34; high temperature option, CX74063-35 and CX74063-36)

- Low power standby mode

#### **DESCRIPTION**

The CX74063-3x transceiver (including -34, -35, and -36 package options) is a highly integrated device for multi-band Global System for Mobile Communications<sup>TM</sup> (GSM<sup>TM</sup>) or General Packet Radio Service (GPRS) applications. The device requires a minimal number of external components to complete a GSM radio subsystem. The CX74063-3x supports GSM850, EGSM900, DCS1800, and PCS1900 applications. The receiver also supports downlink Enhanced Data-Rate GSM Evolution (EDGE).

The receive path implements a direct down-conversion architecture that eliminates the need for Intermediate Frequency (IF) components. The CX74063-3x receiver consists of three integrated Low Noise Amplifiers (LNAs), a quadrature demodulator, tunable receiver baseband filters, and a DC-offset correction sequencer.

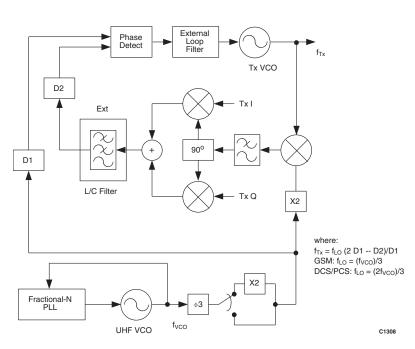

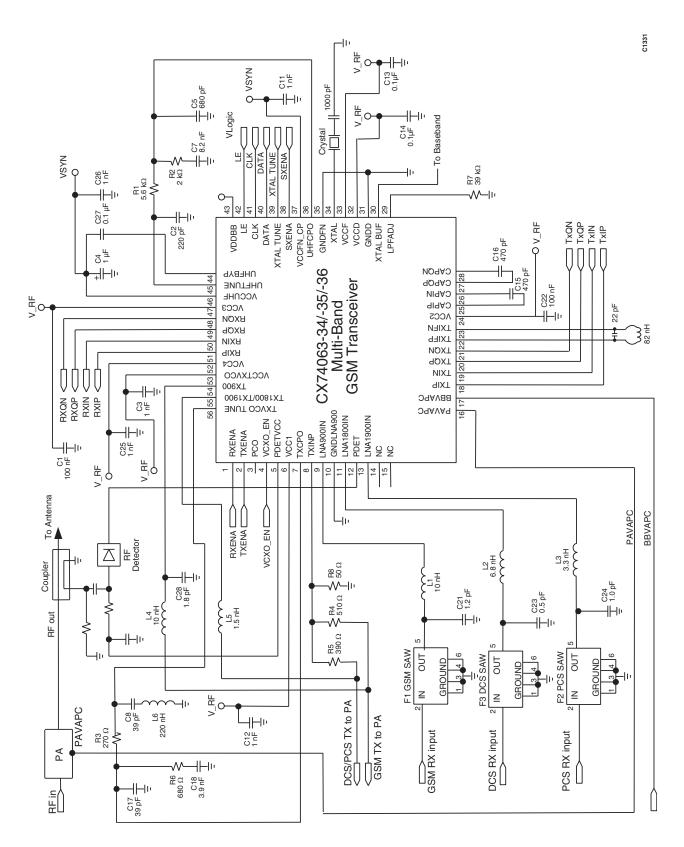

In the transmit path, the device consists of an In-phase and Quadrature (I/Q) modulator within a frequency translation loop designed to perform frequency up-conversion with high output spectral purity. This loop also contains a phase-frequency detector, charge pump, mixer, programmable dividers, and high power transmit Voltage Controlled Oscillators (VCOs) with no external tank required. With the integrated gain controller (and an integrator), the device realizes the Power Amplifier Control (PAC) functionality when combined with a coupler, a Radio Frequency (RF) detector and a Power Amplifier (PA).

The CX74063-3x also features an integrated, fully programmable, sigma-delta fractional-N synthesizer suitable for GPRS multi-slot operation. Except for the loop filter, the frequency synthesizer function, including a wideband VCO, is completely on-chip. The reference frequency for the synthesizer is supplied by the integrated crystal oscillator circuitry.

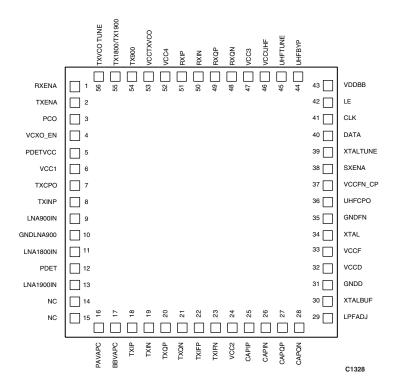

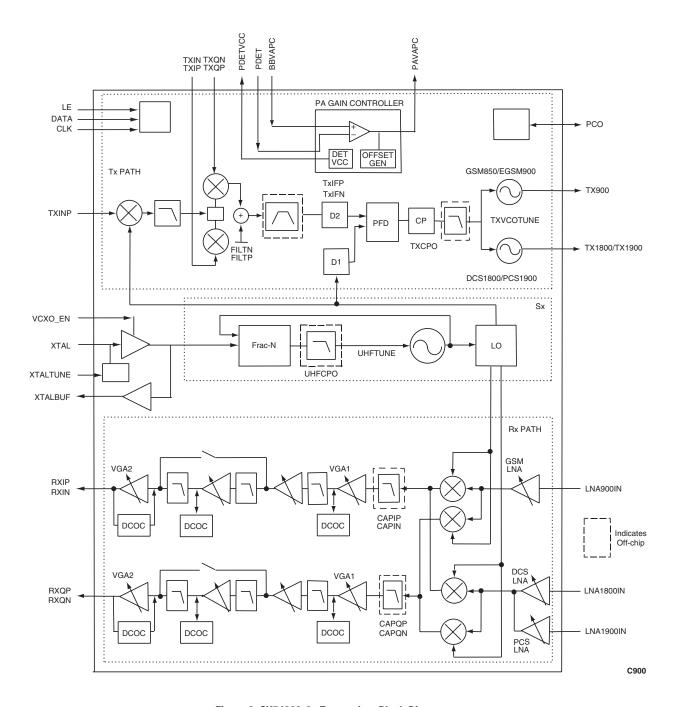

The 56-pin 8x8 RF Land Grid Array (RFLGA<sup>TM</sup>) device package and pin configuration are shown in Figure 1. A functional block diagram is shown in Figure 2. Signal pin assignments, functional pin descriptions, and equivalent circuitry are provided in Table 1.

Figure 1. CX74063-3x Pinout – 56-Pin RFLGA (8 x 8 mm) (Top View)

Figure 2. CX74063-3x Transceiver Block Diagram

Table 1. CX74063-3x Signal Descriptions (1 of 5)

| Pin# | Name     | Description                            | <b>Equivalent Circuit</b>              |

|------|----------|----------------------------------------|----------------------------------------|

| 1    | RXENA    | Receiver enable input                  |                                        |

| 2    | TXENA    | Transmitter enable input               |                                        |

| 3    | PCO      | Bi-directional band select             |                                        |

| 4    | VCXO_EN  | VCXO enable pin                        |                                        |

| 5    | PDETVCC  | Bias for the RF Detector               | Vref                                   |

| 6    | VCC1     | LNA and TX charge pump supply          | VCC1                                   |

| 7    | TXCP0    | Translational loop charge pump output  |                                        |

| 8    | TXINP    | Translational loop feedback input      |                                        |

| 9    | LNA900IN | Low band LNA input for GSM850, EGSM900 | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

Table 1. CX74063-3x Signal Descriptions (2 of 5)

| Pin# | Name      | Description                          | <b>Equivalent Circuit</b>                     |

|------|-----------|--------------------------------------|-----------------------------------------------|

| 10   | GNDLNA900 | Low band LNA emitter ground          |                                               |

| 11   | LNA1800IN | DCS LNA input                        |                                               |

| 12   | PDET      | Feedback Input to power control loop |                                               |

| 13   | LNA1900IN | PCS LNA input                        | <b>○</b> ──────────────────────────────────── |

| 14   | NC        | No connect                           | No connect                                    |

| 15   | NC        | No connect                           | No connect                                    |

| 16   | PAVAPC    | PA control output                    | Vout                                          |

| 17   | BBVAPC    | PA control Baseband input            |                                               |

Table 1. CX74063-3x Signal Descriptions (3 of 5)

| Pin# | Name    | Description                                             | <b>Equivalent Circuit</b> |

|------|---------|---------------------------------------------------------|---------------------------|

| 18   | TXIP    | TX I baseband input positive                            |                           |

| 19   | TXIN    | TX I baseband input negative                            | •                         |

| 20   | TXQP    | TX Q baseband input positive                            |                           |

| 21   | TXQN    | TX Q baseband input negative                            |                           |

| 22   | TXFP    | TX IF filter output positive                            |                           |

| 23   | TXFN    | TX IF filter output negative                            |                           |

| 24   | VCC2    | RX mixer and TX loop supply                             | VCC2                      |

| 25   | CAPIP   | Capacitor filter I positive                             |                           |

| 26   | CAPIN   | Capacitor filter I negative                             | 9_1                       |

| 27   | CAPQP   | Capacitor filter Q positive                             |                           |

| 28   | CAPQN   | Capacitor filter Q negative                             |                           |

| 29   | LPFADJ  | LPF frequency setting resistor                          |                           |

| 30   | XTALBUF | Crystal oscillator buffer output                        |                           |

| 31   | GNDD    | Synthesizer digital ground                              |                           |

| 32   | VCCD    | Synthesizer digital supply                              | VCCD                      |

| 33   | VCCF    | Synthesizer analog supply and crystal oscillator supply | VCCF                      |

| 34   | XTAL    | Crystal input                                           |                           |

Table 1. CX74063-3x Signal Descriptions (4 of 5)

| Pin# | Name     | Description                         | <b>Equivalent Circuit</b> |

|------|----------|-------------------------------------|---------------------------|

| 35   | GNDFN    | Synthesizer analog ground           |                           |

| 36   | UHFCPO   | Synthesizer charge pump output      |                           |

| 37   | VCCFN_CP | Synthesizer charge pump supply      | VCCFN_CP                  |

| 38   | SXENA    | Synthesizer enable input            |                           |

| 39   | XTALTUNE | Crystal oscillator varactor control | •-W                       |

| 40   | DATA     | Serial bus data input               | <b>A</b>                  |

| 41   | CLK      | Serial bus clock input              |                           |

| 42   | LE       | Serial bus latch enable input       |                           |

| 43   | VDDBB    | Digital CMOS supply                 | VDDBB                     |

| 44   | UHFBYP   | Bypass capacitor for UHF VCO        |                           |

| 45   | UHFTUNE  | UHF VCO control input               |                           |

| 46   | VCCUHF   | UHF VCO supply                      | VCCUHF                    |

| 47   | VCC3     | LO chain supply                     | VCC3                      |

| Pin# | Name          | Description                     | <b>Equivalent Circuit</b> |

|------|---------------|---------------------------------|---------------------------|

| 48   | RXQN          | Receiver output Q negative      |                           |

| 49   | RXQP          | Receiver output Q positive      |                           |

| 50   | RXIN          | Receiver output I negative      |                           |

| 51   | RXIP          | Receiver output I positive      |                           |

| 52   | VCC4          | Baseband supply                 | VCC4                      |

| 53   | VCCTXVC0      | Transmit VCO supply             | VCCTXVC0                  |

| 54   | TX900         | Low band transmit VCO           |                           |

| 55   | TX1800/TX1900 | DCS and PCS transmit VCO output |                           |

| 56   | TXVCOTUNE     | Transmit VCO control input      |                           |

Table 1. CX74063-3x Signal Descriptions (5 of 5)

#### **Technical Description**

The CX74063-3x transceiver contains the following sections, as shown in Figure 2.

- Receive section. Includes three integrated LNAs, a

quadrature demodulator section that performs direct down

conversion, baseband amplifier circuitry with I/Q outputs,

and three stages of DC offset correction. The receiver can

be calibrated to optimize IP2 performance.

- Synthesizer section. Includes an integrated on-chip VCO locked by a fractional-N synthesizer loop, and a crystal oscillator to supply the reference frequency.

- Transmit section. The TX path is a translational loop architecture consisting of an I/Q modulator, integrated high power VCOs, offset mixer, programmable divider, PFD, and charge pump. The device also provides integrated gain controller for the PAC loop, plus the bias generator for an external diode detector.

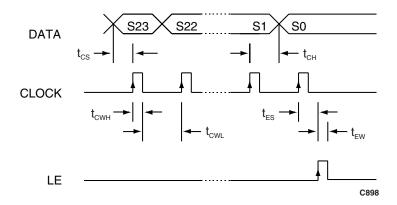

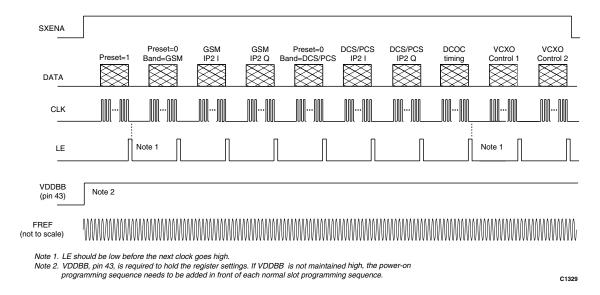

A 3-wire serial interface controls the transceiver and synthesizer. The receiver gain control, as well as the division ratios and charge pump currents in the synthesizer and transmitter, can be programmed using 24-bit words. These 24-bit words are programmed using the 3-wire input signals CLK, DATA, and LE. To ensure that the data stays latched in power down mode, pin 43 (VDDBB) must be continuously supplied with voltage. This pin is provided for the digital sections to allow power supply operation compatible with modern digital baseband devices.

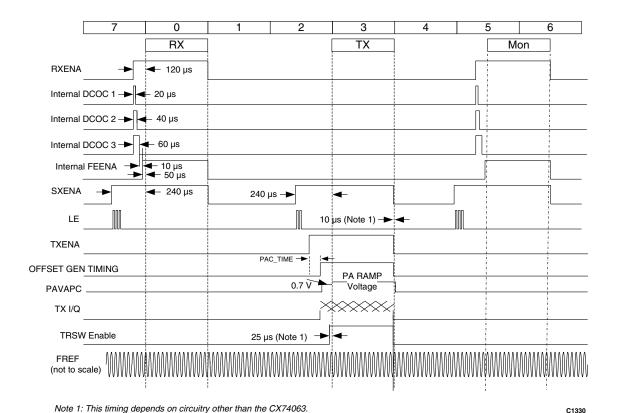

The TXENA, RXENA, and SXENA signals separately enable the CX74063-3x transmitter, receiver, and synthesizer sections.

TXENA and RXENA should be held low during programming. SXENA should be held high during the programming of the R3 IP2 Calibration Register. (These timing signals are detailed in Figures 9, 10, and 11.)

#### **Receive Section**

#### **LNA and Quadrature Demodulator**

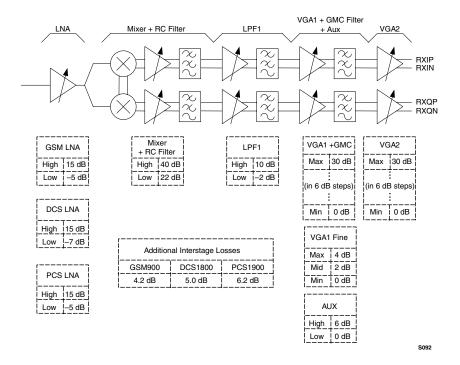

Three separate LNAs are integrated to address different bands of operation. These LNAs have separate single-ended inputs, which are externally matched to 50  $\Omega$ . The gain is switchable between high (i.e., 15 dB typical) and low (i.e., –5 dB GSM, –7 dB DCS, and –5 dB PCS typical) settings. The LNA outputs feed into a quadrature demodulator that downconverts the RF signals directly to baseband. Two external 470 pF capacitors are required at the demodulator output to suppress the out-of-band blockers.

#### **Baseband Section**

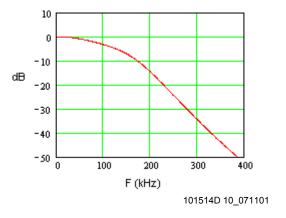

An off-chip capacitor and three fixed poles of on-chip, low pass filtering provide rejection of strong in- and out-of-band interferers. In addition, a tunable, four-pole gmC filter provides rejection of the adjacent channel blockers. Incorporated within the fixed-pole filters are two switchable gain stages of 18 dB and 12 dB gain steps, respectively. There is an additional programmable gain amplifier with a gain range from 0 to + 34 dB, selectable in 2 dB steps in the four-pole tunable filter. The final filter output feeds an amplifier with a gain range from 0 to 30 dB, selectable in 6 dB steps.

There is an additional gain stage on the four-pole tunable filter output, the auxiliary gain stage, selectable at 0 dB or + 6 dB.

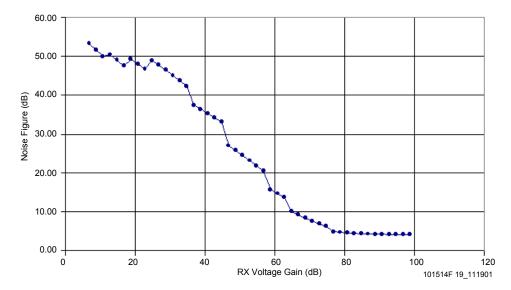

The gain control ranges are shown in Figure 3.

Recommended combinations of individual block gain settings are shown in Table 22 for GSM900, Table 23 for DCS1800, and Table 24 for PCS1900.

For added baseband interface flexibility, the four-pole filter, its associated Variable Gain Amplifier (VGA), and DC offset correction loop can be bypassed and turned off for current savings.

In Table 2 the typical locations of all eight receiver baseband poles are given. The final four poles are produced by the tunable gmC filter, as set by the external resistor (recommended value is 39.2 k $\Omega$ , 1%) placed from pin 29 to ground.

For these tunable poles, Table 2 gives the pole location as a function of this resistor.

#### **DC Offset Correction**

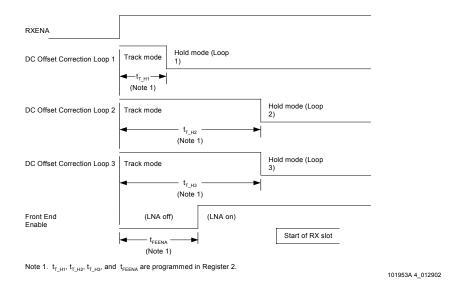

Three DC offset correction (DCOC) loops ensure that DC offsets, generated in the CX74063-3x, do not overload the baseband chain at any point. After compensation, the correction voltages are held on capacitors for the duration of the receive slot(s). Internally, on-chip timing is provided to generate the track and hold (T\_H) signals for the three correction loops.

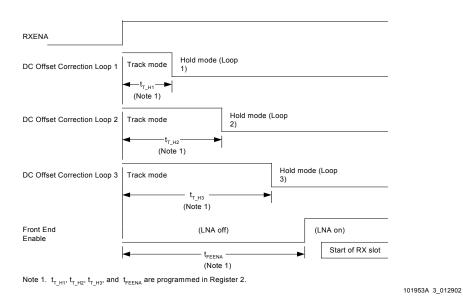

The timing diagram for the DC offset correction sequence with reference to the receive slot is shown in Figure 4. A rising edge on either the RXENA signal, selected via the serial interface, places the DC compensation circuitry in the track mode.

The timing parameters for each of the three compensation loops,  $t_{\text{LH1}}$ ,  $t_{\text{LH2}}$ , and  $t_{\text{LH3}}$ , and the time between compensation start and the LNA being turned on,  $t_{\text{FEENA}}$ , are defined via an internal state machine. The state machine is preprogrammed with fixed default values, but may be readjusted via the serial interface.

The timing parameters for the three compensation loops and the LNA power-up are each independently defined, relative to the compensation start. Therefore, they may be programmed to occur in any order, but the sequences shown in Figure 4 and Figure 5 are recommended. The device default timing is shown in Figure 5, with a total time of 60  $\mu s$ . Individual default timings are given in Table 17. For user-programmed timing, the total time may be set as short as approximately 10  $\mu s$  when FREF has a 13 MHz clock applied. However, the shortest recommended total time is approximately 30  $\mu s$ , since at the highest gain settings, the resulting DC may degrade as correction time is reduced.

#### **AM Suppression and IP2 Calibration**

For direct conversion GSM applications, it is imperative to have extremely low second-order distortion. Mathematically, second-order distortion of a constant tone generates a DC-term proportional to the square of the amplitude. A strong interfering amplitude-modulated (AM) signal is therefore demodulated by second-order distortion in the receiver front end, and generates an interfering baseband signal.

| T        |            | D . I . I |           |

|----------|------------|-----------|-----------|

| i able a | 2. Receive | Pole I    | Locations |

| Stage             | Typical Pole Location (rad/sec)                                                                          | Pole Type                                                 |

|-------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Mixer + RC Filter | $-1.0 \times 10^6$                                                                                       | Real (capacitors at pins 25-26 and 27-28 fixed at 470 pF) |

|                   | −1.65 x 10 <sup>6</sup>                                                                                  | Real                                                      |

| LPF1              | $(-0.91 \text{ x } 10^6) \pm \text{j} (1.35 \text{ x } 10^6)$                                            | Conjugate                                                 |

| VGA1 + gmC filter | $(-0.91 \text{ x } 10^6) \text{ x } (39.2 \text{ k}\Omega/\text{R})$                                     | Real (adjust with resistor at pin 29)                     |

|                   | $(-0.91 \text{ x } 10^6) \text{ x } (39.2 \text{ k}\Omega/\text{R})$                                     | Real (adjust with resistor at pin 29)                     |

|                   | $[(-0.46 \text{ x } 10^6) \pm \text{j}(1.0 \text{ x } 10^6)] \text{ x } (39.2 \text{ k}\Omega/\text{R})$ | Conjugate (adjust with resistor at pin 29)                |

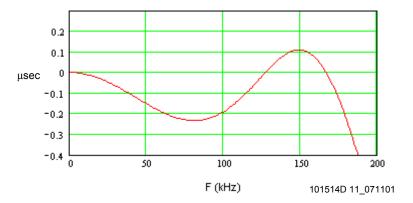

Figure 3. Gain Control Settings

Figure 4. DC Offset Correction Timing (LNA Off During All of the DC Offset Correction Sequence)

Figure 5. DC Offset Correction Timing (LNA On During Part of the DC Offset Correction Sequence)

A commonly used measure for receiver second-order distortion is the second-order intercept point, IP2. For example, to ensure that the unwanted baseband signals are 9 dB below the wanted signal required under the AM suppression test for type approval (see 3GPP TS 51.010-1), an input IP2 of 43 dBm is required:

The CX74063-3x receiver includes a circuit that minimizes second-order distortion. This IP2 calibration circuit effectively compensates any second-order distortion in the receive chain that would otherwise generate unwanted baseband signals in the presence of strong interfering signals. When calibrated correctly, the CX74063-3x IP2 meets the GSM AM suppression test requirements in all bands with good margin.

To calibrate IP2, apply a strong RF signal at the receiver input and observe the resulting DC voltage level change at the receiver I/Q outputs. The exact frequency and level of the signal applied for the purpose of the calibration are not critical. The signal should, however, be within the receive band, but at least 6 MHz offset from the frequency to which the receiver is tuned. The level should be high enough to cause a notable DC shift at the I/Q outputs. A recommended value is -30 dBm at the LNA input, which applies to all three LNAs.

A set of I/Q compensation coefficients can then be programmed to the device to minimize the DC voltage shift resulting from the second-order distortion. When the DC due to the interfering signal is minimized, the IP2 performance is optimized.

**Note:** SXENA, pin 38, must be held high, and a clock signal must be present on XTAL, pin 34, during the programming of the IP2 calibration coefficients in Register 3, see Table 18.

The IP2 calibration is a one-time factory calibration that should be done for each band and each individual device for optimum performance. The determined coefficients must be stored in nonvolatile memory and programmed to the CX74063-3x upon each power-up as part of device initialization. There are on-chip registers that must be programmed through Register 3 with the appropriate IP2 coefficients for the band in use.

As long as a supply voltage is maintained on pin 43, VDDBB, the IP2 coefficients for ILOWBAND, IHIGHBAND, QLOWBAND, QHIGHBAND, programmed to the device remain in the registers. After the supply voltage has been removed from VDDBB, the coefficients must be re-programmed to the device again.

Receive/Transmit I/Q Baseband Signals. Separate pins are provided for receive I/Q outputs and transmit I/Q inputs. However, for basebands that multiplex these signals, the receive I/Q outputs and transmit I/Q inputs can be tied together.

#### **Synthesizer Section**

The CX74063-3x includes a fully integrated UHF VCO with an on-chip LC tank.

A single sigma-delta fractional-N synthesizer can phase-lock the local oscillator used in both transmit and receive paths to a precision frequency reference input. Fractional-N operation offers low phase noise and fast settling times, allowing for multiple slot applications such as GPRS. The CX74063-3x frequency stepping function with a 3 Hz resolution allows triple band operation in both transmit and receive bands using a fully integrated single integrated on-chip UHF VCO. The fine synthesizer resolution allows direct compensation or adjustment for reference frequency errors.

The fractional-N synthesizer consists of the following:

- VCC

- · High frequency prescaler

- · N-divider with a sigma-delta modulator

- · Reference buffer and divider

- · Fast phase frequency detector and charge pump

The user must provide the following three parameters:

- The reference divider value, from 1 to 15

- The N-divider value, in a manner similar to an integer-N synthesizer

- A fractional ratio

The generated frequency is given by the following equation:

$$f_{VCO} = \frac{\left(N + 3.5 + \frac{FN}{2^{22}}\right) f_{ref}}{R}$$

where: fvco = Generated VCO frequency

N = N-divider ratio integer part

FN = Fractional setting R = R-divider ratio

free = Reference frequency

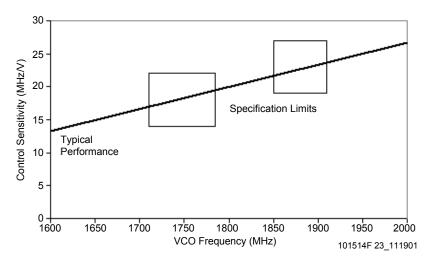

#### **UHF VCO Frequency Setting**

For the receiver, to tune the receive frequency,  $f_{RX}$ , set the VCO frequency,  $f_{VCO}$ , as follows:

•

$$f_{VCO} = \frac{3}{2} f_{RX}$$

for GSM850/900

•

$$f_{VCO} = \frac{3}{4} f_{RX}$$

for DCS1800 and PCS1900

For the transmitter VCO frequency, refer to the equations shown in Figure 6.

#### **Digital Frequency Centering**

The CX74063-3x uses a novel technique whereby the UHF VCO frequency range is re-centered each time the synthesizer is programmed. This technique is called Digital Frequency Centering (DFC). The DFC technique:

- · Extends the VCO frequency coverage

- Speeds up settling time

- Ensures robust performance since the VCO is always operated at the center of its tuning range.

Each time the synthesizer is programmed, the DFC circuit is activated, and the VCO is centered to the programmed frequency in less than 20  $\mu s$ . After this, normal Phase Locked Loop (PLL) operation is resumed and the fine settling of the frequency is finalized. The DFC typically adjusts the VCO center frequency to within a few MHz and no more than 5 MHz offset, and presets the tuning voltage to the center of the range before the PLL takes over. This speeds up frequency settling and ensures that the PLL control voltage never operates close to the rails.

Figure 6. Transmitter Frequency Generation

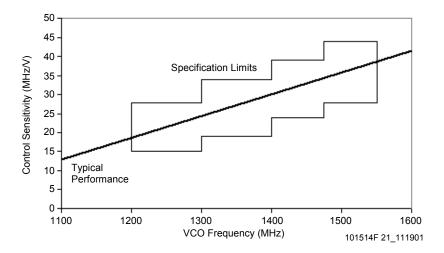

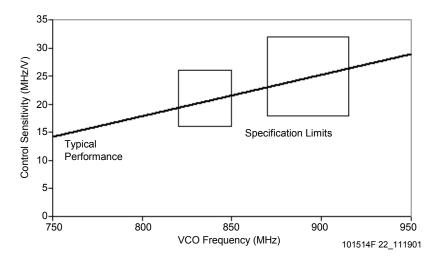

The DFC is an adaptive circuit that corrects for any VCO center frequency errors caused by variations of the integrated VCO circuit, temperature, supply voltage, aging etc. The VCO can be centered at any frequency in the range from 1.2 GHz to 1.55 GHz. Once centered, the VCO has a minimum analog tuning range of 30 MHz.

No calibration or data storage is needed for DFC operation. It is activated by one of two events:

- When the synthesizer is programmed, the rising edge of the LE signal starts the DFC cycle and.

- When changing the level of the SXENA signal from low to high, thereby turning on the synthesizer, the rising edge of the SXENA signal starts the DFC cycle.

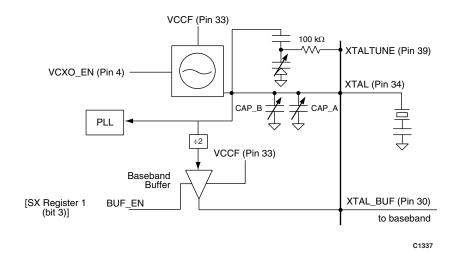

#### **Crystal Oscillator**

A crystal oscillator is designed to provide the reference frequency for the synthesizer. As shown in Figure 7, the oscillator uses an external crystal to generate an accurate oscillation frequency. The reference frequency can be changed through coarse tuning with an integrated capacitor array or fine tuning with the integrated varactor diode. The coarse tuning is done by switching in and out (using a digital word programmed via the serial interface) the capacitor network (CAP A and CAP B) located at the input of the integrated buffer. The fine tuning is done by providing a tuning voltage to the integrated varactor diode. Table 20 describes the control bits.

An output buffer is provided to drive the baseband circuitry (XTALBUF, pin 30). The VCXO and buffer circuitry are powered from pin 33 (VCCF). When VCCF is ramped to a voltage greater than 2.6 V, the output buffer powers on. The oscillator core powers up when pin 4 (VCXO EN) is set to logic 1. If pin 4 is tied permanently to logic 1, the R6 VCXO Control Register is set to a defined state by a power-on reset. Pin 4 should be held

low if an external reference oscillator is used. The buffer may be disabled by programming bit 3 in the SX1 Control Register (see Table 13) to logic 0.

#### **Transmit Section**

To minimize the post-PA filtering requirements and any additional post-PA losses, the transmit path consists of a vector modulator within a frequency translation loop. The translation loop consists of the following:

- · Phase Frequency Detector (PFD) and charge pump

- Mixer with an operating range of 800 MHz to 2 GHz

- An in-loop modulator

- Two programmable dividers

- Two transmit VCOs

#### **Translational Loop**

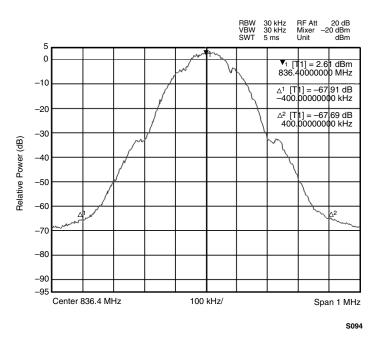

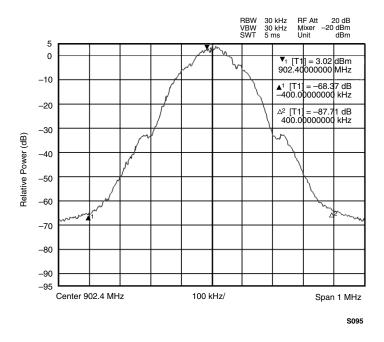

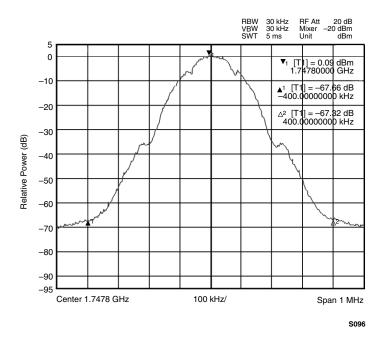

The translational loop takes baseband analog I/Q signals and modulates them with the mixed product of transmitter output and LO signal, as shown in Figure 6. The unmodulated result is compared with a divided down LO at the PFD and the difference is used to control the transmit VCO. The on-chip Low Pass Filter (LPF) following the mixer attenuates the unwanted sidebands as well as harmonics.

#### Transmit VCOs

Two on-chip transmit VCOs are designed to meet GSM850, EGSM900, DCS1800, and PCS1900 requirements. The transmit VCOs use the same DFC technique as described in the Synthesizer section to lock the translational loop. The rising edge on TXENA initializes the transmit DFC.

Figure 7. VCXO Block Diagram

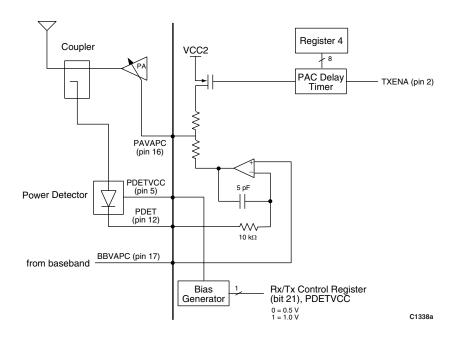

Figure 8. PA Controller Block Diagram

#### **Power Amplifier Gain Controller**

The device contains an error amplifier/integrator to provide transmit burst control for an external power amplifier (PA). As shown in Figure 8, when the device is connected to a PA, an RF detector, and a coupler, a loop is formed that controls the transmit power in a multi-band wireless application. The error amplifier amplifies and integrates the voltage difference between the RF detector output (PDET) and the power control input (BBVAPC). The output of the integrator is fed to an internal gain shaper that drives the gain control input (PAVAPC) of the external RF PA. The device, provides a bandgap voltage (PDETVCC) which can be used as the supply voltage for the external peak detector and can source up to 200  $\mu\text{A}$ .

The PA pre-bias is activated after a programmable delay and time-referenced from the rising edge of TXENA. The time delay is set using the serial interface. See Table 19 for details.

#### **Digital Interface**

The transceiver and synthesizer are controlled by a single three-wire serial interface. The transmitter, receiver, and synthesizer are each enabled through external inputs according to typical timing requirements as shown in Figures 10 and 11.

Band selection for the CX74063-3x is through the three-wire serial interface. The PCO signal (pin 3) provides a band selection control output. DC offset calibration and front-end activation timing can also be controlled by an on-chip signal sequencer, precluding the need for separate control signals. All the logic and the three-wire interface inputs are referenced to the PCO signal (pin 3).

The RX/TX Control Register is used to program the transceiver and to preset other test word states by setting bit 22 as a logic 1. If any test words are to be altered from their preset states, bit 22 must be sent to the RX/TX Control Register again as a logic 0. Typically, this is done only on power-up since the device has a zero-power standby mode that retains programmed test memory.

There are eight additional registers used to program various functions of the CX74063-3x. The SX1 Control Register is used to program the fractional-N synthesizer and the SX2 Fractional-N Modulo Register is used to program the modulus. Four auxiliary registers are used to program the transceiver besides the RX/TX Control Register, and two 24-bit registers are used to program the synthesizer:

- SX1 Synthesizer Control

- SX2 Fractional-N Modulo

- RX/TX Control

- R0 Auxiliary Control

- R2 DC Offset Timing

- R3 IP2 Calibration

- R4 PAC Timing Control

- R6 VCXO Control

- R7 VCXO Control

**SX1 Control Register**. This register is used to program the fractional-N synthesizer, and set the values of the integral-N divider and the input-R divider. The polarity of the Phase/Frequency Detector (PFD) may also be defined by this register. Refer to Table 13.

SX2 Fractional-N Modulo Register. This register is used to program the 24-bit modulo of the fractional-N synthesizer. The data is a 22-bit binary coded decimal word that allows the PLL to lock to precise frequencies. Refer to Table 14.

RX/TX Control Register. This register is used to control divide ratios and charge pump currents in the transmitter, and to control gain in the receiver along with the band select function. Refer to Table 15.

**RO Auxiliary Control Register.** This register is used to bypass the DC offset correction loops and the baseband filters. It also enables and disables the two on-chip transmit VCOs and defines the directionality of the LO port, which allows an external VCO or LO reference to be used or enables the internal VCO to be monitored. Refer to Table 16.

R2 DC Offset Timing Register. This register sets the timing of the tracking of the three DC offset cancellation loops and the time at which the front end turns on relative to the RXENA signal (pin 1). It allows the front-end to be enabled using the internal timer. Refer to Table 17.

R3 IP2 Calibration Register. This register is used to perform 2<sup>nd</sup> order Intercept Point (IP2) calibration by manually adjusting calibration coefficients. A total of four words need to be set: IP2 coefficients for I-high band, I-low band, Q-high band, and Q-low band. Refer to Table 18.

The IP2 coefficient is eight bits long (including polarity) and is intended to be a factory calibration. An algorithm using a test tone needs to be used to determine the coefficient for each individual part.

**R4 PAC Timing Control Register**. This register is used to set timing for the PAC pedestal. Refer to Table 19.

R6 and R7 VCXO Control Registers. These registers are used to control the tuning range and oscillation frequency of the VCXO. See Tables 20 and 21, respectively.

#### **Electrical and Mechanical Specifications**

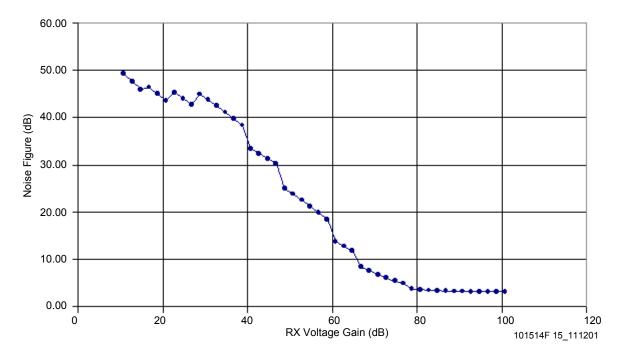

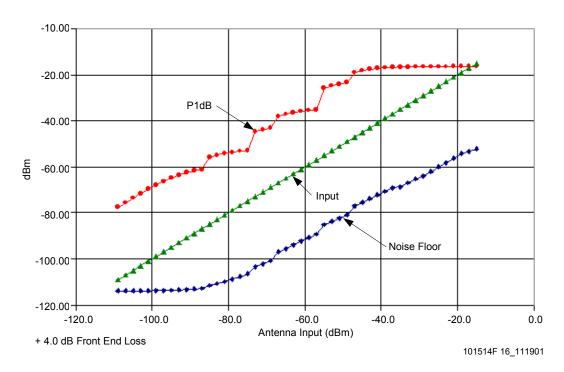

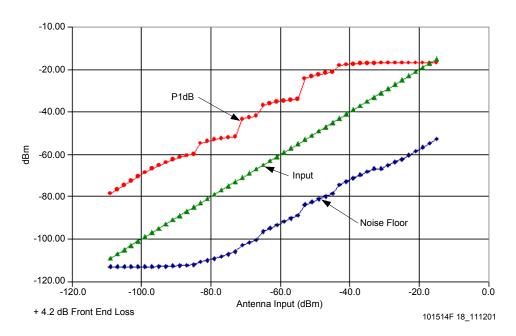

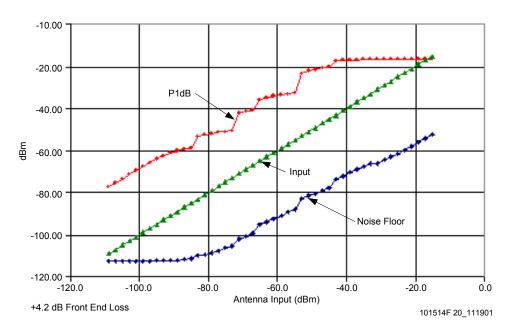

The absolute maximum ratings of the CX74063-3x are provided in Table 3. The recommended operating conditions are specified in Table 4. Electrical specifications are provided in Tables 5 through 11. Tables 12 through 21, and Figures 9 through 11 provide the serial interface programming states, functions, and timing curves. Receiver data is shown in Tables 22 through 33 and illustrated in Figures 12 through 20. Transmit data is illustrated in Figures 21 through 26.

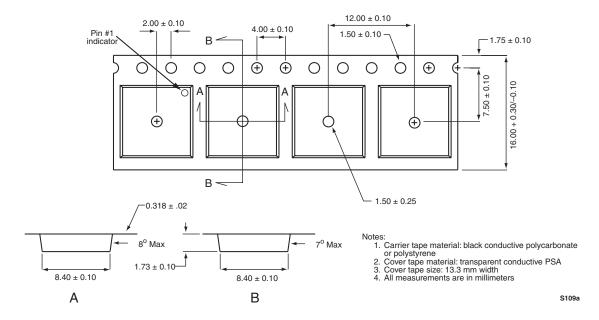

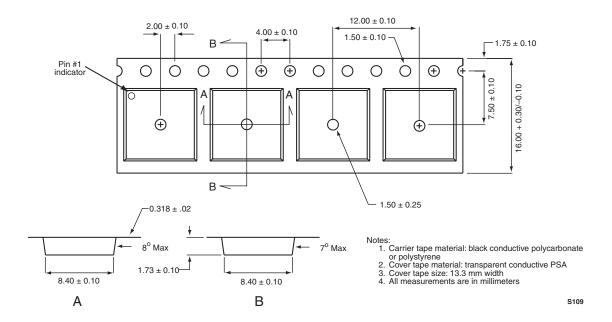

A typical application circuit using the CX74063-3x is shown in Figure 27. The 56-pin RFLGA package dimensions are provided in Figure 28 (-34 and -35 package options) and Figure 29 (-36 package option). Tape and reel dimensions are shown in Figure 30 (-34 and -36 package options) and Figure 31 (-35 package option). Typical package case markings are explained in Figure 32.

#### **Package and Handling Information**

Because this device package is sensitive to moisture absorption, it is baked and vacuum packed before shipment according to IPC J-STD 033 guidelines. Instructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. These instructions adhere to IPC J-STD 020A guidelines for handling moisture sensitive devices. If these instructions are not followed, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.

The CX74063-3x transceiver is available in both low temperature and high temperature attachment packages. The RFLGA package for the low temperature attachment option provides a circular-shaped ground pad (CX74063-34). The RFLGA package for the high temperature options is available with both a circular-shaped ground pad and a four-quadrant. split center ground pad (CX74063-35 and CX74063-36, respectively). Refer to Figures 28 and 29 for package dimensions.

Guidelines for CX74063-3x low and high temperature attachment techniques are provided below. For additional details on attachment techniques, precautions, and recommended handling procedures, refer to the Skyworks' Application Note. PCB Design & SMT Assembly Guidelines for RFLGA Packages, document number 103147.

For The -34 Low Temperature Package Option: If the CX74063-34 is attached in a reflow oven, the temperature ramp rate should not exceed 3 °C per second. Maximum temperature should not exceed 240 °C and the time spent at a temperature that exceeds 235 °C should be limited to less than 10 seconds.

If the part is manually attached, precaution should be taken to ensure that the part is not subjected beyond a maximum temperature of 240 °C or exceeds 235 °C for more than 10 seconds. Care must be taken when this product is attached. whether it is done manually or in a production solder reflow environment, to NOT heat the part beyond the recommended temperature. Measure the temperature on the package itself by attaching thermocouples to the package body.

For The -35 and -36 High Temperature Package Options: If the CX74063-35 or the CX74063-36 are attached in a reflow oven, the temperature ramp rate should not exceed 3 °C per second. Maximum temperature should not exceed 260 °C and the time spent at a temperature that exceeds 255 °C should be limited to less than 15 seconds.

If the part is manually attached, precaution should be taken to ensure that the part is not subjected beyond a maximum temperature of 260 °C or exceeds 255 °C for more than 15 seconds. Care must be taken when this product is attached, whether it is done manually or in a production solder reflow environment, to NOT heat the part beyond the recommended temperature. Measure the temperature on the package itself by attaching thermocouples to the package body.

Production quantities of this product are shipped in a standard tape and reel format. For packaging details, refer to the Skyworks' Application Note, *Tape and Reel*, document number 101568. Typical case markings for the CX74063-3x are shown in Figure 31.

#### **Electrostatic Discharge**

The CX74063-3x contains Class 1 devices. The following Electrostatic Discharge (ESD) precautions are recommended:

- Protective outer garments

- Handle device in ESD safeguarded work area

- Transport device in ESD shielded containers

- Monitor and test all ESD protection equipment

- Treat the CX74063-3x as extremely sensitive to ESD

Table 3. CX74063-3x Absolute Maximum Ratings

| Parameter                           | Minimum | Maximum | Units |

|-------------------------------------|---------|---------|-------|

| Supply voltage (VCC)                | -0.3    | +3.6    | V     |

| Ambient operating temperature range | -40     | +95     | °C    |

| Storage temperature range           | -50     | +125    | °C    |

| Input voltage range                 | GND     | VCC     | V     |

| Maximum power dissipation           |         | 600     | mW    |

**Note**: Stresses above these absolute maximum ratings may cause permanent damage. These are stress ratings only and functional operation at these conditions is not implied. Exposure to maximum rating conditions for extended periods may reduce device reliability.

**Table 4. CX74063-3x Recommended Operating Conditions**

| Parameter                                      | Minimum | Typical | Maximum | Units |

|------------------------------------------------|---------|---------|---------|-------|

| LNA input level (pins 9, 11, 13)<br>RXEN = Off |         |         | 10      | dBm   |

| Power supply                                   | 2.6     | 2.8     | 3.3     | V     |

| Digital power supply, VDDBB                    | 1.8     |         | 3.3     | V     |

| Operating junction temperature                 | -40     |         | +110    | °C    |

| Operating ambient temperature                  | -30     |         | +85     | °C    |

## Table 5. Power Consumption Specifications ( $T_A = 25^{\circ}$ C, VCC = 2.8 V unless otherwise noted)

| Parameter                                                            | Symbol | <b>Test Condition</b>                         | Min | Typical   | Max       | Units    |

|----------------------------------------------------------------------|--------|-----------------------------------------------|-----|-----------|-----------|----------|

| Total supply current:                                                | Icc    |                                               |     |           |           |          |

| Rx section, EGSM/GSM850<br>Tx section, EGSM/GSM850 (includes TX VCO) |        | RXENA=H; SXENA=L<br>TXENA=H; SXENA=L          |     | 41<br>121 | 48<br>137 | mA<br>mA |

| Synthesizer section, EGSM/GSM850 (includes UHF VCO)                  |        | SXENA=H                                       |     | 39        | 46        | mA       |

| Rx section, DCS/PCS<br>Tx section, DCS/PCS (includes TX VCO)         |        | RXENA=H; SXENA=L<br>TXENA=H; SXENA=L          |     | 49<br>126 | 58<br>143 | mA<br>mA |

| Synthesizer section, DCS/PCS (includes UHF VCO)                      |        | SXENA=H                                       |     | 39        | 46        | mA       |

| Sleep mode                                                           |        | @ VCC = 3.3 V<br>RXENA=L; TXENA=L;<br>SXENA=L |     | 20        | 100       | μΑ       |

## Table 6. CX74063-3x Electrical Specifications – EGSM/GSM850 Receiver (1 of 3) $(T_A = 25^{\circ} \text{ C, VCC} = 2.8 \text{ V unless otherwise noted})$

| Parameter                                                     | Symbol  | Test Condition<br>(Note 1)                                      | Min   | Typical | Max   | Units |

|---------------------------------------------------------------|---------|-----------------------------------------------------------------|-------|---------|-------|-------|

| Input impedance. See Figure 12 for unmatched input impedance. | Zın     | With external match                                             |       | 50      |       | Ω     |

| Input operating frequency                                     | Band 1  |                                                                 | 869   |         | 960   | MHz   |

| Receiver maximum voltage gain                                 | GRXMAX  | Highest gain mode                                               | 120   | 126     |       | dB    |

| Receiver minimum voltage gain                                 | Grxmin  | Lowest gain mode                                                |       | 11      | 17    | dB    |

| Receiver gain temperature variation                           | GTEMVAR | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$ |       |         | 4.5   | dB    |

| Gain step                                                     | ΔΑν     |                                                                 |       | 2       |       | dB    |

| Gain step accuracy                                            | GSTEP   | Over range<br>recommended in<br>Table 25                        | -0.75 |         | +0.75 | dB    |

| Gain variation versus frequency                               | GFREQ   | Over 869-894 MHz                                                |       |         | 2     | dB    |

|                                                               |         | Over 925-960 MHz                                                |       |         | 2     | dB    |

| Noise Figure                                                  | NFgain1 | G = 15/40/10/12/0/18                                            |       | 3.2     | 3.9   | dB    |

| Noise Figure (temperature)                                    | NFTEMP  | T <sub>A</sub> = +75 °C                                         |       |         | 5.0   | dB    |

|                                                               |         | T <sub>A</sub> = +85 °C                                         |       |         | 5.2   | dB    |

|                                                               |         | G = 15/40/10/12/0/18                                            |       |         |       |       |

Table 6. CX74063-3x Electrical Specifications – EGSM/GSM850 Receiver (2 of 3)  $(T_A = 25^{\circ} \text{ C, VCC} = 2.8 \text{ V unless otherwise noted})$

| Parameter                                          | Symbol  | Test Condition<br>(Note 1)                                                                  | Min         | Typical | Max  | Units   |

|----------------------------------------------------|---------|---------------------------------------------------------------------------------------------|-------------|---------|------|---------|

| Noise Figure degradation in presence of blocker    | NFBLOC  | With –26 dBm input<br>blocker @ 3 MHz offset<br>(ideal LO)                                  |             | 2       |      | dB      |

|                                                    |         | Internal LO                                                                                 |             | 4       |      | dB      |

|                                                    |         | G = 15/40/10/12/0/18                                                                        |             |         |      |         |

| Input 2nd order intercept point                    | IIP2    | Referred to LNA input<br>calibrated and<br>measured at middle of<br>EGSM or GSM850<br>band. | 50          | 65      |      | dBm     |

| DC shift in presence of blocker                    | AM Supp | With -34 dBm<br>@ 6 MHz offset<br>G = 15/40/10/12/0/18                                      |             |         | 17   | mV      |

| LO re-radiation @ LNA input                        | LOREV   | @ wanted frequency                                                                          |             | -110    | -100 | dBm     |

| Selectivity                                        |         | @ 3 MHz offset                                                                              | 143         |         |      | dB      |

|                                                    |         | @ 1.6 MHz offset                                                                            | 128         | 137     |      | dB      |

|                                                    |         | @ 600 kHz offset                                                                            | 61          | 68      |      | dB      |

|                                                    |         | @ 400 kHz offset                                                                            | 37          | 44      |      | dB      |

|                                                    |         | @ 200 kHz offset                                                                            | 9           | 13      |      | dB      |

|                                                    |         | $T_A = -30  ^{\circ}\text{C}$ to $+85  ^{\circ}\text{C}$                                    |             |         |      |         |

| I/Q amplitude imbalance                            |         | $T_A = -30  ^{\circ}\text{C}$ to $+85  ^{\circ}\text{C}$                                    |             |         | 1    | dB      |

| I/Q phase imbalance                                |         | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$                             | -3          |         | +3   | degrees |

| Input 1 dB compression point                       | IP1dB   | F = 200 kHz,<br>G = 15/40/-2/8/0/18                                                         | -65         | -60     |      | dBm     |

|                                                    |         | F = 400 kHz,<br>G = 15/40/-2/8/0/18                                                         | <b>–45</b>  | -40     |      | dBm     |

|                                                    |         | F = 600 kHz,<br>G = 15/40/10/12/0/18                                                        | -35         | -30     |      | dBm     |

|                                                    |         | F = 1.6 MHz,<br>G = 15/40/10/12/0/18                                                        | -32         | -28     |      | dBm     |

|                                                    |         | F = 3.0 MHz,<br>G = 15/40/10/12/0/18                                                        | -25         | -22     |      | dBm     |

| 3rd order intercept point @ +25 °C                 | IIP3    | F = 3.0 MHz<br>G = 15/40/10/12/0/18                                                         | <b>–</b> 15 | -12     |      | dBm     |

| 3rd order intercept point @ $-20~^{\circ}\text{C}$ | IIP3    | F = 3.0 MHz<br>G = 15/40/10/12/0/18                                                         | <b>–15</b>  | -12     |      | dBm     |

Table 6. CX74063-3x Electrical Specifications – EGSM/GSM850 Receiver (3 of 3) (T<sub>A</sub> = 25° C, VCC = 2.8 V unless otherwise noted)

| Parameter                       | Symbol  | Test Condition<br>(Note 1)                                           | Min         | Typical    | Max         | Units       |

|---------------------------------|---------|----------------------------------------------------------------------|-------------|------------|-------------|-------------|

| Output offset voltage           |         | With DC offset<br>corrected while LNA is<br>off                      |             |            | 200         | mV          |

|                                 |         | T <sub>A</sub> = +85°C                                               |             |            | 220         | mV          |

|                                 |         | With DC offset<br>corrected while LNA is<br>on<br>G=15/40/10/12/0/18 |             |            | 20          | mV          |

|                                 |         | T <sub>A</sub> = +85 °C                                              |             |            | 25          | mV          |

|                                 |         | (60 µs total DC correction time)                                     |             |            |             |             |

| Offset drift (long term)        | DCDRFT1 | 50 ms after correction<br>G = 15/40/10/12/0/18                       |             |            | 100         | mV          |

| Offset drift (short term)       | DCDRFT2 | 577 μs after correction G = 15/40/10/12/0/18                         |             |            | 10          | mV          |

|                                 |         | <b>Baseband Tunable Active</b>                                       | Filter      |            |             |             |

| 3 dB corner frequency (tunable) | Fc      |                                                                      | 80          |            | 100         | kHz         |

| Corner frequency variation      | dFc     | 39.2 kΩ at pin 29<br>470 pF at pins 25-26<br>and 27-28               | -11         |            | +11         | %           |

|                                 |         | Receiver Output Stag                                                 | е           |            |             |             |

| Differential output amplitude   |         | VGA2 = 30 dB                                                         | 3.7         |            |             | ٧           |

| (pk/pk differential)            |         | VGA2 = 0 dB                                                          | 0.3         |            |             | ٧           |

| Output common mode voltage      |         | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$      | VCC/2 - 0.1 | VCC/2      | VCC/2 + 0.1 | ٧           |

| Maximum current drive           | Іоит    |                                                                      |             |            | 0.5         | mA          |

| Output resistance               | Rouт    | RXENA = H,<br>RXENA = L, differential<br>RXENA = L, single-<br>ended | 160<br>>1M  | 200<br>40k | 240         | Ω<br>Ω<br>Ω |

| Output capacitance              | Соит    |                                                                      |             |            | 1           | pF          |

|                                 | •       |                                                                      |             |            |             |             |

Note 1: Gain codes refer to LNA/Mixer/LPF1/VGA1/AUX/VGA2 gains in dB.

Table 7. CX74063-3x Electrical Specifications – DCS1800 Receiver (1 of 3)  $(T_A = 25^{\circ} \text{ C, VCC} = 2.8 \text{ V unless otherwise noted})$

| Parameter                                                    | Symbol   | Test Condition<br>(Note 1)                                               | Min   | Typical | Max        | Units   |

|--------------------------------------------------------------|----------|--------------------------------------------------------------------------|-------|---------|------------|---------|

| Input impedance See Figure 13 for unmatched input impedance. | Zin      | With external match                                                      |       | 50      |            | Ω       |

| Input operating frequency                                    | Band 2   | DCS Rx band                                                              | 1805  |         | 1880       | MHz     |

| Receiver maximum voltage gain                                | GRXMAX   | Highest gain mode                                                        | 117   | 123     |            | dB      |

| Receiver minimum voltage gain                                | Grxmin   | Lowest gain mode                                                         |       | 9       | 15         | dB      |

| Gain step                                                    | ΔΑν      |                                                                          |       | 2       |            | dB      |

| Receiver gain temperature variation                          | GTEMPVAR | $T_A = -30 ^{\circ}\text{C}$ to $+85 ^{\circ}\text{C}$                   |       |         | 4.5        | dB      |

| Gain step accuracy                                           | GSTEP    | Over range<br>recommended in<br>Table 26                                 | -0.75 |         | +0.75      | dB      |

| Gain variation versus frequency                              | GFREQ    | Over band 2                                                              |       |         | 2          | dB      |

| Noise Figure                                                 | NFGAIN1  | G = 15/40/10/12/0/18                                                     |       | 3.6     | 4.3        | dB      |

| Noise Figure (temperature)                                   | NFTEMP   | T <sub>A</sub> = +75 °C<br>T <sub>A</sub> = +85 °C                       |       |         | 5.4<br>5.6 | dB      |

| Noise Figure degradation in presence of blocker              | NFBLOC   | With -30 dBm input<br>blocker @ 3 MHz offset<br>(ideal LO)               |       | 2       |            | dB      |

|                                                              |          | Internal LO                                                              |       | 4       |            | dB      |

|                                                              |          | G = 15/40/10/12/0/18                                                     |       |         |            |         |

| Input 2nd order intercept point                              | IIP2     | Referred to LNA input calibrated and measured at middle of DCS1800 band. | 50    | 65      |            | dBm     |

| DC shift in presence of blocker                              | AM Supp  | With -33 dBm<br>@ 6 MHz offset<br>G = 15/40/10/12/0/18                   |       |         | 17         | mV      |

| LO re-radiation @ LNA input                                  | LOREV    | @ wanted frequency                                                       |       | -110    | -100       | dBm     |

| Selectivity                                                  |          | @ 3 MHz offset                                                           | 143   |         |            | dB      |

|                                                              |          | @ 1.6 MHz offset                                                         | 128   | 137     |            | dB      |

|                                                              |          | @ 600 kHz offset                                                         | 61    | 68      |            | dB      |

|                                                              |          | @ 400 kHz offset                                                         | 37    | 41      |            | dB      |

|                                                              |          | @ 200 kHz offset                                                         | 9     | 13      |            | dB      |

|                                                              |          | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$          |       |         |            |         |

| I/Q amplitude imbalance                                      |          | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$          |       |         | 1          | dB      |

| I/Q phase imbalance                                          |          | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$          | -3    |         | +3         | degrees |

Table 7. CX74063-3x Electrical Specifications – DCS1800 Receiver (2 of 3)  $(T_A = 25^{\circ} \text{ C, VCC} = 2.8 \text{ V unless otherwise noted})$

| Parameter                          | Symbol  | Test Condition<br>(Note 1)                                      | Min         | Typical | Max  | Units |

|------------------------------------|---------|-----------------------------------------------------------------|-------------|---------|------|-------|

| Input 1 dB compression point       | IP1dB   | F = 200 kHz,<br>G = 15/40/-2/8/0/18                             | -65         | -60     |      | dBm   |

|                                    |         | F = 400 kHz,<br>G = 15/40/-2/8/0/18                             | <b>–45</b>  | -40     |      | dBm   |

|                                    |         | F = 600 kHz,<br>G = 15/40/10/12/0/18                            | -35         | -30     |      | dBm   |

|                                    |         | F = 1.6 MHz,<br>G = 15/40/10/12/0/18                            | -32         | -28     |      | dBm   |

|                                    |         | F = 3.0 MHz,<br>G = 15/40/10/12/0/18                            | -25         | -22     |      | dBm   |

| 3rd order intercept point @ +25 °C | IIP3    | F = 3.0 MHz<br>G = 15/40/10/12/0/18                             | <b>–</b> 15 | -12     |      | dBm   |

| 3rd order intercept point @ –20 °C | IIP3    | F = 3.0 MHz<br>G = 15/40/10/12/0/18                             | <b>–</b> 15 | -12     |      | dBm   |

| Output offset voltage              |         | With DC offset corrected while LNA is off                       |             |         | 200  | mV    |

|                                    |         | T <sub>A</sub> = + 85°C                                         |             |         | 220  | mV    |

|                                    |         | With DC offset corrected while LNA is on $G = 15/40/10/12/0/18$ |             |         | 20   | mV    |

|                                    |         | T <sub>A</sub> = + 85 °C                                        |             |         | 25   | mV    |

|                                    |         | (60 µs total DC correction time)                                |             |         |      |       |

| Offset drift (long term)           | DCDRFT1 | G = 15/40/10/12/0/18<br>50 ms after correction                  |             |         | 100  | mV    |

| Offset drift (short term)          | DCDRFT2 | G = 15/40/10/12/0/18<br>577 μs after correction                 |             |         | 10   | mV    |

|                                    |         | Baseband Tunable Active                                         | Filter      |         |      |       |

| 3 dB corner frequency (tunable)    | Fc      |                                                                 | 80          |         | 100  | kHz   |

| Corner frequency variation         | dFc     | 39.2 kΩ at pin 29<br>470 pF at pins 25-26<br>and 27-28          | - 11        |         | + 11 | %     |

Table 7. CX74063-3x Electrical Specifications – DCS1800 Receiver (3 of 3)  $(T_A = 25^{\circ} \text{ C, VCC} = 2.8 \text{ V unless otherwise noted})$

| Parameter                            | Symbol | Test Condition<br>(Note 1)                                            | Min         | Typical    | Max         | Units       |

|--------------------------------------|--------|-----------------------------------------------------------------------|-------------|------------|-------------|-------------|

|                                      |        | Receiver Output Stag                                                  | е           |            |             |             |

| Differential output amplitude (pk/pk |        | VGA2 = 30 dB                                                          | 3.7         |            |             | ٧           |

| differential)                        |        | VGA2 = 0 dB                                                           | 0.3         |            |             | ٧           |

| Output common mode voltage           |        |                                                                       | VCC/2 - 0.1 | VCC/2      | VCC/2 + 0.1 | ٧           |

| Maximum current drive                | lоит   |                                                                       |             |            | 0.5         | mA          |

| Output Resistance                    | Rоит   | RXENA = H,<br>RXENA = L, differential,<br>RXENA = L, single-<br>ended | 160<br>>1M  | 200<br>40k | 240         | Ω<br>Ω<br>Ω |

| Output Capacitance                   | Соит   |                                                                       |             |            | 1           | pF          |

Note 1: Gain codes refer to LNA/Mixer/LPF1/VGA1/AUX/VGA2 gains in dB.

Table 8. CX74063-3x Electrical Specifications – PCS1900 Receiver (1 of 3)  $(T_A = 2.5^{\circ} C, VCC = 2.8 V unless otherwise noted)$

| Parameter                                                     | Symbol             | Test Condition<br>(Note 1)                                      | Min   | Typical | Max        | Units |

|---------------------------------------------------------------|--------------------|-----------------------------------------------------------------|-------|---------|------------|-------|

| Input impedance. See Figure 14 for unmatched input impedance. | Zin                | With external match                                             |       | 50      |            | Ω     |

| Input operating frequency                                     | Band 3             | PCS Rx band                                                     | 1930  |         | 1990       | MHz   |

| Receiver maximum voltage gain                                 | GRXMAX             | Highest gain mode                                               | 117   | 123     |            | dB    |

| Receiver minimum voltage gain                                 | Grxmin             | Lowest gain mode                                                |       | 7       | 13         | dB    |

| Receiver gain temperature variation                           | GTEMPVAR           | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$ |       |         | 4.5        | dB    |

| Gain step                                                     | ΔΑν                |                                                                 |       | 2       |            | dB    |

| Gain step accuracy                                            | GSTEP              | Over range<br>recommended in<br>Table 27                        | -0.75 |         | +0.75      | dB    |

| Gain variation versus frequency                               | GFREQ              | Over band 3                                                     |       |         | 2          | dB    |

| Noise Figure                                                  | NFgain1            | G = 15/40/10/14/0/18                                            |       | 4.2     | 4.9        | dB    |

| Noise Figure (temperature)                                    | NFTEMP             | T <sub>A</sub> = +75 °C<br>T <sub>A</sub> = +85 °C              |       |         | 6.0<br>6.2 | dB    |

| Noise Figure degradation in presence of blocker               | NF <sub>BLOC</sub> | With -30 dBm input<br>blocker @ 3MHz offset<br>(ideal LO)       |       | 2       |            | dB    |

|                                                               |                    | Internal L0<br>G = 15/40/10/14/0/18                             |       | 4       |            | dB    |

Table 8. CX74063-3x Electrical Specifications – PCS1900 Receiver (2 of 3) ( $T_A = 2.5^{\circ}$  C, VCC = 2.8 V unless otherwise noted)

| Parameter                          | Symbol  | Test Condition<br>(Note 1)                                                       | Min        | Typical | Max  | Units   |

|------------------------------------|---------|----------------------------------------------------------------------------------|------------|---------|------|---------|

| Input 2nd order intercept point    | IIP2    | Referred to LNA input<br>calibrated and<br>measured at middle of<br>PCS1900 band | 50         | 65      |      | dBm     |

| DC shift in presence of blocker    | AM Supp | With -33 dBm<br>@ 6 MHz offset<br>G = 15/40/10/14/0/18                           |            |         | 17   | mV      |

| LO Re-radiation @ LNA input        | LOREV   | @ wanted frequency                                                               |            | -110    | -100 | dBm     |

| Selectivity                        |         | @ 3 MHz offset                                                                   | 143        |         |      | dB      |

|                                    |         | @ 1.6 MHz offset                                                                 | 128        | 137     |      | dB      |

|                                    |         | @ 600 kHz offset                                                                 | 61         | 68      |      | dB      |

|                                    |         | @ 400 kHz offset                                                                 | 37         | 41      |      | dB      |

|                                    |         | @ 200 kHz offset                                                                 | 9          | 13      |      | dB      |

|                                    |         | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$                  |            |         |      |         |

| I/Q amplitude imbalance            |         | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$                  |            |         | 1    | dB      |

| I/Q phase imbalance                |         | $T_A = -30  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$                  | -3         |         | +3   | degrees |

| Input 1 dB compression point       | IP1dB   | F = 200 kHz,<br>G = 15/40/-2/8/0/18                                              | -65        | -60     |      | dBm     |

|                                    |         | F = 400 kHz,<br>G = 15/40/-2/8/0/18                                              | <b>–45</b> | -40     |      | dBm     |

|                                    |         | F = 600 kHz,<br>G = 15/40/10/14/0/18                                             | -35        | -30     |      | dBm     |

|                                    |         | F = 1.6 MHz,<br>G = 15/40/10/14/0/18                                             | -32        | -28     |      | dBm     |

|                                    |         | F = 3.0 MHz,<br>G = 15/40/10/14/0/18                                             | <b>–25</b> | -22     |      | dBm     |

| 3rd order intercept point @ +25 °C | IIP3    | F = 3.0 MHz<br>G = 15/40/10/14/0/18                                              | <b>–15</b> | -12     |      | dBm     |

| 3rd order intercept point @ –20 °C | IIP3    | F = 3.0 MHz<br>G = 15/40/10/14/0/18                                              | <b>–15</b> | -12     |      | dBm     |

| Output offset voltage              |         | With DC offset corrected while LNA is off                                        |            |         | 200  | mV      |

|                                    |         | T <sub>A</sub> = +85°C                                                           |            |         | 220  | mV      |

|                                    |         | With DC offset corrected while LNA is on                                         |            |         | 20   | mV      |

|                                    |         | T <sub>A</sub> = +85 °C                                                          |            |         | 25   | mV      |

|                                    |         | G = 15/40/10/12/0/18<br>(60 μs total DC<br>correction time)                      |            |         |      |         |

Table 8. CX74063-3x Electrical Specifications – PCS1900 Receiver (3 of 3) (T<sub>A</sub> = 2 5° C, VCC = 2.8 V unless otherwise noted)

| Parameter                            | Symbol  | Test Condition<br>(Note 1)                                            | Min         | Typical    | Max         | Units       |

|--------------------------------------|---------|-----------------------------------------------------------------------|-------------|------------|-------------|-------------|

| Offset drift (long term)             | DCDRFT1 | 50 ms after correction<br>G = 15/40/10/14/0/18                        |             |            | 100         | mV          |

| Offset drift (short term)            | DCDRFT2 | 577 μs after correction G = 15/40/10/14/0/18                          |             |            | 10          | mV          |

|                                      |         | Baseband Tunable Active                                               | Filter      |            |             |             |

| 3 dB corner frequency (tunable)      | Fc      |                                                                       | 80          |            | 100         | kHz         |

| Corner frequency variation           | dFc     | 39.2 kΩ at pin 29<br>470 pF at pins 25-26<br>and 27-28                | -11         |            | +11         | %           |

|                                      |         | Receiver Output Stag                                                  | е           |            |             |             |

| Differential output amplitude (pk/pk |         | VGA2 = 30 dB                                                          | 3.7         |            |             | V           |

| differential)                        |         | VGA2 = 0 dB                                                           | 0.3         |            |             | ٧           |

| Output common mode voltage           |         |                                                                       | VCC/2 - 0.1 | VCC/2      | VCC/2 + 0.1 | V           |

| Maximum current drive                | louт    |                                                                       |             |            | 0.5         | mA          |

| Output resistance                    | Rоuт    | RXENA = H,<br>RXENA = L, differential,<br>RXENA = L, single-<br>ended | 160<br>>1M  | 200<br>40k | 240         | Ω<br>Ω<br>Ω |

| Output capacitance                   | Соит    |                                                                       |             |            | 1           | pF          |

Note 1: Gain codes refer to LNA/Mixer/LPF1/VGA1/AUX/VGA2 gains in dB.

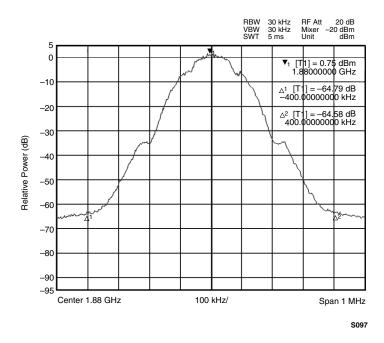

Table 9. CX74063-3x Electrical Specifications – Transmitter (1 of 4)  $(T_A = 2.5^{\circ} \text{ C, VCC} = 2.8 \text{ V unless otherwise noted})$

| Parameter                         | Symbol          | <b>Test Condition</b>                                                               | Min         | Typical | Max       | Units                        |

|-----------------------------------|-----------------|-------------------------------------------------------------------------------------|-------------|---------|-----------|------------------------------|

|                                   |                 | I/Q Modulator                                                                       |             |         |           |                              |

| Input impedance                   | Zin             | TXENA = H, differential,<br>TXENA = L, differential,<br>TXENA = L, single-<br>ended | 400k<br>>1M | 60k     |           | $\Omega \\ \Omega \\ \Omega$ |

| Input signal level                |                 | Differential                                                                        | 0.8         | 1       | 1.2       | Vp-p                         |

| Input common mode voltage range   | V <sub>CM</sub> |                                                                                     | 0.85        | 1.35    | VCC - 1.3 | ٧                            |

| Input frequency 3 dB bandwidth    |                 |                                                                                     |             | 3       |           | MHz                          |

| Input common mode rejection ratio |                 | fin = 100 kHz                                                                       | 65          | 75      |           | dB                           |

|                                   |                 | f <sub>IN</sub> = 1 MHz                                                             | 45          | 55      |           |                              |

| Output operating frequency        | Fоит            |                                                                                     | 70          |         | 130       | MHz                          |

| Output impedance                  | Zouт            | Per side                                                                            | 170         | 200     | 230       | Ω                            |

| Output voltage                    | <b>V</b> out    |                                                                                     |             | -33     |           | dBV                          |

Table 9. CX74063-3x Electrical Specifications – Transmitter (2 of 4) (TA =2 5° C, VCC = 2.8 V unless otherwise noted)

| Parameter                                              | Symbol           | <b>Test Condition</b>                                                                                | Min | Typical       | Max  | Units     |

|--------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------|-----|---------------|------|-----------|

|                                                        |                  | I/Q Modulator (continue                                                                              | d)  |               |      |           |

| Output noise power                                     | No               | @ 10 MHz offset                                                                                      |     | -132          | -128 | dBc/Hz    |

|                                                        |                  | @ 1.8 MHz offset                                                                                     |     | -130          | -126 | dBc/Hz    |

| LO suppression                                         |                  |                                                                                                      | 30  | 35            |      | dBc       |

| Sideband suppression                                   |                  |                                                                                                      | 30  | 35            |      | dBc       |

|                                                        |                  | Translational Loop                                                                                   |     |               |      |           |

| Spurious                                               |                  | Modulation 2nd order                                                                                 |     | -70           | -40  | dBc       |

|                                                        |                  | Modulation 3rd order                                                                                 |     | -60           | -55  | dBc       |

| Transmit frequency (input from VCO)                    | FTX              |                                                                                                      | 800 |               | 2000 | MHz       |

| IF frequency                                           | Fif              |                                                                                                      | 70  |               | 130  | MHz       |

| Transmit input power                                   | Pin              | With external 50 $\Omega$ termination                                                                | -20 | -15           | -10  | dBm       |

| Transmit input impedance                               | Zın              |                                                                                                      |     | 300//<br>0.3  |      | Ω//<br>pF |

| Transmitter output phase noise                         | No               | @ 400 kHz offset                                                                                     |     | -120          | -118 | dBc/Hz    |

| (includes TX VCO and LO PLL)                           |                  | @ 1.8 MHz offset                                                                                     |     | -130          | -124 | dBc/Hz    |

|                                                        |                  | @ 10 MHz offset<br>EGSM/GSM850                                                                       |     | -152          | -150 | dBc/Hz    |

|                                                        |                  | @ 20 MHz offset<br>EGSM/GSM850                                                                       |     | -164          | -162 | dBc/Hz    |