RoHS Compliance

# CAT3200, CAT3200-5

Low Noise Regulated Charge Pump DC-DC Converter

## FEATURES

- Constant high frequency (2MHz) operation

- 100mA output current

- Regulated output voltage (5V fixed CAT3200-5, Adjustable CAT3200)

- Low quiescent current (1.7mA typ.)

- Input voltage operation down to 2.7V

- Soft start, slew rate control

- Thermal overload shutdown protection

- **Low value external capacitors (1μF)**

- Foldback current overload protection

- Shutdown current less than 1µA

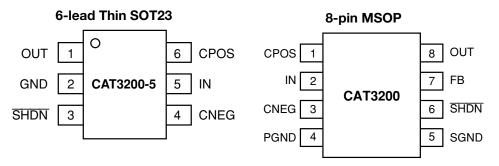

- CAT3200-5 in low profile (1mm thin) 6-lead SOT23 package

- CAT3200 in MSOP-8 package

## **APPLICATIONS**

- 3V to 5V boost conversion

- White LED driver

- USB On-The-Go 5V supply

- Local 5V supply from lower rail

- Battery backup systems

- Handheld portable devices

## DESCRIPTION

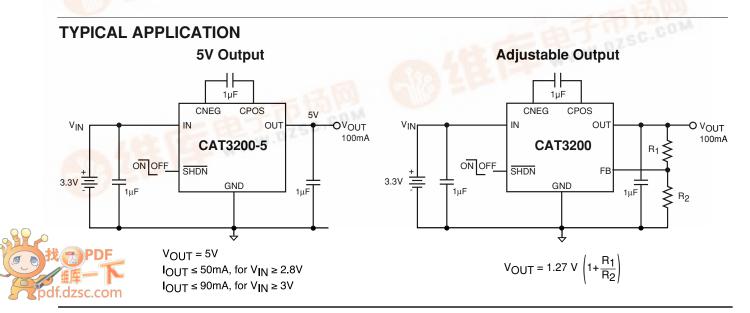

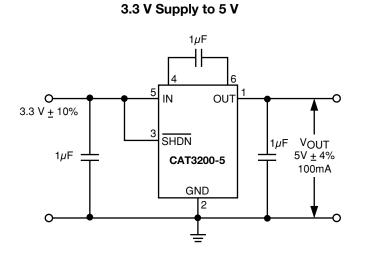

The CAT3200 and CAT3200-5 are switched capacitor boost converters that deliver a low noise, regulated output voltage. The CAT3200-5 gives a fixed regulated 5V output. The CAT3200 has an adjustable output using external resistors. The constant frequency 2MHz charge pump allows small 1 $\mu$ F ceramic capacitors to be used.

Maximum output loads of up to 100mA can be supported over a wide range of input supply voltages (2.7V to 4.5V) making the device ideal for batterypowered applications. A shutdown control input allows the device to be placed in power-down mode, reducing the supply current to less than  $1\mu A$ .

In the event of short circuit or overload conditions, the device is fully protected by both foldback current limiting and thermal overload detection. In addition, a soft start, slew rate control circuit limits inrush current during power-up.

The CAT3200-5 is available in a 6-lead, 1mm max thin SOT23 package. The CAT3200 is available in an 8-lead MSOP package.

## **ORDERING INFORMATION**

| Part Number      | Output Voltage | Package                      | Package Marking | Quantity per Reel |

|------------------|----------------|------------------------------|-----------------|-------------------|

| CAT3200ES6-5-TE7 | 5V             | 6-lead thin SOT23            | BJ              | 3,000             |

| CAT3200TDI-TE7   | 5V             | 6-lead thin SOT23, Lead Free | LN              | 3,000             |

| CAT3200EMS8-TE13 | Adjustable     | 8-lead MSOP                  | AATR            | 2,500             |

| CAT3200ZI-TE13   | Adjustable     | 8-lead MSOP, Lead Free       | ABDA            | 2,500             |

#### **PIN DESCRIPTIONS**

| Designation | Description                                   |  |  |

|-------------|-----------------------------------------------|--|--|

| OUT         | Regulated output voltage.                     |  |  |

| GND         | Ground reference for all voltages.            |  |  |

| SHDN        | Shutdown control logic input (Active LOW)     |  |  |

| CNEG        | Negative connection for the flying capacitor. |  |  |

| IN          | Input power supply.                           |  |  |

| CPOS        | Positive connection for the flying capacitor. |  |  |

| FB          | Feedback to set the output voltage.           |  |  |

| PGND        | Power ground.                                 |  |  |

| SGND        | Signal ground.                                |  |  |

## **PIN CONFIGURATION**

## **ABSOLUTE MAXIMUM RATINGS**

| $V_{\text{IN}},V_{\text{OUT}},\overline{\text{SHDN}},C_{\text{NEG}},C_{\text{POS}}$<br>Voltage0.6V to 6.0V |

|------------------------------------------------------------------------------------------------------------|

| $V_{\text{OUT}}$ Short Circuit Duration Indefinite                                                         |

| Output Current 200mA                                                                                       |

| ESD Protection (HBM) 2000V                                                                                 |

| Junction Temperature 150°C                                                                                 |

| Storage Temperature Range65°C to 160°C                                                                     |

| Lead Soldering Temperature (10 sec) 300°C                                                                  |

| Power Dissipation (SOT23-6)0.3W                                                                            |

Power Dissipation (8-MSOP) ......0.5W

## **RECOMMENDED OPERATING CONDITIONS**

| V <sub>IN</sub>           | 2.7V to 4.5V |

|---------------------------|--------------|

| CIN, COUT, CFLY           | 1μF          |

| ILOAD                     | 0 to 100mA   |

| Ambient Temperature Range | 40°C to 85°C |

## **ELECTRICAL SPECIFICATIONS**

Recommended operating conditions unless otherwise specified.  $C_{IN}$ ,  $C_{OUT}$ ,  $C_{FLY}$  are  $1\mu$ F ceramic capacitors and  $V_{IN}$  is set to 3.6V.

| Symbol            | Parameter                                     | Conditions                                                       | Min  | Тур  | Max  | Units |

|-------------------|-----------------------------------------------|------------------------------------------------------------------|------|------|------|-------|

| Vout              | Regulated Output                              | $eq:load_load_load_load_load_load_load_load_$                    | 4.8  | 5.0  | 5.2  | V     |

| VLINE             | Line Regulation                               | $3.1V \leq V_{IN} \leq 4.5V, \ I_{LOAD} = 50mA$                  |      | 6    |      | mV    |

| Vload             | Load Regulation                               | $I_{LOAD} = 10mA$ to 100mA, $V_{IN} = 3.6V$                      |      | 20   |      | mV    |

| Fosc              | Switching Frequency                           |                                                                  | 1.3  | 2.0  | 2.6  | MHz   |

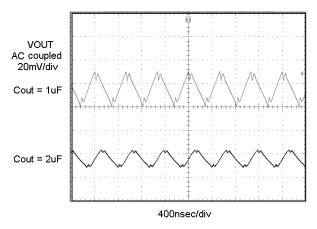

| V <sub>R</sub>    | Output Ripple<br>Voltage                      | l <sub>LOAD</sub> = 100mA<br>CAT3200-5 Only                      |      | 30   |      | mVp-p |

| η                 | Efficiency                                    | $I_{LOAD} = 50mA, V_{IN} = 3V, CAT3200-5$                        |      | 80   |      | %     |

| Ignd              | Ground Current                                | $I_{LOAD} = 0mA, \overline{SHDN} = V_{IN}$                       |      | 1.6  | 4    | mA    |

| ISHDN             | Shutdown Input<br>Current                     | $I_{LOAD} = 0mA$ , $\overline{SHDN} = 0V$ to $V_{IN}$            |      |      | 1    | μΑ    |

| V <sub>FB</sub>   | FB Voltage                                    | CAT3200 Only                                                     | 1.22 | 1.27 | 1.32 | V     |

| I <sub>FB</sub>   | FB Input Current                              | CAT3200 Only                                                     | -50  |      | 50   | nA    |

| R <sub>OL</sub>   | Open-Loop                                     | $I_{LOAD} = 100 \text{mA}, V_{IN} = 3 \text{V} \text{ (Note 1)}$ |      | 10   |      | Ω     |

|                   | Resistance                                    |                                                                  |      |      |      |       |

| T <sub>ON</sub>   | V <sub>OUT</sub> Turn-on time<br>(10% to 90%) | $I_{LOAD} = 0mA, V_{IN} = 3V$                                    |      | 0.5  |      | ms    |

| VIHSHDN           | High Detect<br>Shutdown Threshold             |                                                                  |      | 0.8  | 1.3  | V     |

| VILSHDN           | Low Detect<br>Shutdown Threshold              |                                                                  | 0.4  |      |      | V     |

| I <sub>ROUT</sub> | Reverse Leakage<br>into OUT pin               | V <sub>OUT</sub> = 5V, Shutdown mode (Note 2)                    |      | 15   | 30   | μA    |

| Isc               | Short-circuit Output                          | V <sub>OUT</sub> = 0V                                            |      | 80   |      | mA    |

| T <sub>SD</sub>   | Thermal Shutdown                              |                                                                  |      | 160  |      | °C    |

| T <sub>HYST</sub> | Thermal Hysteresis                            |                                                                  |      | 20   |      | °C    |

Note 1:  $R_{OL} = (2V_{IN} - V_{OUT})/I_{OUT}$

Note 2: In the event of a controlled shutdown, the output will be isolated from the input, but will remain connected to the internal resistor feedback network. This will cause a small level of reverse current to flow back into the device to ground.

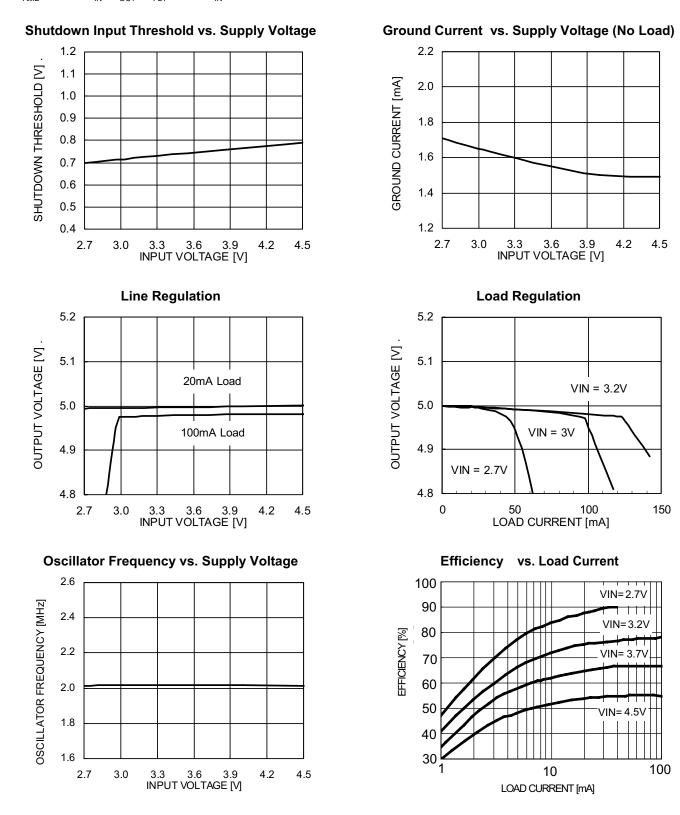

## **TYPICAL PERFORMANCE CHARACTERISTICS (CAT3200-5)**

$T_{AMB}=25^{\circ}C, C_{IN}=C_{OUT}=C_{FLY}=1\mu F, V_{IN}=3.3V$  unless specified otherwise.

## **TYPICAL PERFORMANCE CHARACTERISTICS (CAT3200-5)**

$T_{AMB}$ =25°C,  $C_{IN}$ = $C_{OUT}$ = $C_{FLY}$ =1µF,  $V_{IN}$ =3.3V unless specified otherwise.

## SHDN 5V/div VOUT 2V/div Input current 100mA/div 100usec/div

#### Soft Start Power Up (90mA Load, 3.3V Input)

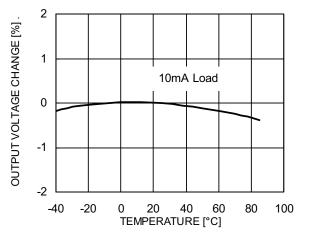

**Output Voltage Change vs. Temperature**

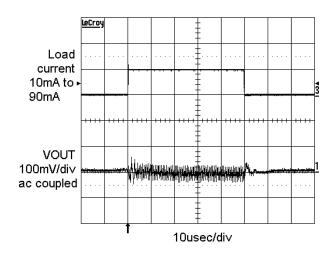

#### Load Step Response (3.3V Input)

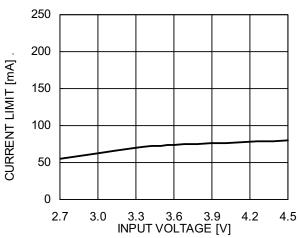

Short Circuit Current vs Supply Voltage

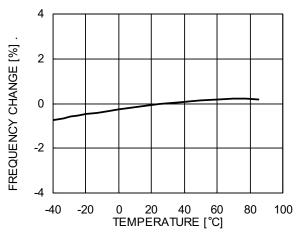

#### **Oscillator Frequency Change vs. Temperature**

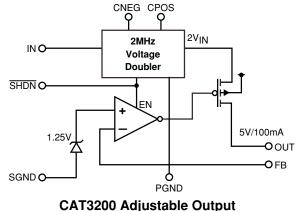

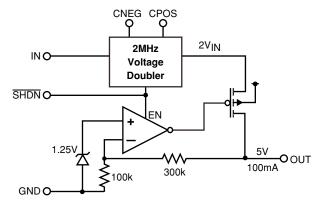

#### **BLOCK DIAGRAM**

CAT3200-5 5V Fixed Output

#### **PIN FUNCTIONS**

**IN** is the power supply. During normal operation the device draws a supply current which is almost constant. A very brief interval of non-conduction will occur at the switching frequency. The duration of the non-conduction interval is set by the internal non-overlapping "break-before-make" timing. IN should be bypassed with a  $1\mu$ F to  $4.7\mu$ F low ESR (Equivalent Series Resistance) ceramic capacitor.

For filtering, a low ESR ceramic bypass capacitor  $(1\mu F)$  in close proximity to the IN pin prevents noise from being injected back into the power supply.

**SHDN** is the logic control input (Active LOW) that places the device into shutdown mode. The internal logic is CMOS and the pin does not use an internal pull-down resistor. The **SHDN** pin should not be allowed to float.

**CPOS, CNEG** are the positive and negative connections respectively for the charge pump flying capacitor. A low ESR ceramic capacitor  $(1\mu F)$  should be connected between these pins. During initial power-up it may be possible for the capacitor to experience a voltage reversal and for this reason, avoid using a polarized (tantalum or aluminum) flying capacitor.

**OUT** is the regulated output voltage to power the load. During normal operation, the device will deliver a train of current pulses to the pin at a frequency of 2MHz. Adequate filtering on the pin can typically be achieved through the use a low ESR ceramic bypass capacitor (1 $\mu$ F to 4.7 $\mu$ F) in close proximity to the OUT pin. The ESR of the output capacitor will directly influence the output ripple voltage.

When the shutdown mode is entered, the output is immediately isolated from the input supply, however, the output will remain connected to the internal feedback resistor network (400k $\Omega$ ). The feedback network will result in a reverse current of 10 $\mu$ A to 20 $\mu$ A to flow back through the device to ground.

Whenever the device is taken out of shutdown mode, the output voltage will experience a slew rate controlled power-up. Full operating voltage is typically achieved in less than 0.5 msec.

**GND** is the ground reference for all voltages on CAT3200-5 devices.

**FB** (CAT3200 Only) is the feedback input pin. An output divider should be connected from OUT to FB to program the output voltage.

**PGND** (CAT3200 Only). Is the same as GND for the CAT3200-5 except for the internal reference connection to SGND.

**SGND** (CAT3200 Only) Ground pin for the internal reference. The CNEG connection is switched to this pin during the normal charge pump operation.

## **DEVICE OPERATION**

The CAT3200/CAT3200-5 use a switched capacitor charge pump to boost the voltage at IN to a regulated output voltage. Regulation is achieved by sensing the output voltage through an internal resistor divider (CAT3200-5) and modulating the charge pump output current based on the error signal. A 2-phase non-overlapping clock activates the charge pump switches. The flying capacitor is charged from the IN voltage on the first phase of the clock. On the second phase of the clock it is stacked in series with the input voltage and connected to OUT. The charging and discharging the flying capacitor continues at a free running frequency of typically 2MHz.

In shutdown mode all circuitry is turned off and the CAT3200/CAT3200-5 draw only leakage current from the V<sub>IN</sub> supply. OUT is disconnected from IN. The SHDN pin is a CMOS input with a threshold voltage of approximately 0.8V. The CAT3200/CAT3200-5 is in shutdown when a logic LOW is applied to the SHDN pin. The SHDN pin is a high impedance CMOS input. SHDN does not have an internal pull-down resistor and should not be allowed to float and. It must always be driven with a valid logic level.

#### **Short-Circuit and Thermal Protection**

The CAT3200 and CAT3200-5 have built-in short-circuit current limiting and over temperature protection. During overload conditions, output current is limited to approximately 225mA. At higher temperatures, or if the input voltage is high enough to cause excessive chip self heating, the thermal shutdown circuit shuts down the charge pump as the junction temperature exceeds approximately 160°C. Once the junction temperature drops back to approximately 140°C, the charge pump is enabled. The CAT3200and CAT3200-5 will cycle in and out of thermal shutdown indefinitely without latch-up or damage until a short-circuit on OUT is removed.

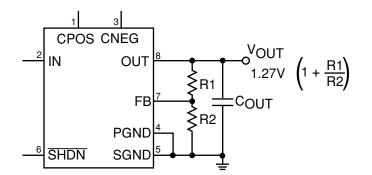

#### Programming the CAT3200 Output Voltage (FB Pin)

The CAT3200-5 version has an internal resistive divider to program the output voltage. The programmable CAT3200 may be set to an arbitrary voltage via an external resistive divider. Since it employs a voltage doubling charge pump, it is not possible to achieve output voltages greater than twice the available input voltage. Figure 1 shows the required voltage divider connection. The voltage divider ratio is given by the formula:

$$\frac{\mathrm{R1}}{\mathrm{R2}} = \frac{\mathrm{V}_{\mathrm{OUT}}}{1.27\mathrm{V}} - 1$$

Typical values for total voltage divider resistance can range from several  $k\Omega s$  up to  $1M\Omega$ .

Figure 1: Programming the Adjustable CAT3200

## **APPLICATION INFORMATION**

#### **Ceramic Capacitors**

Ceramic capacitors of different dielectric materials lose their capacitance with higher temperature and voltage at different rates. For example, a capacitor made of X5R or X7R material will retain most of its capacitance from –  $40^{\circ}$ C to  $85^{\circ}$ C whereas a Z5U or Y5V style capacitor will lose considerable capacitance over that range.

Z5U and Y5V capacitors may also have voltage coefficient causing them to lose 60% or more of their capacitance when the rated voltage is applied. When comparing different capacitors it is often useful consider the amount of achievable capacitance for a given case size rather than discussing the specified capacitance value. For example, over rated voltage and temperature conditions, a 1 $\mu$ F, 10V, Y5V ceramic capacitor in an 0603 case may not provide any more capacitance than a 0.22 $\mu$ F, 10V, X7R available in the same 0603 case. For many CAT3200/CAT3200-5 applications these capacitors can be considered roughly equivalent.

The capacitor manufacturer's data sheet should be consulted to determine what value of capacitor is needed to ensure the desired capacitance at all temperatures and voltages. Below is a list of ceramic capacitor manufacturers and how to contact them:

| Capacitor<br>Manufacturer | Web             | Phone        |

|---------------------------|-----------------|--------------|

| Murata                    | www.murata.com  | 814.237.1431 |

| AVX/Kemet                 | www.avxcorp.com | 843.448.9411 |

| Vishay                    | www.vishay.com  |              |

| Kemet                     | www.kemet.com   | 408.986.0424 |

| Taiyo Yuden               | www.t-yuden.com | 408.573.4150 |

#### **Thermal Management**

For higher input voltages and maximum output current there can be substantial power dissipation in the CAT3200/CAT3200-5. If the junction temperature increases to 160°C, the thermal shutdown circuitry will automatically turn off the output.

A good thermal connection to the PC board is recommended to reduce the chip temperature. Connecting the GND pin (Pins 4/5 for CAT3200, Pin 2 for CAT3200-5) to a ground plane, and maintaining a solid ground plane under the device reduces the overall thermal resistance. The overall junction to ambient thermal resistance  $(\theta_{JA})$  for device power dissipation  $(P_D)$  consists primarily of two paths in series. The first path is the junction to the case  $(\theta_{JC})$  which is defined by the package style, and the second path is case to ambient  $(\theta_{CA})$  thermal resistance which is dependent on board layout. The final operating junction temperature for any set of conditions can be estimated by the following thermal equation:

$$T_{\text{JUNC}} = T_{\text{AMB}} + P_{\text{D}}(\Theta_{\text{JC}}) + P_{\text{D}}(\Theta_{\text{CA}})$$

$$= T_{\text{AMB}} + P_{\text{D}}(\Theta_{\text{JA}})$$

The CAT3200 in SOT23 package, when mounted on printed circuit board with two square inches of copper allocated for "heat spreading", will result with an overall  $\theta_{IA}$  of less than 150°C/W.

For a typical application operating from a 3.8V input supply, the maximum power dissipation is 260mW (100mA x 3V). This would result if a maximum junction temperature of :

$$\begin{aligned} \mathsf{T}_{\mathsf{JUNC}} &= \mathsf{T}_{\mathsf{AMB}} + \mathsf{P}_{\mathsf{D}}(\theta_{\mathsf{J}}\mathsf{A}) \\ &= 85^{\circ}\mathsf{C} + 0.26\mathsf{W}(150^{\circ}\mathsf{C}/\mathsf{W}) \\ &= 85^{\circ}\mathsf{C} + 39^{\circ}\mathsf{C} = 124^{\circ}\mathsf{C} \end{aligned}$$

The use of multi-layer board construction with power planes will further enhance the overall thermal performance. In the event of no dedicated copper area being used for heat spreading, a multi-layer board will typically provide the CAT3200 with an overall  $\theta_{JA}$  of 200°C/W. This level of thermal conduction would allow up to 200mW be safely dissipated within the device.

## **TYPICAL APPLICATIONS**

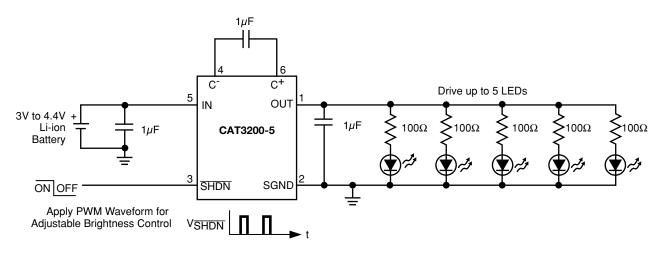

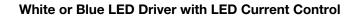

#### Lithium-Ion Battery to 5V White or Blue LED Driver

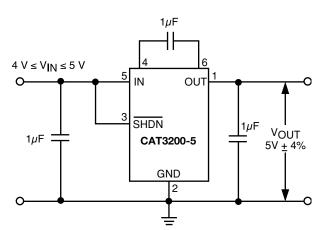

#### USB Port to Regulated 5V Power Supply

D1

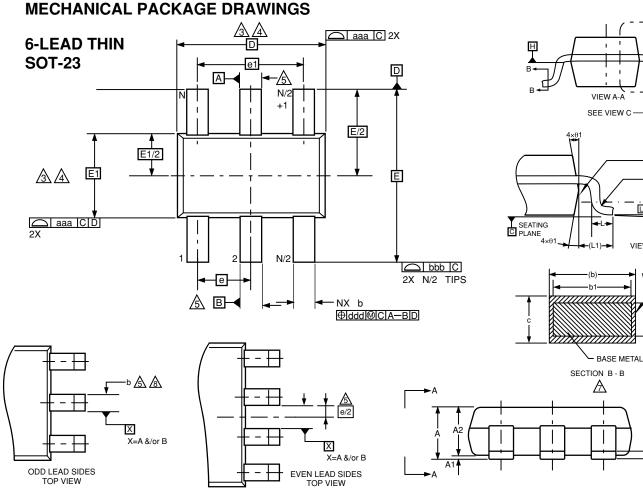

VIEW C

WITH METAL

GAUGE PLAN⊏

SEATING

C PLANE

#### TOP VIEW

All Dimensions are in Millimeters

|    | Min     | Nom Max |            | Notes |

|----|---------|---------|------------|-------|

| A  | _       | —       | 1.00       |       |

| A1 | 0.01    | 0.05    | 0.10       |       |

| A2 | 0.84    | 0.87    | 0.90       |       |

| С  | 0.12    | 0.15    | 0.20       | 7     |

| c1 | 0.08    | 0.13    | 0.16       | 7     |

| D  | 2.80    | 2.90    | 3.00       | 3,4   |

| E  | 2.60    | 2.80    | 3.00       | 3,4   |

| E1 | 1.50    | 1.60    | 1.75       | 3,4   |

| L  | 0.30    | 0.40    | 0.50       |       |

| L1 | 0.60REF |         |            |       |

| L2 |         | 0.25BSC |            |       |

| R  | 0.10    | _       | _          |       |

| R1 | 0.10    | — 0.25  |            |       |

| θ  | 0°      | 4°      | <b>8</b> ° |       |

| θ1 | 4°      | 10°     | 10° 12°    |       |

|       | Tolerances of Form and Position |      |      |          |             |         | Note | s    |      |       |

|-------|---------------------------------|------|------|----------|-------------|---------|------|------|------|-------|

| aaa   | 0.15                            |      |      |          |             |         |      | 1,2  |      |       |

| bbb   | 0.25                            |      |      |          |             | 1,2     |      |      |      |       |

| ccc   | 0.10                            |      |      |          |             | 1,2     |      |      |      |       |

|       | 1                               |      |      |          | Variation   | s       |      |      |      |       |

|       |                                 | AA   |      |          | <u>6</u> AB |         |      | BA   |      |       |

|       | Min                             | Nom  | Max  | Min      | Nom         | Max     | Min  | Nom  | Max  | Notes |

| b     | 0.30                            | —    | 0.45 | 0.30     | —           | 0.45    | 0.22 | _    | 0.36 | 7,8   |

| b1    | 0.31                            | 0.35 | 0.39 | 0.31     | 0.35        | 0.39    | 0.22 | 0.26 | 0.30 |       |

| е     | 0.95BSC 0.95BSC                 |      |      | ;        | 0.65BSC     |         |      |      |      |       |

| e1    | 1.90BSC 1.90BSC                 |      |      |          | 1.95BSC     |         |      |      |      |       |

| Ν     | 6                               |      |      | 5        |             | 8       |      |      |      |       |

|       | 1                               |      | Tole | rances o | f Form a    | nd Posi | tion |      |      | 1     |

| ddd   | 0.20                            |      | 0.20 |          | 0.13        |         | 1,2  |      |      |       |

| otes: | 1                               |      |      | 1        |             |         | 1    |      |      | 1     |

Dimensions and tolerancing per ASME Y14.5M - 1994 Dimension are in mm. Dimension are in mm. Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per end. Dimension E1 does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.15mm per side. D and E1 dimensions are determined at Datum H. Nerd E1 are determined at the externment enterman of the plastic hody evolution of world floath the her.

The package top may be smaller than the package bottom. Dimensions D and E1 are determined at the outermost extremest of the plastic body exclusive of mold flash, the bar burrs, gate burrs and interlead flash, but including any mismatch between the top and bottom of the plastic body. D and E1 dimensions are determined at Datum H. <u>A</u>. Datums A & B to be determined at Datum H.

∕\$.

Package varation "AB" is a 5 lead version of the 6 lead variation "AA" where lead #5 has been removed from the 6 lead "AA" variation.

2. 3.

These dimensions apply to the flat section of the lead between 0.08mm and 0.15mm from the lead tip.

Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall be 0.08mm total in excess of the "b" dimension at maximum material condition. The dambar cannot be located on the lower radius of the foot. Minimum space between protrusion and an adjacent lead shall not be less than 0.07mm.

### **MECHANICAL PACKAGE DRAWINGS**

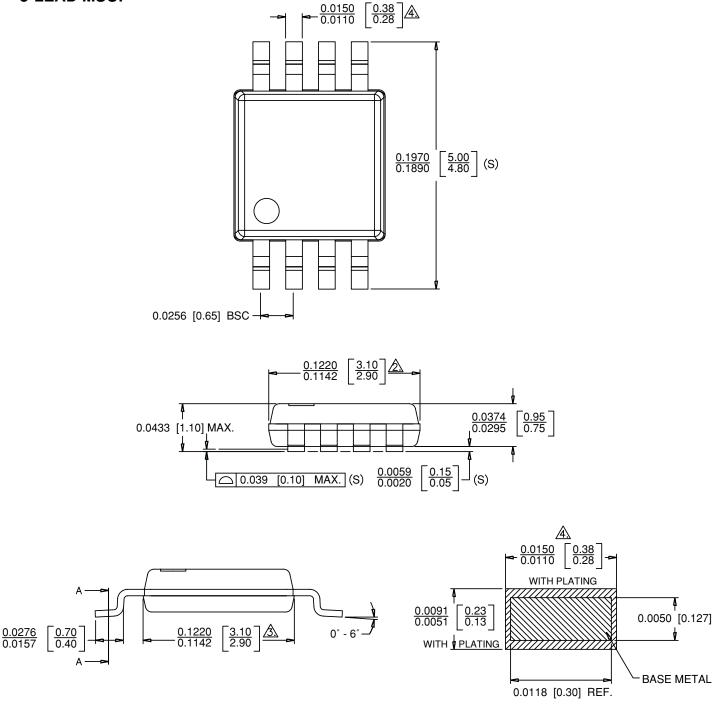

#### 8-LEAD MSOP

SECTION A - A

#### Notes:

- (1) All dimensions are in mm Angles in degrees.

- 🖄 Does not include Mold Flash, Protrusion or Gate Burrs. Mold Flash, Protrusions or Gate Burrs shall not exceed 0.15 mm. per side.

- Does not include Interlead Flash or Protrusion. Interlead Flash or Protrusion shall not exceed 0.25 mm per side.

Does not include Dambar Protrusion, allowable Dambar Protrusion shall be 0.08 mm.

- (5) This part is compliant with JEDEC Specification MO-187 Variations AA.

- (6) Lead span/stand off height/coplanarity are considered as special characteristics. (S)

- (7) Controlling dimensions in inches. [mm]

### **REVISION HISTORY**

| Date       | Rev. | Reason                                          |

|------------|------|-------------------------------------------------|

| 06/17/2004 | Α    | Initial Release                                 |

| 09/3/2004  | В    | Update Ordering Information                     |

| 09/23/2004 | С    | Minor change                                    |

| 10/26/2004 | D    | Removed TDFN package, minor changes             |

| 10/29/2004 | Е    | Added Green Packages                            |

| 02/1/2005  | F    | Update 6-lead SOT-23 mechanical package drawing |

| 02/28/2005 | G    | Update Ordering Information                     |

| 03/18/2005 | Н    | Update Ordering Information                     |

| 09/22/2005 | Ι    | Update Ordering Information                     |

| 01/11/2006 | J    | Update Ordering Information                     |

| 08/01/2006 | K    | Change MSOP Tape&Reel                           |

#### Copyrights, Trademarks and Patents

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following:

DPP <sup>™</sup> AE<sup>2</sup> <sup>™</sup> MiniPot<sup>™</sup>

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents issued to Catalyst Semiconductor contact the Company's corporate office at 408.542.1000.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc. Corporate Headquarters 2975 Stender Way Santa Clara, CA 95054 Phone: 408.542.1000 Fax: 408.542.1200

Publication #: 5002 Revison: K