## Linear Integrated Systems

| FEATURES                                      |                                 |                              |  |  |  |

|-----------------------------------------------|---------------------------------|------------------------------|--|--|--|

| ULTRA LOW NOISE                               | e <sub>n</sub> :                | = 0.9nV/√Hz (typ)            |  |  |  |

| TIGHT MATCHING                                | V <sub>G</sub>                  | <sub>S1-2</sub>   = 20mV max |  |  |  |

| HIGH BREAKDOWN VOLTAGE                        | В                               | V <sub>GSS</sub> = 40V max   |  |  |  |

| HIGH GAIN                                     | HIGH GAIN $Y_{fs} = 20mS (typ)$ |                              |  |  |  |

| LOW CAPACITANCE 25pF typ                      |                                 |                              |  |  |  |

| IMPROVED SECOND SOURCE REPLACEMENT FOR 2SK389 |                                 |                              |  |  |  |

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>         |                                 |                              |  |  |  |

| @ 25 °C (unless otherwise stated)             |                                 |                              |  |  |  |

| Maximum Temperatures                          |                                 |                              |  |  |  |

| Storage Temperature                           |                                 | -65 to +150 °C               |  |  |  |

| Operating Junction Temperature                |                                 | -55 to +135 °C               |  |  |  |

| Maximum Power Dissipation                     |                                 |                              |  |  |  |

| Continuous Power Dissipation @ +125 °C        |                                 | 400mW                        |  |  |  |

| Maximum Currents                              |                                 |                              |  |  |  |

| Gate Forward Current                          |                                 | $I_{G(F)} = 10mA$            |  |  |  |

| Maximum Voltages                              |                                 |                              |  |  |  |

| Gate to Source                                |                                 | $V_{GSS} = 40V$              |  |  |  |

| Gate to Drain                                 | $V_{GDS} = 40V$                 |                              |  |  |  |

# **LSK389**

# ULTRA LOW NOISE MONOLITHIC DUAL N-CHANNEL JFET

\*For equivalent single version, see LSK170 family.

## MATCHING CHARACTERISTICS @ 25 °C (unless otherwise stated)

| SYMBOL                         | CHARACTERISTIC                             | MIN | TYP | MAX | UNIT | CONDITIONS                                  |

|--------------------------------|--------------------------------------------|-----|-----|-----|------|---------------------------------------------|

| $\left V_{GS1}-V_{GS2}\right $ | Differential Gate to Source Cutoff Voltage |     |     | 20  | mV   | $V_{DS}$ = 10V, $I_D$ = 1mA                 |

| I <sub>DSS1</sub>              | Gate to Source Saturation Current Ratio    | 0.9 |     |     | -    | V <sub>DS</sub> = 10V, V <sub>GS</sub> = 0V |

#### ELECTRICAL CHARACTERISTICS @ 25 °C (unless otherwise stated)

| SYMBOL            | CHARACTERISTIC                     |         | MIN  | TYP | MAX | UNITS | CONDITIONS                                  |

|-------------------|------------------------------------|---------|------|-----|-----|-------|---------------------------------------------|

| BV <sub>GSS</sub> | Gate to Source Breakdown Voltage   |         | 40   |     | 7   | V     | $V_{DS} = 0$ , $I_{D} = 100 \mu A$          |

| $V_{GS(OFF)}$     | Gate to Source Pinch-off Voltage   |         | 0.15 |     | 2   | V     | $V_{DS} = 10V, I_D = 0.1 \mu A$             |

|                   | Drain to Source Saturation Current | LSK389A | 2.6  |     | 6.5 | mA    | V <sub>DS</sub> = 10V, V <sub>GS</sub> = 0  |

| I <sub>DSS</sub>  |                                    | LSK389B | 6    |     | 12  |       |                                             |

|                   |                                    | LSK389C | 10   |     | 20  |       |                                             |

| I <sub>GSS</sub>  | Gate to Source Leakage Current     |         |      |     | 200 | рА    | V <sub>GS</sub> = -30V, V <sub>DS</sub> = 0 |

#### ELECTRICAL CHARACTERISTICS CONT. @ 25 °C (unless otherwise stated)

| SYMBOL           | CHARACTERISTIC                      | MIN | TYP | MAX | UNITS  | CONDITIONS                                                    |

|------------------|-------------------------------------|-----|-----|-----|--------|---------------------------------------------------------------|

| Y <sub>fs</sub>  | Full Conduction Transconductance    | 8   | 20  |     | mS     | $V_{DS} = 10V$ , $V_{GS} = 0$ , $I_{DSS} = 3mA$ ,<br>f = 1kHz |

| e <sub>n</sub>   | Noise Voltage                       |     | 0.9 | 1.9 | nV/√Hz | $V_{DS}$ = 10V, $I_{D}$ = 2mA, $f$ = 1kHz,<br>NBW = 1Hz       |

| e <sub>n</sub>   | Noise Voltage                       |     | 2.5 | 4   | nV/√Hz | $V_{DS} = 10V$ , $I_{D} = 2mA$ , $f = 10Hz$ , NBW = 1Hz       |

| C <sub>ISS</sub> | Common Source Input Capacitance     |     | 25  |     | pF     | $V_{DS} = 10V, V_{GS} = 0, f = 1MHz,$                         |

| C <sub>RSS</sub> | Common Source Reverse Transfer Cap. |     | 5.5 |     | pF     | $V_{DG} = 10V, I_{D} = 0, f = 1MHz,$                          |

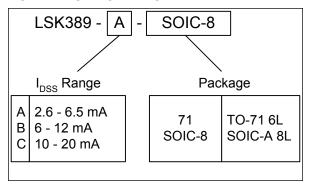

#### ORDERING INFORMATION

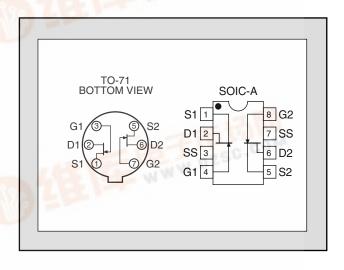

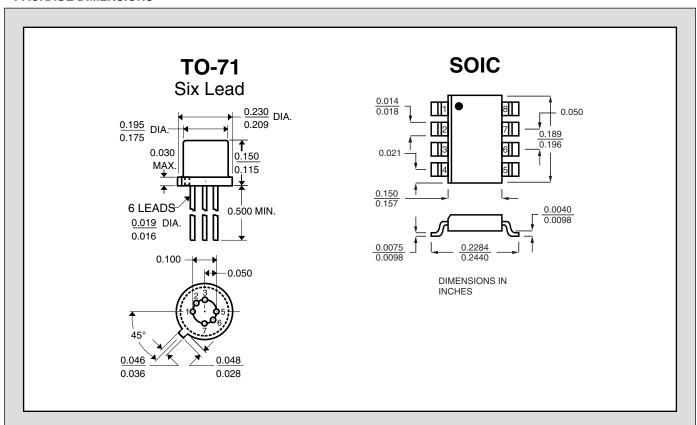

## **PACKAGE DIMENSIONS**

1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems. Revised 07 December 2005.