# LH5497

CMOS 1K × 9 FIFO

#### **FEATURES**

- Fast Access Times:

15/20/25/35/50/65/80 ns

- Full CMOS Dual Port Memory Array

- Fully Asynchronous Read and Write

- Expandable in Width and Depth

- Full, Half-Full, and Empty Status Flags

- Read Retransmit Capability

- TTL Compatible I/O

- Packages:

28-Pin, 300-mil DIP

28-Pin, 600-mil DIP

32-Pin PLCC

- Pin and Functionally Compatible with IDT7202

### **FUNCTIONAL DESCRIPTION**

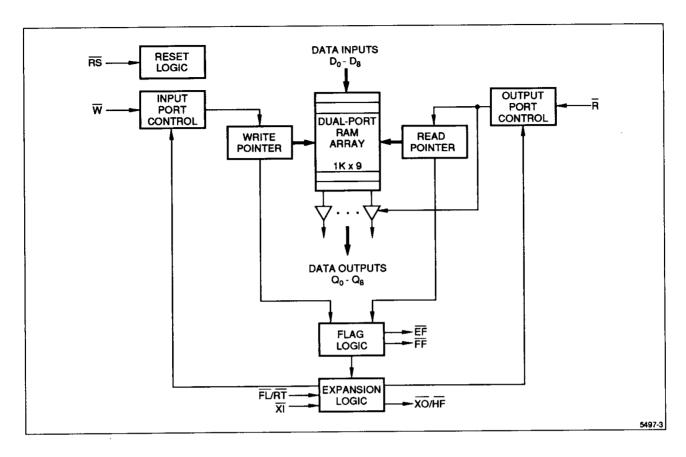

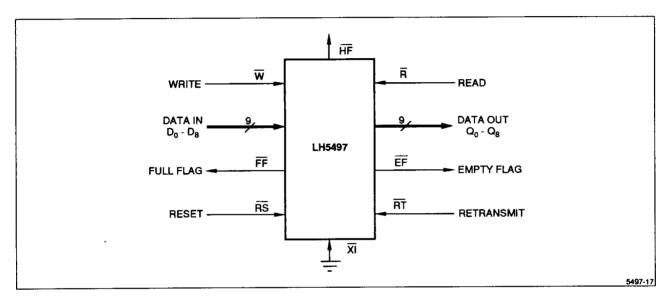

The LH5497 is a dual port memory with internal addressing to implement a First-In, First-Out algorithm. Through an advanced dual port architecture, it provides fully asynchronous read/write operation. Empty, Full, and Half-Full status flags are provided to prevent data overflow and underflow. In addition, internal logic is provided for unlimited expansion in both word size and depth.

Read and Write operations automatically access sequential locations in memory in such a way that data is read out in the same order that it was written, that is on a First-In, First-Out basis. Since the address sequence is internally predefined, no external address information is required for the operation of this device. A ninth data bit is provided for parity or control information often needed in communication applications.

Empty, Full, and Half-Full status flags monitor the extent to which data has been written into the FIFO, and prevent improper operations (i.e. Read if the FIFO is empty, or Write if the FIFO is full). A retransmit feature resets the Read address pointer to its initial position, thereby allowing repetitive readout of the same data. Expansion In and Expansion Out pins implement an expansion scheme that allows individual FIFOs to be cascaded to greater depth without incurring additional latency (bubblethrough) delays.

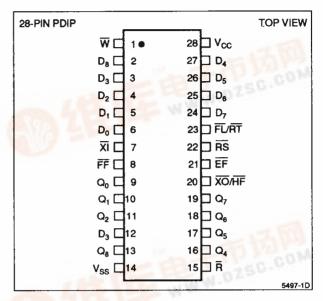

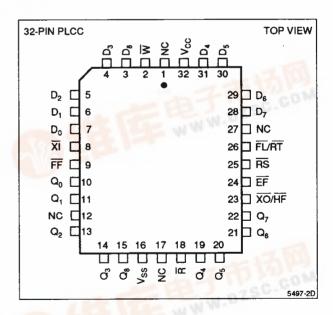

### PIN CONNECTIONS

Figure 1. Pin Connections for DIP Package

Figure 2. Pin Connections for PLCC Package

Figure 3. LH5497 Block Diagram

## **PIN DESCRIPTIONS**

| PIN PIN TYPE *                      |   | DESCRIPTION     |

|-------------------------------------|---|-----------------|

| D <sub>0</sub> – D <sub>8</sub>     |   | Input Data Bus  |

| Q <sub>0</sub> – Q <sub>8</sub> O/Z |   | Output Data Bus |

| w                                   | ı | Write Request   |

| R                                   | ı | Read Request    |

| ĒF                                  | 0 | Empty Flag      |

| FF                                  | 0 | Full Flag       |

| * I Innut O      | Outsut 7    | High-Impedance,       | V - Powe | r Voltage | Level  |

|------------------|-------------|-----------------------|----------|-----------|--------|

| - I = Input. U = | Outout, Z = | · migri-illipedalice, | V = LOM6 | n vollage | CC 4C1 |

| PIN   | PIN TYPE * | DESCRIPTION                  |

|-------|------------|------------------------------|

| XO/HF | 0          | Expansion Out/Half-Full Flag |

| XI    | ı          | Expansion In                 |

| FL/RT | ı          | First Load/Retransmit        |

| RS    | ı          | Reset                        |

| Vcc   | V          | Positive Power Supply        |

| Vss   | V          | Ground                       |

# ABSOLUTE MAXIMUM RATINGS 1

| PARAMETER                                     | RATING                                                |  |  |  |  |  |  |

|-----------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| Supply Voltage to Vss Potential               | -0.5 V to 7 V                                         |  |  |  |  |  |  |

| Signal Pin Voltage to Vss Potential 3         | -0.5 V to V <sub>CC</sub> + 0.5 V (not to exceed 7 V) |  |  |  |  |  |  |

| DC Output Current <sup>2</sup>                | ± 50 mA                                               |  |  |  |  |  |  |

| Storage Temperature Range                     | -65°C to 150°C                                        |  |  |  |  |  |  |

| Power Dissipation (Package Limit)             | 1.0 W                                                 |  |  |  |  |  |  |

| DC Voltage Applied to Outputs in High-Z State | -0.5 V to Vcc + 0.5 V (not to exceed 7 V)             |  |  |  |  |  |  |

#### NOTES:

- Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating for transient conditions only. Functional operation of the device at these or any other conditions above those indicated in the "Operating Range" of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

- 3. Negative undershoots of 1.5 V in amplitude are permitted for up to 10 ns once per cycle.

#### **OPERATING RANGE**

| SYMBOL                         | PARAMETER                            | MIN  | MAX       | UNIT |  |  |

|--------------------------------|--------------------------------------|------|-----------|------|--|--|

| TA                             | Temperature, Ambient                 | 0    | 70        | °C   |  |  |

| V <sub>CC</sub> Supply Voltage |                                      | 4.5  | 5.5       |      |  |  |

| Vss Supply Voltage             |                                      | 0    | 0         | ٧    |  |  |

| VIL                            | Logic "0" Input Voltage <sup>1</sup> | -0.5 | 0.8       | ٧    |  |  |

| ViH                            | Logic "1" Input Voltage              | 2.0  | Vcc + 0.5 | V    |  |  |

#### NOTE:

# DC ELECTRICAL CHARACTERISTICS (Over Operating Range)

| SYMBOL | PARAMETER                       | TEST CONDITIONS                                                | MIN | MAX | UNIT |

|--------|---------------------------------|----------------------------------------------------------------|-----|-----|------|

| lu     | Input Leakage Current           | Vcc = 5.5 V, Vin = 0 V to Vcc                                  | -10 | 10  | μΑ   |

| ILO    | Output Leakage Current          | R ≥ V <sub>IH</sub> , 0 V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub> | -10 | 10  | μA   |

| Vон    | Output High Voltage             | I <sub>OH</sub> = -2.0 mA                                      | 2.4 | _   | ٧    |

| Vol    | Output Low Voltage              | I <sub>OL</sub> = 8.0 mA                                       | Ī   | 0.4 | ٧    |

| lcc    | Average Supply Current 1        | Measured at f = 40MHz                                          | _   | 100 | mA   |

| lcc2   | Average Standby Current 1       | All Inputs = VIH                                               | _   | 15  | mA   |

| Іссз   | Power Down Current <sup>1</sup> | All Inputs = Vcc - 0.2V                                        | _   | 5   | mA   |

#### NOTE:

1. Icc, Icc2, and Icc3 are dependent upon actual output loading and cycle rates. Specified values are with outputs open.

SHARP 5-33

<sup>1.</sup> Negative undershoots of 1.5 V in amplitude are permitted for up to 10 ns once per cycle.

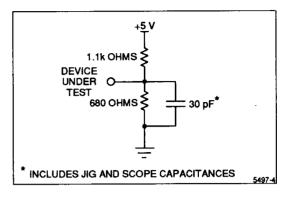

## **AC TEST CONDITIONS**

| PARAMETER                                 | RATING     |

|-------------------------------------------|------------|

| Input Pulse Levels                        | Vss to 3 V |

| Input Rise and Fall Times<br>(10% to 90%) | 5 ns       |

| Input Timing Reference Levels             | 1.5 V      |

| Output Reference Levels                   | 1.5 V      |

| Output Load, Timing Tests                 | Figure 4   |

# CAPACITANCE 1,2

| PARAMETER                   | RATING |

|-----------------------------|--------|

| CIN MAX (Input Capacitance) | 5 pF   |

| MAX (Output Capacitance)    | 7 pF   |

Figure 4. Output Load Circuit

#### NOTES:

- 1. Sample tested only.

- 2. Capacitances are maximum values at 25°C measured at 1.0MHz with  $V_{\text{IN}}$  = 0 V.

# AC ELECTRICAL CHARACTERISTICS 1 (Over Operating Range)

| <del></del> 7                                                          |                                            |                | 5 ns           | ta = 2         | 10 ns       | t <sub>A</sub> = 2 | 5 ns       | t <sub>A</sub> = 3 | 5 ns         | t <sub>A</sub> = 5 | 0 ns       | t_ = 6     | 5 ns | t <sub>A</sub> = 8 | 0 ns     | UNITS |

|------------------------------------------------------------------------|--------------------------------------------|----------------|----------------|----------------|-------------|--------------------|------------|--------------------|--------------|--------------------|------------|------------|------|--------------------|----------|-------|

| SYMBOL                                                                 | PARAMETER                                  |                | MAX            | MIN            | MAX         | MIN                | MAX        | MIN                | MAX          | MIN                | MAX        | MIN        | MAX  | MIN                | MAX      | UNIIS |

| READ CYCLE TIMING                                                      |                                            |                |                |                |             |                    |            |                    |              |                    |            |            |      |                    |          |       |

| t <sub>RC</sub> Read Cycle Time 25 - 30 - 35 - 45 - 65 - 80 - 100 - ns |                                            |                |                |                |             |                    |            |                    |              |                    |            |            |      |                    |          |       |

| t <sub>A</sub>                                                         | Access Time                                | _              | 15             | _              | 20          | _                  | 25         | -                  | 35           | _                  | 50         | _          | 65   | _                  | 80       | ns    |

| t <sub>RR</sub>                                                        | Read Recover Time                          | 10             | _              | 10             | _           | 10                 | _          | 10                 | _            | 15                 | -          | 15         | 1    | 15·                | _        | ns    |

| tapw                                                                   | Read Pulse Width <sup>2</sup>              | 15             | _              | 20             | -           | 25                 | _          | 35                 | -            | 50                 | -          | 65         | ı    | 80                 | _        | ns    |

| talz                                                                   | Data Bus Active from Read LOW 3            | 5              | _              | 5              | -           | 5                  | -          | 5                  | -            | 5                  | 1          | 5          |      | 10                 | _        | ns    |

| twLz                                                                   | Data Bus Active from Write HIGH 3,4        | 10             | _              | 10             | _           | 10                 | _          | 10                 | ı            | 10                 | 1          | 10         | _    | 20                 | _        | ns    |

| tov                                                                    | Data Valid from Read Pulse HIGH            | 5              | _              | 5              | -           | 5                  | 1          | 5                  | _            | 5                  | -          | 5          |      | 5                  |          | ns    |

| t <sub>RHZ</sub>                                                       | Data Bus High-Z from Read HIGH 3           | _              | 15             | _              | 15          | -                  | 15         | -                  | 15           | _                  | 20         | _          | 30   | _                  | 30       | ns    |

| 411112                                                                 |                                            | <b>1</b>       | WRI            | TE C           | CLE         | TIMIN              | lG         |                    |              |                    |            |            |      |                    |          |       |

| two Write Cycle Time 25 - 30 - 35 - 45 - 65 - 80 - 100 - ns            |                                            |                |                |                |             |                    |            |                    |              |                    |            |            |      |                    |          |       |

| twew                                                                   | Write Pulse Width <sup>2</sup>             | 15             | _              | 20             | _           | 25                 | _          | 35                 | _            | 50                 | _          | 65         | _    | 80                 | -        | ns    |

| twn                                                                    | Write Recovery Time                        | 10             | -              | 10             | _           | 10                 | _          | 10                 | _            | 15                 |            | 15         | _    | 15                 | -        | ns    |

| tos                                                                    | Data Setup Time                            | 10             | T -            | 10             | _           | 10                 | -          | 15                 | _            | 20                 | _          | 20         | _    | 20                 | -        | ns    |

| t <sub>DH</sub>                                                        | Data Hold Time                             | 0              | _              | 0              | _           | 0                  | _          | 0                  | _            | 0                  |            | 5          |      | 5                  |          | ns    |

| -5/1                                                                   |                                            | •              |                | RESE           | T TIM       | ING                |            |                    |              |                    |            |            |      |                    |          |       |

| trsc                                                                   | Reset Cycle Time                           | 25             | _              | 30             | <u> </u>    | 35                 | _          | 45                 | Γ-           | 65                 | _          | 80         | _    | 100                | _        | ns    |

| trs                                                                    | Reset Pulse Width <sup>2</sup>             | 15             | _              | 20             | _           | 25                 | _          | 35                 | _            | 50                 | _          | 65         | -    | 80                 | _        | กร    |

| tasa                                                                   | Reset Recovery Time                        | 10             | _              | 10             | _           | 10                 | _          | 10                 | _            | 15                 | _          | 15         | _    | 15                 | _        | ns    |

| teres                                                                  | Read HIGH to RS HIGH                       | 15             | _              | 20             | _           | 25                 | _          | 35                 | _            | 50                 | _          | 65         | -    | 80                 | -        | ns    |

| twass                                                                  | Write HIGH to RS HIGH                      | 15             | -              | 20             | _           | 25                 | _          | 35                 | _            | 50                 | _          | 65         | _    | 80                 | _        | ns    |

| WHOO                                                                   |                                            |                | RE             | TRAN           | SMIT        | TIMIN              | lG         |                    |              |                    |            |            |      |                    |          |       |

| trtc                                                                   | Retransmit Cycle Time                      | 25             | _              | 30             | _           | 35                 | <u> </u>   | 45                 | _            | 65                 | _          | 80         | _    | 100                |          | ns    |

| tRT                                                                    | Retransmit Pulse Width <sup>2</sup>        | 15             | <b> </b>       | 20             | T -         | 25                 | _          | 35                 | -            | 50                 | -          | 65         |      | 80                 |          | ns    |

| t <sub>RTR</sub>                                                       | Retransmit Recovery Time                   | 10             | -              | 10             | _           | 10                 | _          | 10                 | _            | 15                 | _          | 15         |      | 15                 |          | ns    |

| unin                                                                   |                                            |                | .1             | FLAG           | G TIM       | ING                |            |                    |              |                    |            |            |      |                    |          |       |

| 1==:                                                                   | Reset LOW to Empty Flag LOW                | Τ_             | 25             | T _            | 30          | T -                | 35         | _                  | 45           | _                  | 65         | -          | 80   | _                  | 100      | ns    |

| <sup>1</sup> EFL<br><sup>1</sup> HFH,FFH                               | Reset LOW to Half-Full and Full Flags HIGH | -              | 25             | -              | 30          | -                  | 35         | -                  | 45           | -                  | 65         | -          | 80   | -                  | 100      | ns    |

| toes                                                                   | Read LOW to Empty Flag LOW                 | <del>  -</del> | 20             | Τ_             | 25          | _                  | 25         | -                  | 35           | -                  | 45         | -          | 60   | _                  | 60       | ns    |

| tnes                                                                   | Read HIGH to Full Flag HIGH                | <b> </b>       | 20             | T_             | 25          | <u> </u>           | 25         | -                  | 35           | T-                 | 45         | _          | 60   | -                  | 60       | ns    |

| tref                                                                   | Write HIGH to Empty Flag HIGH              | -              | 20             | <b>T</b> -     | 25          | _                  | 25         | _                  | 35           | _                  | 45         | T-         | 60   |                    | 60       | ns    |

| twer                                                                   | Write LOW to Full Flag LOW                 | _              | 20             | 1 -            | 25          | <b> </b>           | 25         | -                  | 35           | -                  | 45         | -          | 60   | _                  | 60       | ns    |

| twee                                                                   | Write LOW to Half-Full Flag LOW            | <b>-</b>       | 25             | <b> </b>       | 30          | T-                 | 35         | T -                | 45           | _                  | 65         | <b> </b> - | 80   |                    | 100      | ns    |

| t <sub>RHF</sub>                                                       | Read HIGH to Half-Full Flag HIGH           | _              | 25             | _              | 30          | -                  | 35         | -                  | 45           | -                  | 65         | <b> </b> - | 80   |                    | 100      | ns    |

| 4NHF                                                                   | 1100011101101101                           |                | EX             | PANS           | SION        | TIMIN              | IG         | •                  | •            |                    |            |            |      |                    |          |       |

| tvo                                                                    | Expansion Out LOW                          | Τ_             | 18             | T -            | 20          | Ι –                | 25         | Τ –                | 35           | _                  | 50         | T -        | 65   | -                  | 80       | ns    |

| txoL                                                                   | Expansion Out HIGH                         | †_             | 18             | <del>  _</del> | 20          | _                  | 25         | 1 -                | 35           | -                  | 50         | T-         | 65   | <b> </b>           | 80       | ns    |

| txon tvi                                                               | Expansion In Pulse Width                   | 15             | <del>  -</del> | 20             | <del></del> | 25                 | -          | 35                 | <b> </b>     | 50                 | -          | 65         | -    | 80                 | <b> </b> | ns    |

| txi                                                                    | Expansion in Recovery Time                 | 10             | † <u>-</u>     | 10             | -           | 10                 | -          | 10                 | † –          | 10                 | <b> </b> - | 10         | -    | 10                 | _        | ns    |

| txiR                                                                   | Expansion in Setup Time                    | 7              | † <u> </u>     | 10             | +           | 10                 | † <u>-</u> | 15                 | <del> </del> | 15                 | T-         | 15         | 1 -  | 15                 | _        | ns    |

| txis                                                                   | Lyanson in Octop time                      |                |                | 1              |             | 1                  | ٠          |                    | -1           | 1                  |            | ,1         | _1   | •                  | •        |       |

#### NOTES:

- 1. All timing measurements performed at "AC Test Condition" levels.

- 2. Pulse widths less than minimum value are not allowed.

- 3. Values guaranteed by design not currently tested.

- 4. Only applies to read data flow-through mode.

CMOS 1K×9 FIFO

#### **OPERATIONAL DESCRIPTION**

#### Reset

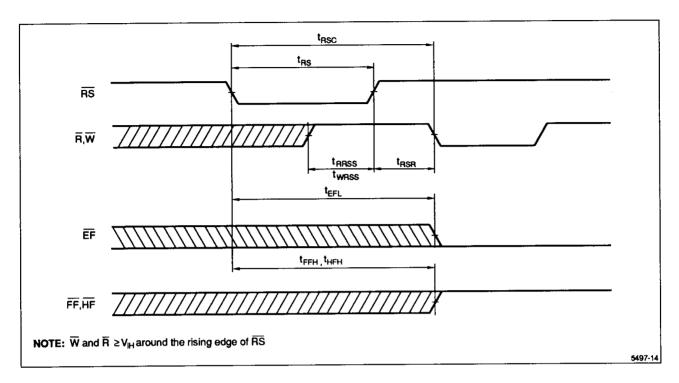

The device is reset whenever the Reset pin  $(\overline{RS})$  is taken to a LOW state. The reset operation initializes both the read and write address pointers to the first memory location. The  $\overline{XI}$  and  $\overline{FL}$  pins are also sampled at this time to determine whether the device is in Single mode or Depth Expansion mode. A reset pulse is required when the device is first powered up. The Read  $(\overline{R})$  and Write  $(\overline{W})$  pins may be in any state when reset is initiated, but must be brought to a HIGH state tapw and twpw before the rising edge of  $\overline{RS}$ .

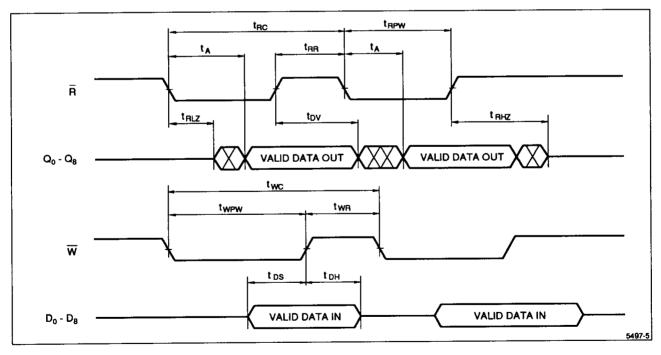

#### Write

A write cycle is initiated on the falling edge of the Write  $(\overline{W})$  pin. Data setup and hold times must be observed on the data in  $(D_0 - D_8)$  pins. A write operation is only possible if the FIFO is not full, (i.e. the Full flag pin is HIGH). Writes may occur independently of any ongoing read operations.

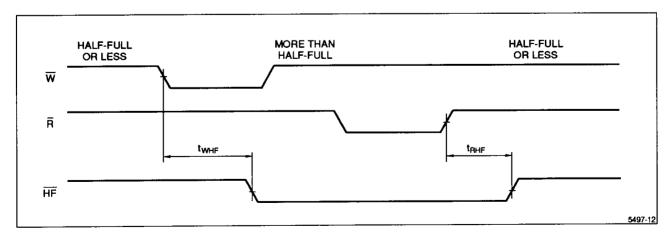

At the falling edge of the first write after the memory is half filled, the Half-Full flag will be asserted ( $\overline{HF}$  = LOW) and will remain asserted until the difference between the write pointer and read pointer indicates that the remaining data in the device is less than or equal to one half the total capacity of the FIFO. The Half-Full flag is deasserted ( $\overline{HF}$  = HIGH) by the appropriate rising edge of  $\overline{R}$ .

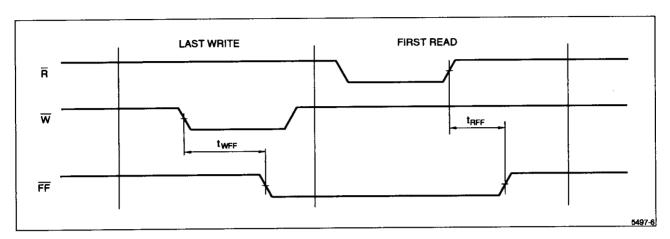

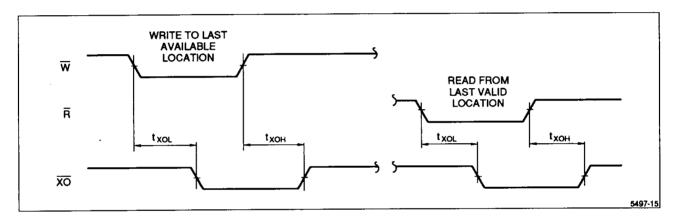

The Full flag is asserted ( $\overline{FF}$  = LOW) at the falling edge of the write operation which fills the last available location in the FIFO memory array. The Full flag will inhibit further writes until cleared by a valid read. The Full flag is deasserted ( $\overline{FF}$  = HIGH) after the next rising edge of  $\overline{R}$  releases another memory location.

### Read

A read cycle is initiated on the falling edge of the Read  $(\overline{R})$  pin. Read data becomes valid on the data out  $(Q_0-Q_8)$  pins after a time to from the falling edge of  $\overline{R}$ . After  $\overline{R}$  goes HIGH, the data out pins return to a high-impedance state. Reads may occur independent of any ongoing write operations. A read is only possible if the FIFO is not empty  $(\overline{EF} = HIGH)$ .

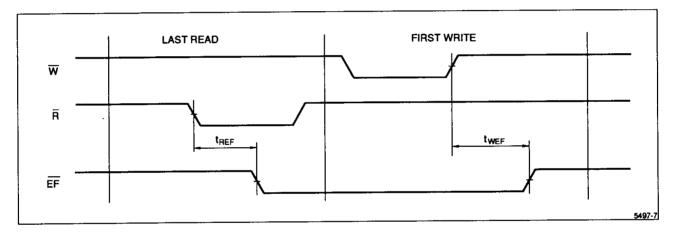

The internal read and write address pointers are maintained by the device such that consecutive read operations will access data in the same order as it was written. The Empty flag is asserted ( $\overline{\text{EF}}$  = LOW) after the falling edge of  $\overline{\text{R}}$  which accesses the last available data in the FIFO memory.  $\overline{\text{EF}}$  is deasserted ( $\overline{\text{EF}}$  = HIGH) after the next rising edge of  $\overline{\text{W}}$  loads another word of valid data.

#### **Data Flow-Through**

Read flow-through mode occurs when the Read  $(\overline{R})$  pin is brought LOW while the FIFO is empty, and held LOW in anticipation of a write cycle. At the end of the next write cycle, the Empty flag will be momentarily deasserted, and the data just written will become available on the data out pins after a maximum time of tweef + ta. Additional writes may occur while the  $\overline{R}$  pin remains LOW, but only data from the first write flows through to the outputs. Additional data, if any, can only be accessed by toggling  $\overline{R}$ .

Write flow-through mode occurs when the Write  $(\overline{W})$  pin is brought LOW while the FIFO is full, and held LOW in anticipation of a read cycle. At the end of the read cycle, the Full flag will be momentarily deasserted, but then immediately reasserted in response to  $\overline{W}$  held LOW. Data is written into the FIFO on the rising edge of  $\overline{W}$  which may occur the + twpw after the read.

#### Retransmit

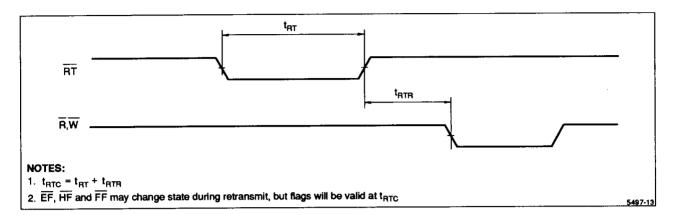

The FIFO can be made to reread previously read data through the retransmit function. Retransmit is initiated by pulsing  $\overline{RT}$  LOW. This resets the internal read address pointer to the first physical location in the memory while leaving the internal write address pointer unchanged. Data between the read and write pointers may be reaccessed by subsequent reads. Both  $\overline{R}$  and  $\overline{W}$  must be inactive (HIGH) during the retransmit pulse. Retransmit is useful if no more than 1024 writes are performed between resets. Retransmit may affect the status of  $\overline{EF}$ ,  $\overline{HF}$ , and  $\overline{FF}$  flags, depending on the relocation of the read pointer. This function is not available in depth expansion mode.

## **TIMING DIAGRAMS**

Figure 5. Reset Timing

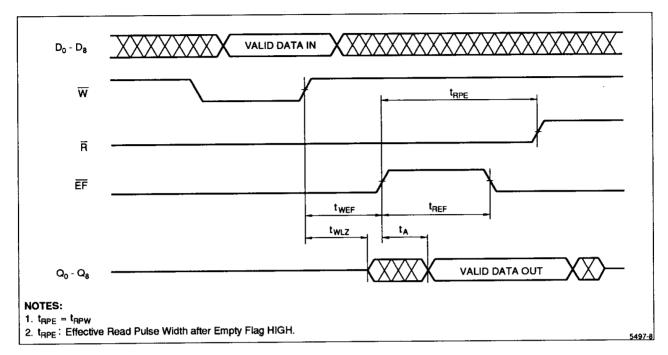

Figure 6. Asynchronous Write and Read Operation

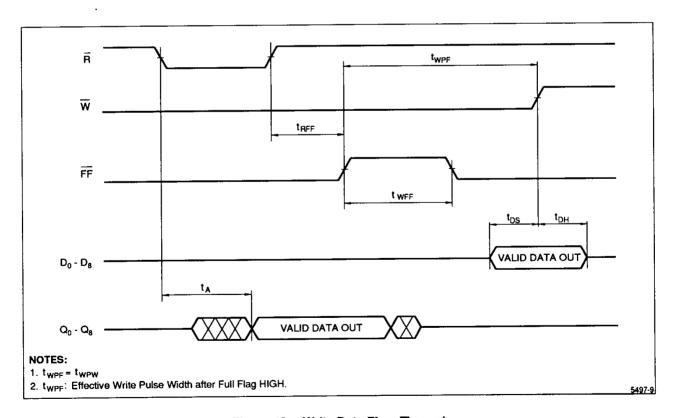

Figure 7. Full Flag from Last Write to First Read

Figure 8. Empty Flag from Last Read to First Write

Figure 9. Read Data Flow-Through

Figure 10. Write Data Flow-Through

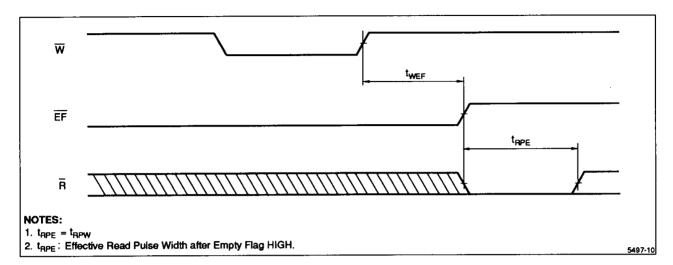

Figure 11. Empty Flag Timing

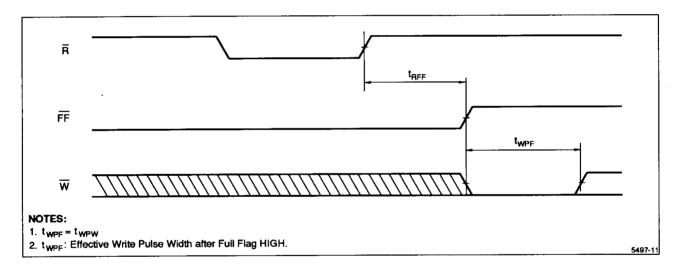

Figure 12. Full Flag Timing

Figure 13. Half-Full Flag Timing

Figure 14. Retransmit Timing

Figure 15. Expansion Out Timing

Figure 16. Expansion In Timing

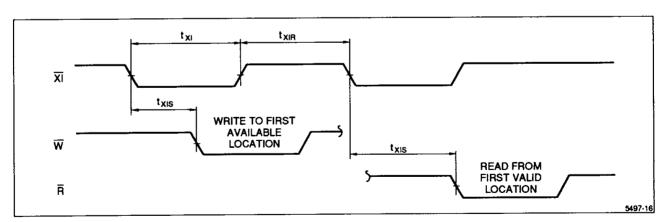

**CMOS 1K × 9 FIFO**

### **OPERATIONAL MODES**

### **Single Device Configuration**

When depth expansion is not required for the given application, the device is placed in Single mode by tying the Expansion In pin  $(\overline{X}I)$  to ground. This pin is internally sampled during reset.

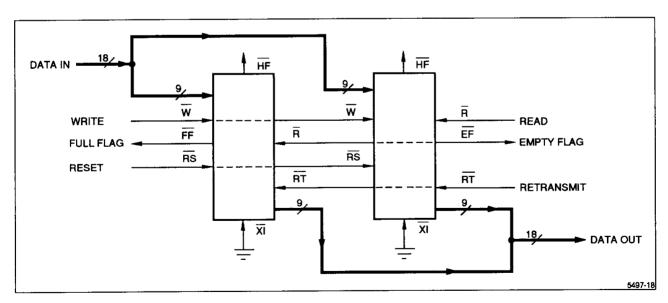

#### Width Expansion

Word-width expansion is implemented by placing multiple LH5497 devices in parallel. Each LH5497 should be configured for standalone mode. In this arrangement, the behavior of the status flags is identical for all devices; so, in principle, a representative value for each of these flags could be derived from any one device. In practice, it is better to derive 'composite' flag values using external logic, since there may be minor speed variations between different actual devices. (See Figures 17 and 18.)

Figure 17. Single FIFO (1K  $\times$  9)

Figure 18. FIFO Width Expansion (1K × 18)

# **OPERATIONAL MODES (cont'd)**

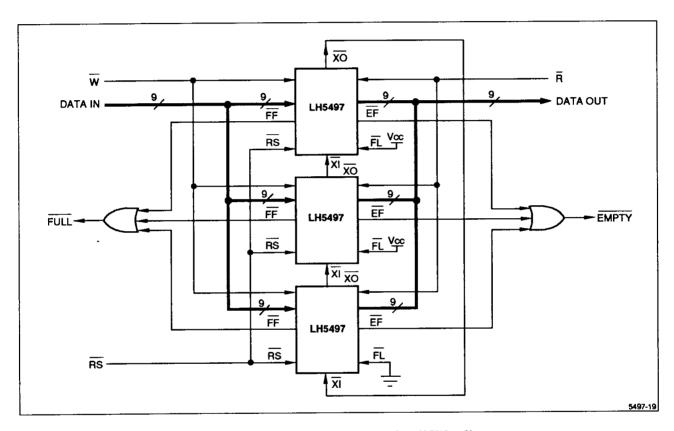

### **Depth Expansion**

Depth expansion is implemented by configuring the required number of FIFOs in Expansion mode. In this arrangement, the FIFOs are connected in a circular fashion with the Expansion Out pin  $(\overline{XO})$  of each device tied to the Expansion In pin  $(\overline{XI})$  of the next device. One FIFO in this group must be designated as the first load device. This is accomplished by tying the First Load pin  $(\overline{FL})$  of this device to ground. All other devices must have their  $\overline{FL}$  pin tied to a high level. In this mode,  $\overline{W}$  and  $\overline{R}$  signals

are shared by all devices, while internal logic controls the steering of data. Only one FIFO will be enabled for any given read cycle, so the common Data Out pins of all devices are wire-ORed together. Likewise, the common Data In pins of all devices are tied together.

In Expansion mode, external logic is required to generate a composite Full or Empty flag. This is achieved by ORing the  $\overline{FF}$  pins of all devices and ORing the  $\overline{EF}$  pins of all devices respectively. The Half-Full flag and Retransmit functions are not available in Depth Expansion mode.

Figure 19. FIFO Depth Expansion (3072 × 9)

# **OPERATIONAL MODES (cont'd)**

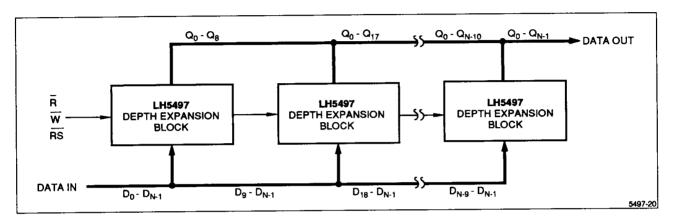

#### **Compound Expansion**

A combination of width and depth expansion can be easily implemented by operating groups of depth expanded FIFOs in parallel.

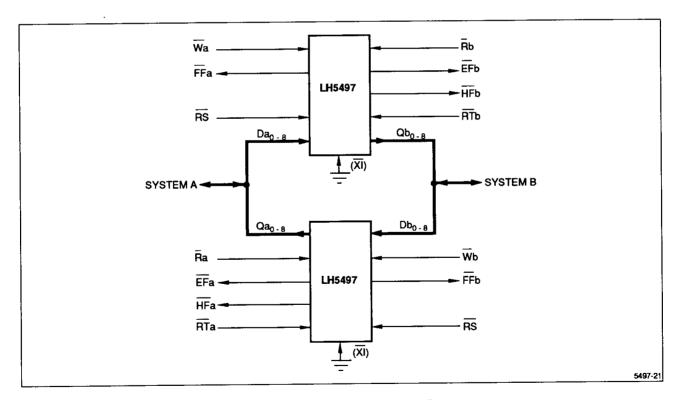

#### **Bidirectional Operation**

Applications which require bidirectional data buffering between two systems can be realized by operating

LH5497 devices in parallel but opposite directions. The Data In pins of a device may be tied to the corresponding Data Out pins of another device operating in the opposite direction to form a single bidirectional bus interface. Care must be taken to assure that the appropriate read, write, and flag signals are routed to each system. Both depth and width expansion may be used in this configuration.

Figure 20. Compound FIFO

Figure 21. Bidirectional FIFO

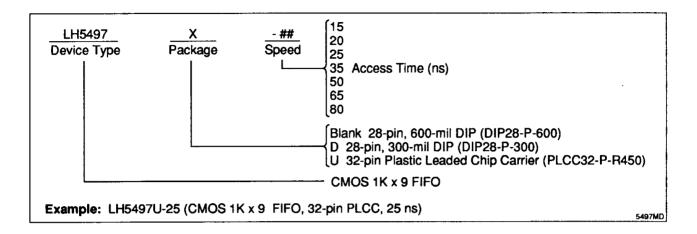

## **ORDERING INFORMATION**

**SHARP**