## Freescale Semiconductor Data Sheet

Document Number: SCF5249EC

Rev. 0, 04/2005

# SCF5249 Integrated ColdFire® Microprocessor Data Sheet

## 1 Introduction

This document provides an overview of the SCF5249 ColdFire® processor and general descriptions of SCF5249 features and its various modules.

The SCF5249 was designed as a system controller/decoder for MP3 music players, especially portable MP3 CD players. The 32-bit ColdFire core with Enhanced Multiply Accumulate (EMAC) unit provides optimum performance and code density for the combination of control code and signal processing required for MP3 decode, file management, and system control.

Low power features include a hardwired CD ROM decoder, advanced 0.18um CMOS process technology, 1.8V core power supply, and on-chip 96KByte SRAM. MP3 decode requires less than 20MHz CPU bandwidth and runs in on-chip SRAM with external access only for data input and output.

The SCF5249 is also an excellent general purpose system controller with over 125 Dhrystone 2.1 MIPS @ 140MHz performance at a very competitive price. The

#### **Table of Contents**

| 1  | Introduction                    | 1  |

|----|---------------------------------|----|

| 2  | SCF5249 Block Diagram           | 3  |

| 3  | SCF5249 Feature Details         | 3  |

| 4  | 160 MAPBGA Ball Assignments     | 6  |

| 5  | SCF5249 Functional Overview     |    |

| 3  | General Device Information      | 12 |

| 7  | Documentation                   | 12 |

| 3  | Signal Descriptions             | 13 |

| 9  | Electrical Characteristics      | 28 |

| 10 | Pin-Out and Package Information | 46 |

#### Introduction

integrated peripherals and EMAC allow the SCF5249 to replace both the microcontroller and the DSP in certain applications. Most peripheral pins can also be remapped as General Purpose I/O pins.

#### 1.1 Orderable Parts Numbers

#### 1.1.1 Orderable Part Table

Table 1. Orderable Part Numbers

| Orderable Part<br>Number | Maximum Clock<br>Frequency | Package Type    | Operating<br>Temperature Range | Part Status |

|--------------------------|----------------------------|-----------------|--------------------------------|-------------|

| SCF5249LPV120            | 120 MHz                    | 144 pin QFP     | -20°C to 70°C                  | Leaded      |

| SCF5249LAG120            | 120 MHz                    | 144 pin QFP     | -20°C to 70°C                  | Lead Free   |

| SCF5249VF140             | 140 MHz                    | 160 ball MAPBGA | -20°C to 70°C                  | Leaded      |

| SCF5249VM140             | 140 MHz                    | 160 ball MAPBGA | -20°C to 70°C                  | Lead Free   |

#### 1.2 SCF5249 Features

The SCF5249 integrated microprocessor combines a Version 2 ColdFire<sup>®</sup> processor core operating at 140MHz with the following modules.

- DMA controller with 4 DMA channels

- Integrated Enhanced Multiply-accumulate Unit (EMAC)

- 8-KByte Direct Mapped Instruction Cache

- 96-KByte SRAM (A 64K and a 32K bank)

- Operates from external crystal oscillator

- Supports 16-bit wide SDRAM memories

- Serial Audio Interface which supports IIS and EIAJ audio protocols

- Digital audio transmitter and two receivers compliant with IEC958 audio protocol

- CD-ROM and CD-ROM XA block decoding and encoding function

- Two UARTS

- Queued Serial Peripheral Interface (QSPI) (Master Only)

- Two timers

- IDE and SmartMedia interfaces

- Analog/Digital Converter

- Flash Memory Card Interface

- Two I<sup>2</sup>C modules

- System debug support

- General Purpose I/O pins shared with other functions

- 1.8V core, 3.3V I/O

- 160 pin MAPBGA package (qualified at 140 MHz) and 144 pin QFP package (qualified at 120 MHz)

- $-20^{0}$  C to  $70^{0}$  C ambient operating temperature range

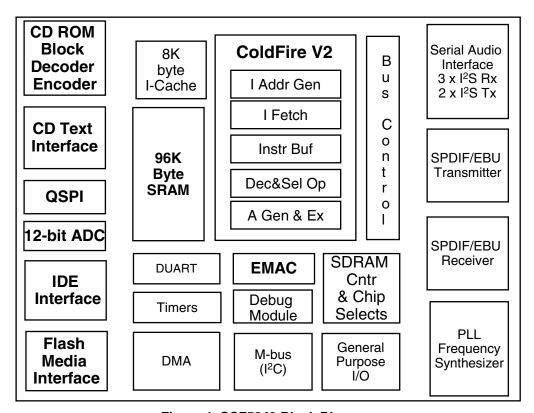

## 2 SCF5249 Block Diagram

Figure 1. SCF5249 Block Diagram

#### 3 SCF5249 Feature Details

The primary features of the SCF5249 integrated processor include the following:

- ColdFire V2 Processor Core operating at 140MHz

- Clock-doubled Version 2 microprocessor core

- 32-bit internal data bus, 16 bit external data bus

- 16 user-visible, 32-bit general-purpose registers

- Supervisor/user modes for system protection

- Vector base register to relocate exception-vector table

- Optimized for high-level language constructs

#### **SCF5249 Feature Details**

- DMA controller

- Four fully programmable channels: Two dedicated to the audio interface module and two dedicated to the UART module (External requests are not supported.)

- Supports dual- and single-address transfers with 32-bit data capability

- Two address pointers that can increment or remain constant

- 16-/24-bit transfer counter

- Operand packing and unpacking support

- Auto-alignment transfers supported for efficient block movement

- Supports bursting and cycle stealing

- All channels support memory to memory transfers

- Interrupt capability

- Provides two clock cycle internal access

- Enhanced Multiply-accumulator Unit

- Single-cycle multiply-accumulate operations for 32 x 32 bit and 16 x 16 bit operands

- Support for signed, unsigned, integer, and fixed-point fractional input operands

- Four 48-bit accumulators to allow the use of a 40-bit product

- The addition of 8 extension bits to increase the dynamic number range

- Fast signed and unsigned integer multiplies

- 8-KByte Direct Mapped instruction cache

- Clock-doubled to match microprocessor core speed

- Flush capability

- Non-blocking cache provides fast access to critical code and data

- 96-KByte SRAM

- Provides one-cycle access to critical code and data

- Split into two banks, SRAM0 (32K), and SRAM1 (64K)

- DMA requests to/from internal SRAM1 supported

- Crystal Trim

- The XTRIM output can be used to trim an external crystal oscillator circuit which would allow lock with an incoming IEC958 or serial audio signal

- Audio Interfaces

- IEC958 input and output

- Four serial Philips IIS/Sony EIAJ interfaces

- One with input and output, one with output only, two with input only (Three inputs, two outputs)

- Master and Slave operation

- CD Text Interface

- Allows the interface of CD subcode (transmitter only)

- Dual Universal Synchronous/asynchronous Receiver/Transmitter (Dual UART)

- Full duplex operation

- Baud-rate generator

- Modem control signals: clear-to-send (CTS) and request-to-send (RTS)

- DMA interrupt capability

- Processor-interrupt capability

- Queued Serial Peripheral Interface (QSPI)

- Programmable queue to support up to 16 transfers without user intervention

- Supports transfer sizes of 8 to 16 bits in 1-bit increments

- Four peripheral chip-select lines for control of up to 15 devices

- Baud rates from 273 Kbps to 17.5 Mbps at 140MHz

- Programmable delays before and after transfers

- Programmable clock phase and polarity

- Supports wraparound mode for continuous transfers

- Master mode only

- Dual 16-bit General-purpose Multimode Timers

- Clock source selectable from external, CPU clock/2 and CPU clock/32.

- 8-bit programmable prescaler

- 2 timer inputs and 2 outputs

- Processor-interrupt capability

- 14.3 nS resolution with CPU clock at 140MHz

- IDE/ SmartMedia Interface

- Allows direct connection to an IDE hard drive or other IDE peripheral

- Analog/Digital Converter

- 12-Bit Resolution

- 4 Muxed inputs

- Flash Memory Card Interface

- Allows connection to Sony MemoryStick compatible devices

- Support SD cards and other types of flash media

- Dual I<sup>2</sup>C Interfaces

- Interchip bus interface for EEPROMs, LCD controllers, A/D converters, keypads

- Master and slave modes, support for multiple masters

- Automatic interrupt generation with programmable level

#### 160 MAPBGA Ball Assignments

- System debug support

- Real-time instruction trace for determining dynamic execution path

- Background debug mode (BDM) for debug features while halted

- Debug exception processing capability

- Real-time debug support

- System Interface

- Glueless bus interface with four chip selects and DRAMC support for interface to 16-bit for DRAM, SRAM, ROM, FLASH, and I/O devices

- Two programmable chip-select signals for static memories or peripherals, with programmable wait states and port sizes.

- Two dedicated chip selects for 16-bit wide DRAM /SDRAM.

- CS0 is active after reset to provide boot-up from external FLASH/ROM.

- Programmable interrupt controller

- Low interrupt latency

- Eight external interrupt requests

- Programmable autovector generator

- 44 programmable general-purpose inputs\*

- 46 programmable general-purpose outputs\*

- \* For the 160 MAPBGA package

- IEEE 1149.1 Test (JTAG) Module

- Clocking

- Clock-multiplied PLL, programmable frequency

- 1.8V Core, 3.3V I/O

- 160 pin MAPBGA package (qualified at 140 MHz) and 144 pin QFP package (qualified at 120 MHz)

## 4 160 MAPBGA Ball Assignments

The following signals are not available on the 144 QFP package.

#### NOTE

The 144 QFP part is qualified for 120 MHz operation. The 160MAPBGA part is qualified for 140 MHz.

| 160 MAPBGA<br>Ball Number | Function        | GPIO    |

|---------------------------|-----------------|---------|

| E3                        | cmd_sdio2       | gpio34  |

| G4                        | sdata0_sdio1    | gpio54  |

| H3                        | RSTO/sdata2_bs2 |         |

| K3                        | A25             | gpo8    |

| L4                        | QSPI_CS1        | gpio24  |

| L8                        | QSPI_CS3        | gpio22  |

| N8                        | SDRAM_CS2       | gpio7   |

| P9                        | EbuOut2         | gpo 37  |

| K11                       | BUFENb2         | gpio17  |

| G12                       | subr            | gpio 53 |

| F13                       | sfsy            | gpio 52 |

| F12                       | rck             | gpio 51 |

| E8                        | SRE             | gpio11  |

| B8                        | Irck3           | gpio 45 |

| E7                        | SWE             | gpio12  |

| A7                        | sclk3           | gpio 49 |

Table 2. 160 MAPBGA Ball Assignments

## 5 SCF5249 Functional Overview

#### 5.1 ColdFire V2 Core

The ColdFire processor Version 2 core consists of two independent, decoupled pipeline structures to maximize performance while minimizing core size. The instruction fetch pipeline (IFP) is a two-stage pipeline for prefetching instructions. The prefetched instruction stream is then gated into the two-stage operand execution pipeline (OEP), which decodes the instruction, fetches the required operands, and then executes the required function. Because the IFP and OEP pipelines are decoupled by an instruction buffer that serves as a FIFO queue, the IFP can prefetch instructions in advance of their actual use by the OEP, which minimizes time stalled waiting for instructions. The OEP is implemented in a two-stage pipeline featuring a traditional RISC data path with a dual-read-ported register file feeding an arithmetic/logic unit (ALU).

#### 5.2 DMA Controller

The SCF5249 provides four fully programmable DMA channels for quick data transfer. Single and dual address mode is supported with the ability to program bursting and cycle stealing. Data transfer is selectable as 8, 16, 32, or 128-bits. Packing and unpacking is supported.

SCF5249 Integrated ColdFire® Microprocessor Data Sheet, Rev. 3

#### **SCF5249 Functional Overview**

Two internal audio channels and the dual UART can be used with the DMA channels. All channels can perform memory to memory transfers. The DMA controller has a user-selectable, 24- or 16-bit counter and a programmable DMA exception handler.

External requests are not supported.

## 5.3 Enhanced Multiply and Accumulate Module (EMAC)

The integrated EMAC unit provides a common set of DSP operations and enhances the integer multiply instructions in the ColdFire architecture. The EMAC provides functionality in three related areas:

- 1. Faster signed and unsigned integer multiplies

- 2. New multiply-accumulate operations supporting signed and unsigned operands

- 3. New miscellaneous register operations

Multiplies of 16x16 and 32x32 with 48-bit accumulates are supported in addition to a full set of extensions for signed and unsigned integers plus signed, fixed-point fractional input operands. The EMAC has a single-clock issue for 32x32-bit multiplication instructions and implements a four-stage execution pipeline.

#### 5.4 Instruction Cache

The instruction cache improves system performance by providing cached instructions to the execution unit in a single clock. The SCF5249 processor uses a 8K-byte, direct-mapped instruction cache to achieve 125 MIPS at 140 Mhz. The cache is accessed by physical addresses, where each 16-byte line consists of an address tag and a valid bit. The instruction cache also includes a bursting interface for 16-bit and 8-bit port sizes to quickly fill cache lines.

## 5.5 Internal 96-KByte SRAM

The 96-KByte on-chip SRAM is split over two banks, SRAM0 (32k) and SRAM1 (64K). It provides one clock-cycle access for the ColdFire core. This SRAM can store processor stack and critical code or data segments to maximize performance. Memory in the second bank can be accessed under DMA.

#### **5.6 DRAM Controller**

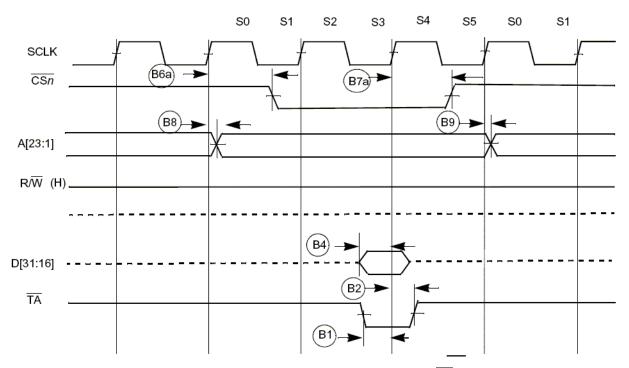

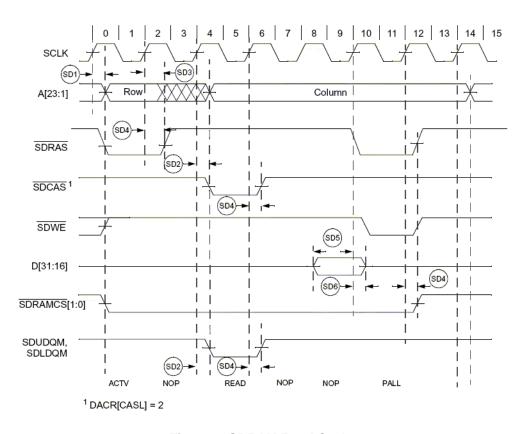

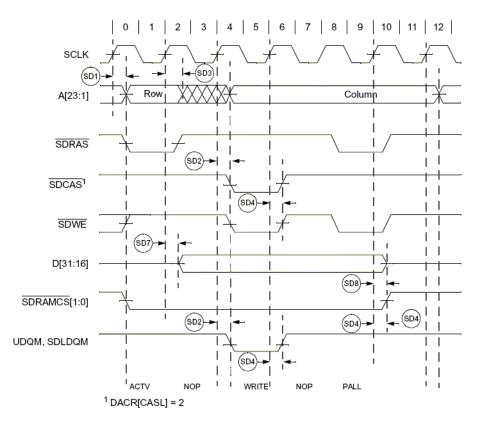

The SCF5249 DRAM controller provides a glueless interface for up to two banks of DRAM, each of which can be up to 32 MBytes. The controller supports a 16-bit data bus. A unique addressing scheme allows for increases in system memory size without rerouting address lines and rewiring boards. The controller operates in page mode, non-page mode, and burst-page mode and supports SDRAMS.

## 5.7 System Interface

The SCF5249 provides a glueless interface to 16-bit port size SRAM, ROM, and peripheral devices with independent programmable control of the assertion and negation of chip-select and write-enable signals.

The SCF5249 also supports bursting ROMs.

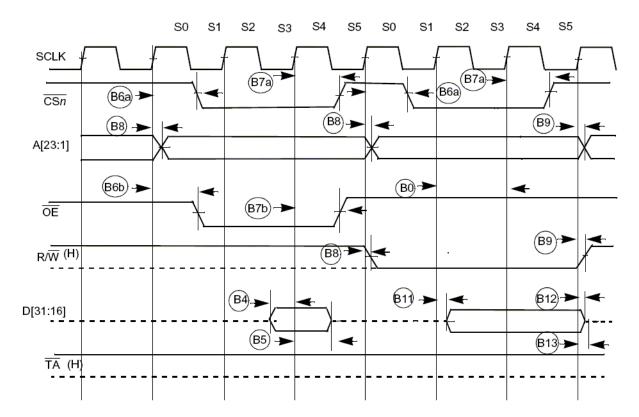

#### 5.8 External Bus Interface

The bus interface controller transfers information between the ColdFire core or DMA and memory, peripherals, or other devices on the external bus. The external bus interface provides 23 bits of address bus space, a 16-bit data bus, Output Enable, and Read/Write signals. This interface implements an extended synchronous protocol that supports bursting operations.

#### 5.9 Serial Audio Interfaces

The SCF5249 digital audio interface provides four serial Philips IIS/Sony EIAJ interfaces. One interface is a 4-pin (1 bit clock, 1 word clock, 1 data in, 1 data out), the other three interfaces are 3-pin (1 bit clock, 1 word clock, 1 data in or out). The serial interfaces have no limit on minimum sampling frequency. Maximum sampling frequency is determined by maximum frequency on bit clock input. This is 1/3 the frequency of the internal system clock.

## 5.10 IEC958 Digital Audio Interfaces

The SCF5249 has two digital audio input interfaces, and one digital audio output interface. There are four digital audio input pins, two digital audio output pins. An internal multiplexer selects one of the four inputs to the digital audio input interface. There is one digital audio output interface but it has two IEC958 outputs. One output carries the professional "c" channel, and the other carries the consumer "c" channel. The rest carry identical data.

The IEC958 output can take the output from the internal IEC958 generator, or multiplex out one of the four IEC958 inputs.

#### 5.11 Audio Bus

The audio interfaces connect to an internal bus that carries all audio data. Each receiver places its received data on the audio bus and each transmitter takes data from the audio bus for transmission. Each transmitter has a source select register.

In addition to the audio interfaces, there are six CPU accessible registers connected to the audio bus. Three of these registers allow data reads from the audio bus and allow selection of the audio source. The other three register provide a write path to the audio bus and can be selected by transmitters as the audio source. Through these registers, the CPU has access to the audio samples for processing.

Audio can be routed from a receiver to a transmitter without the data being processed by the core so the audio bus can be used as a digital audio data switch. The audio bus can also be used for audio format conversion.

#### 5.12 CD-ROM Encoder/Decoder

The SCF5249 is capable of processing CD-ROM sectors in hardware. Processing is compliant with CD-ROM and CD-ROM XA standards.

SCF5249 Integrated ColdFire® Microprocessor Data Sheet, Rev. 3

#### **SCF5249 Functional Overview**

The CD-ROM decoder performs following functions in hardware:

- Sector sync recognition

- Descrambling of sectors

- Verification of the CRC checksum for Mode 1, Mode 2 Form 1, and Mode 2 Form 2 sectors

- Third-layer error correction is not performed

The CD-ROM encoder performs following functions in hardware:

- Sector sync recognition

- Scrambling of sectors

- Insertion of the CRC checksum for Mode 1, Mode 2 Form 1, and Mode 2 Form 2 sectors.

- Third-layer error encoding needs to be done in software. This can use approximately 5-10 Mhz of performance for single-speed.

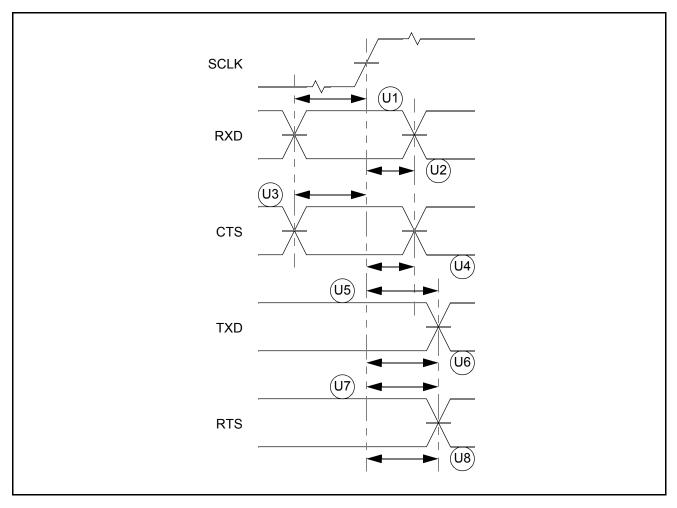

#### 5.13 Dual UART Module

Two full-duplex UARTs with independent receive and transmit buffers are in this module. Data formats can be 5, 6, 7, or 8 bits with even, odd, or no parity, and up to 2 stop bits in 1/16 increments. Four-byte receive buffers and two-byte transmit buffers minimize CPU service calls. The Dual UART module also provides several error-detection and maskable-interrupt capabilities. Modem support includes request-to-send (RTS) and clear-to-send (CTS) lines.

The system clock provides the clocking function from a programmable prescaler. You can select full duplex, auto-echo loopback, local loopback, and remote loopback modes. The programmable Dual UARTs can interrupt the CPU on various normal or error-condition events.

## 5.14 Queued Serial Peripheral Interface QSPI

The QSPI module provides a serial peripheral interface with queued transfer capability. It supports up to 16 stacked transfers at a time, making CPU intervention between transfers unnecessary. Transfers of up to 37 Mbits/second are possible at a CPU clock of 140 MHz. The QSPI supports master mode operation only.

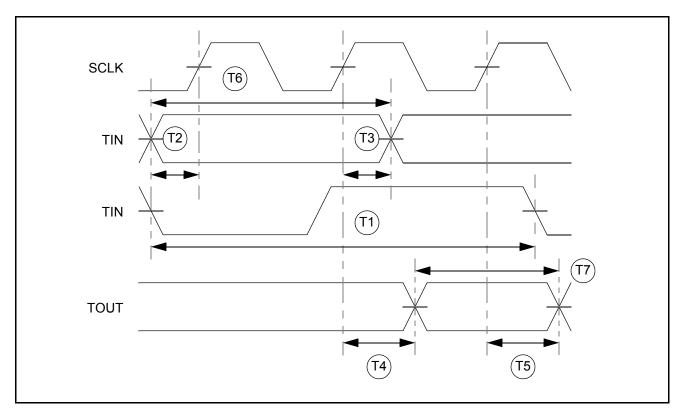

#### 5.15 Timer Module

The timer module includes two general-purpose timers, each of which contains a free-running 16-bit timer for use in any of three modes:

- 1. Timer Capture. This mode captures the timer value with an external event.

- 2. Output Capture. This mode triggers an external signal or interrupts the CPU when the timer reaches a set value

- 3. Event Counter. This mode counts external events.

The timer unit has an 8-bit prescaler that allows programming of the clock input frequency, which is derived from the system clock. In addition to the  $\div 1$  and  $\div 16$  clock derived from the bus clock (CPU clock / 2), the programmable timer-output pins either generate an active-low pulse or toggle the outputs.

#### 5.16 IDE and SmartMedia Interfaces

The SCF5249 system bus allows connection of an IDE hard disk drive and SmartMedia flash card with a minimum of external hardware. The external hardware consists of bus buffers for address and data and are intended to reduce the load on the bus and prevent SDRAM and Flash accesses to propagate to the IDE bus. The control signals for the buffers are generated in the SCF5249.

## 5.17 Analog/Digital Converter (ADC)

The four channel ADC is a based on the Sigma-Delta concept with 12-bit resolution. The digital portion of the ADC is provided internally. The analog voltage comparator must be provided externally as well as an external integrator circuit (resistor/capacitor) which is driven by the ADC output. A software interrupt is provided when the ADC measurement cycle is complete.

## 5.18 Flash Memory Card Interface

The interface is Sony MemoryStick and SecureDigital compatible. However, there is no hardware support for MagicGate.

## 5.19 I<sup>2</sup>C Module

The two-wire I<sup>2</sup>C bus interface, which is compliant with the Philips I<sup>2</sup>C bus standard, is a bidirectional serial bus that exchanges data between devices. The I<sup>2</sup>C bus minimizes the interconnection between devices in the end system and is best suited for applications that need occasional bursts of rapid communication over short distances among several devices. Bus capacitance and the number of unique addresses limit the maximum communication length and the number of devices that can be connected.

## 5.20 Chip-Selects

Two programmable chip-select outputs provide signals that enable glueless connection to external memory and peripheral circuits. The base address, access permissions and automatic wait-state insertion are programmable with configuration registers. These signals also interface to 16-bit ports.

CS0 is active after reset to provide boot-up from external FLASH/ROM.

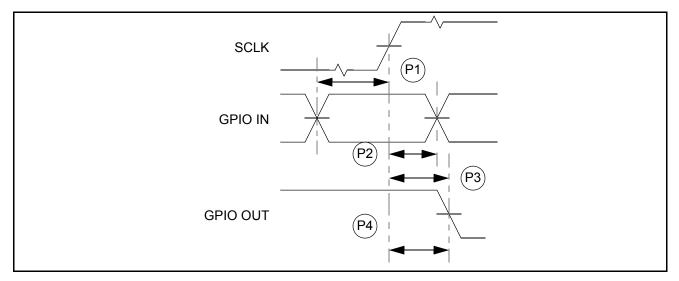

#### 5.21 GPIO Interface

A total of 44 General Purpose inputs and 46 General Purpose outputs are available. These are multiplexed with various other signals. Eight of the GPIO inputs have edge sensitive interrupt capability.

## **5.22 Interrupt Controller**

The interrupt controller provides user-programmable control of a total of 57 interrupts. There are 49 internal interrupt sources. In addition, there are 8 GPIOs where interrupts can be generated on the rising or falling edge of the pin. All interrupts are autovectored and interrupt levels are programmable.

SCF5249 Integrated ColdFire® Microprocessor Data Sheet, Rev. 3

#### **General Device Information**

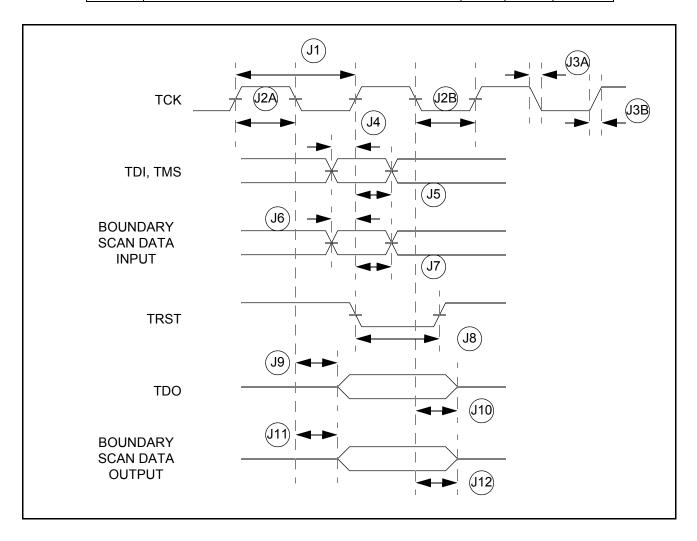

#### **5.23 JTAG**

To help with system diagnostics and manufacturing testing, the SCF5249 includes dedicated user-accessible test logic that complies with the IEEE 1149.1A standard for boundary scan testability, often referred to as Joint Test Action Group, or JTAG. For more information, refer to the IEEE 1149.1A standard. Freescale provides BSDL files for JTAG testing.

## 5.24 System Debug Interface

The ColdFire processor core debug interface supports real-time instruction trace and debug, plus background-debug mode. A background-debug mode (BDM) interface provides system debug.

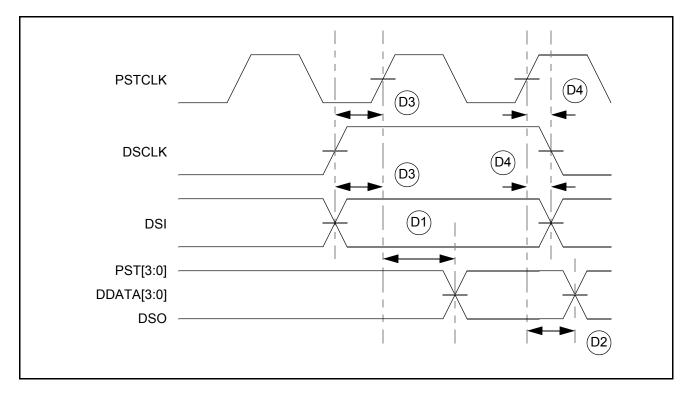

In real-time instruction trace, four status lines provide information on processor activity in real time (PST pins). A four-bit wide debug data bus (DDATA) displays operand data and change-of-flow addresses, which helps track the machine's dynamic execution path.

## 5.25 Crystal and On-chip PLL

Typically, an external 16.92 Mhz or 33.86 Mhz clock input is used for CD R/W applications, while an 11.2896 MHz clock is more practical for Portable CD player applications. However, the on-chip programmable PLL, which generates the processor clock, allows the use of almost any low frequency external clock (5-35 Mhz).

Two clock outputs (MCLK1 and MCLK2) are provided for use as Audio Master Clock. The output frequencies of both outputs are programmable to Fxtal, Fxtal/2, Fxtal/3, and Fxtal/4. The Fxtal/3 option is only available when the 33.86 Mhz crystal is connected.

The SCF5249 supports VCO operation of the oscillator by means of a 16-bit pulse density modulation output. Using this mode, it is possible to lock the oscillator to the frequency of an incoming IEC958 or IIS signal. The maximum trim depends on the type and design of the oscillator. Typically a trim of  $\pm$ 100 ppm can be achieved with a crystal oscillator and over  $\pm$ 1000 ppm with an LC oscillator.

#### 6 General Device Information

The SCF5249 is available in a 160-pin MAP BGA package, or a 144-pin QFP package.

#### 7 Documentation

Table 3 lists the documents that provide a complete description of the SCF5249 and are required to design properly with the part. Documentation is available from a local Freescale distributor, a Freescale semiconductor sales office, a Freescale Literature Distribution Center, or through the Freescale DSP home page on the internet; http://www.freescale.com/ (the source for the latest information).

**Table 3. SCF5249 Documentation**

| Document Name | Description                                                    | Order Number    |

|---------------|----------------------------------------------------------------|-----------------|

| CFPRM/D       | ColdFire Family Programmer's Reference Manual                  | CFPRM/D         |

| ColdFire2UM   | Version 2/2M ColdFire Core<br>Processor User's Manual          | ColdFire2UM/D   |

| ColdFire2UMAD | Version 2/2M ColdFire Core<br>Processor User's Manual Addendum | ColdFire2UMAD/D |

| SCF5249UM     | SCF5249 User's Manual                                          | SCF5249UM/D     |

## 8.1 Introduction

This section describes the SCF5249 input and output signals. The signal descriptions as shown in Table 4 are grouped according to relevant functionality.

Table 4. SCF5249 Signal Index

| Signal Name                       | Mnemonic              | Function                                                          | Input/<br>Output | Reset<br>State |

|-----------------------------------|-----------------------|-------------------------------------------------------------------|------------------|----------------|

| Address                           | A[23:1]<br>A[25]/GPO8 | 23 address lines, address line 25 multiplexed with gpo8.          | Out              | Х              |

| Read-write control                | RW_b                  | Bus write enable - indicates if read or write cycle in progress   | Out              | Н              |

| Output enable                     | OE                    | Output enable for asynchronous memories connected to chip selects | Out              | negated        |

| Data                              | D[31:16]              | Data bus used to transfer word data                               | In/Out           | Hi-Z           |

| Synchronous row address strobe    | SDRAS                 | Row address strobe for external SDRAM.                            | Out              | negated        |

| Synchronous column address strobe | SDCAS                 | Column address strobe for external SDRAM                          | Out              | negated        |

| SDRAM write enable                | SDWE                  | Write enable for external SDRAM                                   | Out              | negated        |

| SDRAM upper byte enable           | SDUDQM                | Indicates during write cycle if high byte is written              | Out              |                |

| SDRAM lower byte enable           | SDLDQM                | Indicates during write cycle if low byte is written               | Out              |                |

| SDRAM chip selects                | SDRAMCS1              | SDRAM chip select                                                 | Outt             | negated        |

| SDRAM chip selects                | SDRAMCS2/GPIO7        | SDRAM chip select                                                 | In/Out           | negated        |

| SDRAM clock enable                | BCLKE                 | SDRAM clock enable                                                | Out              |                |

| System clock                      | SCLK/GPIO10           | SDRAM clock output                                                | In/Out           |                |

Table 4. SCF5249 Signal Index (continued)

| Signal Name           | Mnemonic                              | Function                                                                                           | Input/<br>Output | Reset<br>State |

|-----------------------|---------------------------------------|----------------------------------------------------------------------------------------------------|------------------|----------------|

| ISA bus read strobes  | CS2/IDE-DIOR/GPIO13<br>CS3/SRE/GPIO11 | There are 2 ISA bus read strobes and 2 ISA bus write strobes. They allow                           | In/Out           |                |

| ISA bus write strobes | IDE-DIOW/GPIO14<br>SWE/GPIO12         | connection of two independent ISA bus peripherals, e.g. an IDE slave device and a SmartMedia card. | In/Out           |                |

| ISA bus wait signal   | IDE-IORDY/GPIO16                      | ISA bus wait line - available for both busses                                                      | In/Out           |                |

| Chip Selects[1:0]     | CS0<br>CS1/GPIO58                     | Enables peripherals at programmed addresses.  CS[1:0]. CS[0]provides boot ROM selection            | Out<br>In/Out    | negated        |

| Buffer enable 1       | BUFENB1/GPIO57                        | Two programmable buffer enables                                                                    | In/Out           |                |

| Buffer enable 2       | BUFENB2/GPIO7                         | allow seamless steering of external buffers to split data and address bus in sections.             | In/Out           |                |

| Transfer acknowledge  | TA/GPIO20                             | Transfer Acknowledge signal                                                                        | In/Out           |                |

| Serial Clock Line     | SCL0/QSPI_CLK                         | Clock signal for first I <sup>2</sup> C module operation<br>Signal is also QSPI clock              | In/Out           |                |

| Serial Data Line      | SDA0/QSPI_DIN                         | Serial data port first I <sup>2</sup> C module operation Signal is also QSPI data in               | In/Out           |                |

| Serial Clock Line     | SCL1_GPIO_3                           | Clock signal for second I2C module operation                                                       | In/Out           |                |

| Serial Data Line      | SDA1_GPIO55                           | Serial data port for second I2C module operation                                                   | In/Out           |                |

| Receive Data          | RXD1/GPI28/ADIN2<br>RXD0/GPI27        | Signal is receive serial data input for DUART                                                      | In               |                |

| Transmit Data         | TXD1/GPO28<br>TXD0/GPO27              | Signal is transmit serial data output for DUART                                                    | Out              | asserted       |

| Request-To-Send       | RTS1/GPO31<br>RTS2/GPO30              | DUART signals a ready to receive data query                                                        | Out              | negated        |

| Clear-To-Send         | CTS1/ADIN3/GPI31<br>CTS0/GPI30        | Signals to DUART that data can be transmitted to peripheral CTS2 is multiplexed with an A/D input  | ln               |                |

| Timer Input           | TIN0/GPI33<br>TIN1/GPIO23             | Provides clock input to timer or provides trigger to timer value capture logic                     | In<br>In/Out     |                |

| Timer Output          | TOUT0/GPO33<br>TOUT1/ADOUT/GPO35      | Capable of output waveform or pulse generation                                                     | Out              |                |

Table 4. SCF5249 Signal Index (continued)

| Signal Name                          | Mnemonic                                                                 | Function                                                                                 | Input/<br>Output | Reset<br>State |

|--------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|----------------|

| IEC958 inputs                        | EBUIN1/GPI36<br>EBUIN2/GPI37<br>EBUIN3/ADIN0/GPI38<br>EBUIN4/ADIN1/GPI39 | Audio interfaces IEC958 inputs multiplexed with some A/D inputs                          | In               |                |

| IEC958 outputs                       | EBUOUT1/GPO36<br>EBUOUT2/GPO37                                           | Audio interfaces IEC958 outputs                                                          | Out              |                |

| Serial data in                       | SDATAI1<br>SDATAI3/GPI41<br>SDATA14/GPI42                                | Audio interfaces serial data inputs                                                      | In               |                |

| Serial data out                      | SDATAO1/GPIO25<br>SDATAO2/GPO41                                          | Audio interfaces serial data outputs                                                     | In/Out<br>Out    |                |

| Word clock                           | LRCK1<br>LRCK2/GPIO44<br>LRCK3/GPIO45<br>LRCK4/GPIO46                    | Audio interfaces serial word clocks                                                      | In/Out           |                |

| Bit clock                            | SCLK1<br>SCLK2/GPIO48<br>SCLK3/GPIO49<br>SCLK4/GPIO50                    | Audio interfaces serial bit clocks                                                       | In/Out           |                |

| Serial input                         | EF/GPIO19                                                                | Error flag serial in                                                                     | In/Out           |                |

| Serial input                         | CFLG/GPIO18                                                              | C-flag serial in                                                                         | In/Out           |                |

| Subcode clock                        | RCK/GPIO51                                                               | Audio interfaces subcode clock                                                           | In/Out           |                |

| Subcode sync                         | SFSY/GPIO52                                                              | Aaudio interfaces subcode sync                                                           | In/Out           |                |

| Subcode data                         | SUBR/GPIO53                                                              | Audio interfaces subcode data                                                            | In/Out           |                |

| Clock frequency trim                 | XTRIM/GPO38                                                              | Clock trim control                                                                       | Out              |                |

| Audio clocks out                     | MCLK1/GPIO39<br>MCLK2/GPIO42                                             | DAC output clocks                                                                        | Out              |                |

| MemoryStick/SecureDigit al interface | CMDSDIO2/GPIO34                                                          | Secure Digital command lane<br>MemoryStick interface 2 data i/o                          | In/Out           |                |

|                                      | SCLKOUT/GPIO15                                                           | Clock out for both MemoryStick interfaces and for Secure Digital                         | In/Out           |                |

|                                      | SDATA0_SDIO1/GPIO54                                                      | SecureDigital serial data bit 0<br>MemoryStick interface 1 data i/o                      | In/Out           |                |

|                                      | SDATA1_BS1/GPIO9                                                         | SecureDigital serial data bit 1<br>MemoryStick interface 1 strobe                        | In/Out           |                |

|                                      | RSTO/SDATA2_BS2                                                          | SecureDigital serial data bit 2<br>MemoryStick interface 2 strobe<br>Reset output signal | In/Out           |                |

|                                      | SDATA3/GPIO56                                                            | SecureDigital serial data bit 3                                                          | In/Out           |                |

Table 4. SCF5249 Signal Index (continued)

| Signal Name                                      | Mnemonic                                                                         | Function                                                                                           | Input/<br>Output | Reset<br>State |

|--------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------|----------------|

| ADC                                              | EBUIN3/ADIN0/GPI38<br>EBUIN4/ADIN1/GPI39<br>RXD2/ADIN2/GPI28<br>CTS2/ADIN3/GPI31 | Analog to Digital converter input signals                                                          | In/Out           |                |

| ADC                                              | TOUT1/ADOUT/GPO35                                                                | Analog to digital convertor output signal.                                                         | In/Out           |                |

| QSPI clock                                       | SCL/QSPI_CLK                                                                     | QSPI clock signal                                                                                  | In/Out           |                |

| QSPI data in                                     | SDA/QSPI_DIN                                                                     | QSPI data input                                                                                    | In/Out           |                |

| QSPI data out                                    | QSPIDOUT/GPIO26                                                                  | QSPI data out                                                                                      | In/Out           |                |

| QSPI chip selects                                | QSPICS0/GPIO29<br>QSPICS1/GPIO24<br>QSPICS2/GPIO21<br>QSPICS3/GPIO22             | QSPI chip selects                                                                                  | In/Out           |                |

| Crystal in                                       | CRIN                                                                             | Crystal input                                                                                      | In               |                |

| Reset In                                         | RSTI                                                                             | Processor Reset Input                                                                              | In               |                |

| Freescale Test Mode                              | TEST[3:0]                                                                        | Should always be low.                                                                              | In               |                |

| High Impedance                                   | HIZ                                                                              | Assertion three-states all output signal pins.                                                     | In               |                |

| Debug Data                                       | DDATA3/GPIO4<br>DDATA2/GPIO2<br>DDATA1/GPIO1<br>DDATA0/GPIO0                     | Displays captured processor data and break-point status.                                           | In/Out           | Hi-Z           |

| Processor Status                                 | PST3/GPIO62<br>PST2/GPIO61<br>PST1/GPIO60<br>PST0/GPIO59                         | Indicates internal processor status.                                                               | In/Out           | Hi-Z           |

| Processor clock                                  | PSTCLK/GPO63                                                                     | Processor clock output                                                                             | Out              |                |

| Test Clock                                       | TCK                                                                              | Clock signal for IEEE 1149.1A JTAG.                                                                | In               |                |

| Test Reset/Development<br>Serial Clock           | TRST/DSCLK                                                                       | Multiplexed signal that is asynchronous reset for JTAG controller. Clock input for debug module.   | In               |                |

| Test Mode Select/ Break<br>Point                 | TMS/BKPT                                                                         | Multiplexed signal that is test mode select in JTAG mode and a hardware break-point in debug mode. | In               |                |

| Test Data Input /<br>Development Serial Input    | TDI/DSI                                                                          | Multiplexed serial input for the JTAG or background debug module.                                  | In               |                |

| Test Data<br>Output/Development<br>Serial Output | TDO/DSO                                                                          | Multiplexed serial output for the JTAG or background debug module.                                 | Out              |                |

**Note:** The CMD\_SDIO2, SDATA0\_SDIO1, RSTO/SDATA2\_BS2, A25, QSPI\_CS1, QSPI\_CS3, SDRAM\_CS2, EBUOUT2, BUFENB2, SUBR, SFSY, RCK, SRE, LRCK3, SWE, and the SCLK3 signals are only used in the 160 MAPBGA package.

17

#### **8.2 GPIO**

Many pins have a GPIO as first or second function. If GPIO is second function, following rules apply:

- General purpose input is always active, regardless of state of pin.

- General purpose output or primary output is determined by value written to GPIO function select register.

- Power-on reset function is not GPIO.

## 8.3 SCF5249 Bus Signals

These signals provide the external bus interface to the SCF5249.

#### 8.3.1 Address Bus

- The address bus provides the address of the byte or most significant byte of the word or longword being transferred. The address lines also serve as the DRAM address pins, providing multiplexed row and column address signals.

- Bits 23 down to 1 and 25 of the address are available. A25 is intended to be used with 256 Mbit DRAM's. Signals are named:

- A[23:1]

- A[25]/GPO8

#### 8.3.2 Read-Write Control

This signal indicates during any bus cycle whether a read or write is in progress. A low is write cycle and a high is a read cycle.

#### 8.3.3 Output Enable

The  $\overline{OE}$  signal is intended to be connected to the output enable of asynchronous memories connected to chip selects. During bus read cycles, the ColdFire processor will drive  $\overline{OE}$  low.

#### 8.3.4 Data Bus

The data bus (D[31:16]) is bi-directional and non-multiplexed. Data is registered by the SCF5249 on the rising clock edge. The port width for each chip-select and DRAM bank are programmable. The data bus uses a default configuration if none of the chip-selects or DRAM bank match the address decode. All 16 bits of the data bus are driven during writes, regardless of port width or operand size.

#### 8.3.5 Transfer Acknowledge

The TA/GPIO20 pin is the transfer acknowledge signal.

## 8.4 SDRAM Controller Signals

The following SDRAM signals provide a seamless interface to external SDRAM. An SDRAM width of 16 bits is supported and can access as much as 64 Mybtes of memory. ADRAMs are not supported.

**SDRAM Signal Description** The SDRAS active low pin provides a seamless interface to the RAS Synchronous DRAM row address strobe input on synchronous DRAM Synchronous DRAM Column Address The SDCAS active low pin provides a seamless interface to CAS input Strobe on synchronous DRAM. Synchronous DRAM Write The SDWE active-low pin is asserted to signify that a SDRAM write cycle is underway. This pin outputs logic '1' during read bus cycles. The SD\_CS1 and The SDRAM\_CS2/GPIO7 active-low output signal is Synchronous DRAM Chip Enable used during synchronous mode to route directly to the chip select of up to two SDRAM devices. The SDRAM\_CS2/gpio7 can be programmed to be gpio using the GPIO-FUNCTION register. Synchronous DRAM UDQM and LQDM The DRAM byte enables UDMQ and LDQM are driven by the SDUDQM and SDLDQM byte enable outputs. signals Synchronous DRAM clock The DRAM clock is driven by the SCLK signal Synchronous DRAM Clock Enable The BCLKE active high output signal is used during synchronous mode to route directly to the SCKE signal of external SDRAMs. This signal provides the clock enable to the SDRAM.

**Table 5. SDRAM Controller Signals**

#### **NOTE**

The SDRAM CS2 signal is only used on the 160 MAPBGA package.

#### 8.5 Chip Selects

There are two chip select outputs on the SCF5249 device.  $\overline{CS0}$  and  $\overline{CS1}/GPIO58$ . The second signal is multiplexed with a GPIO signal. The active low chip selects can be used to access asynchronous memories. The interface is glueless.

#### 8.6 ISA Bus

The SCF5249 supports an ISA bus. (No ISA DMA channel). Using the ISA bus protocol, reads and writes to up to two ISA bus peripherals are possible. For the first peripheral, CS2/IDE-DIOR/GPIO13 and IDE-DIOW/GPIO14 are the read and write strobe. For the second peripheral, CS3/SRE/GPIO11 and SWE/GPIO12 are the read and write strobe. Either peripheral can insert wait states by pulling IDE-IORDY/GPIO16

## 8.7 Bus Buffer Signals

As the SCF5249 has a quite complicated slave bus, with the possibility to put DRAM on the bus, put asynchronous memories on the bus, and to put ISA bus peripherals on the bus, it may become necessary to introduce a bus buffer on the bus. The SCF5249 has a glueless interface to steer these bus buffers with 2 bus buffer output signals BUFENB1/GPIO57 and BUFENB2/GPIO7.

#### NOTE

The BUFENB2 signal is only used in the 160 MAPBGA package.

## 8.8 I<sup>2</sup>C Module Signals

There are two I<sup>2</sup>C interfaces on this device.

The I<sup>2</sup>C module acts as a quick two-wire, bidirectional serial interface between the SCF5249 processor and peripherals with an I<sup>2</sup>C interface (e.g., LED controller, A-to-D converter, D-to-A converter). When devices connected to the I<sup>2</sup>C bus drive the bus, they will either drive logic-0 or high-impedance. This can be accomplished with an open-drain output.

| l <sup>2</sup> c Module Signal | Description                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

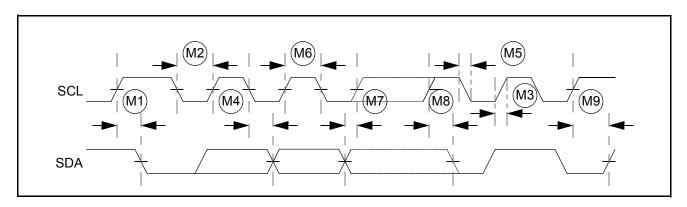

| I <sup>2</sup> C Serial Clock  | The SCL/QPSICLK and SCL2/GPIO3 bidirectional signals are the clock signal for first and second I <sup>2</sup> C module operation. The I <sup>2</sup> C module controls this signal when the bus is in master mode; all I <sup>2</sup> C devices drive this signal to synchronize I <sup>2</sup> C timing.  Signals are multiplexed Function select is done via PLLCR register. |

| I <sup>2</sup> C Serial Data   | The SDA/QSPI_DIN and SDA2/GPIO55 bidirectional signals are the data input/output for the first and second serial I <sup>2</sup> C interface.  Signals are multiplexed Function select is done via PLLCR register.                                                                                                                                                              |

Table 6. I<sup>2</sup>C Module Signals

## 8.9 Serial Module Signals

The following signals transfer serial data between the two UART modules and external peripherals.

All serial module signals can be used as gpi or gpo. The GPIO-FUNCTION and GPIO1-FUNCTION registers must be programmed to determine pin functions of the inputs and outputs. If used as gpo or gpi, UART functionality is lost.

**Table 7. Serial Module Signals**

| Serial Module Signal | Description                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Data         | The RXD1_GPI27 and RXD2/ADIN2/GPI28 are the inputs on which serial data is received by the DUART. Data is sampled on RxD[1:0] on the rising edge of the serial clock source, with the least significant bit received first.                                                                                                                                         |

| Transmit Data        | The DUART transmits serial data on the TXD1/GPO27 and TXD2/GPO28 output signals. Data is transmitted on the falling edge of the serial clock source, with the least significant bit transmitted (LSB) first. When no data is being transmitted or the transmitter is disabled, these two signals are held high. TxD[1:0] are also held high in local loopback mode. |

| Request To Send      | The RTS1/GPO30 and RTS2/GPO31 request-to-send outputs indicate to the peripheral device that the DUART is ready to send data and requires a clear-to-send signal to initiate transfer.                                                                                                                                                                              |

| Clear To Send        | Peripherals drive the CTS1/GPI30 and CTS2/ADIN3/GPI31 inputs to indicate to the SCF5249 serial module that it can begin data transmission.                                                                                                                                                                                                                          |

## 8.10 Timer Module Signals

The following signals are external interface to the two general-purpose SCF5249 timers. These 16-bit timers can capture timer values, trigger external events, or internal interrupts, or count external events. These pins can be reused as GPO or GPI. Registers GPIO-FUNCTION and GPIO1-FUNCTION must be programmed for this.

**Table 8. Timer Module Signals**

| Serial Module Signal | Description                                                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | Users can program the TIN0/GPI33 and TIN1/GPIO23 inputs as clocks that cause events in the counter and prescalars. They can also cause capture on the rising edge, falling edge, or both edges. |

| Timer Output         | The TOUT0/GPO33 and TOUT1/ADOUT/GPO35 programmable outputs pulse or toggle on various timer events.                                                                                             |

## 8.11 Serial Audio Interface Signals

All serial audio interface signals can be programmed to serve as general purpose I/Os or as serial audio interface signals. The function is programmed using GPIO-FUNCTION and GPIO1-FUNCTION registers.

#### NOTE

The LRCK3 and SCLK3 signals are only used in the 160 MAPBGA package..

**Table 9. Serial Audio Interface Signals**

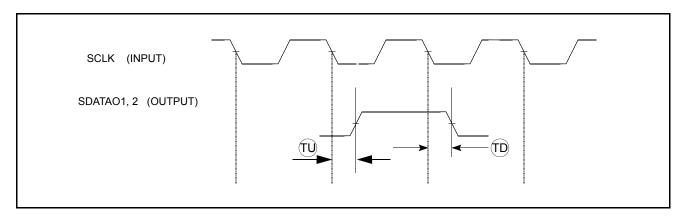

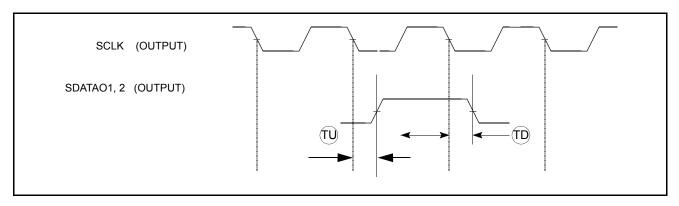

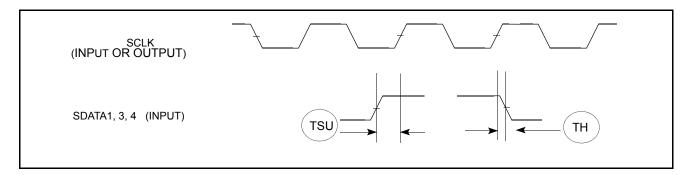

| Serial Module Signal    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Audio Bit Clock  | The SCLK1, SCLK2/GPIO48 and SCLK3/GPIO49, and SCLK4/GPIO50 multiplexed pins can serve as general purpose I/Os or serial audio bit clocks. As bit clocks, these bidirectional pins can be programmed as outputs to drive their associated serial audio (IIS) bit clocks. Alternately, these pins can be programmed as inputs when the serial audio bit clocks are driven internally. The functionality is programmed within the Audio module. During reset, these pins are configured as input serial audio bit clocks. |

| Serial Audio Word Clock | The LRCK1, LRCK2/GPIO44, LRCK3/GPIO45, and LRCK/GPIO46 multiplexed pins can serve as general purpose I/Os or serial audio word clocks. As word clocks, the bidirectional pins can be programmed as inputs to drive their associated serial audio word clock. Alternately, these pins can be programmed as outputs when the serial audio word clocks are derived internally. The functionality is programmed within the Audio module. During reset, these pins are configured as input serial audio word clocks.        |

| Serial Audio Data In    | The SDATAI1, SDATAI3/GPIO41, and SDATAI4/GPI42 multiplexed pins can serve as general purpose I/Os or serial audio inputs. As serial audio inputs the data is sent to interfaces 1 and 3 respectively. The functionality of these pins is programmed with the GPIO-FUNCTION and GPIO1-FUNCTION registers. During reset, the pins are configured as serial data inputs.                                                                                                                                                  |

| Serial Audio Data Out   | The SDATAO1/GPIO25 AND SDATAO2/GPI41 multiplexed pins can serve as general purpose I/Os or serial audio outputs. The functionality of these pins is programmed with registers GPIO-FUNCTION and GPIO1-FUNCTION. During reset, the pins are configured as serial data outputs                                                                                                                                                                                                                                           |

| Serial audio error flag | The EF/GPIO19 multiplexed pin can serve as general purpose I/Os or error flag input. As error flag input, this pin will input the error flag delivered by the CD-DSP. EF/GPIO19 is only relevant for serial interface interface 1.                                                                                                                                                                                                                                                                                     |

| Serial audio CFLG       | The CFLG/GPIO18 multiplexed pin can serve as general purpose I/O or CFLG input. As CFLG input, the pin will input the CFLG flag delivered by the CD-DSP. CFLG/GPIO18 is only relevant for serial interface 1.                                                                                                                                                                                                                                                                                                          |

## 8.12 Digital Audio Interface Signals

**Table 10. Digital Audio Interface Signals**

| Serial Module Signal | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Audio In     | The EBUIN1/GPI36, EBUIN2/GPI37, EBUIN3/ADIN0/GPI38, and EBUIN4/ADIN1/GPI39 multiplexed signals can serve as general purpose input or can be driven by various digital audio (IEC958) input sources. Both functionalities are always active. Input chosen for IEC958 receiver is programmed within the audio module. Input value on the 4 pins can always be read from the appropriate gpio register |

| Digital Audio Out    | The EBUOUT1_GPO36 and EBUOUT2_GPO37 multiplexed pins can serve as general purpose I/O or as digital audio (IEC958) output. EBUOUT1 is digital audio out for consumer mode, EBUOUT2 is digital audio out for professional mode. The functionality of the pins is programmed with the GPIO-FUNCTION and GPIO1-FUNCTION register. During reset, the pin is configured as a digital audio output.       |

#### NOTE

The EBUOUT2 signal is only used on the 160 MAPBGA package.

#### 8.13 Subcode Interface

There is a 3-line subcode interface on the SCF5249. This 3-line subcode interface allows the device to format and transmit subcode in EIAJ format to a CD channel encoder device. The three signals are described in Table 11.

Table 11. Subcode Interface Signal

| Signal name | Description                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------|

| RCK/GPIO51  | Subcode clock input. When pin is used as subcode clock, this pin is driven by the CD channel encoder.    |

| SFSY/GPIO52 | Subcode sync output This signal is driven high if a subcode sync needs to be inserted in the EFM stream. |

| SUBR/GPIO53 | Subcode data output This signal is a subcode data out pin.                                               |

#### **NOTE**

The SUBR, SFSY, and the RCK signals are only used in the 160 MAPBGA package.

23

## 8.14 Analog to Digital Converter (ADC)

The single output on the TOUT1/ADOUT/GPO35 pin provides the reference voltage in PDM format therefore this output requires an external integrator circuit (resistor/capacitor) to convert it to a DC level to

be used by the external comparator circuit. Four external comparators compare the DC level obtained after filtering TOUT1/ADOUT/GPO35 with the relevant input signals. The outputs of the comparators are fed to the 4 ADIN inputs on the SCF5249: EBUIN3/ADIN0/GPI38, EBUIN4/ADIN1/GPI39, RXD2/ADIN2/GPI38 and CTS2/ADIN3/GPI31. Selection of function for pin TOUT1/ADOUT/GPO35 is done by writing GPIO function select register (determines if function is GPIO or not), and differentiation between timer and adout functions is done in the ADCONFIG Register.

## 8.15 Secure Digital/ MemoryStick Card Interface

The device has a versatile flash card interface that supports both SecureDigital and MemoryStick cards. The interface can either support one SecureDigital or two MemoryStick cards. No mixing of card types is possible. Table 12 gives the pin descriptions.

| Flash Memory Signal | Description                                                                                                                                                               |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLKOUT/GPIO15      | Clock out for both MemoryStick interfaces and for SecureDigital                                                                                                           |

| CMD_SDIO2/GPIO34    | Secure Digital command line<br>MemoryStick interface 2 data i/o                                                                                                           |

| SDATA0_SDIO1/GPIO54 | SecureDigital serial data bit 0<br>MemoryStick interface 1 data i/o                                                                                                       |

| SDATA1_BS1/GPIO9    | SecureDigital serial data bit 1 MemoryStick interface 1 strobe                                                                                                            |

| RSTO/SDATA2_BS2     | SecureDigital serial data bit 2 MemoryStick interface 2 strobe Reset output signal Selection between Reset function and SDATA2_BS2 is done by programming PLLCR register. |

| SDATA3/GPIO57       | SecureDigital serial data bit 3                                                                                                                                           |

**Table 12. Flash Memory Card Signals**

#### NOTE

The SDATA0\_SDIO1 and RSTO/SDATA2\_BS2 signals are only used in the 160 MAPBGA package.

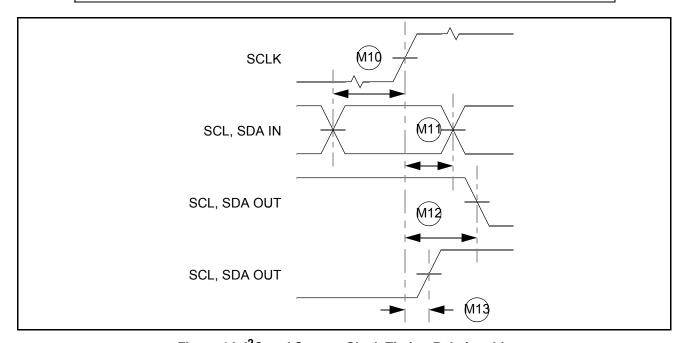

## 8.16 Queued Serial Peripheral Interface (QSPI)

Table 13. Queued Serial Peripheral Interface (QSPI) Signals

| Serial Module Signal | Description                                                                                             |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| SCL_QSPICLK          | Multiplexed signal IIC interface clock or QSPI clock output Function select is done via PLLCR register. |  |  |  |  |

| SDA_QSPIDIN          | Multiplexed signal IIC interface data or QSPI data input. Function select is done via PLLCR register.   |  |  |  |  |

| QSPIDOUT_GPIO26      | QSPI data output                                                                                        |  |  |  |  |

| QSPICS0_GPIO29       | 4 different QSPI chip selects                                                                           |  |  |  |  |

| QSPICS1_GPIO24       |                                                                                                         |  |  |  |  |

| QSPICS2_GPIO21       |                                                                                                         |  |  |  |  |

| QSPICS3_GPIO22       |                                                                                                         |  |  |  |  |

#### NOTE

The QSPI interface is a high-speed serial interface allowing transmit and receive of serial data

## 8.17 Crystal Trim

The XTRIM\_GPIO38 output produces a pulse-density modulated phase/frequency difference signal to be used after low-pass filtering to control varicap-voltage to control crystal oscillation frequency. This will lock the crystal to the incoming digital audio signal.

#### 8.18 Clock Out

The MCLK1/GPO39 and /MCLK2/GPO42 can serve as general purpose I/Os or as DAC clock outputs. When programmed as DAC clock outputs, these signals are directly derived from the crystal.

## 8.19 Debug and Test Signals

These signals interface with external I/O to provide processor status signals.

#### **8.19.1 Test Mode**

The TEST[3:0] inputs are used for various manufacturing and debug tests. For normal mode these inputs should be always be tied low. Use TEST0 to switch between background debug mode and JTAG mode. Drive TEST0 high for debug mode.

#### 8.19.2 High Impedance

The assertion of  $\overline{HI}$  will force all output drivers to a high-impedance state. The timing on  $\overline{HI}$  is independent of the clock.

25

#### **NOTE**

JTAG operation will override the  $\overline{HI}$  Z pin.

#### 8.19.3 Processor Clock Output

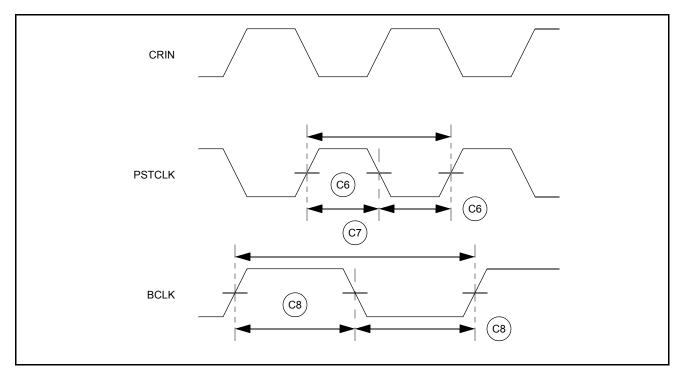

The internal PLL generates this PSTCLK/GPO63 and output signal, and is the processor clock output that is used as the timing reference for the Debug bus timing (DDATA[3:0] and PST[3:0]). The PSTCLK/GPO63 is at the same frequency as the core processor and cache memory. The frequency will be twice the bus clock (SCLK) frequency.

#### 8.19.4 Debug Data

The debug data pins, DDATA0\_GPIO0, DDATA1\_GPIO1, DDATA2\_GPIO2, and DDATA3\_GPIO4, are four bits wide. This nibble-wide bus displays captured processor data and break-point status.

#### 8.19.5 Processor Status

The processor status pins, PST0\_GPIO59, PST1\_GPIO60, PST2\_GPIO61, and PST3\_GPIO62, indicate the SCF5249 processor status. During debug mode, the timing is synchronous with the processor clock (PSTCLK) and the status is not related to the current bus transfer.

PST[3:0] **Definition** (HEX) (BINARY) 0000 \$0 Continue execution \$1 0001 Begin execution of an instruction 0010 Reserved \$2 \$3 0011 Entry into user-mode 0100 Begin execution of PULSE and WDDATA instructions \$4 0101 Begin execution of taken branch or Synch\_PC<sup>1</sup> \$5 0110 Reserved \$6 Begin execution of RTE instruction \$7 0111 1000 \$8 Begin 1-byte data transfer on DDATA Begin 2-byte data transfer on DDATA \$9 1001 1010 Begin 3-byte data transfer on DDATA \$A \$B 1011 Begin 4-byte data transfer on DDATA Exception processing<sup>2</sup> \$C 1100 Emulator mode entry exception processing<sup>2</sup> \$D 1101 \$E 1110 Processor is stopped, waiting for interrupt<sup>2</sup> Processor is halted<sup>2</sup> \$F 1111 Notes:

**Table 14. Processor Status Signal Encodings**

- 4. Rev. B enhancement.

- These encodings are asserted for multiple cycles.

## 8.20 BDM/JTAG Signals

The SCF5249 complies with the IEEE 1149.1A JTAG testing standard. The JTAG test pins are multiplexed with background debug pins.

#### 8.20.1 Test Clock

TCK is the dedicated JTAG test logic clock that is independent of the SCF5249 processor clock. Various JTAG operations occur on the rising or falling edge of TCK. The internal JTAG controller logic is designed such that holding TCK high or low for an indefinite period of time will not cause the JTAG test logic to lose state information. If TCK will not be used, it should be tied to ground.

#### 8.20.2 Test Reset/Development Serial Clock

The TEST[3:0] signals determine the function of the TRST/DSCLK dual-purpose pin. If TEST[3:0]=0001, the DSCLK function is selected. If TEST[3:0]=0000, the TRST function is selected. TEST[3:0] should not be changed while RSTI = 1. When used as TRST, this pin will asynchronously reset the internal JTAG controller to the test logic reset state, causing the JTAG instruction register to choose the ibypassî command. When this occurs, all the JTAG logic is benign and will not interfere with the normal functionality of the SCF5249 processor. Although this signal is asynchronous, Freescale recommends that TRST make only a 0 to 1 (asserted to negated) transition while TMS is held at a logic 1 value. TRST has an internal pullup so that if it is not driven low its value will default to a logic level of 1. However, if TRST will not be used, it can either be tied to ground or, if TCK is clocked, it can be tied to VDD. If it is tied to ground, it will place the JTAG controller in the test logic reset state immediately. If it is tied to VDD, it will cause the JTAG controller (if TMS is a logic 1) to eventually end up in the test logic reset state after 5 clocks of TCK. This pin is also used as the development serial clock (DSCLK) for the serial interface to the Debug Module. The maximum frequency for the DSCLK signal is 1/5 the BCLKO frequency.

#### 8.20.3 Test Mode Select/Break Point

The TEST[3:0] signals determine the TMS/BKPT pin function. If TEST[3:0] =0001, the BKPT function is selected. If TEST[3:0] = 0000, then the TMS function is selected. TEST[3:0] should not change while RSTI = 1. When used as TMS, this input signal provides the JTAG controller with information to determine which test operation mode should be performed. The value of TMS and current state of the internal 16-state JTAG controller state machine at the rising edge of TCK determine whether the JTAG controller holds its current state or advances to the next state. This directly controls whether JTAG data or instruction operations occur. TMS has an internal pullup so that if it is not driven low, its value will default to a logic level of 1. However, if TMS will not be used, it should be tied to VDD. This pin also signals a hardware breakpoint to the processor when in the debug mode.

#### 8.20.4 Test Data Input/Development Serial Input

The TDI/DS is a dual-function pin. If TEST[3:0] = 0001, then DSI is selected. If TEST[3:0] = 0000, then TDI is selected. When used as TDI, this input signal provides the serial data port for loading the various JTAG shift registers composed of the boundary scan register, the bypass register, and the instruction register. Shifting in of data depends on the state of the JTAG controller state machine and the instruction currently in the instruction register. This data shift occurs on the rising edge of TCK. TDI also has an internal pullup so that if it is not driven low its value will default to a logic level of 1. However, if TDI will not be used, it should be tied to VDD. This pin also provides the single-bit communication for the debug module commands.

#### 8.20.5 Test Data Output/Development Serial Output

The TDO/DSO is a dual-function pin. When TEST[3:0] = 0001, then DSO is selected. When TEST[3:0] = 0000, TDO is selected. When used as TDO, this output signal provides the serial data port for outputting

SCF5249 Integrated ColdFire® Microprocessor Data Sheet, Rev. 3

#### **Electrical Characteristics**

data from the JTAG logic. Shifting out of data depends on the state of the JTAG controller state machine and the instruction currently in the instruction register. This data shift occurs on the falling edge of TCK. When TDO is not outputting test data, it is three-stated. TDO can also be placed in three-state mode to allow bussed or parallel connections to other devices having JTAG. This signal also provides single-bit communication for the debug module responses.

## 8.21 Clock and Reset Signals

These signals configure the SCF5249 and provide interface signals to the external system.

#### 8.21.1 Reset In

Asserting  $\overline{RSTI}$  causes the SCF5249 to enter reset exception processing. When  $\overline{RSTI}$  is recognized, the data bus is tri-stated.

#### 8.21.2 System Bus Input

The CRIN signal is the system clock input. The device has no on-chip clock oscillator, and needs an external oscillator.

#### 9 Electrical Characteristics

**Table 15. Maximum Ratings**

| Rating                         | Symbol                                   | Value        | Units |

|--------------------------------|------------------------------------------|--------------|-------|

| Supply Core Voltage            | V <sub>cc</sub>                          | -0.5 to +2.5 | V     |

| Maximum Core Operating Voltage | V <sub>cc</sub>                          | +1.98        | V     |

| Minimum Core Operating Voltage | V <sub>cc</sub>                          | +1.62        | V     |

| Supply I/O Voltage             | V <sub>cc</sub>                          | -0.5 to +4.6 | V     |

| Maximum I/O Operating Voltage  | erating Voltage V <sub>cc</sub> +3.6     |              | V     |

| Minimum I/O Operating Voltage  | V <sub>cc</sub>                          | +3.0         | V     |

| Input Voltage                  | out Voltage V <sub>in</sub> -0.5 to +6.0 |              | V     |

| Storage Temperature Range      | e Range T <sub>stg</sub> -65 to15        |              | °C    |

**Table 16. Operating Temperature**

| Characteristic                        | Symbol            | Value           | Units |

|---------------------------------------|-------------------|-----------------|-------|

| Maximum Operating Ambient Temperature | T <sub>Amax</sub> | 85 <sup>1</sup> | °C    |

| Minimum Operating Ambient Temperature | T <sub>Amin</sub> | 0               | °C    |

Note: This published maximum operating ambient temperature should be used only as a system design guideline. All device operating parameters are guaranteed only when the junction temperature does not exceed 105°C.

Table 17. DC Electrical Specifications (Vcc =  $3.3 \text{ Vdc} \pm 0.3 \text{ Vdc}$ )

| Characteristic                                                                                                                                                                                           | Symbol           | Min  | Max | Units |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|-------|

| Operation Voltage Range for I/O                                                                                                                                                                          | V <sub>cc</sub>  | 3.0  | 3.6 | V     |

| Input High Voltage                                                                                                                                                                                       | V <sub>IH</sub>  | 2    | 5.5 | V     |

| Input Low Voltage                                                                                                                                                                                        | V <sub>IL</sub>  | -0.3 | 0.8 | V     |

| Input Leakage Current @ 0.0 V /3.3 V<br>During Normal Operation                                                                                                                                          | I <sub>in</sub>  | -    | ±1  | μμΑ   |

| Hi-Impedance (Three-State) Leakage Current<br>@ 0.0 V/3.3 V During Normal Operation                                                                                                                      | I <sub>TSI</sub> | -    | ±1  | μμΑ   |

| Output High Voltage I <sub>OH</sub> = 8mA <sup>1</sup> , 4mA <sup>2</sup> , 2mA <sup>3</sup>                                                                                                             | V <sub>OH</sub>  | 2.4  | -   | V     |

| Output Low Voltage I <sub>OL</sub> = 8mA <sup>1</sup> , 4mA <sup>2</sup> , 2mA <sup>3</sup>                                                                                                              | V <sub>OL</sub>  | -    | 0.4 | V     |

| Schmitt Trigger Low to High Threshold Point <sup>6</sup>                                                                                                                                                 | $V_{T+}$         | 1.47 | -   | V     |

| Schmitt Trigger High to Low Threshold Point <sup>6</sup>                                                                                                                                                 | V <sub>T-</sub>  | -    | .95 | V     |

| Load Capacitance (DATA[31:16], DCL0, DCL1, SCLK[4:1], SCLKOUT, EBUOUT[2:1], LRCK[4:1], SDATAO[2:1], CFLG, EF, DBCDDATA[3:0], DBCPST[3:0], CNPSTCLK, IDEDIOR, IDEDIOW, IORDY, SRE, SWE)                   | C <sub>L</sub>   | -    | 50  | pF    |