# HM626770Series

捷多邦,专业PCBIMaInterlande Only

Refer to HM6287H Series

### 65536-word x 1-bit High Speed CMOS Static RAM

#### ■ FEATURES

- High Speed: Fast Access Time 45/55/70ns (max.)

- Single 5V Supply and High Density 22 Pin Package

- Low Power Standby and Low Power Operation Standby: 100μW (typ.)/10μW (typ.) (L-version) Operation: 300mW (typ.)

- Completely Static Memory

No Clock or Timing Strobe Required

- Equal Access and Cycle Times

- Directly TTL Compatible: All Inputs and Output

- Capability of Battery Back Up Operation (L-version)

#### **■ ORDERING INFORMATION**

| Type No.    | Access Time | Package                       |

|-------------|-------------|-------------------------------|

| HM6287P-45  | 45ns        |                               |

| HM6287P-55  | 55ns        |                               |

| HM6287P-70  | 70ns        | 300 mil 22 pin<br>Plastic DIP |

| HM6287LP-45 | 45ns        |                               |

| HM6287LP-55 | 55ns        |                               |

| HM6287LP-70 | 70ns        |                               |

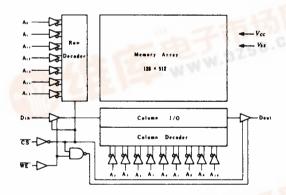

#### BLOCK DIAGRAM

#### PIN ARRANGEMENT

#### TRUTH TABLE

| CS | WE | Mode         | V <sub>CC</sub> Current            | Dout Pin | Ref. Cycle  |

|----|----|--------------|------------------------------------|----------|-------------|

| Н  | х  | Not Selected | I <sub>SB</sub> , I <sub>SB1</sub> | High Z   |             |

| L  | Н  | Read         | Icc                                | Dout     | Read Cycle  |

| L  | L  | Write        | I <sub>CC</sub>                    | High Z   | Write Cycle |

#### **■ ABSOLUTE MAXIMUM RATINGS**

| Item                                    | Symbol | Rating         | Unit |

|-----------------------------------------|--------|----------------|------|

| Voltage on Any Pin Relative to $V_{SS}$ | $V_T$  | -0.5°1 to +7.0 | V    |

| Power Dissipation                       | $P_T$  | 1.0            | W    |

| Operating Temperature                   | Topr   | 0 to +70       | °c   |

| Storage Temperature                     | Tetg   | -55 to +125    | °C   |

| Temperature Under Bias                  | Tbias  | -10 to +85     | °C   |

Note) \*1. -3.5V for pulse width  $\leq 20$ ns

# ■ RECOMMENDED DC OPERATING CONDITIONS ( $T_a = 0 \text{ to } +70^{\circ}\text{C}$ )

| Item           | Symbol          | min                | typ | max | Unit |

|----------------|-----------------|--------------------|-----|-----|------|

|                | Vcc             | 4.5                | 5.0 | 5.5 | v    |

| Supply Voltage | V <sub>SS</sub> | 0                  | 0   | 0   | V    |

|                | V <sub>IH</sub> | 2.2                | -   | 6.0 | v    |

| Input Voltage  | $V_{IL}$        | -0.5 <sup>*1</sup> | -   | 0.8 | V    |

Note) \*1. -3.0V for pulse width ≤ 20ns

# ■ DC AND OPERATING CHARACTERISTICS ( $V_{CC}$ = 5V ± 10%, $V_{SS}$ = 0V, $T_a$ = 0 to +70°C)

| Item                           | Symbol           | Test Conditions                                                  | min | typ*1 | max   | Unit |

|--------------------------------|------------------|------------------------------------------------------------------|-----|-------|-------|------|

| Input Leakage Current          | ILI              | $V_{CC}$ = 5.5V, $V_{in}$ = $V_{SS}$ to $V_{CC}$                 | _   |       | 2.0   | μА   |

| Output Leakage Current         | ILOI             | $\overline{CS} = V_{IH}, V_{out} = V_{SS} \text{ to } V_{CC}$    |     |       | 2.0   | μA   |

| Operating Power Supply Current | ICC              | $\overline{CS} = V_{IL}$ , $I_{out} = 0$ mA, min. cycle          |     | 60    | 100   | mA   |

| Operating to work depths,      | I <sub>SB</sub>  | $\overline{\text{CS}} = V_{IH}$ , min. cycle                     |     | 10    | 30    | mA   |

| Standby Power Supply Current   | - 55             | $\overline{CS} \ge V_{CC}-0.2V$                                  |     | 0.02  | 2.0   | mA   |

| Standby rower supply current   | I <sub>SB1</sub> | $0V \leq V_{in} \leq 0.2V \text{ or } V_{CC} - 0.2V \leq V_{in}$ | _   | 2*2   | 100°2 | μA   |

|                                | VOL              | I <sub>OL</sub> = 8mA                                            |     | _     | 0.4   | v    |

| Output Voltage                 | VOH              | $I_{OH} = -4.0$ mA                                               | 2.4 | Ι-    |       | V    |

Notes) \*1. Typical limits are at  $V_{CC}$  = 5.0V,  $T_a$  = 25°C and specified loading. \*2. This characteristics is guaranteed only for L-version.

# ■ CAPACITANCE (f = 1 MHz, $T_a = 25 ^{\circ}\text{C}$ )

| Item               | Symbol | Test Conditions       | min | typ | max | Unit |

|--------------------|--------|-----------------------|-----|-----|-----|------|

| Input Capacitance  | Cin    | V <sub>in</sub> = 0V  | -   |     | 5   | pF   |

| Output Capacitance | Cout   | V <sub>out</sub> = 0V |     | -   | 7.5 | pF   |

Note) This parameter is sampled and not 100% tested.

## ■ AC CHARACTERISTICS ( $V_{CC} = 5V \pm 10\%$ , $T_a = 0$ to +70°C, unless otherwise noted)

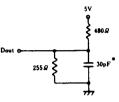

#### • AC TEST CONDITIONS

Input Pulse Levels: VSS to 3.0V Input Rise and Fall Times: 5ns

Input and Output Timing Reference Levels: 1.5V

Output Load: See Figure

#### **Output Load A**

Output Load B

# Including scope & jig capacitance

#### #Including scope & jig capacitance

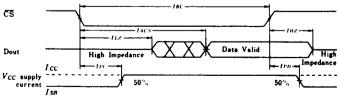

#### READ CYCLE

| Item                                 | Symbol | HM6287-45 |     | HM6287-55 |     | HM6287-70 |     | 11-:4 | Ι., .   |

|--------------------------------------|--------|-----------|-----|-----------|-----|-----------|-----|-------|---------|

| item                                 | Symbol | min       | max | min       | max | min       | max | Unit  | Notes   |

| Read Cycle Time                      | †RC    | 45        | _   | 55        | -   | 70        | -   | ns    | 1       |

| Address Access Time                  | †AA    | _         | 45  | _         | 55  | _         | 70  | ns    |         |

| Chip Select Access Time              | †ACS   | _         | 45  | _         | 55  | -         | 70  | ns    |         |

| Output Hold from Address Change      | †OH    | 5         |     | 5         | -   | 5         | -   | ns    |         |

| Chip Selection to Output in Low Z    | tLZ    | 5         | -   | 5         | _   | 5         | _   | ns    | 2, 3, 7 |

| Chip Deselection to Output in High Z | †HZ    | 0         | 30  | 0         | 30  | 0         | 30  | ns    | 2, 3, 7 |

| Chip Selection to Power Up Time      | †PU    | 0         | _   | 0         | -   | 0         | -   | ns    | 7       |

| Chip Deselection to Power Down Time  | tPD    | _         | 40  |           | 40  |           | 40  | ns    | 7       |

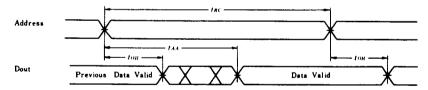

### Timing Waveform of Read Cycle No. 1 (4)(5)

### Timing Waveform of Read Cycle No. 2<sup>(4)(6)</sup>

#### Notes:

- 1. All Read Cycle timings are referenced from last valid address to the first transitioning address.

- 2. At any given temperature and voltage condition, tHZ max, is less than tLZ min, both for a given device and from device to device.

- Transition is measured ±500 mV from steady state voltage with specified loading in Load B.

- 4. WE is high for READ Cycle.

- 5. Device is continuously selected, while  $\overline{CS} = V_{IL}$ .

- 6. Address valid prior to or coincident with CS transition low.

- 7. This parameter is sampled and not 100% tested.

# (C) HITACHI

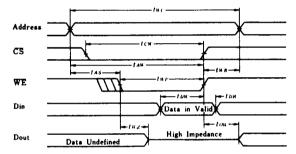

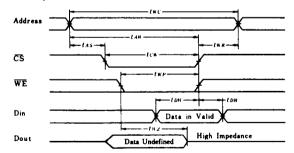

#### WRITE CYCLE

| •                                 | 0      | HM62 | HM6287-45 |     | HM6287-55 |     | 87-70 | Unit | Notes |

|-----------------------------------|--------|------|-----------|-----|-----------|-----|-------|------|-------|

| Item                              | Symbol | min  | max       | min | max       | min | max   | Omi  | Notes |

| Write Cycle Time                  | tWC    | 45   | -         | 55  | -         | 70  | -     | ns   | 2     |

| Chip Selection to End of Write    | tCW    | 40   |           | 50  | _         | 55  | -     | ns   |       |

| Address Valid to End of Write     | tAW.   | 40   | _         | 50  | [ -       | 55  | -     | ns   |       |

| Address Setup Time                | tAS.   | 0    | _         | 0   |           | 0   | -     | ns   |       |

| Write Pulse Width                 | tWP    | 25   |           | 35  |           | 40  | -     | ns   |       |

| Write Recovery Time               | tWR    | 0    | -         | 0   | -         | 0   |       | ns   |       |

| Data Valid to End of Write        | †DW    | 25   |           | 25  | -         | 30  |       | ns   |       |

| Data Hold Time                    | t DH   | 0    | _         | 0   | -         | 0   | -     | ns   | l     |

| Write Enabled to Output in High Z | twz    | 0    | 25        | 0   | 25        | 0   | 30    | ns   | 3,4   |

| Output Active from End of Write   | tow    | 0    | T -       | 0   | -         | 0   | _     | ns   | 3,4   |

### ● Timing Waveform of Write Cycle No. 1 (WE Controlled)

#### ● Timing Waveform of Write Cycle No. 1 (CS Controlled)

- Notes)

1. If CS goes high Simultaneously with WE high, the output remains in a high impedance state.

2. All Write Cycle timings are referenced from the last valid address to the first transitioning address.

- 3. Transition is measured ±500mV from steady state voltage with specified loading in Load B.

- 4. This parameter is sampled and not 100% tested.

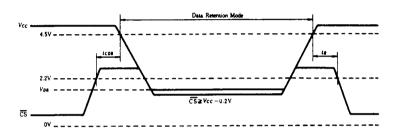

# ■ LOW $V_{CC}$ DATA RETENTION CHARACTERISTICS ( $T_a = 0 \text{ to } +70^{\circ}\text{C}$ ) This characteristics is guaranteed only for L-version.

| Parameter                            | Symbol          | Test Condition                                                                        | min.  | typ. | max. | Unit |

|--------------------------------------|-----------------|---------------------------------------------------------------------------------------|-------|------|------|------|

| VCC for Data Retention               | V <sub>DR</sub> | $\frac{\overline{CS} \ge VCC - 0.2V}{Vin \ge VCC - 0.2V}$ or                          | 2.0   | -    |      | V    |

| Data Retention Current               | ICCDR           | $\begin{array}{c c} Vin \leq VCC^{-0.2}V & 0.2V \\ 0V \leq Vin \leq 0.2V \end{array}$ | -     | 1    | 50*2 | μA   |

| Chip Deselect to Data Retention Time | †CDR            | See retention wave-                                                                   | 0     | -    | -    | ns   |

| Operation Recovery Time              | t <sub>R</sub>  | form                                                                                  | tRC*1 | -    | -    | ns   |

Note) \*1.  $t_{RC}$  = Read Cycle Time \*2.  $V_{CC}$  = 3.0V

### LOW V<sub>CC</sub> DATA RETENTION WAVEFORM

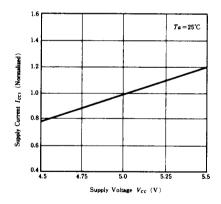

#### SUPPLY CURRENT vs. SUPPLY VOLTAGE

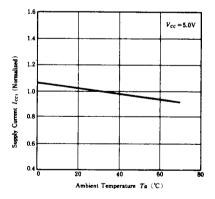

#### SUPPLY CURRENT Vs. AMBIENT TEMPERATURE

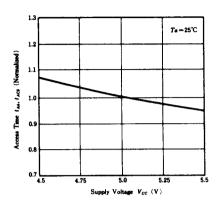

#### ACCESS TIME vs. SUPPLY VOLTAGE

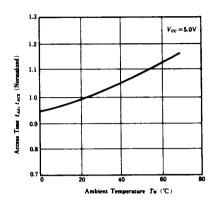

### ACCESS TIME VS. AMBIENT TEMPERATURE

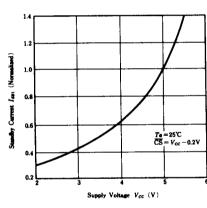

STANDBY CURRENT VS. SUPPLY VOLTAGE

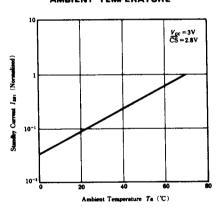

STANDBY CURRENT vs. AMBIENT TEMPERATURE

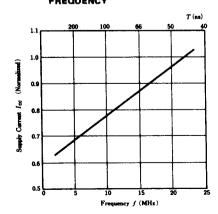

SUPPLY CURRENT W. FREQUENCY

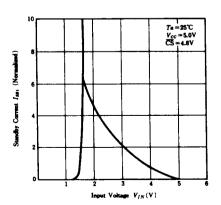

STANDBY CURRENT VS. INPUT VOLTAGE

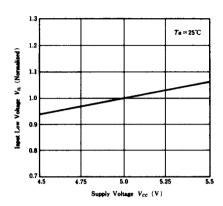

# INPUT LOW VOLTAGE VS. SUPPLY VOLTAGE

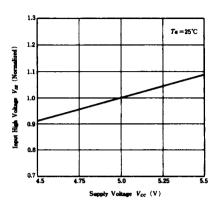

# INPUT HIGH VOLTAGE VS. SUPPLY VOLTAGE

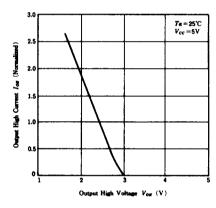

# OUTPUT HIGH CURRENT VS. OUTPUT HIGH VOLTAGE

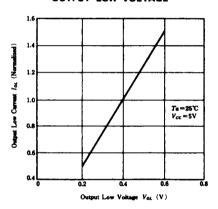

# OUTPUT LOW CURRENT WS. OUTPUT LOW VOLTAGE