# **Features**

- Compatible with MCS®-51 Products

- 4K Bytes of In-System Programmable (ISP) Flash Memory

Endurance: 1000 Write/Erase Cycles

- 2.7V to 4.0V Operating Range

- Fully Static Operation: 0 Hz to 16 MHz

- Three-level Program Memory Lock

- 128 x 8-bit Internal RAM

- 32 Programmable I/O Lines

- Two 16-bit Timer/Counters

- Six Interrupt Sources

- Full Duplex UART Serial Channel

- Low-power Idle and Power-down Modes

- Interrupt Recovery from Power-down Mode

- Watchdog Timer

- Dual Data Pointer

- Power-off Flag

- Flexible ISP Programming (Byte and Page Mode)

- Green (Pb/Halide-free) Packaging Option

# 1. Description

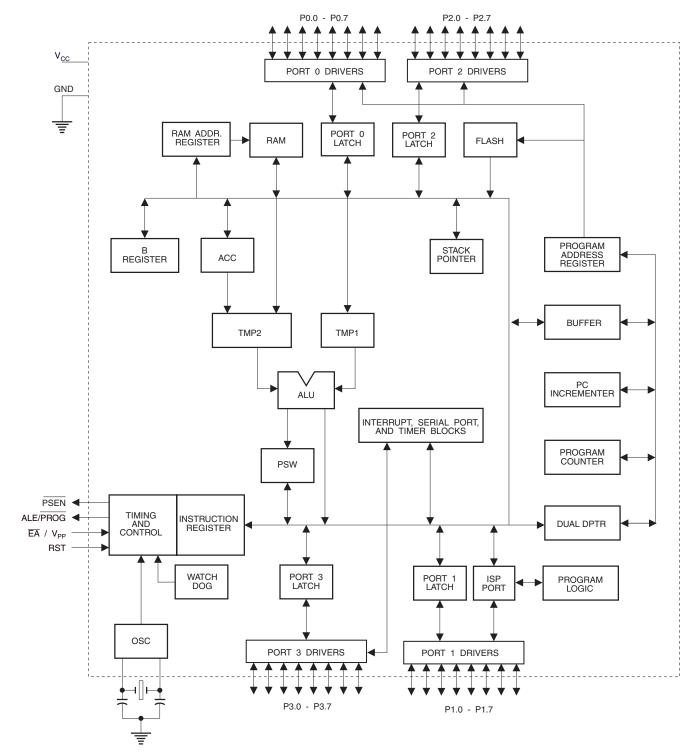

The AT89LS51 is a low-voltage, high-performance CMOS 8-bit microcontroller with 4K bytes of in-system programmable Flash memory. The device is manufactured using Atmel's high-density nonvolatile memory technology and is compatible with the industry-standard 80C51 instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with in-system programmable Flash on a monolithic chip, the Atmel AT89LS51 is a powerful microcontroller which provides a highly-flexible and cost-effective solution to many embedded control applications.

The AT89LS51 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, two 16-bit timer/counters, a five-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89LS51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power-down mode saves the RAM contents but freezes the oscillator, disabling all other chip functions until the next external interrupt or hardware reset.

8-bit Low-Voltage Microcontroller with 4K Bytes In-System Programmable Flash

# AT89LS51

3053B-MICRO-3/05

# <u>AIMEL</u>

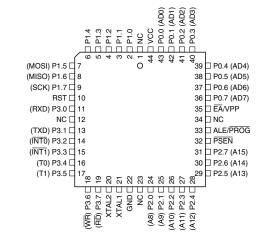

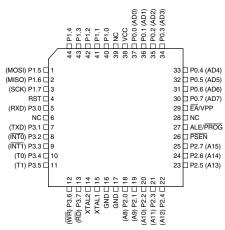

# 2. Pin Configurations

### 2.1 40-lead PDIP

|               |    |    | 1            |

|---------------|----|----|--------------|

| P1.0 🗆        | 1  | 40 | ⊐ vcc        |

| P1.1 🗆        | 2  | 39 | D P0.0 (AD0) |

| P1.2 🗆        | 3  | 38 | D P0.1 (AD1) |

| P1.3 🗆        | 4  | 37 | DP0.2 (AD2)  |

| P1.4 🗆        | 5  | 36 | DP0.3 (AD3)  |

| (MOSI) P1.5 🗆 | 6  | 35 | DP0.4 (AD4)  |

| (MISO) P1.6 🗆 | 7  | 34 | DP0.5 (AD5)  |

| (SCK) P1.7 🗆  | 8  | 33 | DP0.6 (AD6)  |

| RST 🗆         | 9  | 32 | D P0.7 (AD7) |

| (RXD) P3.0 🗆  | 10 | 31 | EA/VPP       |

| (TXD) P3.1 🗆  | 11 | 30 | ALE/PROG     |

| (INT0) P3.2 🗆 | 12 | 29 | D PSEN       |

| (INT1) P3.3 🗆 | 13 | 28 | 🗆 P2.7 (A15) |

| (T0) P3.4 🗆   | 14 | 27 | 🗆 P2.6 (A14) |

| (T1) P3.5 🗆   | 15 | 26 | 🗆 P2.5 (A13) |

| (WR) P3.6 🗆   | 16 | 25 | 🗆 P2.4 (A12) |

| (RD) P3.7 🗆   | 17 | 24 | 🗆 P2.3 (A11) |

| XTAL2 🗆       | 18 | 23 | 🗆 P2.2 (A10) |

| XTAL1 🗆       | 19 | 22 | 🗆 P2.1 (A9)  |

| GND 🗆         | 20 | 21 | 🗆 P2.0 (A8)  |

|               |    |    |              |

## 2.3 44-lead PLCC

## 2.2 44-lead TQFP

### 2.4 42-lead PDIP

|               |    |    | 1             |

|---------------|----|----|---------------|

| RST 🗆         | 1  | 42 | □ P1.7 (SCK)  |

| (RXD) P3.0 🗆  | 2  | 41 | P1.6 (MISO)   |

| (TXD) P3.1 🗆  | 3  | 40 | D P1.5 (MOSI) |

| (INT0) P3.2 🗆 | 4  | 39 | 🗆 P1.4        |

| (INT1) P3.3 🗆 | 5  | 38 | 🗆 P1.3        |

| (T0) P3.4 🗆   | 6  | 37 | 🗆 P1.2        |

| (T1) P3.5 🗆   | 7  | 36 | 🗆 P1.1        |

| (WR) P3.6 🗆   | 8  | 35 | 🗆 P1.0        |

| (RD) P3.7 🗆   | 9  | 34 |               |

| XTAL2         | 10 | 33 | PWRVDD        |

| XTAL1 🗆       | 11 | 32 | 🗆 P0.0 (AD0)  |

| GND 🗆         | 12 | 31 | 🗆 P0.1 (AD1)  |

| PWRGND 🗆      | 13 | 30 | 🗆 P0.2 (AD2)  |

| (A8) P2.0 🗆   | 14 | 29 | 🗆 P0.3 (AD3)  |

| (A9) P2.1 🗆   | 15 | 28 | 🗆 P0.4 (AD4)  |

| (A10) P2.2 🗆  | 16 | 27 | 🗆 P0.5 (AD5)  |

| (A11) P2.3 🗆  | 17 | 26 | 🗆 P0.6 (AD6)  |

| (A12) P2.4 🗆  | 18 | 25 | 🗆 P0.7 (AD7)  |

| (A13) P2.5 🗆  | 19 | 24 | EA/VPP        |

| (A14) P2.6 🗆  | 20 | 23 | ALE/PROG      |

| (A15) P2.7 🗆  | 21 | 22 | D PSEN        |

|               |    |    | ]             |

# 3. Block Diagram

# 4. Pin Description

4.1 VCC

Supply voltage.

4.2 GND

Ground.

## 4.3 Port 0

Port 0 is an 8-bit open drain bidirectional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-impedance inputs.

Port 0 can also be configured to be the multiplexed low-order address/data bus during accesses to external program and data memory. In this mode, P0 has internal pull-ups.

Port 0 also receives the code bytes during Flash programming and outputs the code bytes during program verification. **External pull-ups are required during program verification**.

## 4.4 Port 1

Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current  $(I_{IL})$  because of the internal pull-ups.

Port 1 also receives the low-order address bytes during Flash programming and verification.

| Port Pin | Alternate Functions                   |

|----------|---------------------------------------|

| P1.5     | MOSI (used for In-System Programming) |

| P1.6     | MISO (used for In-System Programming) |

| P1.7     | SCK (used for In-System Programming)  |

### 4.5 Port 2

Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current ( $I_{IL}$ ) because of the internal pull-ups.

Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application, Port 2 uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.

Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.

#### 4.6 Port 3

Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current ( $I_{II}$ ) because of the pull-ups.

Port 3 receives some control signals for Flash programming and verification.

Port 3 also serves the functions of various special features of the AT89LS51, as shown in the following table.

| Port Pin | Alternate Functions                    |

|----------|----------------------------------------|

| P3.0     | RXD (serial input port)                |

| P3.1     | TXD (serial output port)               |

| P3.2     | INT0 (external interrupt 0)            |

| P3.3     | INT1 (external interrupt 1)            |

| P3.4     | T0 (timer 0 external input)            |

| P3.5     | T1 (timer 1 external input)            |

| P3.6     | WR (external data memory write strobe) |

| P3.7     | RD (external data memory read strobe)  |

#### 4.7 RST

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device. This pin drives High for 98 oscillator periods after the Watchdog times out. The DISRTO bit in SFR AUXR (address 8EH) can be used to disable this feature. In the default state of bit DISRTO, the RESET HIGH out feature is enabled.

### 4.8 ALE/PROG

Address Latch Enable (ALE) is an output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.

In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external data memory.

If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.

#### 4.9 **PSEN**

Program Store Enable (PSEN) is the read strobe to external program memory.

When the AT89LS51 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.

# <u>AMEL</u>®

# 4.10 EA/VPP

External Access Enable.  $\overline{EA}$  must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed,  $\overline{EA}$  will be internally latched on reset.

$\overline{\text{EA}}$  should be strapped to  $V_{\text{CC}}$  for internal program executions.

This pin also receives the 12-volt programming enable voltage ( $V_{PP}$ ) during Flash programming.

# **4.11 XTAL1** Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

# 4.12 XTAL2

Output from the inverting oscillator amplifier

# 5. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in Table 5-1.

Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect.

| 0F8H |                  |                  |                   |                  |                  |                  |                    |                  | 0FFH |

|------|------------------|------------------|-------------------|------------------|------------------|------------------|--------------------|------------------|------|

| 0F0H | B<br>00000000    |                  |                   |                  |                  |                  |                    |                  | 0F7H |

| 0E8H |                  |                  |                   |                  |                  |                  |                    |                  | 0EFH |

| 0E0H | ACC<br>00000000  |                  |                   |                  |                  |                  |                    |                  | 0E7H |

| 0D8H |                  |                  |                   |                  |                  |                  |                    |                  | 0DFH |

| 0D0H | PSW<br>00000000  |                  |                   |                  |                  |                  |                    |                  | 0D7H |

| 0C8H |                  |                  |                   |                  |                  |                  |                    |                  | 0CFH |

| 0C0H |                  |                  |                   |                  |                  |                  |                    |                  | 0C7H |

| 0B8H | IP<br>XX000000   |                  |                   |                  |                  |                  |                    |                  | 0BFH |

| 0B0H | P3<br>11111111   |                  |                   |                  |                  |                  |                    |                  | 0B7H |

| 0A8H | IE<br>0X000000   |                  |                   |                  |                  |                  |                    |                  | 0AFH |

| 0A0H | P2<br>11111111   |                  | AUXR1<br>XXXXXXX0 |                  |                  |                  | WDTRST<br>XXXXXXXX |                  | 0A7H |

| 98H  | SCON<br>00000000 | SBUF<br>XXXXXXXX |                   |                  |                  |                  |                    |                  | 9FH  |

| 90H  | P1<br>11111111   |                  |                   |                  |                  |                  |                    |                  | 97H  |

| 88H  | TCON<br>00000000 | TMOD<br>00000000 | TL0<br>00000000   | TL1<br>00000000  | TH0<br>00000000  | TH1<br>00000000  | AUXR<br>XXX00XX0   |                  | 8FH  |

| 80H  | P0<br>11111111   | SP<br>00000111   | DP0L<br>00000000  | DP0H<br>00000000 | DP1L<br>00000000 | DP1H<br>00000000 |                    | PCON<br>0XXX0000 | 87H  |

Table 5-1.

AT89LS51 SFR Map and Reset Values

User software should not write 1s to these unlisted locations, since they may be used in future products to invoke new features. In that case, the reset or inactive values of the new bits will always be 0.

**Interrupt Registers:** The individual interrupt enable bits are in the IE register. Two priorities can be set for each of the five interrupt sources in the IP register.

| Table 5-2.             | AUXI                     | R: Auxi                       | liary Re  | egister       |                 |             |             |                     |  |  |

|------------------------|--------------------------|-------------------------------|-----------|---------------|-----------------|-------------|-------------|---------------------|--|--|

| AUXR                   | A                        | ddress =                      | = 8EH     |               |                 |             | Reset       | t Value = XXX00XX0B |  |  |

| Not Bit<br>Addressable |                          |                               |           |               |                 |             |             |                     |  |  |

|                        | _                        | -                             | _         | WDIDLE        | DISRTO          | -           | _           | DISALE              |  |  |

| Bit                    | 7                        | 6                             | 5         | 4             | 3               | 2           | 1           | 0                   |  |  |

| –<br>DISALE            |                          | Reserved for future expansion |           |               |                 |             |             |                     |  |  |

|                        | DISALE<br>Operating Mode |                               |           |               |                 |             |             |                     |  |  |

|                        | 0                        | ALE                           | is emitt  | ed at a const | ant rate of 1/6 | 6 the oscil | lator frequ | iency               |  |  |

|                        | 1                        | ALE                           | is active | e only during | a MOVX or M     | IOVC inst   | ruction     |                     |  |  |

| DISRTO                 | Disabl                   | e/Enabl                       | e Reset   | out           |                 |             |             |                     |  |  |

|                        | DISRT                    | 0                             |           |               |                 |             |             |                     |  |  |

|                        | 0                        | Rese                          | et pin is | driven High a | after WDT tim   | ies out     |             |                     |  |  |

|                        | 1                        | Rese                          | et pin is | input only    |                 |             |             |                     |  |  |

| WDIDLE                 | Disabl                   | e/Enabl                       | e WDT     | n IDLE mode   | e               |             |             |                     |  |  |

| WDIDLE                 |                          |                               |           |               |                 |             |             |                     |  |  |

| 0                      | WDT                      | continu                       | es to co  | unt in IDLE n | node            |             |             |                     |  |  |

| 1                      | WDT                      | halts co                      | ounting i | n IDLE mode   | )               |             |             |                     |  |  |

Table 5-2. AUXR: Auxiliary Register

**Dual Data Pointer Registers:** To facilitate accessing both internal and external data memory, two banks of 16-bit Data Pointer Registers are provided: DP0 at SFR address locations 82H-83H and DP1 at 84H-85H. Bit DPS = 0 in SFR AUXR1 selects DP0 and DPS = 1 selects DP1. The user should **always** initialize the DPS bit to the appropriate value before accessing the respective Data Pointer Register.

**Power Off Flag:** The Power Off Flag (POF) is located at bit 4 (PCON.4) in the PCON SFR. POF is set to "1" during power up. It can be set and rest under software control and is not affected by reset.

AUXR1 Address = A2H Reset Value = XXXXXX0B Not Bit Addressable DPS Bit 4 7 6 5 3 2 1 0 Reserved for future expansion DPS Data Pointer Register Select DPS 0 Selects DPTR Registers DP0L, DP0H Selects DPTR Registers DP1L, DP1H 1

Table 5-3. AUXR1: Auxiliary Register 1

#### Memory Organization 6.

MCS-51 devices have a separate address space for Program and Data Memory. Up to 64K bytes each of external Program and Data Memory can be addressed.

#### **Program Memory** 6.1

If the EA pin is connected to GND, all program fetches are directed to external memory.

On the AT89LS51, if  $\overline{EA}$  is connected to V<sub>CC</sub>, program fetches to addresses 0000H through FFFH are directed to internal memory and fetches to addresses 1000H through FFFFH are directed to external memory.

#### 6.2 Data Memory

The AT89LS51 implements 128 bytes of on-chip RAM. The 128 bytes are accessible via direct and indirect addressing modes. Stack operations are examples of indirect addressing, so the 128 bytes of data RAM are available as stack space.

#### 7. Watchdog Timer (One-time Enabled with Reset-out)

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upsets. The WDT consists of a 14-bit counter and the Watchdog Timer Reset (WDTRST) SFR. The WDT is defaulted to disable from exiting reset. To enable the WDT, a user must write 01EH and 0E1H in sequence to the WDTRST register (SFR location 0A6H). When the WDT is enabled, it will increment every machine cycle while the oscillator is running. The WDT timeout period is dependent on the external clock frequency. There is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST pin.

## 7.1 Using the WDT

To enable the WDT, a user must write 01EH and 0E1H in sequence to the WDTRST register (SFR location 0A6H). When the WDT is enabled, the user needs to service it by writing 01EH and 0E1H to WDTRST to avoid a WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH), and this will reset the device. When the WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must reset the WDT at least every 16383 machine cycles. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write-only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST pin. The RESET pulse duration is 98xTOSC, where TOSC=1/FOSC. To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

#### 7.2 WDT During Power-down and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Powerdown mode, the user does not need to service the WDT. There are two methods of exiting Power-down mode: by a hardware reset or via a level-activated external interrupt, which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally does whenever the AT89LS51 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service for the interrupt used to exit Power-down mode.

To ensure that the WDT does not overflow within a few states of exiting Power-down, it is best to reset the WDT just before entering Power-down mode.

Before going into the IDLE mode, the WDIDLE bit in SFR AUXR is used to determine whether the WDT continues to count if enabled. The WDT keeps counting during IDLE (WDIDLE bit = 0) as the default state. To prevent the WDT from resetting the AT89LS51 while in IDLE mode, the user should always set up a timer that will periodically exit IDLE, service the WDT, and reenter IDLE mode.

With WDIDLE bit enabled, the WDT will stop to count in IDLE mode and resumes the count upon exit from IDLE.

# 8. UART

The UART in the AT89LS51 operates the same way as the UART in the AT89C51. For further information on the UART operation, please click on the document link below:

http://www.atmel.com/dyn/resources/prod\_documents/DOC4316.PDF

### 9. Timer 0 and 1

Timer 0 and Timer 1 in the AT89LS51 operate the same way as Timer 0 and Timer 1 in the AT89C51. For further information on the timers' operation, please click on the document link below:

http://www.atmel.com/dyn/resources/prod\_documents/DOC4316.PDF

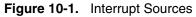

# 10. Interrupts

The AT89LS51 has a total of five interrupt vectors: two external interrupts (INT0 and INT1), two timer interrupts (Timers 0 and 1), and the serial port interrupt. These interrupts are all shown in Figure 10-1.

Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in Special Function Register IE. IE also contains a global disable bit, EA, which disables all interrupts at once.

Note that Table 10-1 shows that bit positions IE.5 and IE.6 are unimplemented. User software should not write 1s to these bit positions, since they may be used in future AT89 products.

The Timer 0 and Timer 1 flags, TF0 and TF1, are set at S5P2 of the cycle in which the timers overflow. The values are then polled by the circuitry in the next cycle.

| (MSB)                                       |          |        |                |       |                                                                                                                                                                                        | (LSB)         |               |                                                                                                         |     |  |  |  |  |  |  |

|---------------------------------------------|----------|--------|----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|

| EA                                          | -        |        | -              | ES    |                                                                                                                                                                                        | ET1           | EX1           | ET0                                                                                                     | EX0 |  |  |  |  |  |  |

| Enable Bit = <sup>-</sup><br>Enable Bit = 0 |          |        | •              |       |                                                                                                                                                                                        |               |               |                                                                                                         |     |  |  |  |  |  |  |

| Symbol                                      |          | Positi | on             |       | Funct                                                                                                                                                                                  | ion           |               |                                                                                                         |     |  |  |  |  |  |  |

| EA IE.7                                     |          |        |                |       | Disables all interrupts. If EA = 0, no interrupt is<br>acknowledged. If EA = 1, each interrupt source is<br>individually enabled or disabled by setting or clearing its<br>enable bit. |               |               |                                                                                                         |     |  |  |  |  |  |  |

| -                                           |          | IE.6   |                |       | Reser                                                                                                                                                                                  | Reserved      |               |                                                                                                         |     |  |  |  |  |  |  |

| -                                           |          | IE.5   |                |       | Reser                                                                                                                                                                                  | ved           |               |                                                                                                         |     |  |  |  |  |  |  |

| ES                                          |          | IE.4   |                |       | Serial                                                                                                                                                                                 | Port interru  | pt enable bit | t                                                                                                       |     |  |  |  |  |  |  |

| ET1                                         |          | IE.3   |                |       | Timer                                                                                                                                                                                  | 1 interrupt e | enable bit    |                                                                                                         |     |  |  |  |  |  |  |

| EX1                                         |          | IE.2   |                |       | External interrupt 1 enable bit                                                                                                                                                        |               |               |                                                                                                         |     |  |  |  |  |  |  |

| ET0                                         |          | IE.1   |                |       | Timer 0 interrupt enable bit                                                                                                                                                           |               |               |                                                                                                         |     |  |  |  |  |  |  |

| EX0                                         |          | IE.0   |                |       | Exterr                                                                                                                                                                                 | nal interrupt | 0 enable bit  |                                                                                                         |     |  |  |  |  |  |  |

| User software s                             | hould ne | ever w | rite 1s to res | serve | d bits, b                                                                                                                                                                              | ecause they   | / may be us   | User software should never write 1s to reserved bits, because they may be used in future AT89 products. |     |  |  |  |  |  |  |

Table 10-1. Interrupt Enable (IE) Register

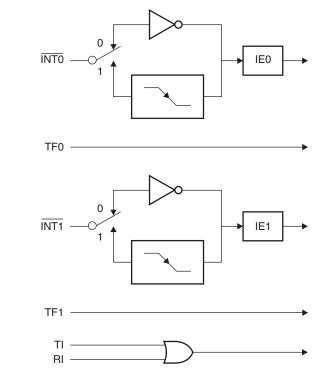

# **11. Oscillator Characteristics**

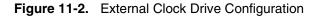

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator, as shown in Figure 11-1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven, as shown in Figure 11-2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clock-ing circuitry is hrough a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

Note: C1, C2 = 30 pF  $\pm$  10 pF for Crystals = 40 pF  $\pm$  10 pF for Ceramic Resonators

# 12. Idle Mode

In idle mode, the CPU puts itself to sleep while all the on-chip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special function registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.

Note that when idle mode is terminated by a hardware reset, the device normally resumes program execution from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when idle mode is terminated by a reset, the instruction following the one that invokes idle mode should not write to a port pin or to external memory.

# 13. Power-down Mode

In the Power-down mode, the oscillator is stopped, and the instruction that invokes Power-down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the Power-down mode is terminated. Exit from Power-down mode can be initiated either by a hardware reset or by activation of an enabled external interrupt (INTO or INT1). Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before  $V_{CC}$  is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize.

| Mode       | Program Memory | ALE | PSEN | PORT0 | PORT1 | PORT2   | PORT3 |

|------------|----------------|-----|------|-------|-------|---------|-------|

| Idle       | Internal       | 1   | 1    | Data  | Data  | Data    | Data  |

| Idle       | External       | 1   | 1    | Float | Data  | Address | Data  |

| Power-down | Internal       | 0   | 0    | Data  | Data  | Data    | Data  |

| Power-down | External       | 0   | 0    | Float | Data  | Data    | Data  |

**Table 13-1.** Status of External Pins During Idle and Power-down Modes

# 14. Program Memory Lock Bits

The AT89LS51 has three lock bits that can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in Table 14-1.

Table 14-1. Lock Bit Protection Modes

|   | Program | Lock Bits |     |                                                                                                                                                                                                                              |

|---|---------|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | LB1     | LB2       | LB3 | Protection Type                                                                                                                                                                                                              |

| 1 | U       | U         | U   | No program lock features                                                                                                                                                                                                     |

| 2 | Ρ       | U         | U   | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on reset, and further programming of the Flash memory is disabled |

| 3 | Р       | Р         | U   | Same as mode 2, but verify is also disabled                                                                                                                                                                                  |

| 4 | Р       | Р         | Р   | Same as mode 3, but external execution is also disabled                                                                                                                                                                      |

When lock bit 1 is programmed, the logic level at the  $\overline{EA}$  pin is sampled and latched during reset. If the device is powered up without a reset, the latch initializes to a random value and holds that value until reset is activated. The latched value of  $\overline{EA}$  must agree with the current logic level at that pin in order for the device to function properly.

# 15. Programming the Flash – Parallel Mode

The AT89LS51 is shipped with the on-chip Flash memory array ready to be programmed. The programming interface needs a high-voltage (12-volt) program enable signal and is compatible with conventional third-party Flash or EPROM programmers.

The AT89LS51 code memory array is programmed byte-by-byte.

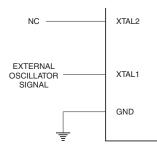

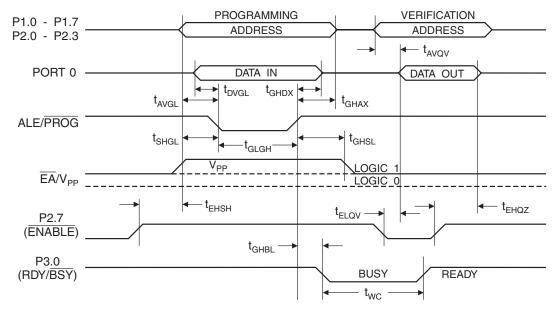

**Programming Algorithm:** Before programming the AT89LS51, the address, data, and control signals should be set up according to the Flash programming mode table (Table 17-1) and Figure 17-1 and Figure 17-2. To program the AT89LS51, take the following steps:

- 1. Input the desired memory location on the address lines.

- 2. Input the appropriate data byte on the data lines.

- 3. Activate the correct combination of control signals.

- 4. Raise  $\overline{EA}/V_{PP}$  to 12V.

- 5. Pulse ALE/PROG once to program a byte in the Flash array or the lock bits. The bytewrite cycle is self-timed and typically takes no more than 50 µs. Repeat steps 1 through 5, changing the address and data for the entire array or until the end of the object file is reached.

**Data Polling:** The AT89LS51 features Data Polling to indicate the end of a byte write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written data on P0.7. Once the write cycle has been completed, true data is valid on all outputs, and the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.

**Ready/Busy:** The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.0 is pulled low after ALE goes high during programming to indicate BUSY. P3.0 is pulled high again when programming is done to indicate READY.

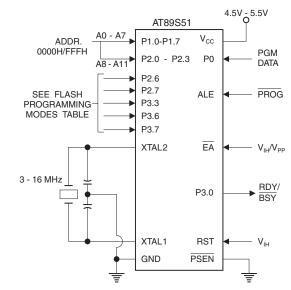

**Program Verify:** If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification. **The status of the individual lock bits can be verified directly by reading them back.**

**Reading the Signature Bytes:** The signature bytes are read by the same procedure as a normal verification of locations 000H, 100H, and 200H, except that P3.6 and P3.7 must be pulled to a logic low. The values returned are as follows.

(000H) = 1EH indicates manufactured by Atmel (100H) = 61H indicates 89LS51 (200H) = 06H

**Chip Erase:** In the parallel programming mode, a chip erase operation is initiated by using the proper combination of control signals and by pulsing ALE/PROG low for a duration of 200 ns - 500 ns.

In the serial programming mode, a chip erase operation is initiated by issuing the Chip Erase instruction. In this mode, chip erase is self-timed and takes about 500 ms.

During chip erase, a serial read from any address location will return 00H at the data output.

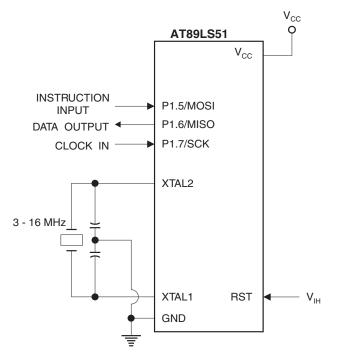

# 16. Programming the Flash – Serial Mode

The Code memory array can be programmed using the serial ISP interface while RST is pulled to  $V_{cc}$ . The serial interface consists of pins SCK, MOSI (input) and MISO (output). After RST is set high, the Programming Enable instruction needs to be executed first before other operations can be executed. Before a reprogramming sequence can occur, a Chip Erase operation is required.

The Chip Erase operation turns the content of every memory location in the Code array into FFH.

Either an external system clock can be supplied at pin XTAL1 or a crystal needs to be connected across pins XTAL1 and XTAL2. The maximum serial clock (SCK) frequency should be less than 1/16 of the crystal frequency. With a 16 MHz oscillator clock, the maximum SCK frequency is 1 MHz.

### 16.1 Serial Programming Algorithm

To program and verify the AT89LS51 in the serial programming mode, the following sequence is recommended:

- 1. Power-up sequence:

- a. Apply power between VCC and GND pins.

- b. Set RST pin to "H".

If a crystal is not connected across pins XTAL1 and XTAL2, apply a 3 MHz to 16 MHz clock to XTAL1 pin and wait for at least 10 milliseconds.

- 2. Enable serial programming by sending the Programming Enable serial instruction to pin MOSI/P1.5. The frequency of the shift clock supplied at pin SCK/P1.7 needs to be less than the CPU clock at XTAL1 divided by 16.

- 3. The Code array is programmed one byte at a time in either the Byte or Page mode. The write cycle is self-timed and typically takes less than 1 ms at 2.7V.

- 4. Any memory location can be verified by using the Read instruction that returns the content at the selected address at serial output MISO/P1.6.

5. At the end of a programming session, RST can be set low to commence normal device operation.

Power-off sequence (if needed):

- 1. Set XTAL1 to "L" (if a crystal is not used).

- 2. Set RST to "L".

- 3. Turn  $V_{CC}$  power off.

**Data Polling:** The Data Polling feature is also available in the serial mode. In this mode, during a write cycle an attempted read of the last byte written will result in the complement of the MSB of the serial output byte on MISO.

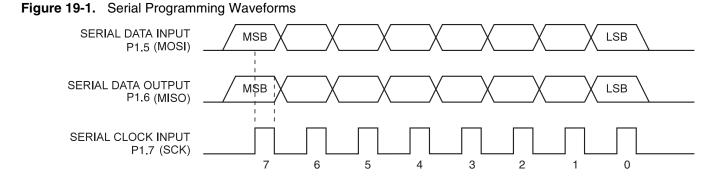

#### 16.2 Serial Programming Instruction Set

The Instruction Set for Serial Programming follows a 4-byte protocol and is shown in Table 19-1.

# 17. Programming Interface – Parallel Mode

Every code byte in the Flash array can be programmed by using the appropriate combination of control signals. The write operation cycle is self-timed and once initiated, will automatically time itself to completion.

Most major worldwide programming vendors offer support for the Atmel microcontroller series. Please contact your local programming vendor for the appropriate software revision.

|                           |          |     |      | ALE/ | EA/             |      |      |      |      |      | P0.7-0                 | P2.3-0  | P1.7-0 |

|---------------------------|----------|-----|------|------|-----------------|------|------|------|------|------|------------------------|---------|--------|

| Mode                      | $v_{cc}$ | RST | PSEN | PROG | V <sub>PP</sub> | P2.6 | P2.7 | P3.3 | P3.6 | P3.7 | Data                   | Address |        |

| Write Code Data           | 5V       | н   | L    | (2)  | 12V             | L    | Н    | Н    | Н    | Н    | D <sub>IN</sub>        | A11-8   | A7-0   |

| Read Code Data            | 5V       | н   | L    | Н    | Н               | L    | L    | L    | Н    | н    | D <sub>OUT</sub>       | A11-8   | A7-0   |

| Write Lock Bit 1          | 5V       | н   | L    | (3)  | 12V             | Н    | н    | Н    | Н    | Н    | х                      | х       | х      |

| Write Lock Bit 2          | 5V       | н   | L    | (3)  | 12V             | Н    | Н    | Н    | L    | L    | х                      | х       | х      |

| Write Lock Bit 3          | 5V       | н   | L    | (3)  | 12V             | Н    | L    | Н    | Н    | L    | х                      | х       | х      |

| Read Lock Bits<br>1, 2, 3 | 5V       | н   | L    | Н    | н               | н    | Н    | L    | н    | L    | P0.2,<br>P0.3,<br>P0.4 | х       | х      |

| Chip Erase                | 5V       | н   | L    | (1)  | 12V             | Н    | L    | Н    | L    | L    | х                      | х       | х      |

| Read Atmel ID             | 5V       | н   | L    | Н    | Н               | L    | L    | L    | L    | L    | 1EH                    | 0000    | 00H    |

| Read Device ID            | 5V       | н   | L    | Н    | Н               | L    | L    | L    | L    | L    | 61H                    | 0001    | 00H    |

| Read Device ID            | 5V       | Н   | L    | Н    | н               | L    | L    | L    | L    | L    | 06H                    | 0010    | 00H    |

**Table 17-1.**Flash Programming Modes

Notes: 1. Each PROG pulse is 200 ns - 500 ns for Chip Erase.

2. Each PROG pulse is 200 ns - 500 ns for Write Code Data.

3. Each PROG pulse is 200 ns - 500 ns for Write Lock Bits.

4. RDY/BSY signal is output on P3.0 during programming.

5. X = don't care.

# AT89LS51

Figure 17-1. Programming the Flash Memory (Parallel Mode)

Figure 17-2. Verifying the Flash Memory (Parallel Mode)

# 18. Flash Programming and Verification Characteristics (Parallel Mode)

| Symbol              | Parameter                             | Min                  | Мах                  | Units |  |

|---------------------|---------------------------------------|----------------------|----------------------|-------|--|

| V <sub>PP</sub>     | Programming Supply Voltage            | 11.5                 | 12.5                 | V     |  |

| I <sub>PP</sub>     | Programming Supply Current            |                      | 10                   | mA    |  |

| I <sub>CC</sub>     | V <sub>CC</sub> Supply Current        |                      | 30                   | mA    |  |

| 1/t <sub>CLCL</sub> | Oscillator Frequency                  | 3                    | 16                   | MHz   |  |

| t <sub>AVGL</sub>   | Address Setup to PROG Low             | 48 t <sub>CLCL</sub> |                      |       |  |

| t <sub>GHAX</sub>   | Address Hold After PROG               | 48 t <sub>CLCL</sub> |                      |       |  |

| t <sub>DVGL</sub>   | Data Setup to PROG Low                | 48 t <sub>CLCL</sub> |                      |       |  |

| t <sub>GHDX</sub>   | Data Hold After PROG                  | 48 t <sub>CLCL</sub> |                      |       |  |

| t <sub>EHSH</sub>   | P2.7 (ENABLE) High to V <sub>PP</sub> | 48 t <sub>CLCL</sub> |                      |       |  |

| t <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low     | 10                   |                      | μs    |  |

| t <sub>GHSL</sub>   | V <sub>PP</sub> Hold After PROG       | 10                   |                      | μs    |  |

| t <sub>GLGH</sub>   | PROG Width                            | 0.2                  | 1                    | μs    |  |

| t <sub>AVQV</sub>   | Address to Data Valid                 |                      | 48 t <sub>CLCL</sub> |       |  |

| t <sub>ELQV</sub>   | ENABLE Low to Data Valid              |                      | 48 t <sub>CLCL</sub> |       |  |

| t <sub>EHQZ</sub>   | Data Float After ENABLE               | 0                    | 48 t <sub>CLCL</sub> |       |  |

| t <sub>GHBL</sub>   | PROG High to BUSY Low                 |                      | 1.0                  | μs    |  |

| t <sub>wc</sub>     | Byte Write Cycle Time                 |                      | 50                   | μs    |  |

Figure 18-1. Flash Programming and Verification Waveforms – Parallel Mode

Figure 18-2. Flash Memory Serial Downloading

# 19. Flash Programming and Verification Waveforms – Serial Mode

#### Table 19-1. Serial Programming Instruction Set

|                                     |           | Instruc                                                                   | tion Format                          |                                            |                                                                                             |

|-------------------------------------|-----------|---------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------|

| Instruction                         | Byte 1    | Byte 2                                                                    | Byte 3                               | Byte 4                                     | Operation                                                                                   |

| Programming Enable                  | 1010 1100 | 0101 0011                                                                 | XXXX XXXX                            | xxxx xxxx<br>0110 1001<br>(Output on MISO) | Enable Serial Programming while RST is high                                                 |

| Chip Erase                          | 1010 1100 | 100x xxxx                                                                 | XXXX XXXX                            | xxxx xxxx                                  | Chip Erase Flash memory array                                                               |

| Read Program Memory<br>(Byte Mode)  | 0010 0000 | A11<br>A00<br>800<br>800<br>800<br>800<br>800<br>800<br>800<br>800<br>800 | A7<br>A55<br>A1233<br>A1233<br>A1233 | 0000 0000<br>0100 40000                    | Read data from Program<br>memory in the byte mode                                           |

| Write Program Memory<br>(Byte Mode) | 0100 0000 | A111 XXXX<br>A111 XXXX<br>A0001                                           | 444<br>44567<br>0123                 | 0000 0000                                  | Write data to Program<br>memory in the byte mode                                            |

| Write Lock Bits <sup>(1)</sup>      | 1010 1100 | 1110 00 🚡 🔛                                                               | xxxx xxxx                            | xxxx xxxx                                  | Write Lock bits (see Note 1)                                                                |

| Read Lock Bits                      | 0010 0100 | xxxx xxxx                                                                 | XXXX XXXX                            | XXTEL EBX                                  | Read back current status of<br>the lock bits (a programmed<br>lock bit reads back as a "1") |

| Read Signature Bytes                | 0010 1000 | A89011 XXXX<br>A89011 XXXX                                                | ⊱xxx xxx0                            | Signature Byte                             | Read Signature Byte                                                                         |

| Read Program Memory<br>(Page Mode)  | 0011 0000 | A411 XXXX<br>A111 XXXX                                                    | Byte 0                               | Byte 1<br>Byte 255                         | Read data from Program<br>memory in the Page Mode<br>(256 bytes)                            |

| Write Program Memory<br>(Page Mode) | 0101 0000 | A10<br>A10<br>A89001<br>A89001                                            | Byte 0                               | Byte 1<br>Byte 255                         | Write data to Program<br>memory in the Page Mode<br>(256 bytes)                             |

Note: 1.  $B1 = 0, B2 = 0 \rightarrow Mode 1$ , no lock protection  $B1 = 0, B2 = 1 \rightarrow Mode 2$ , lock bit 1 activated

B1 = 1, B2 = 0  $\rightarrow$  Mode 3, lock bit 2 activated B1 = 1, B1 = 1  $\rightarrow$  Mode 4, lock bit 3 activated Each of the lock bit modes needs to be activated sequentially before Mode 4 can be executed.

After Reset signal is high, SCK should be low for at least 64 system clocks before it goes high to clock in the enable data bytes. No pulsing of Reset signal is necessary. SCK should be no faster than 1/16 of the system clock at XTAL1.

For Page Read/Write, the data always starts from byte 0 to 255. After the command byte and upper address byte are latched, each byte thereafter is treated as data until all 256 bytes are shifted in/out. Then the next instruction will be ready to be decoded.

# 20. Serial Programming Characteristics

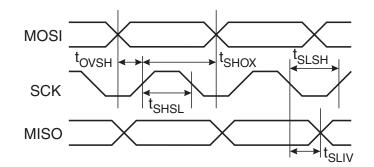

Figure 20-1. Serial Programming Timing

**Table 20-1.**Serial Programming Characteristics,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$ ,  $V_{CC} = 2.7V - 4.0V$  (Unless Otherwise Noted)

| Symbol              | Parameter                         | Min                 | Тур | Max                        | Units |  |

|---------------------|-----------------------------------|---------------------|-----|----------------------------|-------|--|

| 1/t <sub>CLCL</sub> | Oscillator Frequency              | 3                   |     | 16                         | MHz   |  |

| t <sub>CLCL</sub>   | Oscillator Period                 | 62.5                |     |                            | ns    |  |

| t <sub>SHSL</sub>   | SCK Pulse Width High              | 8 t <sub>CLCL</sub> |     |                            | ns    |  |

| t <sub>SLSH</sub>   | SCK Pulse Width Low               | 8 t <sub>CLCL</sub> |     |                            | ns    |  |

| t <sub>ovsH</sub>   | MOSI Setup to SCK High            | t <sub>CLCL</sub>   |     |                            | ns    |  |

| t <sub>SHOX</sub>   | MOSI Hold after SCK High          | 2 t <sub>CLCL</sub> |     |                            | ns    |  |

| t <sub>SLIV</sub>   | SCK Low to MISO Valid             | 10                  | 16  | 32                         | ns    |  |

| t <sub>ERASE</sub>  | Chip Erase Instruction Cycle Time |                     |     | 500                        | ms    |  |

| t <sub>swc</sub>    | Serial Byte Write Cycle Time      |                     |     | 64 t <sub>CLCL</sub> + 400 | μs    |  |

# 21. Absolute Maximum Ratings\*

| Operating Temperature55°C to +125°C                       |

|-----------------------------------------------------------|

| Storage Temperature65°C to +150°C                         |

| Voltage on Any Pin<br>with Respect to Ground1.0V to +7.0V |

| Maximum Operating Voltage 6.6V                            |

| DC Output Current 15.0 mA                                 |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 22. DC Characteristics

The values shown in this table are valid for  $T_A = -40^{\circ}$ C to 85°C and  $V_{CC} = 2.7$ V to 4.0V, unless otherwise noted.

| Symbol           | Parameter                                                | Condition                                 | Min                      | Max                      | Units |  |

|------------------|----------------------------------------------------------|-------------------------------------------|--------------------------|--------------------------|-------|--|

| V <sub>IL</sub>  | Input Low Voltage                                        | (Except EA)                               | -0.5                     | 0.7                      | V     |  |

| V <sub>IL1</sub> | Input Low Voltage (EA)                                   |                                           | -0.5                     | 0.2 V <sub>CC</sub> -0.3 | V     |  |

| V <sub>IH</sub>  | Input High Voltage                                       | (Except XTAL1, RST)                       | 0.2 V <sub>CC</sub> +0.9 | V <sub>CC</sub> +0.5     | V     |  |

| V <sub>IH1</sub> | Input High Voltage                                       | (XTAL1, RST)                              | 0.7 V <sub>CC</sub>      | V <sub>CC</sub> +0.5     | V     |  |

| V <sub>OL</sub>  | Output Low Voltage <sup>(1)</sup> (Ports 1,2,3)          | I <sub>OL</sub> = 0.8 mA                  |                          | 0.45                     | V     |  |

| V <sub>OL1</sub> | Output Low Voltage <sup>(1)</sup><br>(Port 0, ALE, PSEN) | I <sub>OL</sub> = 1.6 mA                  |                          | 0.45                     | V     |  |

|                  |                                                          | I <sub>OH</sub> = -60 μA                  | 2.4                      |                          | V     |  |

| V <sub>OH</sub>  | Output High Voltage<br>(Ports 1,2,3, ALE, PSEN)          | I <sub>OH</sub> = -25 μA                  | 0.65 V <sub>CC</sub>     |                          | V     |  |

|                  |                                                          | I <sub>OH</sub> = -10 μA                  | 0.80 V <sub>CC</sub>     |                          | V     |  |

|                  |                                                          | I <sub>OH</sub> = -800 μA                 | 2.4                      |                          | V     |  |

| V <sub>OH1</sub> | Output High Voltage<br>(Port 0 in External Bus Mode)     | I <sub>OH</sub> = -300 μA                 | 0.75 V <sub>CC</sub>     |                          | V     |  |

|                  |                                                          | I <sub>OH</sub> = -80 μA                  | 0.9 V <sub>CC</sub>      |                          | V     |  |

| I <sub>IL</sub>  | Logical 0 Input Current (Ports 1,2,3)                    | V <sub>IN</sub> = 0.45V                   |                          | -50                      | μA    |  |

| I <sub>TL</sub>  | Logical 1 to 0 Transition Current<br>(Ports 1,2,3)       | V <sub>IN</sub> = 2V                      |                          | -150                     | μA    |  |

| I <sub>LI</sub>  | Input Leakage Current (Port 0, EA)                       | 0.45 < V <sub>IN</sub> < V <sub>CC</sub>  |                          | ±10                      | μA    |  |

| RRST             | Reset Pulldown Resistor                                  |                                           | 50                       | 300                      | KΩ    |  |

| C <sub>IO</sub>  | Pin Capacitance                                          | Test Freq. = 1 MHz, T <sub>A</sub> = 25°C |                          | 10                       | pF    |  |

|                  | Power Supply Current                                     | Active Mode, 12 MHz                       |                          | 25                       | mA    |  |

| I <sub>cc</sub>  | Power Supply Current                                     | Idle Mode, 12 MHz                         |                          | 6.5                      | mA    |  |

|                  | Power-down Mode <sup>(2)</sup>                           | $V_{CC} = 4.0V$                           |                          | 30                       | μA    |  |

Notes: 1. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port:

Port 0: 26 mA Ports 1, 2, 3: 15 mA

Maximum total  $\mathrm{I}_{\mathrm{OL}}$  for all output pins: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

2. Minimum  $V_{\text{CC}}$  for Power-down is 2V.

# 23. AC Characteristics

Under operating conditions, load capacitance for Port 0, ALE/ $\overline{PROG}$ , and  $\overline{PSEN} = 100 \text{ pF}$ ; load capacitance for all other outputs = 80 pF.

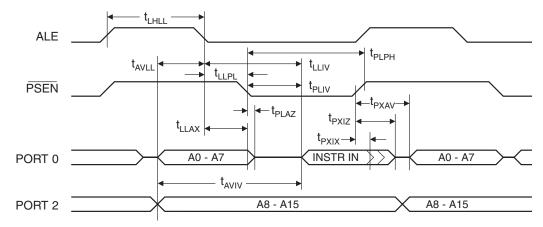

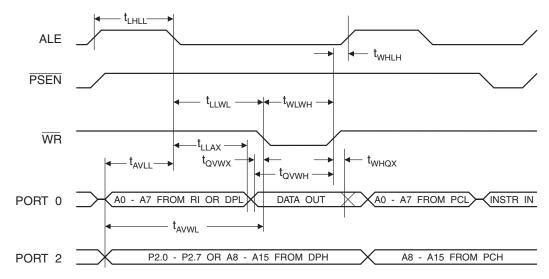

| 23.1 | External | Program | and Data | Memory | Characteristics |

|------|----------|---------|----------|--------|-----------------|

|------|----------|---------|----------|--------|-----------------|

|                     |                                    | 16 MHz ( | Oscillator | Variable Oscillator     |                         |       |

|---------------------|------------------------------------|----------|------------|-------------------------|-------------------------|-------|

| Symbol              | Parameter                          | Min      | Мах        | Min                     | Мах                     | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency               |          |            | 0                       | 16                      | MHz   |

| t <sub>LHLL</sub>   | ALE Pulse Width                    | 85       |            | 2t <sub>CLCL</sub> -40  |                         | ns    |

| t <sub>AVLL</sub>   | Address Valid to ALE Low           | 22       |            | t <sub>CLCL</sub> -40   |                         | ns    |

| t <sub>LLAX</sub>   | Address Hold After ALE Low         | 32       |            | t <sub>CLCL</sub> -30   |                         | ns    |

| t <sub>LLIV</sub>   | ALE Low to Valid Instruction In    |          | 150        |                         | 4t <sub>CLCL</sub> -100 | ns    |

| t <sub>LLPL</sub>   | ALE Low to PSEN Low                | 32       |            | t <sub>CLCL</sub> -30   |                         | ns    |

| t <sub>PLPH</sub>   | PSEN Pulse Width                   | 142      |            | 3t <sub>CLCL</sub> -45  |                         | ns    |

| t <sub>PLIV</sub>   | PSEN Low to Valid Instruction In   |          | 82         |                         | 3t <sub>CLCL</sub> -105 | ns    |

| t <sub>PXIX</sub>   | Input Instruction Hold After PSEN  | 0        |            | 0                       |                         | ns    |

| t <sub>PXIZ</sub>   | Input Instruction Float After PSEN |          | 37         |                         | t <sub>CLCL</sub> -25   | ns    |

| t <sub>PXAV</sub>   | PSEN to Address Valid              | 75       |            | t <sub>CLCL</sub> -8    |                         | ns    |

| t <sub>AVIV</sub>   | Address to Valid Instruction In    |          | 207        |                         | 5t <sub>CLCL</sub> -105 | ns    |

| t <sub>PLAZ</sub>   | PSEN Low to Address Float          |          | 10         |                         | 10                      | ns    |

| t <sub>RLRH</sub>   | RD Pulse Width                     | 275      |            | 6t <sub>CLCL</sub> -100 |                         | ns    |

| t <sub>wLWH</sub>   | WR Pulse Width                     | 275      |            | 6t <sub>CLCL</sub> -100 |                         | ns    |

| t <sub>RLDV</sub>   | RD Low to Valid Data In            |          | 147        |                         | 5t <sub>CLCL</sub> -165 | ns    |

| t <sub>RHDX</sub>   | Data Hold After RD                 | 0        |            | 0                       |                         | ns    |

| t <sub>RHDZ</sub>   | Data Float After RD                |          | 65         |                         | 2t <sub>CLCL</sub> -60  | ns    |

| t <sub>LLDV</sub>   | ALE Low to Valid Data In           |          | 350        |                         | 8t <sub>CLCL</sub> -150 | ns    |

| t <sub>AVDV</sub>   | Address to Valid Data In           |          | 397        |                         | 9t <sub>CLCL</sub> -165 | ns    |

| t <sub>LLWL</sub>   | ALE Low to RD or WR Low            | 137      | 239        | 3t <sub>CLCL</sub> -50  | 3t <sub>CLCL</sub> +50  | ns    |

| t <sub>AVWL</sub>   | Address to RD or WR Low            | 122      |            | 4t <sub>CLCL</sub> -130 |                         | ns    |

| t <sub>QVWX</sub>   | Data Valid to WR Transition        | 13       |            | t <sub>CLCL</sub> -50   |                         | ns    |

| t <sub>QVWH</sub>   | Data Valid to WR High              | 287      |            | 7t <sub>CLCL</sub> -150 |                         | ns    |

| t <sub>wHQX</sub>   | Data Hold After WR                 | 13       |            | t <sub>CLCL</sub> -50   |                         | ns    |

| t <sub>RLAZ</sub>   | RD Low to Address Float            |          | 0          |                         | 0                       | ns    |

| t <sub>WHLH</sub>   | RD or WR High to ALE High          | 23       | 103        | t <sub>CLCL</sub> -40   | t <sub>CLCL</sub> +40   | ns    |

# 24. External Program Memory Read Cycle

# 25. External Data Memory Read Cycle

AT89LS51

# 26. External Data Memory Write Cycle

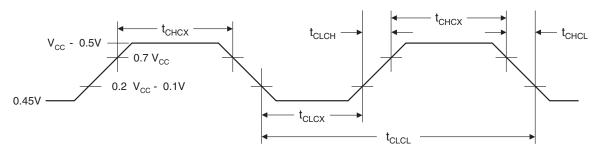

# 27. External Clock Drive Waveforms

# 28. External Clock Drive

| Symbol              | Parameter            | Min  | Мах | Units |

|---------------------|----------------------|------|-----|-------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0    | 16  | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 62.5 |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 20   |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 20   |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |      | 20  | ns    |

| t <sub>CHCL</sub>   | Fall Time            |      | 20  | ns    |

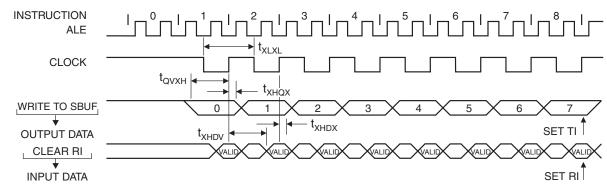

# 29. Serial Port Timing: Shift Register Mode Test Conditions

The values in this table are valid for  $V_{CC}$  = 2.7V to 4.0V and Load Capacitance = 80 pF.

|                   |                                          | 12 MI | Iz Osc | Variable Oscillator      |                          |       |

|-------------------|------------------------------------------|-------|--------|--------------------------|--------------------------|-------|

| Symbol            | Parameter                                | Min   | Мах    | Min                      | Мах                      | Units |

| t <sub>XLXL</sub> | Serial Port Clock Cycle Time             | 1.0   |        | 12t <sub>CLCL</sub>      |                          | μs    |

| t <sub>QVXH</sub> | Output Data Setup to Clock Rising Edge   | 700   |        | 10t <sub>CLCL</sub> -133 |                          | ns    |

| t <sub>XHQX</sub> | Output Data Hold After Clock Rising Edge | 50    |        | 2t <sub>CLCL</sub> -80   |                          | ns    |

| t <sub>XHDX</sub> | Input Data Hold After Clock Rising Edge  | 0     |        | 0                        |                          | ns    |

| t <sub>XHDV</sub> | Clock Rising Edge to Input Data Valid    |       | 700    |                          | 10t <sub>CLCL</sub> -133 | ns    |

# 30. Shift Register Mode Timing Waveforms

# 31. AC Testing Input/Output Waveforms<sup>(1)</sup>

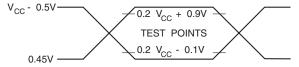

Note: 1. AC Inputs during testing are driven at V<sub>CC</sub> - 0.5V for a logic 1 and 0.45V for a logic 0. Timing measurements are made at V<sub>IH</sub> min. for a logic 1 and V<sub>IL</sub> max. for a logic 0.

# 32. Float Waveforms<sup>(1)</sup>

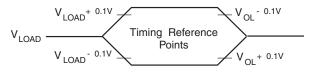

Note: 1. For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs. A port pin begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.

# 26 AT89LS51

# 33. Ordering Information

# 33.1 Standard Package

| Speed | Power        |               |         |                 |

|-------|--------------|---------------|---------|-----------------|

| (MHz) | Supply       | Ordering Code | Package | Operation Range |

|       |              | AT89LS51-16AC | 44A     |                 |

|       |              | AT89LS51-16JC | 44J     | Commercial      |

|       |              | AT89LS51-16PC | 40P6    | (0°C to 70°C)   |

| 16    |              | AT89LS51-16SC | 42PS6   |                 |

| 10    | 2.7V to 4.0V | AT89LS51-16AI | 44A     |                 |

|       |              | AT89LS51-16JI | 44J     | Industrial      |

|       |              | AT89LS51-16PI | 40P6    | (-40°C to 85°C) |

|       |              | AT89LS51-16SI | 42PS6   |                 |

# 33.2 Green Package Option (Pb/Halide-free)

| Speed<br>(MHz) | Power<br>Supply | Ordering Code | Package | Operation Range |

|----------------|-----------------|---------------|---------|-----------------|

|                |                 | AT89LS51-16AU | 44A     | Industrial      |

| 16             | 2.7V to 4.0V    | AT89LS51-16JU | 44J     |                 |

|                |                 | AT89LS51-16PU | 40P6    | (-40°C to 85°C) |

|                                                   | Package Type                                            |  |  |  |  |

|---------------------------------------------------|---------------------------------------------------------|--|--|--|--|

| 44 <b>A</b>                                       | 44-lead, Thin Plastic Gull Wing Quad Flatpack (TQFP)    |  |  |  |  |

| 44J 44-lead, Plastic J-leaded Chip Carrier (PLCC) |                                                         |  |  |  |  |

| 40P6                                              | 40-pin, 0.600" Wide, Plastic Dual Inline Package (PDIP) |  |  |  |  |

| 42PS6                                             | 42-pin, 0.600" Wide, Plastic Dual Inline Package (PDIP) |  |  |  |  |

# 34. Packaging Information

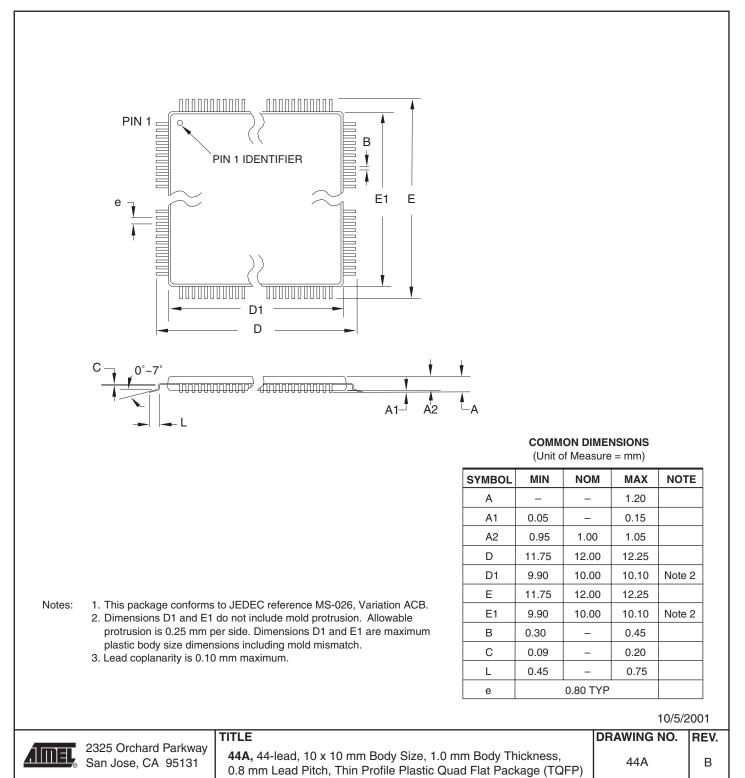

# 34.1 44A – TQFP

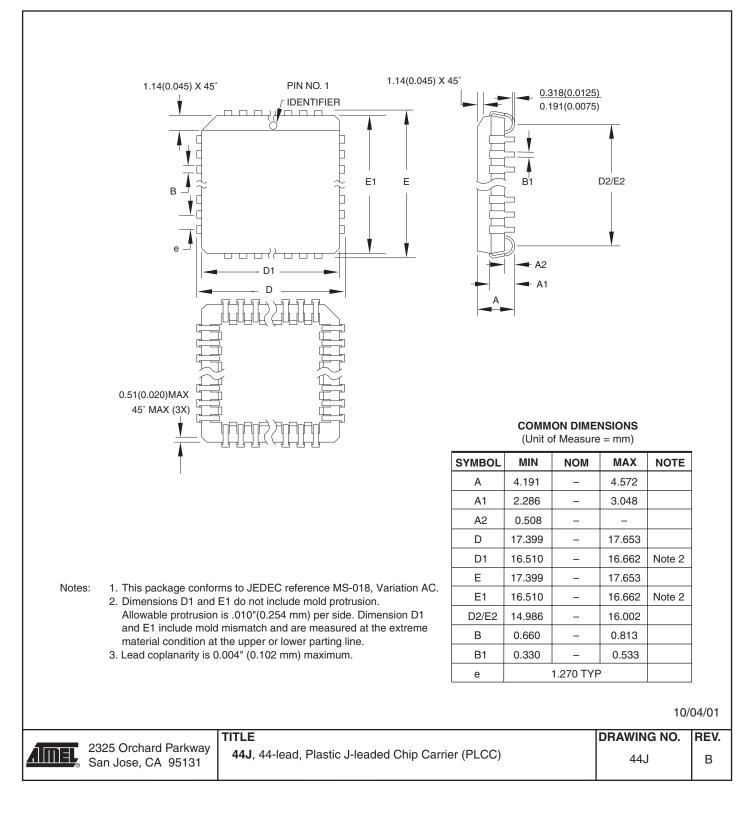

# 34.2 44J – PLCC

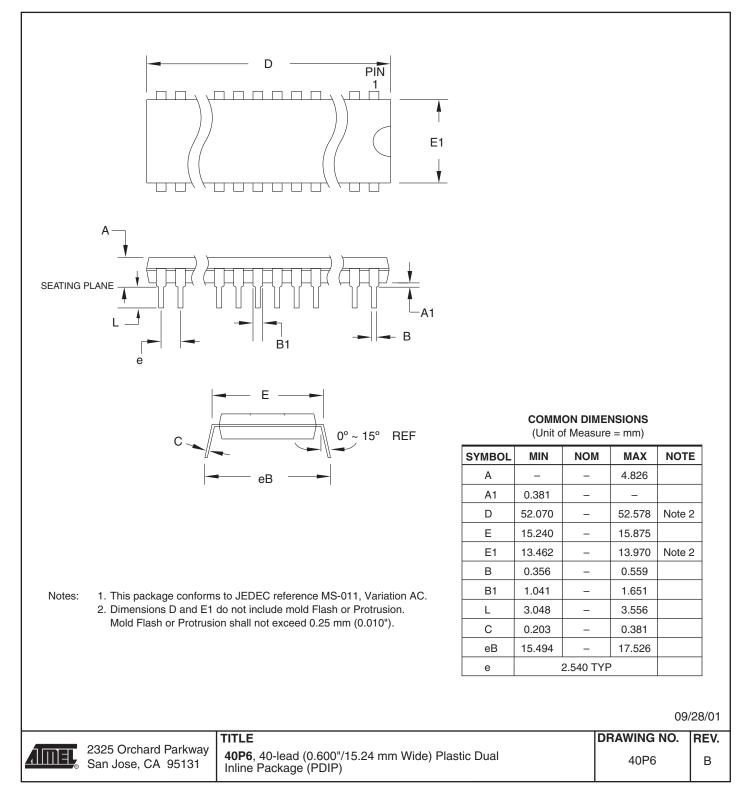

#### 34.3 40P6 - PDIP

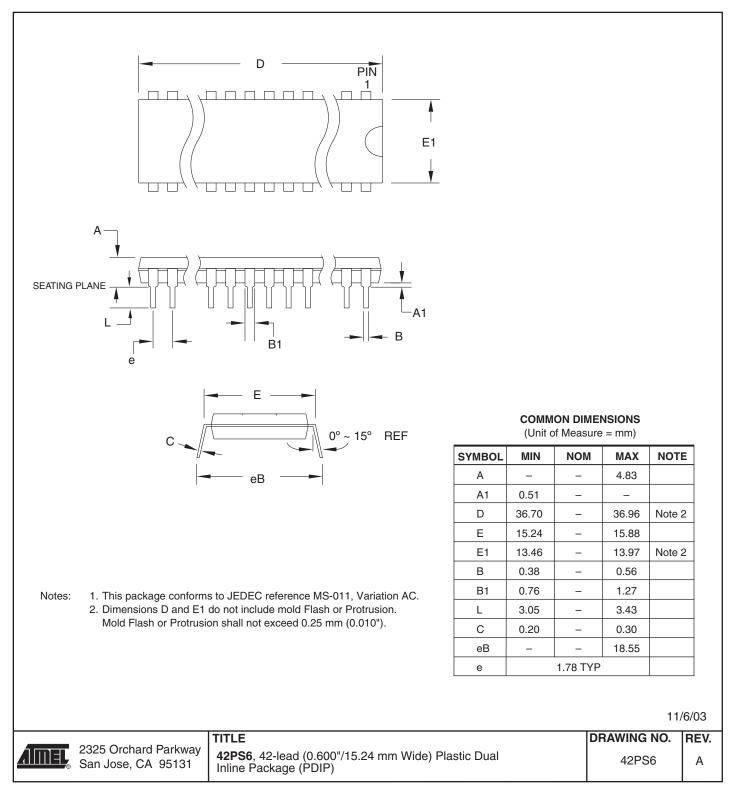

# 34.4 42PS6 - PDIP

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

Memory 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2005. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others, are registered trademarks, and Everywhere You Are<sup>SM</sup> and others are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.