# **Dual Operational Transconductance Amplifier**

The AU5517 and NE5517 contain two current-controlled transconductance amplifiers, each with a differential input and push-pull output. The AU5517/NE5517 offers significant design and performance advantages over similar devices for all types of programmable gain applications. Circuit performance is enhanced through the use of linearizing diodes at the inputs which enable a 10 dB signal-to-noise improvement referenced to 0.5% THD. The AU5517/NE5517 is suited for a wide variety of industrial and consumer applications.

Constant impedance of the buffers on the chip allow general use of the AU5517/NE5517. These buffers are made of Darlington transistors and a biasing network that virtually eliminate the change of offset voltage due to a burst in the bias current  $I_{ABC}$ , hence eliminating the audible noise that could otherwise be heard in high quality audio applications.

#### **Features**

- Constant Impedance Buffers

- ΔV<sub>BE</sub> of Buffer is Constant with Amplifier I<sub>BIAS</sub> Change

- Excellent Matching Between Amplifiers

- Linearizing Diodes

- High Output Signal-to-Noise Ratio

- Pb-Free Packages are Available\*

### **Applications**

- Multiplexers

- Timers

- Electronic Music Synthesizers

- Dolby® HX Systems

- Current-Controlled Amplifiers, Filters

- Current-Controlled Oscillators, Impedances

#### ON Semiconductor®

http://onsemi.com

MARKING DIAGRAMS

xx = AU or NE yy = AN or N

A = Assembly Location

WL = Wafer Lot

YY, Y = Year

WW = Work Week

G = Pb-Free Package

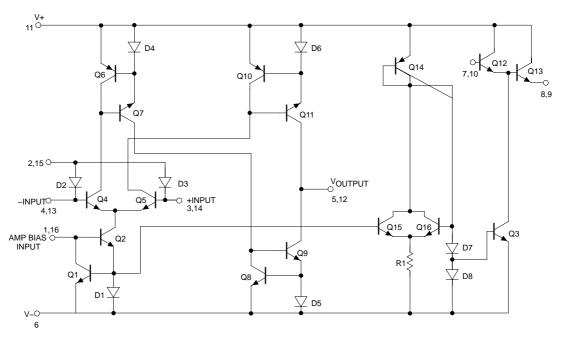

#### PIN CONNECTIONS

####

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

For additional information on our Pb–Free strategy and soldering details, please cownload the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### PIN DESCRIPTION

| Pin No. | Symbol                | Description            |

|---------|-----------------------|------------------------|

| 1       | I <sub>ABCa</sub>     | Amplifier Bias Input A |

| 2       | Da                    | Diode Bias A           |

| 3       | +IN <sub>a</sub>      | Non-inverted Input A   |

| 4       | -IN <sub>a</sub>      | Inverted Input A       |

| 5       | VOa                   | Output A               |

| 6       | V–                    | Negative Supply        |

| 7       | IN <sub>BUFFERa</sub> | Buffer Input A         |

| 8       | VO <sub>BUFFERa</sub> | Buffer Output A        |

| 9       | VO <sub>BUFFERb</sub> | Buffer Output B        |

| 10      | IN <sub>BUFFERb</sub> | Buffer Input B         |

| 11      | V+                    | Positive Supply        |

| 12      | VO <sub>b</sub>       | Output B               |

| 13      | -IN <sub>b</sub>      | Inverted Input B       |

| 14      | +IN <sub>b</sub>      | Non-inverted Input B   |

| 15      | D <sub>b</sub>        | Diode Bias B           |

| 16      | I <sub>ABCb</sub>     | Amplifier Bias Input B |

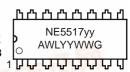

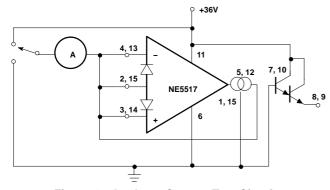

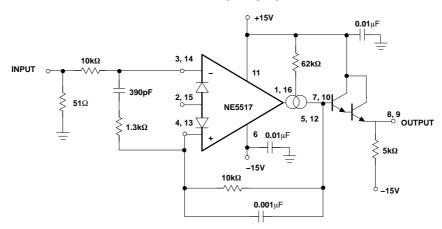

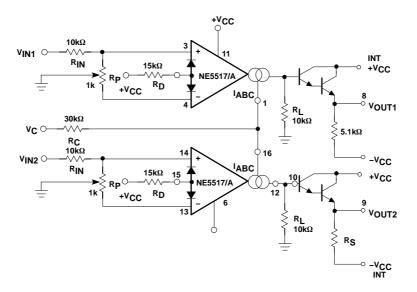

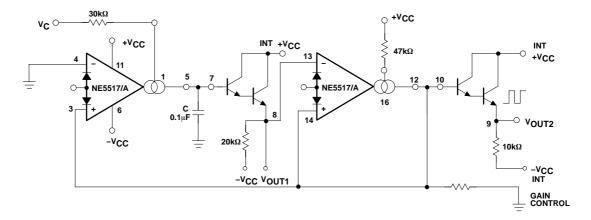

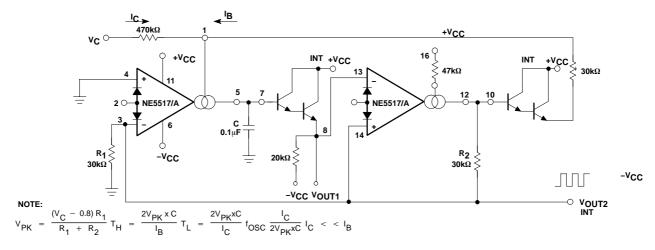

Figure 1. Circuit Schematic

NOTE: V+ of output buffers and amplifiers are internally connected.

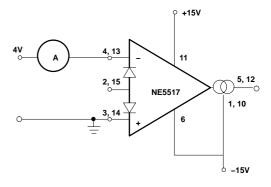

Figure 2. Connection Diagram

#### **MAXIMUM RATINGS**

| Rating                                                                                                    | Symbol           | Value                               | Unit |

|-----------------------------------------------------------------------------------------------------------|------------------|-------------------------------------|------|

| Supply Voltage (Note 1)                                                                                   | V <sub>S</sub>   | 44 V <sub>DC</sub> or ±22           | V    |

| Power Dissipation, T <sub>amb</sub> = 25 °C (Still Air) (Note 2)<br>NE5517N, NE5517AN<br>NE5517D, AU5517D | P <sub>D</sub>   | 1500<br>1125                        | mW   |

| Thermal Resistance, Junction–to–Ambient D Package N Package                                               | $R_{	heta JA}$   | 140<br>94                           | °C/W |

| Differential Input Voltage                                                                                | V <sub>IN</sub>  | ±5.0                                | V    |

| Diode Bias Current                                                                                        | I <sub>D</sub>   | 2.0                                 | mA   |

| Amplifier Bias Current                                                                                    | I <sub>ABC</sub> | 2.0                                 | mA   |

| Output Short-Circuit Duration                                                                             | I <sub>sc</sub>  | Indefinite                          |      |

| Buffer Output Current (Note 3)                                                                            | I <sub>ОИТ</sub> | 20                                  | mA   |

| Operating Temperature Range<br>NE5517N, NE5517AN<br>AU5517T                                               | T <sub>amb</sub> | 0 °C to +70 °C<br>-40 °C to +125 °C | °C   |

| Operating Junction Temperature                                                                            | TJ               | 150                                 | °C   |

| DC Input Voltage                                                                                          | V <sub>DC</sub>  | +V <sub>S</sub> to -V <sub>S</sub>  |      |

| Storage Temperature Range                                                                                 | T <sub>stg</sub> | -65 °C to +150 °C                   | °C   |

| Lead Soldering Temperature (10 sec max)                                                                   | T <sub>sld</sub> | 230                                 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- For selections to a supply voltage above ±22 V, contact factory.

The following derating factors should be applied above 25 °C

- - N package at 10.6 mW/°C

- D package at 7.1 mW/°C.

- 3. Buffer output current should be limited so as to not exceed package dissipation.

#### **ELECTRICAL CHARACTERISTICS** (Note 4)

|                                               |                                                                                                                                            |                      | AU5517/NE5517 |                | NE5517A    |                   |                |            |       |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|----------------|------------|-------------------|----------------|------------|-------|

| Characteristic                                | Test Conditions                                                                                                                            | Symbol               | Min           | Тур            | Max        | Min               | Тур            | Max        | Unit  |

| Input Offset Voltage                          | Overtere exeture Decree                                                                                                                    | Vos                  |               | 0.4            | 5.0        |                   | 0.4            | 2.0        | mV    |

|                                               | Overtemperature Range<br>I <sub>ABC</sub> 5.0 μA                                                                                           |                      |               | 0.3            | 5.0        |                   | 0.3            | 5.0<br>2.0 |       |

| $\Delta V_{OS}/\Delta T$                      | Avg. TC of Input Offset Voltage                                                                                                            |                      |               | 7.0            |            |                   | 7.0            |            | μV/°C |

| V <sub>OS</sub> Including Diodes              | Diode Bias Current<br>(I <sub>D</sub> ) = 500 μA                                                                                           |                      |               | 0.5            | 5          |                   | 0.5            | 2.0        | mV    |

| Input Offset Change                           | 5.0 μA ≤ I <sub>ABC</sub> ≤ 500 μA                                                                                                         | Vos                  |               | 0.1            |            |                   | 0.1            | 3.0        | mV    |

| Input Offset Current                          |                                                                                                                                            | Ios                  |               | 0.1            | 0.6        |                   | 0.1            | 0.6        | μΑ    |

| $\Delta I_{OS}/\Delta T$                      | Avg. TC of Input Offset Current                                                                                                            |                      |               | 0.001          |            |                   | 0.001          |            | μΑ/°C |

| Input Bias Current                            | Overtemperature Range                                                                                                                      | I <sub>BIAS</sub>    |               | 0.4<br>1.0     | 5.0<br>8.0 |                   | 0.4<br>1.0     | 5.0<br>7.0 | μΑ    |

| $\Delta I_{B}/\Delta T$                       | Avg. TC of Input Current                                                                                                                   |                      |               | 0.01           |            |                   | 0.01           |            | μΑ/°C |

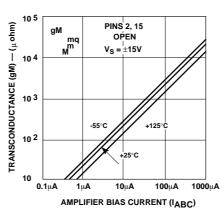

| Forward Transconductance                      | Overtemperature Range                                                                                                                      | 9м                   | 6700<br>5400  | 9600           | 13000      | 7700<br>4000      | 9600           | 12000      | μmho  |

| g <sub>M</sub> Tracking                       |                                                                                                                                            |                      |               | 0.3            |            |                   | 0.3            |            | dB    |

| Peak Output Current                           | $\begin{array}{c} R_L=0,I_{ABC}=5.0~\mu\text{A}\\ R_L=0,I_{ABC}=500~\mu\text{A}\\ R_L=0,\text{Overtemperature}\\ \text{Range} \end{array}$ | I <sub>OUT</sub>     | 350<br>300    | 5.0<br>500     | 650        | 3.0<br>350<br>300 | 5.0<br>500     | 7.0<br>650 | μΑ    |

| Peak Output Voltage<br>Positive<br>Negative   | $R_L = \infty$ , 5.0 $\mu A \le I_{ABC} \le 500 \ \mu A$<br>$R_L = \infty$ , 5.0 $\mu A \le I_{ABC} \le 500 \ \mu A$                       | V <sub>OUT</sub>     | +12<br>-12    | +14.2<br>-14.4 |            | +12<br>-12        | +14.2<br>-14.4 |            | V     |

| Supply Current                                | I <sub>ABC</sub> = 500 μA, both channels                                                                                                   | I <sub>CC</sub>      |               | 2.6            | 4.0        |                   | 2.6            | 4.0        | mA    |

| V <sub>OS</sub> Sensitivity Positive Negative | Δ V <sub>OS</sub> /Δ V+<br>Δ V <sub>OS</sub> /Δ V-                                                                                         |                      |               | 20<br>20       | 150<br>150 |                   | 20<br>20       | 150<br>150 | μV/V  |

| Common-mode Rejection Ration                  |                                                                                                                                            | CMRR                 | 80            | 110            |            | 80                | 110            |            | dB    |

| Common-mode Range                             |                                                                                                                                            |                      | ±12           | ±13.5          |            | ±12               | ±13.5          |            | V     |

| Crosstalk                                     | Referred to Input (Note 5)<br>20 Hz < f < 20 kHz                                                                                           |                      |               | 100            |            |                   | 100            |            | dB    |

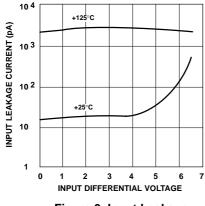

| Differential Input Current                    | $I_{ABC} = 0$ , Input = $\pm 4.0 \text{ V}$                                                                                                | I <sub>IN</sub>      |               | 0.02           | 100        |                   | 0.02           | 10         | nA    |

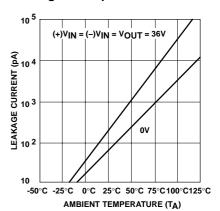

| Leakage Current                               | I <sub>ABC</sub> = 0 (Refer to Test Circuit)                                                                                               |                      |               | 0.2            | 100        |                   | 0.2            | 5.0        | nA    |

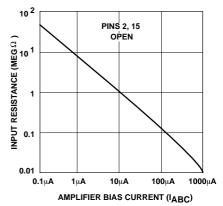

| Input Resistance                              |                                                                                                                                            | R <sub>IN</sub>      | 10            | 26             |            | 10                | 26             |            | kΩ    |

| Open-loop Bandwidth                           |                                                                                                                                            | B <sub>W</sub>       |               | 2.0            |            |                   | 2.0            |            | MHz   |

| Slew Rate Unity Gain Compensated              |                                                                                                                                            | SR                   |               | 50             |            |                   | 50             |            | V/μs  |

| Buffer Input Current                          | 5                                                                                                                                          | IN <sub>BUFFER</sub> |               | 0.4            | 5.0        |                   | 0.4            | 5.0        | μΑ    |

| Peak Buffer Output Voltage                    | 5                                                                                                                                          | VO <sub>BUFFER</sub> | 10            |                |            | 10                |                |            | V     |

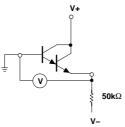

| $\Delta V_{BE}$ of Buffer                     | Refer to Buffer V <sub>BE</sub> Test<br>Circuit (Note 6)                                                                                   |                      |               | 0.5            | 5.0        |                   | 0.5            | 5.0        | mV    |

These specifications apply for V<sub>S</sub> = ±15 V, T<sub>amb</sub> = 25°C, amplifier bias current (I<sub>ABC</sub>) = 500 μA, Pins 2 and 15 open unless otherwise specified. The inputs to the buffers are grounded and outputs are open.

These specifications apply for V<sub>S</sub> = ±15 V, I<sub>ABC</sub> = 500 μA, R<sub>OUT</sub> = 5.0 kΩ connected from the buffer output to -V<sub>S</sub> and the input of the buffer is connected to the transconductance amplifier output.

V<sub>S</sub> = ±15, R<sub>OUT</sub> = 5.0 kΩ connected from Buffer output to -V<sub>S</sub> and 5.0 μA ≤ I<sub>ABC</sub> ≤ 500 μA.

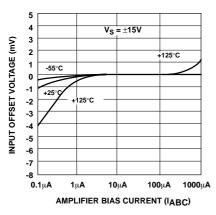

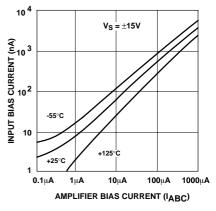

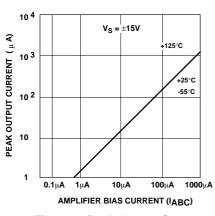

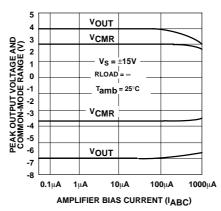

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

10 3 V<sub>S</sub> = ±15V V<sub>S</sub> = ±15V V<sub>S</sub> = ±15V 10 10 2 -55°C +125°C +125°C +125°C AMPLIFIER BIAS CURRENT (I<sub>ABC</sub>)

Figure 3. Input Offset Voltage

Figure 4. Input Bias Current

Figure 5. Input Bias Current

Figure 6. Peak Output Current

Figure 7. Peak Output Voltage and Common-Mode Range

Figure 8. Leakage Current

Figure 9. Input Leakage

Figure 10. Transconductance

Figure 11. Input Resistance

#### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

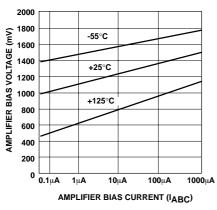

Figure 12. Amplifier Bias Voltage vs. Amplifier Bias Current

Figure 13. Input and Output Capacitance

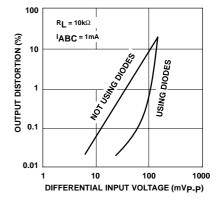

Figure 14. Distortion vs. Differential Input Voltage

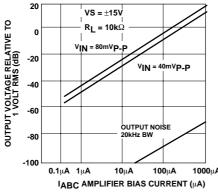

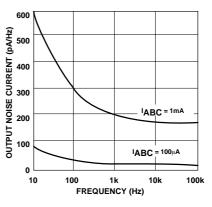

Figure 16. Noise vs. Frequency

Figure 17. Leakage Current Test Circuit

Figure 18. Differential Input Current Test Circuit

Figure 19. Buffer  $V_{\text{BE}}$  Test Circuit

#### **APPLICATIONS**

Figure 20. Unity Gain Follower

#### **CIRCUIT DESCRIPTION**

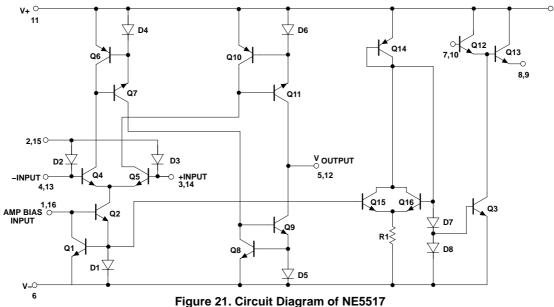

The circuit schematic diagram of one-half of the AU5517/NE5517, a dual operational transconductance amplifier with linearizing diodes and impedance buffers, is shown in Figure 21.

#### **Transconductance Amplifier**

The transistor pair,  $Q_4$  and  $Q_5$ , forms a transconductance stage. The ratio of their collector currents (I<sub>4</sub> and I<sub>5</sub>, respectively) is defined by the differential input voltage, V<sub>IN</sub>, which is shown in Equation 1.

$$V_{IN} = \frac{KT}{q} \ln \frac{I_5}{I_4}$$

(eq. 1)

Where V<sub>IN</sub> is the difference of the two input voltages  $KT \cong 26 \text{ mV}$  at room temperature (300°k).

Transistors  $Q_1,\,Q_2$  and diode  $D_1$  form a current mirror which focuses the sum of current I4 and I5 to be equal to amplifier bias current IB:

$$I_4 + I_5 = I_B \tag{eq. 2}$$

If V<sub>IN</sub> is small, the ratio of I<sub>5</sub> and I<sub>4</sub> will approach unity and the Taylor series of In function can be approximated as

$$\begin{split} \frac{\text{KT}}{\text{q}} & \text{ In } \frac{I_5}{I_4} \approx \frac{\text{KT}}{\text{q}} \frac{I_5 - I_4}{I_4} & \text{ (eq. 3)} \\ & \text{and } I_4 \cong I_5 \cong I_B \\ \frac{\text{KT}}{\text{q}} & \text{In } \frac{I_5}{I_4} \approx \frac{\text{KT}}{\text{q}} \frac{I_5 - I_4}{1/2I_B} = \frac{2\text{KT}}{\text{q}} \frac{I_5 - I_4}{I_B} = V_{\text{IN}} & \text{ (eq. 4)} \\ & I_5 - I_4 = V_{\text{IN}} \frac{\left(I_B^{\text{q}}\right)}{2\text{KT}} \end{split}$$

The remaining transistors ( $Q_6$  to  $Q_{11}$ ) and diodes ( $D_4$  to  $D_6$ ) form three current mirrors that produce an output current equal to I<sub>5</sub> minus I<sub>4</sub>. Thus:

$$V_{IN}\left(I_{B}\frac{q}{2KT}\right) = I_{O}$$

(eq. 5)

The term  $\frac{(I_B^q)}{2KT}$  is then the transconductance of the amplifier and is proportional to I<sub>B</sub>.

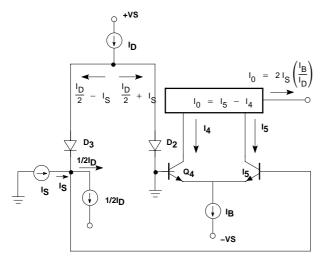

#### **Linearizing Diodes**

For  $V_{IN}$  greater than a few millivolts, Equation 3 becomes invalid and the transconductance increases non-linearly. Figure 22 shows how the internal diodes can linearize the transfer function of the operational amplifier. Assume  $D_2$  and  $D_3$  are biased with current sources and the input signal current is  $I_S.$  Since  $I_4 + I_5 = I_B$  and  $I_5 - I_4 = I_0,$  that is:  $I_4 = (I_B - I_0), \, I_5 = (I_B + I_0)$

Figure 22. Linearizing Diode

For the diodes and the input transistors that have identical geometries and are subject to similar voltages and temperatures, the following equation is true:

$$\frac{T}{q} \ln \frac{\frac{I_D}{2} + I_S}{\frac{I_D}{2} - I_S} = \frac{KT}{q} \ln \frac{1/2(I_B + I_O)}{1/2(I_B - I_O)}$$

(eq. 6)

$$I_O = I_S \frac{2IB}{I_D} \text{ for } |I_S| < \frac{I_D}{2}$$

The only limitation is that the signal current should not exceed  $I_{\text{D}}$ .

#### Impedance Buffer

The upper limit of transconductance is defined by the maximum value of  $I_B$  (2.0 mA). The lowest value of  $I_B$  for which the amplifier will function therefore determines the overall dynamic range. At low values of  $I_B$ , a buffer with very low input bias current is desired. A Darlington amplifier with constant-current source ( $Q_{14}$ ,  $Q_{15}$ ,  $Q_{16}$ ,  $D_7$ ,  $D_8$ , and  $R_1$ ) suits the need.

#### **APPLICATIONS**

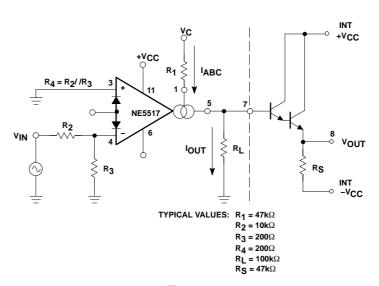

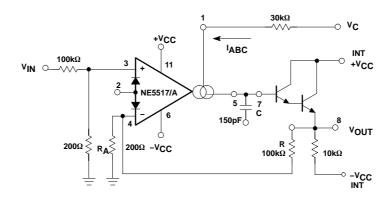

#### **Voltage-Controlled Amplifier**

In Figure 23, the voltage divider  $R_2$ ,  $R_3$  divides the input-voltage into small values (mV range) so the amplifier operates in a linear manner.

It is:

$$\begin{split} I_{OUT} &= -V_{IN} \cdot \frac{R_3}{R_2 + R_3} \cdot g_M; \\ V_{OUT} &= I_{OUT} \cdot R_L; \\ A &= \frac{V_{OUT}}{V_{IN}} = \frac{R_3}{R_2 + R_3} \cdot g_M \cdot R_L \\ &\qquad \qquad (3) \ g_M = 19.2 \ I_{ABC} \\ (g_M \ in \ \mu mhos \ for \ I_{ABC} \ in \ mA) \end{split}$$

Since  $g_M$  is directly proportional to  $I_{ABC}$ , the amplification is controlled by the voltage  $V_C$  in a simple way.

When  $V_C$  is taken relative to  $-V_{CC}$  the following formula is valid:

$$I_{ABC} = \frac{(V_C - 1.2V)}{R_1}$$

The 1.2~V is the voltage across two base-emitter baths in the current mirrors. This circuit is the base for many applications of the AU5517/NE5517.

Figure 23.

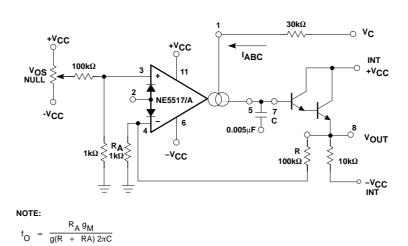

#### **Stereo Amplifier With Gain Control**

Figure 24 shows a stereo amplifier with variable gain via a control input. Excellent tracking of typical 0.3 dB is easy to achieve. With the potentiometer,  $R_{\rm P}$ , the offset can be adjusted. For AC-coupled amplifiers, the potentiometer may be replaced with two 510  $\Omega$  resistors.

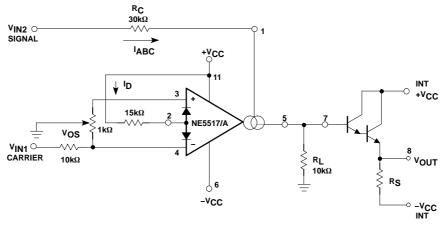

#### **Modulators**

Because the transconductance of an OTA (Operational Transconductance Amplifier) is directly proportional to  $I_{ABC}$ , the amplification of a signal can be controlled easily. The output current is the product from transconductance×input voltage. The circuit is effective up to approximately 200 kHz. Modulation of 99% is easy to achieve.

Figure 24. Gain-Controlled Stereo Amplifier

Figure 25. Amplitude Modulator

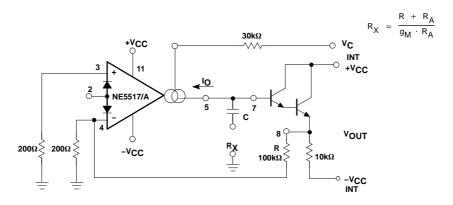

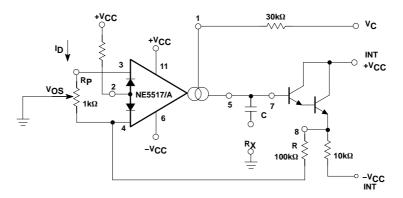

#### **Voltage-Controlled Resistor (VCR)**

Because an OTA is capable of producing an output current proportional to the input voltage, a voltage variable resistor can be made. Figure 26 shows how this is done. A voltage presented at the  $R_X$  terminals forces a voltage at the input. This voltage is multiplied by  $g_M$  and thereby forces a current through the  $R_X$  terminals:

$$R_x = \frac{R + R_A}{g_M + R_A}$$

where  $g_M$  is approximately 19.21  $\mu MHOs$  at room temperature. Figure 27 shows a Voltage Controlled Resistor using linearizing diodes. This improves the noise performance of the resistor.

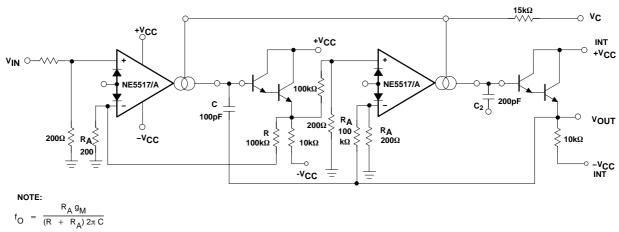

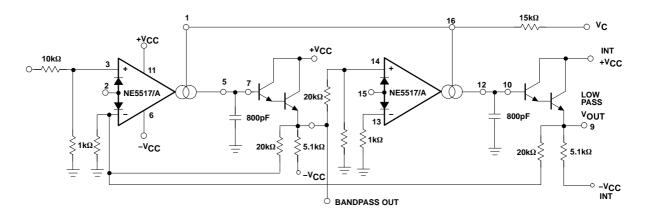

#### **Voltage-Controlled Filters**

Figure 28 shows a Voltage Controlled Low-Pass Filter. The circuit is a unity gain buffer until  $X_C/g_M$  is equal to  $R/R_A$ . Then, the frequency response rolls off at a 6dB per octave with the -3 dB point being defined by the given equations. Operating in the same manner, a Voltage Controlled High-Pass Filter is shown in Figure 29. Higher order filters can be made using additional amplifiers as shown in Figures 30 and 31.

#### **Voltage-Controlled Oscillators**

Figure 32 shows a voltage-controlled triangle-square wave generator. With the indicated values a range from 2.0 Hz to 200 kHz is possible by varying  $I_{ABC}$  from 1.0 mA to 10  $\mu$ A.

The output amplitude is determined by  $I_{OUT} \times R_{OUT}$ .

Please notice the differential input voltage is not allowed to be above 5.0 V.

With a slight modification of this circuit you can get the sawtooth pulse generator, as shown in Figure 33.

#### **APPLICATION HINTS**

To hold the transconductance  $g_M$  within the linear range,  $I_{ABC}$  should be chosen not greater than 1.0 mA. The current mirror ratio should be as accurate as possible over the entire current range. A current mirror with only two transistors is not recommended. A suitable current mirror can be built with a PNP transistor array which causes excellent matching and thermal coupling among the transistors. The output current range of the DAC normally reaches from 0 to -2.0 mA. In this application, however, the current range is set through  $R_{REF}$  (10 k $\Omega$ ) to 0 to -1.0 mA.

$$I_{DACMAX} = 2 \cdot \frac{V_{REF}}{R_{REF}} = 2 \cdot \frac{5V}{10k\Omega} = 1mA$$

Figure 26. VCR

Figure 27. VCR with Linearizing Diodes

NOTE:

$$f_O = \frac{R_A g_M}{g(R + RA) 2\pi C}$$

Figure 28. Voltage-Controlled Low-Pass Filter

Figure 29. Voltage-Controlled High-Pass Filter

Figure 30. Butterworth Filter – 2nd Order

Figure 31. State Variable Filter

Figure 32. Triangle-Square Wave Generator (VCO)

Figure 33. Sawtooth Pulse VCO

#### **ORDERING INFORMATION**

| Device     | Temperature Range | Package              | Shipping <sup>†</sup> |  |

|------------|-------------------|----------------------|-----------------------|--|

| AU5517DR2  |                   | SOIC-16              |                       |  |

| AU5517DR2G | -40 to +125 °C    | SOIC-16<br>(Pb-Free) | 2500 Tape & Reel      |  |

| NE5517D    | SOIC-16           |                      |                       |  |

| NE5517DG   |                   | SOIC-16<br>(Pb-Free) | 48 Units/Rail         |  |

| NE5517DR2  | <b>-</b>          | SOIC-16              |                       |  |

| NE5517DR2G |                   | SOIC-16<br>(Pb-Free) | 2500 Tape & Reel      |  |

| NE5517N    | 0 to +70 °C       | PDIP-16              |                       |  |

| NE5517NG   |                   | PDIP-16<br>(Pb-Free) |                       |  |

| NE5517AN   |                   | PDIP-16              | 25 Units/Rail         |  |

| NE5517ANG  |                   | PDIP-16<br>(Pb-Free) | 7                     |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### PACKAGE DIMENSIONS

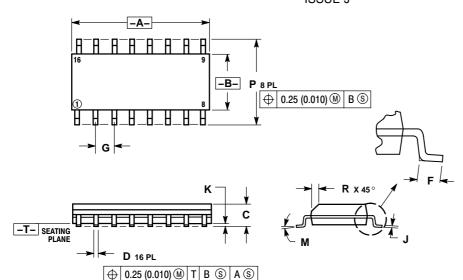

SOIC-16 CASE 751B-05 **ISSUE J**

#### NOTES

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982

- CONTROLLING DIMENSION: MILLIMETER.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR DIMENSION D DOES NOT INCLODE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INCHES    |       |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 9.80   | 10.00  | 0.386     | 0.393 |  |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |  |

| С   | 1.35   | 1.75   | 0.054     | 0.068 |  |

| D   | 0.35   | 0.49   | 0.014     | 0.019 |  |

| F   | 0.40   | 1.25   | 0.016     | 0.049 |  |

| G   | 1.27   | BSC    | 0.050 BSC |       |  |

| J   | 0.19   | 0.25   | 0.008     | 0.009 |  |

| K   | 0.10   | 0.25   | 0.004     | 0.009 |  |

| М   | 0°     | 7°     | 0°        | 7°    |  |

| P   | 5.80   | 6.20   | 0.229     | 0.244 |  |

| R   | 0.25   | 0.50   | 0.010     | 0.019 |  |

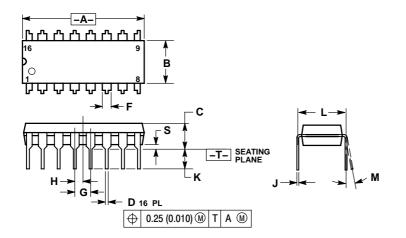

#### PDIP-16 CASE 648-08 **ISSUE T**

#### NOTES

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: INCH.

DIMENSION L TO CENTER OF LEADS

WHEN FORMED PARALLEL.

- DIMENSION B DOES NOT INCLUDE MOLD FLASH

- ROUNDED CORNERS OPTIONAL.

|     | INC   | HES   | MILLIMETERS |       |  |

|-----|-------|-------|-------------|-------|--|

| DIM | MIN   | MAX   | MIN         | MAX   |  |

| Α   | 0.740 | 0.770 | 18.80       | 19.55 |  |

| В   | 0.250 | 0.270 | 6.35        | 6.85  |  |

| С   | 0.145 | 0.175 | 3.69        | 4.44  |  |

| D   | 0.015 | 0.021 | 0.39        | 0.53  |  |

| F   | 0.040 | 0.70  | 1.02        | 1.77  |  |

| G   | 0.100 | BSC   | 2.54 BSC    |       |  |

| Н   | 0.050 | BSC   | 1.27 BSC    |       |  |

| J   | 0.008 | 0.015 | 0.21        | 0.38  |  |

| K   | 0.110 | 0.130 | 2.80        | 3.30  |  |

| L   | 0.295 | 0.305 | 7.50        | 7.74  |  |

| М   | 0°    | 10 °  | 0°          | 10 °  |  |

| S   | 0.020 | 0.040 | 0.51        | 1.01  |  |

Dolby is a registered trademark of Dolby Laboratories Inc., San Francisco, Calif.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

"Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082–1312 USA **Phone**: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Fax: 480-829-7709 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Japan: ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051 Phone: 81–3–5773–3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative