eh

## <mark>捷多邦,专业PCB打样工厂</mark>,24小时加急出货

A300

## DESCRIPTION

The Acumos A300 is a high performance analog/digital gate array. The gate array can perform analog and/or digital functions. The gate array is silicon gate construction using a doublepoly p-well process. The minimum gate channel length is 4 microns. Customization is done by single layer metal.

### FEATURES

- $\sqrt{}$  Analog & Digital sections

- $\sqrt{10}$  High breakdown voltage -- 12V

- $\sqrt{1}$  Internal gate prop delay -- less than 5ns

- $\sqrt{\text{Output sink current per transistor 6 mA}}$

- $\sqrt{\text{Op amps with gain over 70 dB}}$

- $\sqrt{}$  Matched resistors and capacitors on chip

- $\sqrt{300}$  equivalent gates in digital section

- $\sqrt{}$  Single or dual supply operation

**Analog/Digital**

**Gate Array**

A300 Analog/Digital Gate Array Chip

Chip size: 138 mils X 167 mils

### APPLICATIONS

The A300 can be configured to do many functions. Here's a list of some of them:

- A to D and D to A converter with up to 8 bits resolution

- A set of filters. For example the chip can contain two "MF10" type filters plus other functions.

- A set of comparators ... as many as 20 comparators ... Offset voltage (uncompensated) as low as 15mV .... offsets that are internally compensated (no external components)can be in the micro volt region.

- Voltage reference.

- Phase locked loops, including the loop filter.

- Peak detectors and sample and hold circuits.

- Analog multiplexer.

Besides performing a selection of any of these functions, one chip can contain the normal housekeeping jobs such as decoding, buffering, etc.

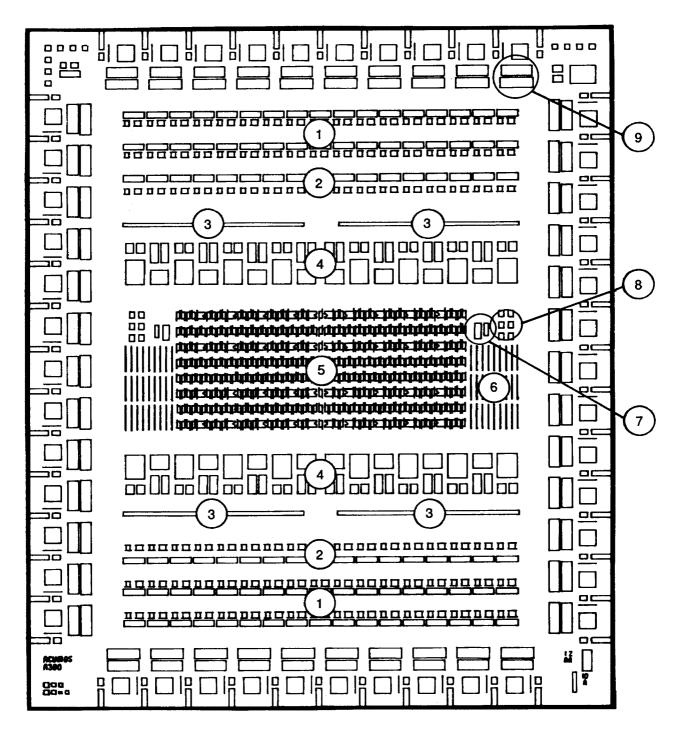

#### The array has 9 sections:

1. Digital section. This area contains 400 CMOS transistor pairs. A transistor pair consists of one p channel and one n channel device. Since it takes two pairs to make a two input NAND gate, this area has the potential of making 200 two input NAND gates. Due to interconnect congestion it is difficult to realize 200 gates -- a good estimate is 80 to 90% depending on the particular circuit.

2. Analog/digital section. This section contains 200 transistor pairs. The dimensions of the devices are the same as those in the digital section, however they are laid out such that p and n channel devices can be used separately. This allows the designer to use them either as individual transistors for analog applications or as pairs for additional digital functions. Used as pairs this gives the chip an additional 100 two input NAND gates.

3. Analog switch section. This section contains 192 minimum geometry MOS switches. These devices are particularly suited for building switched capacitor filters.

4. Analog section. This section contains 256 large transistors. This is the section that is used to make op amps, comparators, etc.

5. Capacitor section. This section contains 250 capacitor units of 0.4 pF each. Units can be paralleled to make larger values. Capacitors are constructed of poly-silicon, silicon-dioxide-poly silicon. They have a tolerance of approximately plus or minus 15%.

6. Resistor section: This contains 54 20k ohm P well resistors and have a tolerance of about 30%.

7. High resistance FET section. These devices are used to make high resistance values.

Values on these devices can become very high but due to their nature the tolerances are more than 2 to 300%.

8. **Bipolar transistor section**. This contains 12 lateral NPN transistors which can be used as low noise input devices or in a voltage reference circuit.

9. Output driver section. There are 46 driver pairs arranged around the periphery of the device. These devices can sink 6 mA at a VOL of 0.4V maximum.

| SECTION     | DEVICE    | QUANTITY | SIZE    |

|-------------|-----------|----------|---------|

| Digital     | nMOS      | 400      | 31/4    |

| Digital     | pMOS      | 400      | 39/4    |

| Digital-    | nMOS      | 100      | 31/4    |

| Analog      | pMOS      | 100      | 39/4    |

|             | nMOS      | 64       | 59/9    |

| Analog      | pMOS      | 64       | 59/9    |

| Analog      | nMOS      | 64       | 118/9   |

|             | pMOS      | 64       | 118/9   |

| Analog      | nMOS      | 96       | 4/4     |

| Switch      | pMOS      | 96       | 4/4     |

| Bipolar     | NPN       | 12       |         |

| Output      | pMOS      | 176      | 80/4    |

| Transistor  | nMOS      | 176      | 80/4    |

| Output Pads |           | 46       |         |

| Capacitor   | Poly-Poly | 250      | 0.4 pf  |

| Resistor    | P - Well  | 54       | 20 k    |

| Hi R. FET   | Pinch FET | 4        | >15 meg |

### **A300 ORGANIZATION**

- 1. Digital section

- 2. Digital/analog section

- 3. Analog/switch section

- 4. Analog section

- 5. Capacitor section

- 6. Resistor section

- 7. High resistance FET section

- 8. Bipolar transistor section

- 9. Output driver section (entire periphery)

# MAXIMUM OPERATING CONDITIONS:

|   | SYMBOL | ITEM                | RATING                   | UNITS |

|---|--------|---------------------|--------------------------|-------|

| ł | Vcc    | D.C. Supply voltage | 12 volts                 | V     |

| Î |        | Voltage on any pin  | VSS- 0.3 V to VDD+ 0.3 V | V     |

| ľ | 1      | Input current       | ± 20 mA                  | mA    |

|   | Topr   | Operating temp      | - 10 to + 85° C          | С     |

### DIGITAL CIRCUIT SECTION SPECIFICATIONS:

## D.C. CHARACTERISTICS : $V_{CC} = 5 V$ ; $T_A = 25^{\circ} C$

| SYMBOL | ITEM                                 | TEST CONDITIONS        | RATING |     |      | UNITS |

|--------|--------------------------------------|------------------------|--------|-----|------|-------|

|        |                                      |                        | MIN    | TYP | MAX  | UNITS |

| VIL    | Low level input voltage (TTL Input)  | $V_{CC} = 5 V$         |        |     | 0.8  | V     |

| VIH    | High level input voltage (TTL Input) |                        | 2.0    |     |      | V     |

| Vol    | Low level outout voltage:            |                        |        |     |      |       |

|        |                                      | @1 <sub>OL</sub> =−1µA |        |     | 0.05 | V     |

|        |                                      | @IOL = - 6 mA          |        |     | 0.4  | V     |

| Voh    | High level outout votage             |                        |        |     |      |       |

|        |                                      | @IOH = 1µA             | 4.95   |     |      | V     |

|        |                                      | @ I OH = 2 mA          | 4.0    |     |      | V     |

## A.C. CHARACTERISTICS : $V_{CC} = 5 V$ ; $T_A = 25^{\circ}C$

| SYMBOL          | ITEM                         | TEST CONDITIONS | RATING |     |     | UNITS |

|-----------------|------------------------------|-----------------|--------|-----|-----|-------|

|                 |                              |                 | MIN    | TYP | MAX | UNITS |

| fmax            | Maximum Clock Frequency      | 50% duty cycle  |        |     | 20  | MHz   |

| td              | Gate Delay for 2-input gate  |                 |        | 5   |     | ns    |

| t <sub>dz</sub> | Gate Delay for input buffer  |                 |        | 10  |     | ns    |

| tdo             | Gate Delay for output buffer |                 |        | 10  |     | ns    |

### **AVAILABLE PACKAGES**

| TYPES | NO. OF PINS                      |

|-------|----------------------------------|

| DIP   | 14, 16, 18, 20, 22,24,28, and 40 |

| PLCC  | 28 and 44                        |