**VL6524** VS6524

### VGA single-chip camera module

**Preliminary Data**

#### **Features**

- 640H x 480V active pixels

- 3.6 µm pixel size, 1/6 inch optical format

- RGB Bayer color filter array

- Integrated 10-bit ADC

- Integrated digital image processing functions, including defect correction, lens shading correction, demosaicing, sharpening, gamma correction and color space conversion

- Embedded camera controller for automatic exposure control, automatic white balance control, black level compensation, 50/60 Hz flicker cancellation and flashgun support

- Up to 30 fps progressive scan, flexible subsampling and cropping modes

- ITU-R BT.656-4 YUV (YCbCr) 4:2:2 with embedded syncs, RGB 565, RGB 444 or Bayer 10-bit output formats

- Viewlive feature allows different sizes, formats and reconstruction settings to be applied to alternate frames

- 8-bit parallel video interface, horizontal and vertical syncs, 24 MHz clock

- Two-wire serial control interface (I<sup>2</sup>C)

- On-chip PLL, 6.5 to 26 MHz clock input

- Analog power supply, from 2.4V to 3.0V

- Separate I/O power supply, 1.8V or 2.8V levels

- 3.3V tolerant I/O for power supply > 2.7V

- Integrated power management with power switch, automatic power-on reset and powersafe pins

- Low power consumption, ultra low standby

- Dual-element plastic lens, F# 2.8, ~59° DFOV (VS6524)

change without notice.

dzsc.com

### Description

The VL6524/VS6524 is a general purpose VGA resolution CMOS color digital camera featuring low size and low power consumption. This complete camera module is ready to connect to camera enabled baseband processors, back-end IC devices or PDA engines. WWW.BZSC.COM

### **Applications**

- Mobile phone

- Videophone

- Video surveillance

- Medical

- Machine Vision

- Toys

- PDA

- **Biometry**

- Bar Code Reader

- **Lighting Control**

Contents VL6524/VS6524

# **Contents**

| 1 | Ove  | Overview                                  |  |  |  |  |  |

|---|------|-------------------------------------------|--|--|--|--|--|

|   | 1.1  | Description                               |  |  |  |  |  |

| 2 | Elec | trical interface                          |  |  |  |  |  |

| 3 | Syst | em architecture10                         |  |  |  |  |  |

|   | 3.1  | Operation                                 |  |  |  |  |  |

|   |      | 3.1.1 Video pipe                          |  |  |  |  |  |

|   | 3.2  | Microprocessor functions                  |  |  |  |  |  |

| 4 | Ope  | rational modes13                          |  |  |  |  |  |

|   | Mode | e transitions                             |  |  |  |  |  |

| 5 | Cloc | k control16                               |  |  |  |  |  |

|   | 5.1  | Input clock                               |  |  |  |  |  |

|   | 5.2  | System clock division                     |  |  |  |  |  |

|   | 5.3  | Pixel clock (PCLK)                        |  |  |  |  |  |

|   | 5.4  | PCLK gating 17                            |  |  |  |  |  |

| 6 | Outp | out frame size control                    |  |  |  |  |  |

|   | 6.1  | Frame format                              |  |  |  |  |  |

|   |      | 6.1.1 Cropping module                     |  |  |  |  |  |

|   |      | 6.1.2 Subsampling module                  |  |  |  |  |  |

|   | 6.2  | Frame rate control                        |  |  |  |  |  |

|   |      | 6.2.1 Horizontal mirror and vertical flip |  |  |  |  |  |

|   | 6.3  | ViewLive Operation                        |  |  |  |  |  |

|   |      | Video pipe setup                          |  |  |  |  |  |

|   | 6.4  | Context switching                         |  |  |  |  |  |

| 7 | Outp | out data formats                          |  |  |  |  |  |

|   | 7.1  | YUV 4:2:2 data format                     |  |  |  |  |  |

|   | 7.2  | RGB and Bayer data formats                |  |  |  |  |  |

|   |      | 7.2.1 Manipulation of RGB data            |  |  |  |  |  |

VL6524/VS6524 Contents

|    |      | 7.2.2                | Dithering                                         | 25 |

|----|------|----------------------|---------------------------------------------------|----|

| 8  | Data | synchi               | ronization methods                                | 26 |

|    | 8.1  | Embe                 | dded codes                                        | 26 |

|    |      | 8.1.1                | Prevention of false synchronization codes         | 26 |

|    |      | 8.1.2                | Mode 1(ITU656 compatible)                         | 26 |

|    |      | 8.1.3                | Mode 2                                            | 28 |

|    | 8.2  | VSYN                 | C and HSYNC                                       | 29 |

|    |      | 8.2.1                | Horizontal synchronization signal (HSYNC)         | 29 |

|    |      | 8.2.2                | Vertical synchronization (VSYNC)                  | 30 |

| 9  | Gett | ing star             | rted                                              | 31 |

|    | 9.1  | Initial <sub>I</sub> | power up                                          | 31 |

|    | 9.2  | Minim                | um startup command sequence                       | 31 |

| 10 | Host | t comm               | unication - I <sup>2</sup> C control interface    | 32 |

|    | V2W  | protocol             | layer                                             | 32 |

|    |      | Protoco              | ol                                                | 32 |

|    |      | Detaile              | ed overview of the message format                 | 33 |

|    |      | Data va              | alid                                              | 34 |

|    |      | Start (S             | S) and Stop (P) conditions                        | 35 |

|    |      | Acknow               | wledge                                            | 35 |

|    |      | Index s              | space                                             | 36 |

|    |      | Types                | of messages                                       | 37 |

|    |      | Rando                | m location, single data write                     | 37 |

|    |      | Curren               | t location, single data read                      | 38 |

|    |      | Rando                | m location, single data read                      | 39 |

|    |      | •                    | e location write                                  |    |

|    |      | Multiple             | e location read stating from the current location | 40 |

| 11 | Regi | ister ma             | ap                                                | 42 |

|    |      |                      | vel control registers                             |    |

|    |      |                      | parameters [read only]                            |    |

|    |      |                      | control                                           |    |

|    |      |                      | Status [read only]                                |    |

|    |      |                      | odeControl                                        |    |

|    |      | Clock r              | manager input control                             | 45 |

|    |      |                      |                                                   |    |

|    |       | Power management control                | 45 |

|----|-------|-----------------------------------------|----|

|    |       | Frame rate control                      | 46 |

|    |       | Pipe setup bank selection               | 46 |

|    |       | Pipe setup bank0 control                | 46 |

|    |       | Pipe Setup Bank1 Control                | 48 |

|    |       | View live control                       | 49 |

|    |       | White balance control                   | 49 |

|    |       | Exposure control                        | 50 |

|    |       | Exposure status (Read only)             | 51 |

|    |       | Exposure algorithm control              | 51 |

|    |       | Flashgun control                        | 51 |

|    |       | Flicker frequency control               | 52 |

|    |       | Defect correction control               | 52 |

|    |       | Sharpening control                      | 52 |

|    |       | Fade to black damper control            | 52 |

|    |       | Dither control                          | 54 |

|    |       | Output formatter control                | 54 |

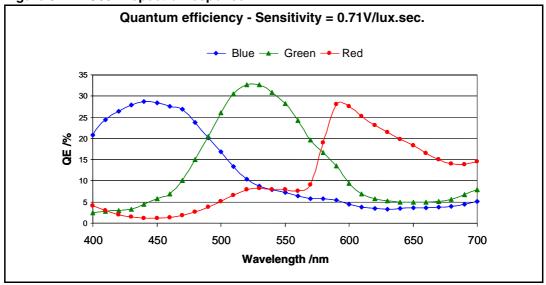

| 12 | Optio | cal specifications                      | 56 |

|    | 12.1  | Average sensitivity                     | 56 |

|    | 12.2  | Spectral response                       | 57 |

| 13 | Elect | rical characteristics                   | 58 |

|    | 13.1  | Absolute maximum ratings                | 58 |

|    | 13.2  | Operating conditions                    |    |

|    | 13.3  | DC electrical characteristics           |    |

|    |       |                                         |    |

|    | 13.4  | AC electrical characteristics           |    |

|    |       | 13.4.1 External clock                   |    |

|    |       | 13.4.2 Chip enable                      |    |

|    |       | 13.4.3 I <sup>2</sup> C slave interface |    |

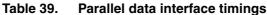

|    |       | 13.4.4 Parallel data interface timing   |    |

|    | 13.5  | ESD handling characteristics            | 63 |

| 14 | Pack  | age outline                             | 64 |

|    | 14.1  | SmOP                                    | 64 |

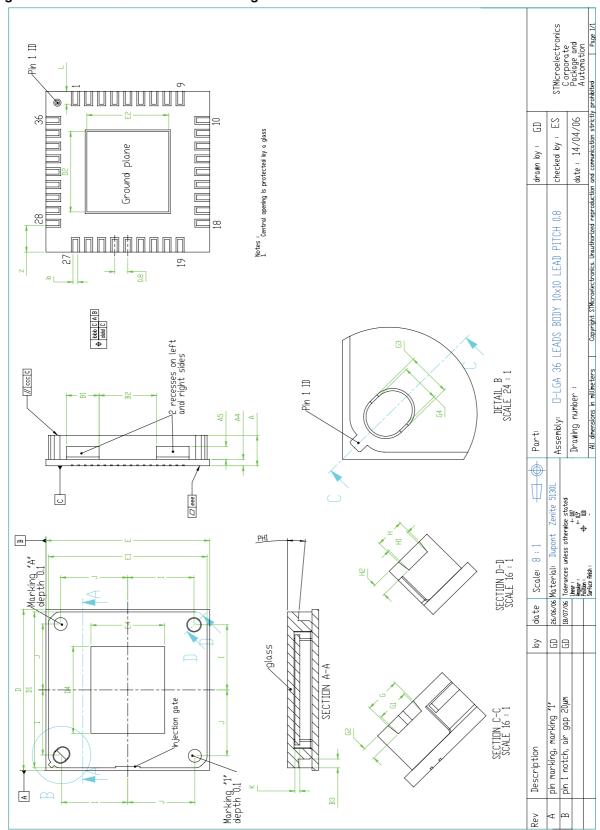

|    | 14.2  | LGA                                     | 66 |

| VL6524 | /VS6524              | Cc | ontents |

|--------|----------------------|----|---------|

| 15     | Ordering information |    | 69      |

| 16     | Revision history     |    | 69      |

List of tables VL6524/VS6524

# **List of tables**

| Table 1.  | VL6524/VS6524 signal description                              | . 9 |

|-----------|---------------------------------------------------------------|-----|

| Table 2.  | Subsampled image sizes                                        |     |

| Table 3.  | ITU656 embedded synchronization code definition (even frames) | 27  |

| Table 4.  | ITU656 embedded synchronization code definition (odd frames)  | 28  |

| Table 5.  | Mode 2 - embedded synchronization code definition             | 28  |

| Table 6.  | Data type                                                     | 42  |

| Table 7.  | Low-level control registers                                   | 44  |

| Table 8.  | Device parameters                                             | 44  |

| Table 9.  | Mode control                                                  | 44  |

| Table 10. | Mode status                                                   | 45  |

| Table 11. | RunModeControl                                                | 45  |

| Table 12. | Clock manager input control                                   | 45  |

| Table 13. | Power management control                                      | 45  |

| Table 14. | Frame rate control                                            | 46  |

| Table 15. | Pipe setup bank selection                                     | 46  |

| Table 16. | Pipe setup bank0 control                                      | 46  |

| Table 17. | Pipe setup bank1 control                                      | 48  |

| Table 18. | View live control                                             |     |

| Table 19. | White balance control                                         | 49  |

| Table 20. | Exposure control                                              | 50  |

| Table 21. | Exposure status                                               | 51  |

| Table 22. | Exposure algorithm control                                    |     |

| Table 23. | Flashgun control                                              | 51  |

| Table 24. | Flicker frequency control                                     |     |

| Table 25. | Defect correction control                                     | 52  |

| Table 26. | Sharpening control                                            | 52  |

| Table 27. | Fade to black damper control                                  | 52  |

| Table 28. | Dither control                                                |     |

| Table 29. | Output formatter control                                      |     |

| Table 30. | Optical specifications                                        | 56  |

| Table 31. | VS6524 average sensitivity                                    | 56  |

| Table 32. | Absolute maximum ratings                                      | 58  |

| Table 33. | Supply specifications                                         | 58  |

| Table 34. | DC electrical characteristics                                 | 59  |

| Table 35. | Typical current consumption                                   | 59  |

| Table 36. | External clock                                                | 60  |

| Table 37. | Serial interface voltage levels                               | 60  |

| Table 38. | Timing specification                                          | 61  |

| Table 39. | Parallel data interface timings                               |     |

| Table 40. | ESD handling characteristics                                  | 63  |

| Table 41. | LGA package mechanical data                                   | 66  |

| Table 42. | VL6524 pin assignment                                         | 69  |

| Table 43. | Order codes                                                   | 69  |

| Table 44  | Document revision history                                     | 69  |

VL6524/VS6524 List of figures

# List of figures

| Figure 1.  | VL6524/VS6524 simplified block diagram                          |      |

|------------|-----------------------------------------------------------------|------|

| Figure 2.  | State machine at power -up and user mode transitions            | . 13 |

| Figure 3.  | Power up sequence                                               |      |

| Figure 4.  | Frame output format against framerate                           | . 16 |

| Figure 5.  | VGA 30fps output frame                                          |      |

| Figure 6.  | Crop controls (Table 16: Pipe setup bank0 control)              | . 19 |

| Figure 7.  | Crop 30fps output frame                                         |      |

| Figure 9.  | ViewLive frame output format                                    |      |

| Figure 10. | Standard Y Cb Cr data order                                     |      |

| Figure 11. | Y Cb Cr data swapping options                                   | . 23 |

| Figure 12. | RGB and Bayer data formats                                      | . 24 |

| Figure 13. | ITU656 frame structure with even codes                          | . 27 |

| Figure 14. | Mode 2 frame structure (VGA example)                            | . 28 |

| Figure 15. | HSYNC timing example                                            | . 29 |

| Figure 16. | VSYNC timing example                                            | . 30 |

| Figure 17. | Write message                                                   | . 32 |

| Figure 18. | Read message                                                    | . 32 |

| Figure 19. | Detailed overview of message format                             | . 33 |

| Figure 20. | Device addresses                                                | . 34 |

| Figure 21. | SDA data valid                                                  | . 34 |

| Figure 22. | START and STOP conditions                                       | . 35 |

| Figure 23. | Data acknowledge                                                | . 35 |

| Figure 24. | Internal register index space                                   | . 36 |

| Figure 25. | Random location, single write                                   | . 37 |

| Figure 26. | Current location, single read                                   | . 38 |

| Figure 27. | Random location, single data read                               | . 39 |

| Figure 28. | Multiple location write                                         | . 39 |

| Figure 29. | Multiple location read                                          | . 40 |

| Figure 30. | Multiple location read starting from a random location          | . 41 |

| Figure 31. | VS6524 spectral response                                        | . 57 |

| Figure 32. | Voltage level specification                                     | . 61 |

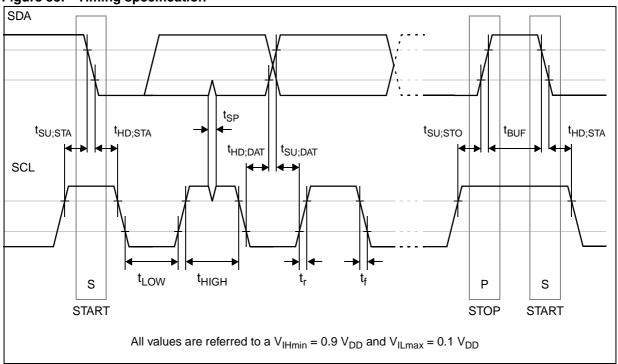

| Figure 33. | Timing specification                                            | . 62 |

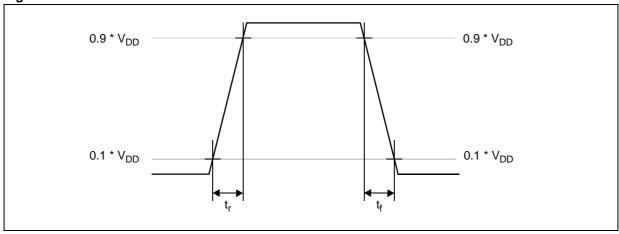

| Figure 34. | SDA/SCL rise and fall times                                     | . 62 |

| Figure 35. | Parallel data output video timing                               | . 63 |

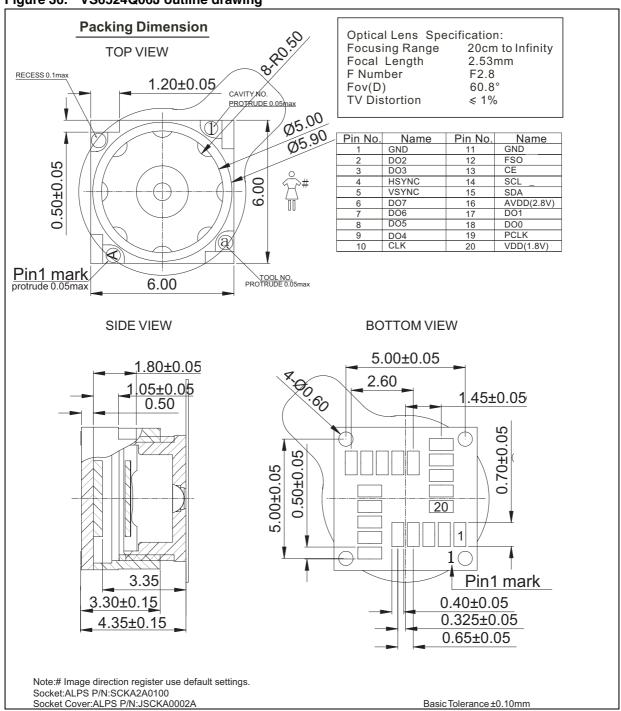

| Figure 36. | VS6524Q06J outline drawing                                      |      |

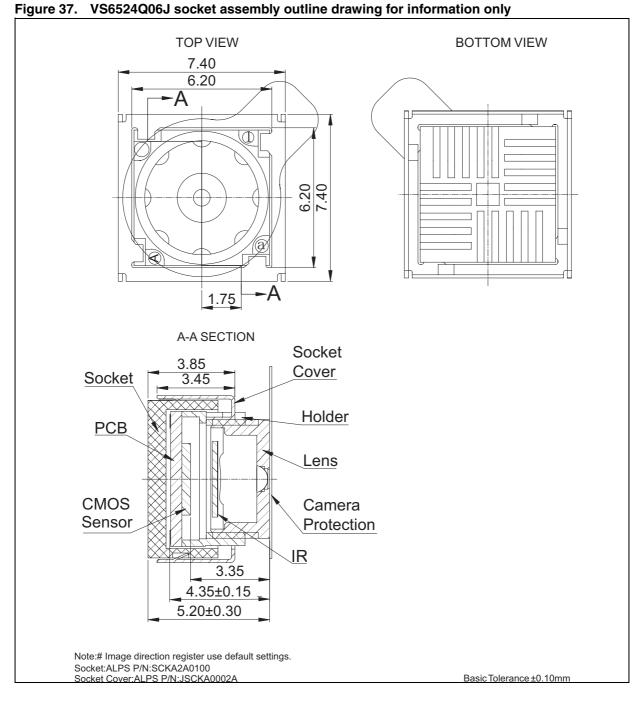

| Figure 37. | VS6524Q06J socket assembly outline drawing for information only |      |

| Figure 38  | VI 6524QOMH outline drawing                                     |      |

Overview VL6524/VS6524

### 1 Overview

### 1.1 Description

The VL6524/VS6524 is a VGA resolution CMOS imaging device designed for low power systems.

Video data is output from the VS6524 over an 8-bit parallel bus in RGB, YCbCr or bayer formats and is controlled via an I<sup>2</sup>C interface.

The VL6524/VS6524 requires an analogue power supply of between 2.4 V to 3.0 V and a digital supply of either 1.8 V or 2.8 V (dependant on interface levels required). An input clock is required in the range 6.5 MHz to 26 MHz.

The device contains an embedded video processor and delivers fully color processed images at up to 30 frames per second. The video processor integrates a wide range of image enhancement functions, designed to ensure high image quality, these include:

- Automatic exposure control

- Automatic white balance

- Lens shading compensation

- Defect correction algorithms

- Demosaic (Bayer to RGB conversion)

- Matrix compensation

- Sharpening

- Gamma correction

- Flicker cancellation

VL6524/VS6524 Electrical interface

## 2 Electrical interface

The device has 20 electrical connections as listed in *Table 1*. The physical orientation of the pins on the device is shown in *Figure 36*.

Table 1. VL6524/VS6524 signal description

| Pad socket | Pad name | I/O | Description                       |

|------------|----------|-----|-----------------------------------|

| 1          | GND      | PWR | Analogue ground                   |

| 2          | D02      | OUT | Data output D2                    |

| 3          | D03      | OUT | Data output D3                    |

| 4          | HSYNC    | OUT | Horizontal synchronization output |

| 5          | VSYNC    | OUT | Vertical synchronization output   |

| 6          | D07      | OUT | Data output D7                    |

| 7          | D06      | OUT | Data output D6                    |

| 8          | D05      | OUT | Data output D5                    |

| 9          | D04      | OUT | Data output D4                    |

| 10         | CLK      | IN  | Clock input - 6.5MHz to 26 MHz    |

| 11         | GND      | PWR | Digital ground                    |

| 12         | FSO      | OUT | Flash output                      |

| 13         | CE       | IN  | Chip enable signal active HIGH    |

| 14         | SCL      | IN  | I <sup>2</sup> C clock input      |

| 15         | SDA      | I/O | I <sup>2</sup> C data line        |

| 16         | AVDD     | PWR | Analogue supply 2.4 V to 3.0 V    |

| 17         | D01      | OUT | Data output D1                    |

| 18         | D00      | OUT | Data output D0                    |

| 19         | PCLK     | OUT | Pixel qualification clock         |

| 20         | VDD      | PWR | Digital supply 1.8 V OR 2.8 V     |

9/70

System architecture VL6524/VS6524

### 3 System architecture

The VL6524/VS6524 consists of the following main blocks:

- VGA-sized pixel array

- Video timing generator

- Video pipe

- Statistics gathering unit

- Clock generator

- Microprocessor

A simplified block diagram is shown in Figure 1.

I<sup>2</sup>C Interface ► SDA Clock CLK generator I<sup>2</sup>C SCL Reset CE Microprocessor **VREG VDD GND** Video timing **Statistics** generator Gathering ► FSO AVDD -VSYNC ► HSYNC ► PCLK **VGA** Video pipe Pixel array D[0:7] **GND**

Figure 1. VL6524/VS6524 simplified block diagram

### 3.1 Operation

A video timing generator controls a VGA-sized pixel array to produce raw images at up to 30 frames per second. The analogue pixel information is digitized and passed into the video pipe. The video pipe contains a number of different functions (explained in detail later). At the end of the video pipe data is output to the host system over an 8-bit parallel interface along with qualification signals.

VL6524/VS6524 System architecture

The whole system is controlled by an embedded microprocessor that is running firmware stored in an internal ROM. The external host communicates with this microprocessor over an I<sup>2</sup>C interface. The microprocessor does not handle the video data itself but is able to control all the functions within the video pipe. Real-time information about the video data is gathered by a statistics engine and is available to the microprocessor. The processor uses this information to perform real-time image control tasks such as automatic exposure control.

#### 3.1.1 Video pipe

The main functions contained within the VL6524/VS6524 video processing pipe are as follows.

**Gain and offset:** This function is used to apply gain and offset to data coming from the sensor array. The required gain and offset values result from the automatic exposure and white balance functions from the microprocessor.

**Anti-vignette:** This function is used to compensate for the radial roll-off in intensity caused by the lens. By default the anti-vignette setting matches the lens used in this module and does not need to be adjusted.

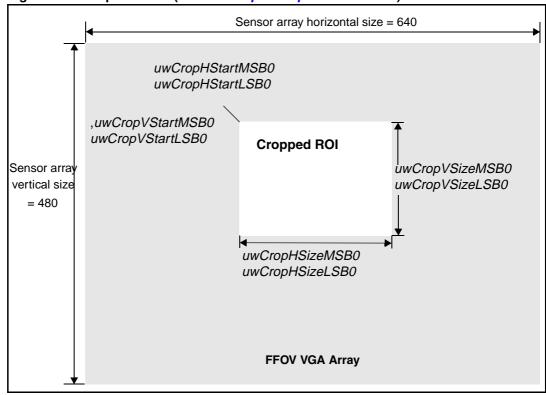

**Crop:** This function allows the user to select an arbitrary Window Of Interest (WOI) from the VGA-sized pixel array. It is fully accessible to the user.

**Defect correction:** This function runs a defect correction filter over the data in order to remove defects from the final output. This function has been optimized to attain the minimum level of defects from the system and does not need to be adjusted.

**Demosaic:** This module performs an interpolation on the Bayer data from the sensor array to produce an RGB image. It also applies an anti-alias filter.

**Subsampler:** This module allows the image to be sub-sampled in the X and Y directions by 2, 3, 4, 5 or 6.

**Matrix:** This function performs a color-space conversion from the sensor RGB data to standard RGB color space.

**Sharpening:** This module increases the high frequency content of the image in order to compensate for the low-pass filtering effects of the previous modules.

**Gamma:** This module applies a programmable gain curve to the output data. It is user adjustable.

**YUV conversion:** This module performs color space conversion from RGB to YUV. It is used to control the contrast and color saturation of the output image as well as the fade to black feature.

**Dither:** This module is used to reduce the contouring effect seen in RGB images with truncated data.

**Output formatter:** This module controls the embedded codes which are inserted into the data stream to allow the host system to synchronize with the output data. It also controls the optional HSYNC and VSYNC output signals.

System architecture VL6524/VS6524

### 3.2 Microprocessor functions

The microprocessor inside the VL6524/VS6524 performs the following tasks:

Host communication: handles the I<sup>2</sup>C communication with the host processor.

**Video pipe configuration**: configures the video pipe modules to produce the output required by the host.

**Automatic exposure control**: In normal operation the VL6524/VS6524 determines the appropriate exposure settings for a particular scene and outputs correctly exposed images.

**Flicker cancellation:** The 50/60Hz flicker frequency present in the lighting (due to fluorescent lighting) can be cancelled by the system.

**Automatic white balance:** The microprocessor adjusts the gains applied to the individual color channels in order to achieve a correctly color balanced image.

**Dark calibration:** The microprocessor uses information from special dark lines within the pixel array to apply an offset to the video data and ensure a consistent 'black' level.

**Active noise management:** The microprocessor is able to modify certain video pipe functions according to the current exposure settings determined by the automatic exposure controller. The main purpose of this is to improve the noise level in the system under low lighting conditions. Functions which 'strength' is reduced under low lighting conditions (e.g. sharpening) are controlled by 'dampers'. Functions which 'strength' is increased under low lighting conditions are controlled by 'promoters'. The fade to black operation is also controlled by the microprocessor

VL6524/VS6524 Operational modes

# 4 Operational modes

VL6524/VS6524 has a number of operational modes. The STANDBY mode is entered and exited by driving the hardware CE signal. Transitions between all other modes are initiated by I<sup>2</sup>C transactions from the host system or automatically after time-outs.

Supplies turned ON & CE pin LOW Supplies Supplies OFI Power-down turned OFF CE pin LOW Supplies turned-off CE pin HIGH State Machine at power-up Standby I<sup>2</sup>C controlled user mode transitions 1 STOP mode PAUSE mode Flashgun mode Run mode Note: It is possible to enter any of the user modes direct from Standby via an I2C command

Figure 2. State machine at power -up and user mode transitions

**Power Down/Up:** The power down state is entered from all other modes when CE is pulled low or the supplies are removed.

During the power-down state (CE = logic 0)

- The internal digital supply of the VL6524/VS6524 is shut down by an internal switch mechanism. This method allows a very low power-down current value.

- The device input / outputs are fail-safe, and consequently can be considered high impedance.

Operational modes VL6524/VS6524

During the power-up sequence (CE = logic 1)

- The digital supplies must be on and stable.

- The internal digital supply of the VL6524/VS6524 is enabled by an internal switch mechanism.

- All internal registers are reset to default values by an internal power on reset cell.

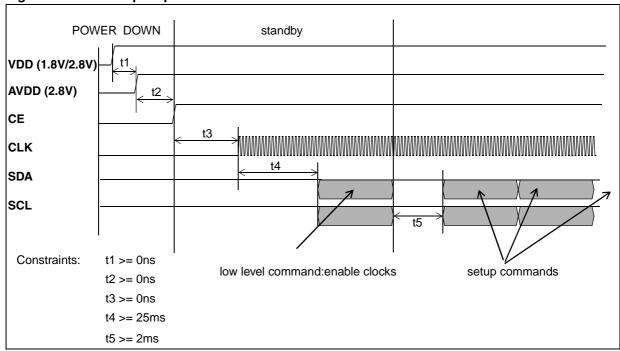

Figure 3. Power up sequence

**STANDBY mode:** The VL6524/VS6524 enters STANDBY mode when the CE pin on the device is pulled HIGH. Power consumption is very low, most clocks inside the device are switched off.

In this state I<sup>2</sup>C communication is possible when CLK is present and when the microprocessor is enabled by writing the value 0x06 to the *MicroEnable* register 0xC003 (*Table 7*).

All registers are reset to their default values. The device I/O pins have a very high-impedance.

Note:

On exit from STANDBY mode, the VL6524/VS6524 is in a transient mode called UNINITIALISED, this mode is not a user mode.

**STOP mode:** This is a low power mode. The analogue section of the VL6524/VS6524 is switched off and all registers are accessed over the  $I^2C$  interface. A run command received in this state automatically sets a transition through the PAUSE state to the run mode.

**PAUSE mode:** In this mode all VL6524/VS6524 clocks are running and all registers are accessible but no data is output from the device. The device is ready to start streaming but is halted. This mode is used to set up the required output format before outputting any data.

Note:

The PowerManagement register bTimeToPowerdown can be adjusted in PAUSE mode but has no effect until the next RUN to PAUSE transition (Table 13).

**RUN mode:**This is the fully operational mode.

VL6524/VS6524 Operational modes

**ViewLive:** this feature allows different sizes, formats and reconstruction settings to be applied to alternate frames of data, while in run mode.

**FLASHGUN mode:** In flashgun mode, the array is configured for use with an external flashgun. A flash is triggered and a single frame of data is output and the device automatically switches to Pause Mode.

#### **Mode transitions**

Transitions between operating modes are normally controlled by the host by writing to the *Mode control* register. Some transitions can occur automatically after a time out. If there is no activity in the PAUSE state then an automatic transition to the STOP state occurs. This functionality is controlled by the *Power management control* register. Writing 0xFF disables the automatic transition to STOP mode.

Clock control VL6524/VS6524

### 5 Clock control

### 5.1 Input clock

The VL6524/VS6524 contains an internal PLL allowing it to produce accurate frame rates from a wide range of input clock frequencies. The allowable input range is from 6.5 MHz to 26 MHz. The input clock frequency must be programmed in the <code>uwExtClockFreqNum</code> (MSB), <code>uwExtClockFreqNum</code> (LSB) and <code>bExtClockFreqDen</code> registers (Table 12). To program an input frequency of 6.5 MHz, the numerator can be set to 13 and the denominator to 2. The default input frequency is 12 MHz.

### 5.2 System clock division

It is possible to set an overall system clock division of 2 in the bEnableGlobalSystemClockDivision register (*Table 12*). This results in a PCLK of 12MHz and a maximum frame rate of 15fps VGA.

### 5.3 Pixel clock (PCLK)

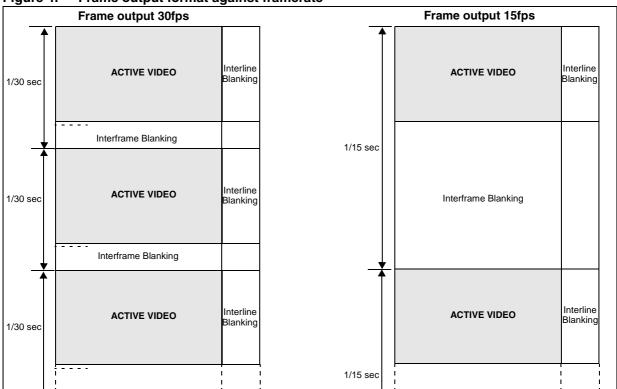

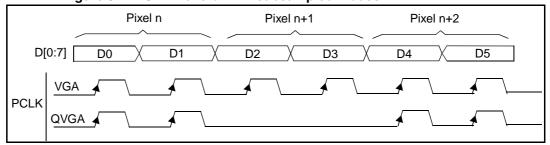

All data output from the VL6524/VS6524 is qualified by the PCLK output. The PCLK frequency is 24 MHz (equivalent to a 12 MHz pixel rate as each pixel is represented by 2 bytes of data). For frame rates less than 30 fps the PCLK frequency is not reduced, instead additional interframe lines are added into the output data stream.

Figure 4. Frame output format against framerate

VL6524/VS6524 Clock control

Similarly when using sub-sampled output modes the PCLK frequency is not reduced but instead pairs of PCLKs are 'dropped', see *Section 6.1.2: Subsampling module* for details.

The PCLK edge used to qualify the output data is fully programmable. It is also possible to program the state of the PCLK line (high or low) for the times when it is inactive.

### 5.4 PCLK gating

By default the PCLK output from the VL6524/VS6524 is *not* continuous. The PCLK qualifies all video data (and embedded codes if selected) on each video line and each interframe line but does *not* qualify the interline blanking data. In non-subsampled modes the PCLK is continuous *during* the video data output. The operation of the PCLK can be controlled using the *bPClkSetup* register (*Table 29*).

#### **Output frame size control** 6

#### 6.1 Frame format

An output frame consists of a number of active lines and a number of interframe lines. Each line consists of embedded line codes (if selected), active pixel data and interline blank data. Note that by default the interline blanking data is not qualified by the PCLK and therefore is not captured by the host system.

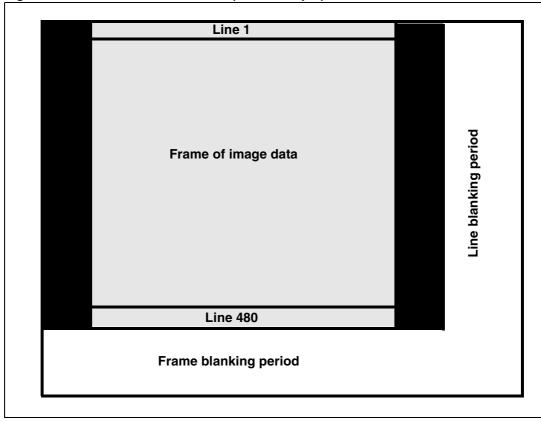

The default 30fps VGA output frame is shown in *Figure 5*.

1460 PCLKs 16 interframe blanking lines(0x10/0x80) **1280 PCLKs** 553 lines Line blanking 480 lines ACTIVE VIDEO (0x10/0x80)(640 by 480 pixels) 37 interframe blanking lines (0x10/0x80)

Figure 5. VGA 30fps output frame

If embedded codes are enabled then 8 additional clocks are required in every line to qualify the codes and 8 fewer interline clock are output leaving the total constant at 1460 clocks per

By default the PCLK output does not qualify the line blanking data and so each line contains only 1280 clocks (or 1288 if embedded codes are enabled).

The values which are output during line and frame blanking are an alternating pattern of 0x10 and 0x80 by default. These values can be changed by writing to the BlankData MSB and BlankData\_LSB registers in the Output formatter control bank.

#### 6.1.1 Cropping module

The VL6524/VS6524 contains a cropping module which can be used to define a window of interest within the full VGA array size. The user can set a start location and the required output size. Figure 6 shows the example with pipe setup bank0.

Figure 6. Crop controls (Table 16: Pipe setup bank0 control)

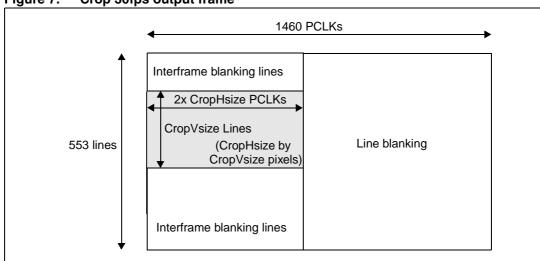

Complete lines which fall outside the window of interest are replaced in the output data frame with lines of blanking data thus the overall frame length is *not* reduced.

The portion of the output line which contains video data is reduced in length to contain only those pixels defined by the window of interest. However the *overall* line length remains unchanged as the number of interline clocks increases by the same amount.

Figure 7. Crop 30fps output frame

#### 6.1.2 Subsampling module

The VL6524/VS6524 has a built in sub-sampler which can divide the image by 1, 2, 3, 4, 5, or 6.

Using the sub-sampler gives output images with reduced resolution but the same field of view as the full VGA image or the region of interest defined in the cropping module. *Table 2* lists the available image sizes.

| Subsample ratio | Image format | Image dimensions |

|-----------------|--------------|------------------|

| 1 (default)     | VGA          | 640 by 480       |

| 2               | QVGA         | 320 by 240       |

| 3               | -            | 213 by 160       |

| 4               | QQVGA        | 160 by 120       |

| 5               | SQCIF        | 128 by 96        |

| 6               | -            | 106 by 80        |

Table 2. Subsampled image sizes

Subsampled images are produced by 'dropping' PCLKs so that only certain pixels are qualified in the output data stream. The figure below indicates a portion of the PCLK waveform for VGA and QVGA images. The effect of this is that the *time* taken to readout one line of the image remains constant in all subsampled modes - it is just the number of clocks that changes.

Figure 8. PCLK waveform in subsampled modes

It is possible to use the crop module and the sub-sampler together to achieve almost any required image size. When using the crop *and* subsampling functions together then the number of lines in a frame must be an integer multiple of the subsample ratio.

#### 6.2 Frame rate control

The VL6524/VS6524 features an extremely flexible frame rate controller. Using registers *uwDesiredFrame Rate\_Num (MSB)*, *uwDesiredFrame Rate\_Num (LSB)* and *bDesiredFrameRate\_Den* any desired frame rate between 1 and 30 fps can be selected (see *Table 14: Frame rate control* for register description). To program a required frame rate of 7.5 fps the numerator can be set to 15 and the denominator to 2. The default frame rate is 30 fps.

Slower frame rates are achieved by adding interframe lines. This results in a longer frame period and therefore a longer period over which integration is possible. Due to the longer

integration time available slower frame rates have improved performance in low light conditions.

#### 6.2.1 Horizontal mirror and vertical flip

The image data output from the VL6524/VS6524 can be mirrored horizontally or flipped vertically (or both).

These functions are available in the *Pipe setup bank0 control* register bank.

### 6.3 ViewLive Operation

ViewLive is an option which allows different size, format and image settings to be applied to alternate frames of the output data.

The controls for ViewLive function are found in the *View live control* register bank where the *fEnable* register allows the host to enable or disable the function and the *InitalPipeSetupBank* register selects which pipe setup bank is output first (see *Table 18: View live control* for register description).

#### Video pipe setup

The key controls for VL6524/VS6524 video pipe setup are grouped into register banks called *Pipe setup bank0 control* and *Pipe setup bank1 control*.

Pipe setup bank0 control setup is used when ViewLive is disabled.

When ViewLive is enabled the output data switches between *Pipe setup bank0 control* and *Pipe setup bank1 control* on each alternate frame.

Figure 9. ViewLive frame output format

| Frame output                     |                       |

|----------------------------------|-----------------------|

| Active video<br>Pipe setup bank0 | Interline<br>Blanking |

| Interframe Blanking              |                       |

| Active Video<br>Pipe setup bank1 | Interline<br>Blanking |

| Interframe Blanking              |                       |

### 6.4 Context switching

It is possible to control which pipe setup bank is used and to switch between banks without the need to pause streaming, the change will occur at the next frame boundry after the change to the register has been made.

For example this function allows the VL6524/VS6524 to stream an output targetting a display (e.g. RGB 444) and switch to capture an image (e.g. YUV 4:2:2) with no need to pause streaming or enter any other operating mode.

The register bNonViewLive\_ ActivePipeSetupBank allows selection of the pipe setup bank (see Table 15: Pipe setup bank selection).

VL6524/VS6524 Output data formats

### 7 Output data formats

The VL6524/VS6524 supports the following data formats:

- YUV4:2:2

- RGB565

- RGB444 (encapsulated as 565)

- RGB444 (zero padded)

- Bayer 10-bit

In all output formats there are 2 output bytes per pixel.

The required data format is selected using the *bdataFormat0* register described in *Table 16*. The various options available for each format are controlled using the *bRgbSetup* and *bYuvSetup* registers (*Table 29*).

### 7.1 YUV 4:2:2 data format

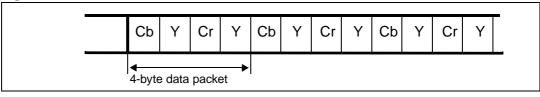

YUV 422 data format requires 4 bytes of data to represent 2 adjacent pixels. ITU601-656 defines the order of the Y, Cb and Cr components as shown in *Figure 10*.

Figure 10. Standard Y Cb Cr data order

The VL6524/VS6524 *bYuvSetup* register can be programmed to change the order of the components as follows:

Figure 11. Y Cb Cr data swapping options

|         | Y first | Cb first |    | omponents<br>4-byte data<br>2nd |    | 4th |

|---------|---------|----------|----|---------------------------------|----|-----|

|         | 1       | 1        | Υ  | Cb                              | Υ  | Cr  |

| DEFAULT | 0       | 1        | Cb | Υ                               | Cr | Υ   |

|         | 1       | 0        | Y  | Cr                              | Y  | Cb  |

|         | 0       | 0        | Cr | Υ                               | Cb | Υ   |

**Output data formats** VL6524/VS6524

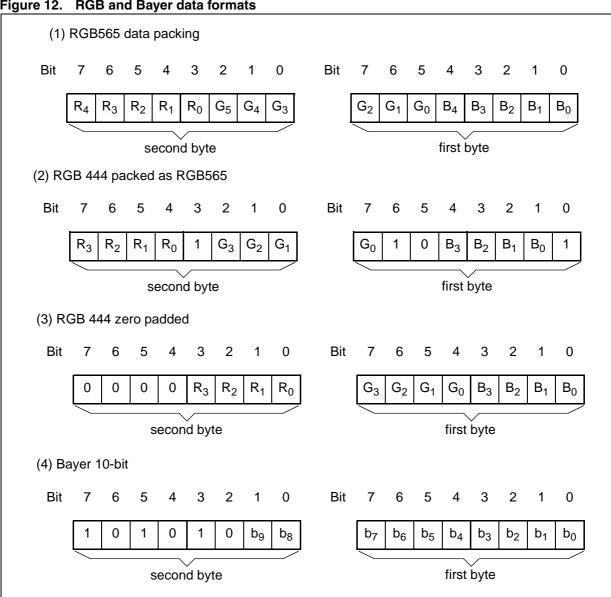

#### **RGB** and Bayer data formats 7.2

The VL6524/VS6524 can output RGB data in the following formats:

- **RGB565**

- RGB444 (encapsulated as RGB565)

- RGB444 (zero padded)

- Bayer 10-bit

Note:

Pixels in Bayer 10-bit data output are defect corrected, correctly exposed and white balanced. Any or all of these functions can be disabled.

In each of these modes 2 bytes of data are required for each output pixel. The encapsulation of the data is shown in Figure 12.

Figure 12. RGB and Bayer data formats

VL6524/VS6524 Output data formats

### 7.2.1 Manipulation of RGB data

It is possible to modify the encapsulation of the RGB data in a number of ways:

- swap the location of the RED and BLUE data

- reverse the bit order of the individual color channel data

- reverse the order of the data bytes themselves

### 7.2.2 Dithering

An optional dithering function can be enabled for each RGB output mode to reduce the appearance of contours produced by RGB data truncation. This is enabled through the *DitherControl* register (*Table 28: Dither control*).

25/70

### 8 Data synchronization methods

External capture systems can synchronize with the data output from VL6524/VS6524 in one of two ways:

- 1. Synchronization codes are embedded in the output data

- 2. Via the use of two additional synchronization signals: VSYNC and HSYNC

Both methods of synchronization can be programmed to meet the needs of the host system.

#### 8.1 Embedded codes

The embedded code sequence can be inserted into the output data stream to enable the external host system to synchronize with the output frames. The code consists of a 4-byte sequence starting with 0xFF, 0x00, 0x00. The final byte in the sequence depends on the mode selected.

Two types of embedded codes are supported by the VL6524/VS6524: Mode 1 (ITU656) and Mode 2. The *bSyncCodeSetup* register is used to select whether codes are inserted or not and to select the type of code to insert (*Table 29: Output formatter control*).

When embedded codes are selected each line of data output contains 8 additional clocks: 4 before the active video data and 4 after it.

### 8.1.1 Prevention of false synchronization codes

The VL6524/VS6524 is able to prevent the output of 0xFF and/or 0x00 data from being misinterpreted by a host system as the start of synchronization data. This function is controlled the *bCodeCheckEnable* register (*Table 29: Output formatter control*).

### 8.1.2 Mode 1(ITU656 compatible)

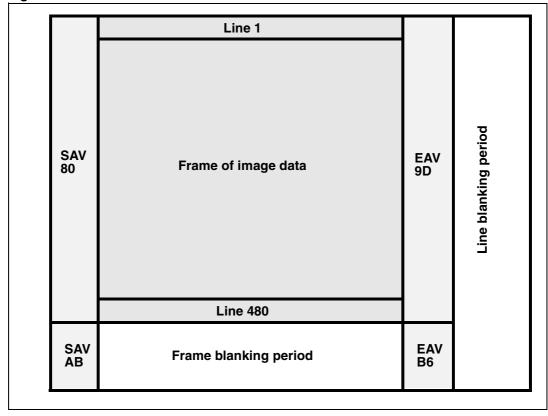

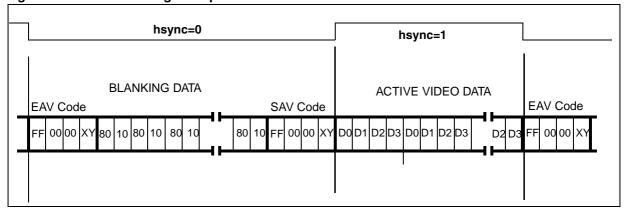

The structure of an image frame with ITU656 codes is shown in *Figure 13*.

Figure 13. ITU656 frame structure with even codes

The synchronization codes for odd and even frames are listed in *Table 3* and *Table 4*. By default all frames output from the VL6524/VS6524 are EVEN. It is possible to set all frames to be ODD or to alternate between ODD and EVEN using the SyncCodeSetup register in the *Output formatter control* register bank.

Table 3. ITU656 embedded synchronization code definition (even frames)

| Name           | Description           | 4-byte sequence |

|----------------|-----------------------|-----------------|

| SAV            | Line start - active   | FF 00 00 80     |

| EAV            | Line end - active     | FF 00 00 9D     |

| SAV (blanking) | Line start - blanking | FF 00 00 AB     |

| EAV (blanking) | Line end - blanking   | FF 00 00 B6     |

#### 8.1.3 Mode 2

Table 4. ITU656 embedded synchronization code definition (odd frames)

| Name           | Description           | 4-byte sequence |

|----------------|-----------------------|-----------------|

| SAV            | Line start - active   | FF 00 00 C7     |

| EAV            | Line end - active     | FF 00 00 DA     |

| SAV (blanking) | Line start - blanking | FF 00 00 EC     |

| EAV (blanking) | Line end - blanking   | FF 00 00 F1     |

The structure of a mode 2 image frame is shown Figure 14.

Figure 14. Mode 2 frame structure (VGA example)

For mode 2, the synchronization codes are as listed in *Table 5*.

Table 5. Mode 2 - embedded synchronization code definition

| Name | Description | 4-byte sequence |

|------|-------------|-----------------|

| LS   | Line start  | FF 00 00 00     |

| LE   | Line end    | FF 00 00 01     |

Table 5. Mode 2 - embedded synchronization code definition

| Name        | Description | 4-byte sequence |  |  |  |  |

|-------------|-------------|-----------------|--|--|--|--|

| Frame Start |             | FF 00 00 02     |  |  |  |  |

| FE          | Frame End   | FF 00 00 03     |  |  |  |  |

#### 8.2 VSYNC and HSYNC

The VL6524/VS6524 can provide two programmable hardware synchronization signals: VSYNC and HSYNC. The position of these signals within the output frame can be programmed by the user or an automatic setting can be used where the signals track the active video portion of the output frame regardless of its size.

#### 8.2.1 Horizontal synchronization signal (HSYNC)

The HSYNC signal is controlled by the *bHSyncSetup* register (*Table 29*). The following options are available:

- enable/disable

- select polarity

- all lines or active lines only

- manual or automatic

In automatic mode the HSYNC signal envelops all the active video data on every line in the output frame regardless of the programmed image size. Line codes (if selected) fall outside the HSYNC envelope as shown in *Figure 15*.

Figure 15. HSYNC timing example

If manual mode is selected then the pixel positions for HSYNC rising edge and falling edge are programmable. The pixel position for the rising edge of HSYNC is programmed in the bHsyncRisingH, bHsyncRisingL registers. The pixel position for the falling edge of HSYNC is programmed in the bHsyncFallingH and bHsyncFallingL registers (Table 29).

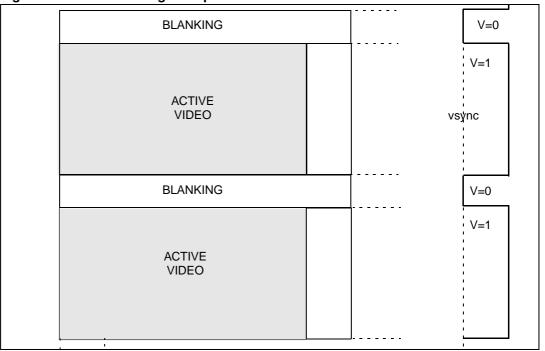

#### 8.2.2 Vertical synchronization (VSYNC)

The VSYNC signal is controlled by the *bVSyncSetup* register. The following options are available:

- enable/disable

- select polarity

- manual or automatic

In automatic mode the VSYNC signal envelops all the active video lines in the output frame regardless of the programmed image size as shown in *Figure 16*.

Figure 16. VSYNC timing example

If manual mode is selected then the line number for VSYNC rising edge and falling edge is programmable. The rising edge of VSYNC is programmed in the <code>bVsyncRisingLineH</code>, <code>bVsyncRisingLineL</code> registers, the pixel position for VSYNC rising edge is programmed in the <code>bVsyncRisingPixelH</code> and <code>bVsyncRisingPixelL</code> registers. Similarly the line count for the falling edge position is specified in the <code>bVsyncFallingLineH</code> and <code>bVsyncFallingLineL</code> registers, and the pixel count is specified in the <code>bVsyncFallingPixelH</code> and <code>bVsyncFallingPixelL</code> registers described in <code>Table 29: Output formatter control</code>.

VL6524/VS6524 Getting started

### 9 Getting started

### 9.1 Initial power up

Before any communication is possible with the VL6524/VS6524 the following steps must take place:

- 1. Apply VDD (1.8V or 2.8V)

- 2. Apply AVDD (2.8V)

- 3. Apply an external CLOCK (6.5 MHz to 26 MHz)

- 4. Assert CE line HIGH

These steps can all take place simultaneously. After these steps are complete a delay of 200 µs is required before any I<sup>2</sup>C communication can take place, see *Figure 3: Power up sequence*.

### 9.2 Minimum startup command sequence

- Enable the microprocessor before any commands can be sent to the VL6524/VS6524, the internal microprocessor must be enabled by writing the value 0x06 to the *MicroEnable* register 0xC003 (*Table 7: Low-level control registers*).

- Enable the digital I/O after power up the digital I/O of the VL6524/VS6524 is in a high-impedance state ('tri-state'). The I/O are enabled by writing the value 0x01 to the Enable I/O register 0xC034 (Table 7: Low-level control registers).

- The user can then program the system clock frequency and setup the required output format before placing the VL6524/VS6524 in RUN mode by writing 0x02 to the bUserCommand register 0x0180 (Table 9: Mode control).

The above three commands represent the absolute minimum required to get video data output.

The default configuration results in an output of VGA, 30 fps, YUV data format with ITU embedded codes requiring a external clock frequency of 12MHz.

In practice the user is likely to require to write some additional setup information prior to receive the required data output.

### 10 Host communication - I<sup>2</sup>C control interface

The interface used on the VL6524/VS6524 is a subset of the I<sup>2</sup>C standard. Higher level protocol adaptations have been made to allow for greater addressing flexibility. This extended interface is known as the V2W interface.

### V2W protocol layer

#### **Protocol**

A message contains two or more bytes of data preceded by a START (S) condition and followed by either a STOP (P) or a repeated START (Sr) condition followed by another message.

STOP and START conditions can only be generated by a V2W master.

After every byte transferred the receiving device must output an acknowledge bit which tells the transmitter if the data byte has been successfully received or not.

The first byte of the message is called the device address byte and contains the 7-bit address of the V2W slave to be addressed plus a read/write bit which defines the direction of the data flow between the master and the slave.

The meaning of the data bytes that follow device address changes depending whether the master is writing to or reading from the slave.

Figure 17. Write message

For the master writing to the slave the device address byte is followed by 2 bytes which specify the 16-bit internal location (index) for the data write. The next byte of data contains the value to be written to that register index. If multiple data bytes are written then the internal register index is automatically incremented after each byte of data transferred. The master can send data bytes continuously to the slave until the slave fails to provide an acknowledge or the master terminates the write communication with a STOP condition or sends a repeated START (Sr).

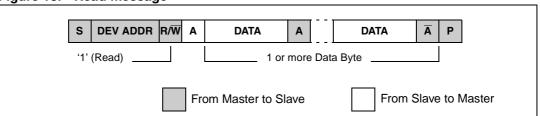

Figure 18. Read message

For the master reading from the slave the device address is followed by the contents of last register index that the previous read or write message accessed. If multiple data bytes are read then the internal register index is automatically incremented after each byte of data read. A read message is terminated by the bus master generating a negative acknowledge after reading a final byte of data.

A message can only be terminated by the bus master, either by issuing a stop condition, a repeated start condition or by a negative acknowledge after reading a complete byte during a read operation.

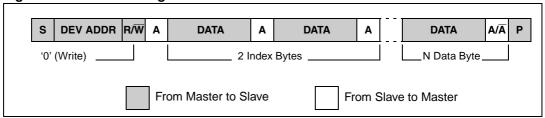

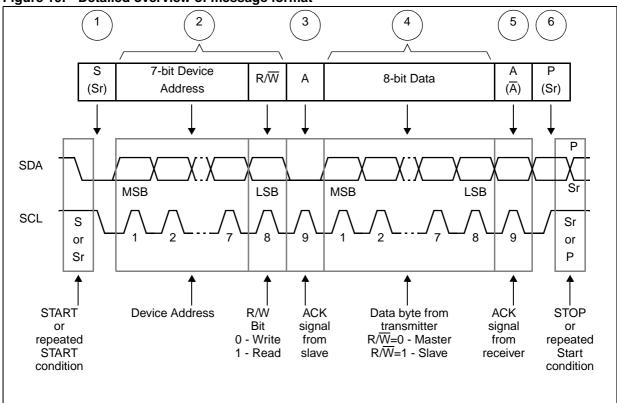

### Detailed overview of the message format

Figure 19. Detailed overview of message format

The V2W generic message format consists of the following sequence

- Master generates a START condition to signal the start of new message.

- 2. Master outputs, MS bit first, a 7-bit device address of the slave the master is trying to communicate with followed by a R/W bit.

Figure 20. Device addresses

| Sensor Address                       | 0 | 0 | 1 | 0 | 0 | 0 | 0 | R/W |  |

|--------------------------------------|---|---|---|---|---|---|---|-----|--|

| Sensor write Address 20 <sub>H</sub> | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0   |  |

| Sensor read Address 21 <sub>H</sub>  | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1   |  |

- a)  $R/\overline{W} = 0$  then the master (transmitter) is writing to the slave (receiver).

- b)  $R/\overline{W} = 1$  the master (receiver) is reading from the slave (transmitter).

- 3. The addressed slave acknowledges the device address.

- 4. Data transmitted on the bus

- a) When a write is performed then master outputs 8-bits of data on SDA (MS Bit first).

- b) When a read is performed then slave outputs 8-bits of data on SDA (MS Bit First).

- 5. Data receive acknowledge

- a) When a write is performed slave acknowledges data.

- b) When a read is performed master acknowledges data.

- Repeat 4 and 5 until all the required data has been written or read.

- Minimum number of data bytes for a read =1 (Shortest Message length is 2-bytes).

- The master outputs a negative acknowledge for the data when reading the last byte of data. This causes the slave to stop the output of data and allows the master to generate a STOP condition.

- 6. Master generates a STOP condition or a repeated START.

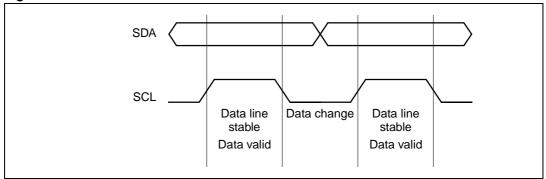

#### Data valid

The data on SDA is stable during the high period of SCL. The state of SDA is changed during the low phase of SCL. The only exceptions to this are the start (S) and stop (P) conditions as defined below. (See *Figure 33: Timing specification* and *Table 38: Timing specification*).

Figure 21. SDA data valid

34/70

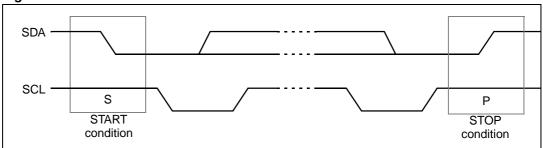

### Start (S) and Stop (P) conditions

A START (S) condition defines the start of a V2W message. It consists of a high to low transition on SDA while SCL is high.

A STOP (P) condition defines the end of a V2W message. It consists of a low to high transition on SDA while SCL is high.

After STOP condition the bus is considered free for use by other devices. If a repeated START (Sr) is used instead of a stop then the bus stays busy. A START (S) and a repeated START (Sr) are considered to be functionally equivalent.

Figure 22. START and STOP conditions

#### **Acknowledge**

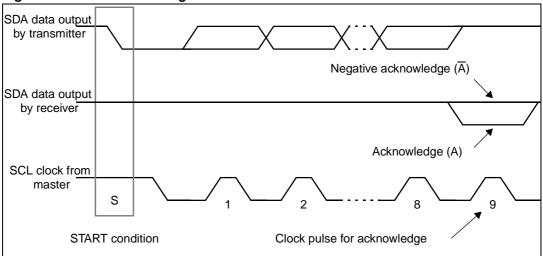

After every byte transferred the receiver must output an acknowledge bit. To acknowledge the data byte receiver pulls SDA during the 9th SCL clock cycle generated by the master. If SDA is not pulled low then the transmitter stops the output of data and releases control of the bus back to the master so that it can either generate a STOP or a repeated START condition.

Figure 23. Data acknowledge

#### **Index space**

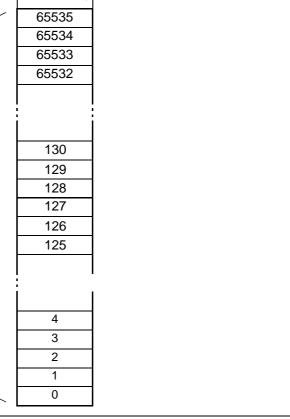

Communication using the serial bus centres around a number of registers internal to the either the sensor or the co-processor. These registers store sensor status, set-up, exposure and system information. Most of the registers are read/write allowing the receiving equipment to change their contents. Others (such as the chip id) are read only.

8 bits

The internal register locations are organized in a 64k by 8-bit wide space. This space includes "real" registers, SRAM, ROM and/or micro controller values.

Figure 24. Internal register index space

16-bit Index / 8-bit Data Format 64k by 8-bit wide index space (Valid Addresses 0-65535)

### Types of messages

This section gives guidelines on the basic operations to read data from and write data to VL6524/VS6524.

The serial interface supports variable length messages. A message contains no data bytes or one data byte or many data bytes. This data can be written to or read from common or different locations within the sensor. The range of instructions available are detailed below.

Single location, single byte data read or write.

Write no data byte. Only sets the index for a subsequent read message.

Multiple location, multiple data read or write for fast information transfers.

Any messages formats other than those specified in the following section should be considered illegal.

### Random location, single data write

For the master writing to the slave the R/W bit is set to zero.

The register index value written is preserved and is used by a subsequent read. The write message is terminated with a stop condition from the master.

16-bit Index, 8-bit Data, Random Location, Single Data Write Previous Index Value, K Index M DEV ADDR R/W Ρ **DATA** Α **DATA DATA** A/A Α Α '0' (Write) INDEX[15:8] INDEX[7:0] **DATA**[7:0] Index[15:0] value, M DATA[7:0] From Master to Slave S = START Condition A = Acknowledge Sr = repeated START P = STOP Condition A = Negative Acknowledge From Slave to Master

Figure 25. Random location, single write

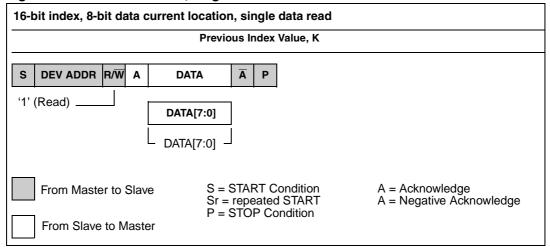

#### Current location, single data read

For the master reading from the slave the  $R/\overline{W}$  bit is set to one. The register index of the data returned is that accessed by the previous read or write message.

The first data byte returned by a read message is the contents of the internal index value and NOT the index value. This was the case in older V2W implementations.

Note that the read message is terminated with a negative acknowledge  $(\overline{A})$  from the master: it is not guaranteed that the master will be able to issue a stop condition at any other time during a read message. This is because if the data sent by the slave is all zeros, the SDA line cannot rise, which is part of the stop condition.

Figure 26. Current location, single read

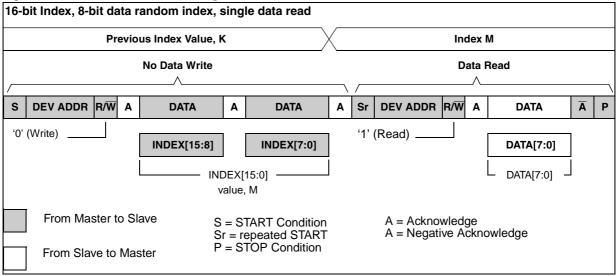

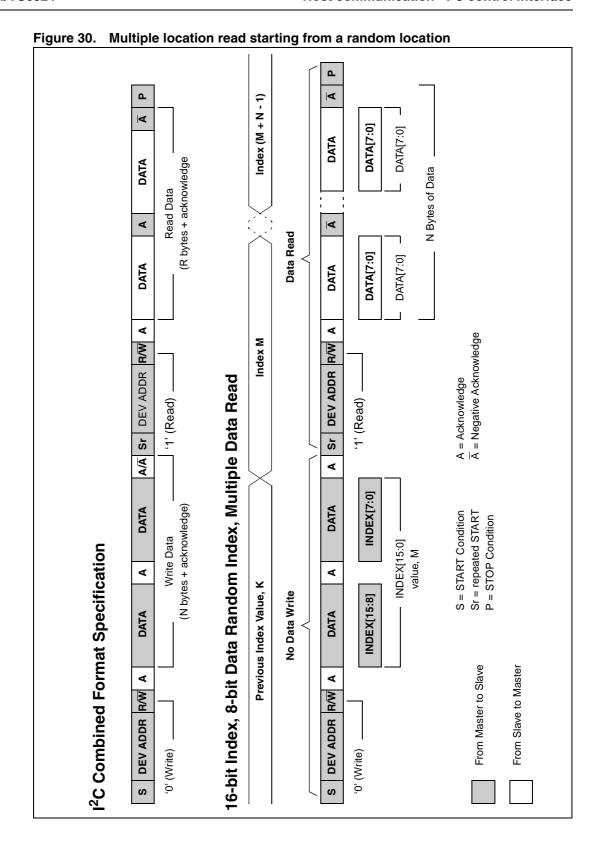

#### Random location, single data read

When a location is to be read, but the value of the stored index is not known, a write message with no data byte must be written first, specifying the index. The read message then completes the message sequence. To avoid relinquishing the serial to bus to another master a repeated start condition is asserted between the write and read messages.

As mentioned in the previous example, the read message is terminated with a negative acknowledge  $(\overline{A})$  from the master.

Figure 27. Random location, single data read

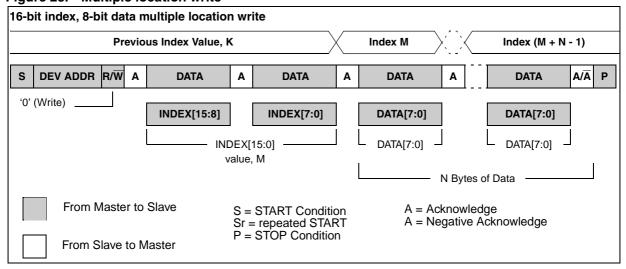

#### **Multiple location write**

For messages with more than 1 data byte the internal register index is automatically incremented for each byte of data output, making it possible to write data bytes to consecutive adjacent internal registers without having to send explicit indexes prior to sending each data byte.

Figure 28. Multiple location write

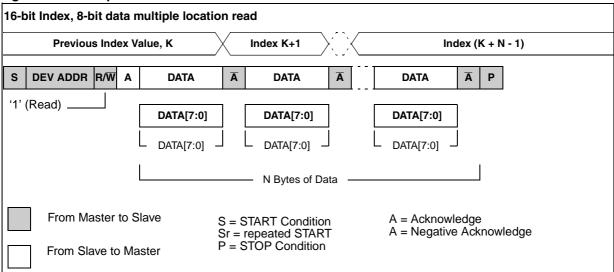

### Multiple location read stating from the current location

In the same manner to multiple location writes, multiple locations can be read with a single read message.

Figure 29. Multiple location read

### 11 Register map

The VL6524/VS6524 I<sup>2</sup>C write address is 0x20.

All I<sup>2</sup>C locations contain an 8-bit byte. However, certain parameters require 16 bits to represent them and are therefore stored in more than 1 location.

Note: For all 16 bit parameters the MSB register must be written before the LSB register.

The data stored in each location can be interpreted in different ways as shown below. Register contents represent different data types as described in *Table 6*.

Table 6. Data type

| Data Type | Description                                              |  |  |  |  |  |  |  |

|-----------|----------------------------------------------------------|--|--|--|--|--|--|--|

| I         | Integer parameter.                                       |  |  |  |  |  |  |  |

| М         | Multiple field registers - 16 bit parameter              |  |  |  |  |  |  |  |

| В         | Bit field register - individual bits must be set/cleared |  |  |  |  |  |  |  |

| С         | Coded register - function depends on value written       |  |  |  |  |  |  |  |

| F         | Float Value                                              |  |  |  |  |  |  |  |

#### Float number format

Float 900 is used in ST co-processors to represent floating point numbers in 2 bytes of data. It conforms to the following structure:

Bit[15] = Sign bit (1 represents negative)

Bit[14:9] = 6 bits of exponent, biased at decimal 31

Bit[8:0] = 9 bits of mantissa

To convert a floating point number to Float 900, use the following procedure:

- represent the number as a binary floating point number. Normalize the mantissa and calculate the exponent to give a binary scientific representation of 1.xxxxxxxxx \* 2^y.

- The x symbols should represent 9 binary digits of the mantissa, round or pad with zeros to achieve 9 digits in total. Remove the leading 1 from the mantissa as it is redundant.

- To calculate the y value Bias the exponent by adding to 31 decimal then converting to binary.

- The data can then be placed in the structure above.

#### **Example**

Convert -0.41 to Float 900

Convert the fraction into binary by successive multiplication by 2 and removal of integer component

```

0.41 * 2 = 0.82

0

0.82 * 2 = 1.64

0.64 * 2 = 1.28

1

0.28 * 2 = 0.56

0.56 * 2 = 1.12

0.12 * 2 = 0.24

0.24 * 2 = 0.48

0.48 * 2 = 0.96

0.96 * 2 = 1.92

0.92 * 2 = 1.84

0.84 * 2 = 1.68

1

0.68 * 2 = 1.36

1

0.36 * 2 = 0.72

```

This gives us -0.0110100011110.

We then normalize by moving the decimal point to give - 1.10100011110 \* 2^-2.

The mantissa is rounded and the leading zero removed to give 101001000.

We add the exponent to the bias of 31 that gives us 29 or 11101.

A leading zero is added to give 6 bits 011101.

The sign bit is set at 1 as the number is negative.

This gives us 1011 1011 0100 1000 as our Float 900 representation or BB48 in hex.

To convert the encoded representation back to a decimal floating point, we can use the following formula.

```

Real is = (-1)^sign * ((512+mantissae) >> 9) * 2^(exp-31)

```

Thus to convert BB48 back to decimal, the following procedure is followed:

Note that >>9 right shift is equal to division by 2^9.

```

Sign = 1

```

```

Exponent = 11101 (29 decimal)

```

Mantissa = 101001000 (328 decimal)

This gives us:

```

real = (-1)^1 * ((512+328)/2^9) * 2^(29-31)

```

real = -0.41015625

When compared to the original -0.41, we see that some rounding errors have been introduced.

### Low level control registers

Table 7. Low-level control registers

| Name        | Index  | R/W | Data<br>Type | Format<br><i>default</i> | Description             |

|-------------|--------|-----|--------------|--------------------------|-------------------------|

| MicroEnable | 0xC003 | R/W | С            | 0x38                     | 0x06 - clocks enabled   |

| Enable I/O  | 0xC034 | R/W | В            | 0x00                     | set bit[0] to enable IO |

Note:

The default values for the above registers are true when the device is powered on, Ext. Clk input is present and the CE pin is high. All other registers can be read when the Clock enable register is set to 0x06.

### **Device parameters [read only]**

Table 8. Device parameters

| Name              | Index  | R/W | Data<br>Type | Format<br>default | Description      |

|-------------------|--------|-----|--------------|-------------------|------------------|

| uwDeviceId (MSB)  | 0x0001 | R   | I            | 0x02              | 0x020c = 524     |

| uwDeviceId (LSB)  | 0x0002 | R   | I            | 0x0c              | 000200 = 324     |

| bFirmwareVsnMajor | 0x0004 | R   | I            | 0x01              | Firmware version |

| bFirmwareVsnMinor | 0x0006 | R   | I            | 0x01              | 0x0101 = 1.1     |

| bPatchVsnMajor    | 0x0008 | R   | I            | 0x00              | Patch version    |

| bPatchVsnMinor    | 0x000a | R   | I            | 0x00              | 0x0000           |

#### **Mode control**

Table 9. Mode control

| Name         | Index  | R/W | Data<br>Type | Format<br><i>default</i> | Description                                                                                         |

|--------------|--------|-----|--------------|--------------------------|-----------------------------------------------------------------------------------------------------|

| bUserCommand | 0x0180 | RW  | С            | 0                        | 0x00 - UNINITIALISED<br>0x01 - BOOT<br>0x02 - RUN<br>0x03 - PAUSE<br>0x04 - STOP<br>0x05 - FLASHGUN |

### Mode Status [read only]

Table 10. Mode status

| Name   | Index  | R/W | Data<br>Type | Format<br><i>default</i> | Description                                                                                                                                    |

|--------|--------|-----|--------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bState | 0x0202 | R   | С            | 0x10                     | 0x10 - RAW 0x21 - Waiting for BOOT 0x22 - PAUSED 0x26 - Waiting for RUN 0x31 - RUNNING 0x32 - Waiting for PAUSE 0x40 - FLASHGUN 0x50 - STOPPED |

#### RunModeControl

Table 11. RunModeControl

| Name        | Index  | R/W | Data<br>Type | Format default | Description                 |

|-------------|--------|-----|--------------|----------------|-----------------------------|

| fMeteringOn | 0x0280 | R/W | В            | 0x01           | 0x00 = False<br>0x01 = True |

### **Clock manager input control**

Table 12. Clock manager input control

| Name                                 | Index  | R/W | Data<br>Type | Format<br>default | Description                                             |

|--------------------------------------|--------|-----|--------------|-------------------|---------------------------------------------------------|

| uwExtClockFreqNum<br>(MSB)           | 0x060b | R/W | I            | 0x00              | Specifies the external clock frequency numerator        |

| uwExtClockFreqNum<br>(LSB)           | 0x060c | R/W | I            | 0x0c              | Default = 12 MHz                                        |

| bExtClockFreqDen                     | 0x060e | R/W | I            | 0x01              | Specifies the external clock frequency denominator      |

| bEnableGlobalSystem<br>ClockDivision | 0x0610 | R/W | В            | 0x00              | 0x00 = False<br>0x01 = True -system clock division by 2 |

### **Power management control**

Table 13. Power management control

| Name             | Index  | R/W | Data<br>Type | Format default | Description                                                                                |

|------------------|--------|-----|--------------|----------------|--------------------------------------------------------------------------------------------|

| bTimeToPowerdown | 0x0580 | R/W | 1            | 0x0f           | Time (ms) from pausing streaming to entering stop. In the range 5 to 154 ms 0xff - disable |

#### Frame rate control

Table 14. Frame rate control

| Name                             | Index  | R/W | Data<br>Type | Format<br>default | Description                    |

|----------------------------------|--------|-----|--------------|-------------------|--------------------------------|

| uwDesiredFrame<br>Rate_Num (MSB) | 0x0d81 | R/W | I            | 0x00              | Numerator for the Frame Rate   |

| uwDesiredFrame<br>Rate_Num (LSB) | 0x0d82 | R/W | I            | 0x1e              | Default = 30 fps               |

| bDesiredFrameRate_<br>Den        | 0x0d84 | R/W | I            | 0x01              | Denominator for the Frame Rate |

### Pipe setup bank selection

Table 15. Pipe setup bank selection

| Name                                 | Index  | R/W | Data<br>Type | Format default | Description                                             |

|--------------------------------------|--------|-----|--------------|----------------|---------------------------------------------------------|

| bNonViewLive_<br>ActivePipeSetupBank | 0x0302 | R/W | 1            | 0x00           | 0x00 -Pipe setup bank0 used 0x01 -Pipe setup bank1 used |

# Pipe setup bank0 control

Table 16. Pipe setup bank0 control

| Name             | Index  | R/W | Data<br>Type | Format<br>default | Description                                                                                                         |

|------------------|--------|-----|--------------|-------------------|---------------------------------------------------------------------------------------------------------------------|

| blmageSize0      | 0x0380 | R/W | С            | 0x01              | Required output dimension 0x01 - ImageSize_VGA 0x02 - ImageSize_QVGA 0x03 - ImageSize_QQVGA 0x04 - ImageSize_Manual |

| bSubSample0      | 0x0382 | R/W | I            | 0x01              | 0x01 = Minimum sub-sample corresponding to no sub-sampling. MAX = 0x06                                              |

| fEnableCrop0     | 0x0384 | R/W | В            | 0x00              | 0x00 = False - 0x01 = True                                                                                          |

| uwCropHStartMSB0 | 0x0387 | R/W | ΜI           | 0x00              | Light and a start agent for manual area                                                                             |

| uwCropHStartLSB0 | 0x0388 | R/W | ΜI           | 0x00              | Horizontal start point for manual crop                                                                              |

| uwCropHSizeMSB0  | 0x038b | R/W | МΙ           | 0x00              | Hari-outel size for months and                                                                                      |

| uwCropHSizeLSB0  | 0x038c | R/W | ΜI           | 0x00              | Horizontal size for manual crop                                                                                     |

| uwCropVStartMSB0 | 0x038f | R/W | ΜI           | 0x00              | Vertical start point for manual erap                                                                                |

| uwCropVStartLSB0 | 0x0390 | R/W | МТ           | 0x00              | Vertical start point for manual crop                                                                                |

| uwCropVSizeMSB0  | 0x0393 | R/W | ΜI           | 0x00              | Vertical size for manual grap                                                                                       |

| uwCropVSizeLSB0  | 0x0394 | R/W | ΜI           | 0x00              | Vertical size for manual crop                                                                                       |

Table 16. Pipe setup bank0 control

| Name                       | Index  | R/W | Data<br>Type | Format default | Description                                                                                                                                                                                        |

|----------------------------|--------|-----|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bdataFormat0               | 0x0396 | R/W | С            | 0x01           | 0x00 = YCbCr_JFIF<br>0x01 = YCbCr_Rec601<br>0x02 = YCbCr_Custom<br>0x03 = RGB_565<br>0x04 = RGB_565_Custom<br>0x05 = RGB_444<br>0x06 = RGB_444_Custom<br>0x07 = reserved<br>0x08 = Bayer output VP |

| bBayerOutput<br>Alignment0 | 0x398  | R/W | С            | 0x04           | 0x04 = Bayer output right shifted<br>0x05 = Bayer output left shifted                                                                                                                              |

| bContrast0                 | 0x039a |     | I            | 0x79           | Contrast control (%)                                                                                                                                                                               |

| bColorSaturation0          | 0x039c |     | I            | 0x7d           | Color saturation control (%)                                                                                                                                                                       |

| bGamma0                    | 0x039e |     | I            | 0x0f           | Gamma settings<br>0x00 = Gamma_Linear<br>0x10 = Gamma SMPTE 240M<br>0x1F = Gamma_Max                                                                                                               |

| fHorizontaiMirror0         | 0x03a0 |     | В            | 0x00           | Horizontal mirror control,<br>0x00 = False - 0x01 = True                                                                                                                                           |

| fVerticalFlip0             | 0x03a2 |     | В            | 0x00           | Vertical mirror control,<br>0x00 = False - 0x01= True                                                                                                                                              |

# **Pipe Setup Bank1 Control**

Table 17. Pipe setup bank1 control

| Index  | R/W                                                                                                                    | Data<br>Type                                                                                                                                                                           | Format<br><i>default</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0400 | R/W                                                                                                                    | С                                                                                                                                                                                      | 0x01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Required output dimension  0x01 = ImageSize_VGA  0x02 = ImageSize_QVGA  0x03 = ImageSize_QQVGA  0x04 = ImageSize_Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |