# 查询VP8708GCGDPAS供应商

**#GEC PLESSEY** SEMICONDUCTOR

加急出货

**ADVANCE INFORMATION**

D.S.3182 2.2

# **VP8708**

# 30MHz 8–BIT ANALOG VIDEO INPUT INTERFACE

(Supersedes edition in December 1993 Digital Video & Digital Signal Processing Handbook)

The VP8708 is an analog input interface designed for video signal conditioning and digitisation.

Operating from a single +5V supply, the VP8708 includes an input multiplexer, video amplifier with clamp and gain control, an onboard reference and a buffered 8-bit ADC capable of digitising signals upto the Nyquist limit.

Video signals may be supplied to the VP8708 either directly to the ADC, or via one of three multiplexed inputs for signal conditioning. The analog signal (with appropriate gain and clamping) is available as output prior to digitisation. The coded data, updated at the sample rate, is available in either binary or two's complement format via the 3-state TTL output buffers,

#### FEATURES

- Direct replacement for the PhilipsTDA8708\*

- 30MHz Sampling rate

- Selectable data format:

- Internal ADC reference

- Clamp and AGC functions

- 3-state TTL outputs

†GEC Plessey also offer direct replacements for Philips TDA8708A (GPS part no VP87A8) TΓ

### ORD

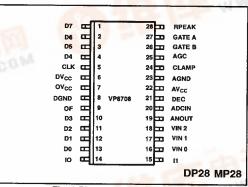

Fig. 1 Pin connections - top view

| DA8709A (GPS part n<br>DERING INFORM<br>/P8708G CG DPAS<br>/P8708G CG MPES | ATION<br>(Commercial - Pla | stic DIL)<br>ature Plastic DIL) | Supply<br>Supply<br>Groun<br>Video | V voltages, AV <sub>CC</sub><br>v differential<br>d differential<br>input voltage<br>t current |                            | +7V<br>±1V<br>±1V<br>AV <sub>CC</sub><br>10mA                                                                          |

|----------------------------------------------------------------------------|----------------------------|---------------------------------|------------------------------------|------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------|

|                                                                            |                            | E B AGND                        | DRIVER<br>AMP                      |                                                                                                | OVCC<br>3 STATE<br>OUTPUTS | <ul> <li>OF</li> <li>D7</li> <li>D6</li> <li>D5</li> <li>D4</li> <li>D3</li> <li>D2</li> <li>D1</li> <li>D0</li> </ul> |

|                                                                            |                            | rig. 2 Syste                    | m block diagrai                    | m                                                                                              |                            |                                                                                                                        |

68522 0024404 882

# RECOMMENDED OPERATING CONDITIONS

| Supply voltage AV <sub>CC</sub> , DV <sub>CC</sub> , OV <sub>CC</sub> | +5V   |

|-----------------------------------------------------------------------|-------|

| Supply differential                                                   | 0V    |

| Ground differential                                                   | 0V    |

| Video input voltage                                                   | 1Vp–p |

#### **OPERATING TEMPERATURE RANGE**

Commercial 0°C to +70°C (still air ambient)

ELECTRICAL CHARACTERISTICS: Test conditions (unless otherwise stated): AV<sub>CC</sub>, DV<sub>CC</sub>, OV<sub>CC</sub>=5V±0.5V, AGND/DGND shorted together, Temp=T<sub>full.</sub> =0 to + 70°C.

|                                               |                          |              | Test          | Value      |            |            | Units        | Conditions                                   |

|-----------------------------------------------|--------------------------|--------------|---------------|------------|------------|------------|--------------|----------------------------------------------|

| Parameter                                     | Symbol                   | Temp<br>(°C) | Test<br>level | Min        | Тур        | Max        | <b>U</b> III |                                              |

| POWER SUPPLY                                  |                          |              |               |            |            |            |              |                                              |

| Analog supply voltage                         | AV <sub>CC</sub>         | 25<br>FULL   | 1<br>4        | 4.5<br>4.5 | 5.0<br>5.0 | 5.5<br>5.5 | V<br>V       |                                              |

| Digital supply voltage                        | DV <sub>CC</sub>         | 25<br>FULL   | 1<br>4        | 4.5<br>4.5 | 5.0<br>5₊0 | 5.5<br>5.5 | v            |                                              |

| Output supply voltage                         | ov <sub>cc</sub>         | 25<br>FULL   | 1<br>4        | 4.5<br>4.5 | 5.0<br>5.0 | 5.5<br>5.5 | v            |                                              |

| Analog supply current                         | Alcc                     | 25<br>FULL   | 1<br>4        |            | 60         | 72         | mA<br>mA     |                                              |

| Digital supply current                        | DICC                     | 25<br>FULL   | 1<br>4        |            | 13         | 19         | mA<br>mA     |                                              |

| Output supply current                         | Olcc                     | 25<br>FULL   | 1<br>4        |            | 12         | 18         | mA<br>mA     |                                              |

| Power dissipation                             | Р                        | 25<br>FULL   | 1<br>4        |            | 425        | 600        | mW<br>mW     |                                              |

| VIDEO INPUTS                                  |                          |              |               |            |            |            | ļ            |                                              |

| Input range                                   | V <sub>IN</sub><br>(p–p) | FULL         | 4             | 0.5        | 1.0        | 1.6        | v            |                                              |

| Input impedance                               | IZ <sub>IN</sub> I       | FULL         | 4             | 18         | 20         | 22         | kΩ           | f <sub>in</sub> =6MHZ                        |

| Input capacitance                             | C <sub>in</sub>          | 25           | 5             |            | 2          |            | pF           | f <sub>in</sub> =6MHZ                        |

| 11, IO GATE B,TTL<br>INPUTS + GATE A          |                          |              |               |            | ļ          |            |              |                                              |

| Input voltage LOW                             | V <sub>il</sub>          | 25<br>FULL   | 1<br>4        |            |            | 0.8<br>0.8 | v<br>v       |                                              |

| Input current HIGH                            | V <sub>ih</sub>          | 25<br>FULL   | 1<br>4        | 2.0<br>2.0 |            |            | V<br>V       |                                              |

| Input current LOW                             | lit                      | 25<br>FULL   | 1 4           | 150<br>200 |            |            | μΑ<br>μΑ     | Vi=0.4V<br>Vi=0.4V                           |

| Input current HIGH                            | l <sub>ih</sub>          | 25<br>FULL   | 1<br>4        |            |            | 10<br>20   | μΑ<br>μΑ     | V <sub>i</sub> =3.6V<br>V <sub>i</sub> =3.6V |

| RPEAK input                                   |                          |              | 1             |            |            |            |              |                                              |

| Peak capacitor<br>charge/discharge<br>current | IPEAK                    | FULL         | 4             |            | 80         |            | μA           | R <sub>peak</sub> = 0Ω                       |

# THERMAL CHARACTERISTICS

| Storage temperature range<br>Lead temperature (soldering 11 seconds)<br>THERMAL RESISTANCES, DP PACKAG                                                                | -65°C to 150°C<br>+265°C |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Intermal Hesistances, DF FACKA           Junction to ambient (θ <sub>ja</sub> )           Junction to case (θ <sub>ic</sub> )           THERMAL RESISTANCES, MP PACKA | 55°C/W                   |

| THERMAL RESISTANCES, MP PACKA<br>Junction to ambient $(\theta_{ja})$<br>Junction to case $(\theta_{jc})$                                                              | 84°C/W<br>32°C/W         |

### **ELECTRICAL CHARACTERISTICS:**

Test conditions (unless otherwise stated):  $AV_{CC}$ ,  $DV_{CC}$ ,  $OV_{CC}=5V\pm0.5V$ , AGND/DGND shorted together, Temp=T<sub>full</sub> =0 to + 70°C.

| Parameter                            | Symbol             | Tomp       | Temp Test |              | Value                    |            |          |                                                           |

|--------------------------------------|--------------------|------------|-----------|--------------|--------------------------|------------|----------|-----------------------------------------------------------|

| r arameter                           | Symbol             | (°C)       | level     | Min          | Тур                      | Max        | Units    | Conditions                                                |

| AGC Control Input                    |                    |            |           |              |                          |            |          |                                                           |

| AGC voltage for<br>minimum gain      | V <sub>agc</sub>   | 25         | 4         |              | 2.7                      |            | v        |                                                           |

| AGC voltage for<br>maximum gain      | V <sub>agc</sub>   | 25         | 4         |              | 3.9                      |            | v        |                                                           |

| AGC output current                   | lagc               | 25         | 1         |              | •                        |            |          | * See table 4                                             |

| CLAMP Control Input                  |                    |            |           | Î            |                          |            |          |                                                           |

| Clamp voltage                        | V <sub>cip</sub>   | 25         | 4         |              | 3.5                      |            | v        | ADC output = 128                                          |

| Clamp output current                 | I <sub>cip</sub>   | 25         | 1         |              | •                        |            |          | * See table 4                                             |

| VIDEO Amplifier<br>Outputs           |                    |            |           |              |                          |            |          |                                                           |

| Internal current source              | l <sub>19</sub>    | 25         | 4         |              |                          | 2          | mA       |                                                           |

| DC Output voltage for<br>black level | V <sub>blk</sub>   | FULL       | 4         |              | AV <sub>CC</sub><br>3.25 |            | v        |                                                           |

| AC Output voltage<br>(peak-peak)     | V <sub>19</sub>    | FULL       | 4         |              | 1                        |            | V        |                                                           |

| Output impedance                     | Z <sub>19</sub>    | 25         | 4         |              | 45                       |            | Ω        |                                                           |

| CLK INPUT                            |                    |            |           |              |                          |            |          |                                                           |

| Input voltage LOW                    | V <sub>il</sub>    | 25<br>FULL | 1<br>4    |              |                          | 0.8<br>0.8 | v<br>v   |                                                           |

| Input voltage HIGH                   | V <sub>ih</sub>    | 25<br>FULL | 1<br>4    | 2.0<br>2.0   |                          |            | v<br>v   |                                                           |

| Input current LOW                    | կլ                 | 25<br>FULL | 1<br>4    | -150<br>-200 |                          |            | μΑ<br>μΑ | $\begin{array}{l} V_i = 0.4 V \\ V_i = 0.4 V \end{array}$ |

| Input current HIGH                   | l <sub>ih</sub>    | 25<br>FULL | 1<br>4    |              |                          | 10<br>20   | μΑ<br>μΑ | V <sub>i</sub> = 3.6V<br>V <sub>i</sub> = 3.6V            |

| Input impedance                      | iZ <sub>IN</sub> i | 25         | 4         |              | 3.5                      |            | kΩ       |                                                           |

| Input capacitance                    | C <sub>clk</sub>   | 25         | 4         |              | 5                        |            | рF       |                                                           |

| Maximum frequency                    | f <sub>max</sub>   | FULL       | 4         | 30           |                          |            | MHz      |                                                           |

| OF INPUT<br>(3-state control)        |                    |            |           |              |                          |            |          |                                                           |

| Input voltage LOW                    | Vil                | 25<br>FULL | 1<br>4    |              |                          | 0.8<br>0.8 | v<br>v   |                                                           |

| Input voltage HIGH                   | V <sub>ih</sub>    | 25<br>FULL | 1<br>4    | 2.0<br>2.0   |                          |            | v        |                                                           |

| Input voltage 3-STATE                | V <sub>z</sub>     | 25         | 1         |              | 1.4                      |            | v        |                                                           |

| Input current LOW                    | l <sub>iř</sub>    | 25<br>FULL | 1<br>4    | -175<br>-200 |                          |            | μΑ<br>μΑ | Vi=0.4V<br>Vi=0.4V                                        |

| Input current HIGH                   | l <sub>ih</sub>    | 25<br>FULL | 1<br>4    |              |                          | 500<br>700 | μΑ<br>μΑ | Vi=3.6V<br>Vj=3.6V                                        |

## ELECTRICAL CHARACTERISTICS:

Test conditions (unless otherwise stated): AV<sub>CC</sub>, DV<sub>CC</sub>, OV<sub>CC</sub>=5V $\pm$ 0.5V, AGND/DGND shorted together, Temp=T<sub>full</sub> =0 to + 70°C.

|                                           |                  |              |               | Value      |                          |            | Units      | Conditions                                         |

|-------------------------------------------|------------------|--------------|---------------|------------|--------------------------|------------|------------|----------------------------------------------------|

| Parameter                                 | Symbol           | Temp<br>(°C) | Test<br>level | Min        | Тур                      | Max        | Units      | Conditions                                         |

| ADCIN INPUT                               |                  |              |               |            |                          |            |            |                                                    |

| Input voltage                             | Vadc             | FULL         | 4             |            | AV <sub>CC</sub><br>1.75 |            | v          | For Code 0                                         |

| input voltage                             | V <sub>adc</sub> | FULL         | 4             |            | AV <sub>CC</sub><br>1.25 |            | v          | For Code 255                                       |

| Input voltage<br>amplitude (p–p)          | V <sub>20</sub>  | FULL         | 4             |            | 0.5                      |            | v          |                                                    |

| Input current                             | l <sub>adc</sub> | 25           | 1             |            | 1                        |            | μΑ         |                                                    |

| Input impedance                           | Zadc             | 25           | 1             |            | 14                       |            | MΩ         |                                                    |

| Input capacitance                         | C <sub>adc</sub> | 25           | 4             |            | 5                        |            | pF         |                                                    |

| DIGITAL OUTPUTS                           |                  |              |               |            |                          |            |            |                                                    |

| Output voltage LOW                        | Vol              | 25<br>FULL   | 4<br>4        |            |                          | 0.4<br>0.4 | v<br>v     | l <sub>ol=</sub> 2mA<br>l <sub>ol=</sub> 2mA       |

| Output voltage HIGH                       | V <sub>oh</sub>  | 25<br>FULL   | 1<br>4        | 2.4<br>2.4 |                          |            | v<br>v     | I <sub>oh=</sub> _0.4mA<br>I <sub>oh</sub> =−0.4mA |

| 3-STATE Output<br>current                 | loz              | 25           | 4             |            | 2                        |            | μĄ         |                                                    |

| ADC PERFORMANCE                           | [                |              |               |            |                          |            |            |                                                    |

| Static differential non –<br>linearity    | DNL              | 25<br>FULL   | 1<br>4        |            | ±0.5<br>±0.5             |            | lsb<br>Isb |                                                    |

| Static integral non –<br>linearity        | INL              | 25<br>FULL   | 1<br>4        |            | ±1<br>±1                 |            | lsb<br>Isb |                                                    |

| Dynamic integral non –<br>linearity       | INL              | 25<br>FULL   | 1<br>4        |            | ±2<br>±2                 |            | lsb<br>Isb |                                                    |

| VIDEO AMPLIFIER<br>DYNAMIC<br>PERFORMANCE |                  |              |               |            |                          |            |            |                                                    |

| -3dB Bandwidth                            | f3dB             | 25           | 4             |            | 20                       |            | MHz        |                                                    |

| Differential gain                         | Gd               | 25           | 4             |            | 2                        |            | %          |                                                    |

| Differential phase                        | Ød               | 25           | 4             |            | 2                        |            | degrees    |                                                    |

| Gain rang <del>e</del>                    | ∆G               | 25           | 4             | 3          |                          | 7          | dB         |                                                    |

| Crosstalk between<br>VIN inputs           |                  | 25           | 4             |            | -60                      |            | dB         |                                                    |

| Signal-to-noise ratio                     | SNR              | 25           | 4             |            | 55                       |            | dB         |                                                    |

| ANALOG SIGNAL*<br>PROCESSING              |                  |              |               |            |                          |            |            | *f <sub>clk</sub> = 30MHz                          |

| -3dB Bandwidth                            | f3dB             | 25           | 1             | 1          | 15                       |            | MHz        |                                                    |

| Differential gain                         | Gd               | 25           | 4             |            | 2                        |            | %          |                                                    |

| Differential phase                        | Ød               | 25           | 4             | 1          | 2                        | 1          | degrees    |                                                    |

| Total harmonic distortion                 | THD              | 25           | 4             |            | 55                       |            | dB         |                                                    |

| Supply voltage ripple rejection           | SVRR             | 25           | 4             |            | 5                        |            | %∕∨        |                                                    |

#### **ELECTRICAL CHARACTERISTICS:**

Test conditions (unless otherwise stated): AV<sub>CC</sub>, DV<sub>CC</sub>, OV<sub>CC</sub>=5V $\pm$ 0.5V, AGND/DGND shorted together, Temp=T<sub>full</sub> =0 to + 70°C.

| Parameter                         | Symbol          | Temp | Test  | Value |     |     |       |                                                                           |

|-----------------------------------|-----------------|------|-------|-------|-----|-----|-------|---------------------------------------------------------------------------|

|                                   | Symbol          | (°C) | level | Min   | Тур | Max | Units | Conditions                                                                |

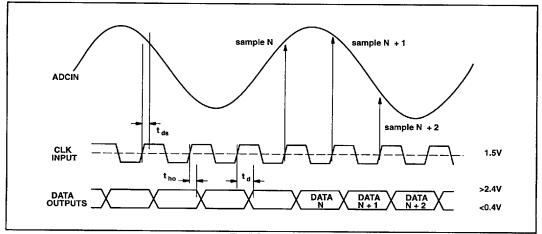

| TIMING⁺                           |                 |      |       |       | -   |     |       | * f <sub>clk</sub> ≃30MHz<br>C <sub>1</sub> =15pF<br>I <sub>0I</sub> =2mA |

| Sampling delay                    | t <sub>ds</sub> | FULL | 4     |       | 3   |     | ns    |                                                                           |

| Output hold time                  | t <sub>ho</sub> | FULL | 4     | 5     |     |     | ns    |                                                                           |

| Output delay time                 | ta              | FULL | 4     |       |     | 20  | ns    |                                                                           |

| 3 State delay time for<br>enble   | t <sub>ez</sub> | FULL | 4     |       |     | 25  | ns    |                                                                           |

| 3 State delay time for<br>disable | t <sub>dz</sub> | FULL | 4     |       |     | 25  | ns    |                                                                           |

### ELECTRICAL CHARACTERISTIC DEFINITIONS Analog –3dB Bandwidth ADC

The analog input frequency at which the spectral power of the fundamental frequency, as determined by Fast Fourier Transform analysis, is 3dB down on the DC level.

#### Differential Non–Linearity (DNL)

The deviation of any code width from an ideal 1LSB step size.

#### Integral Non–Linearity (INL)

The deviation of the centre of each code from a reference line which has been determined by a least-square curve-fit.

#### Differential Gain (G<sub>d</sub>) and Phase (O<sub>d</sub>)

The difference in gain/phase at the ADC output when a 17.5 IRE units peak to peak, 3.58MHz input signal is superimposed on a dc level at 1/16 and 15/16 full scale input.

#### Supply Voltage Rejection Ratio (SVRR)

The variation in the amplitude of the given signal when the supply voltage is changed by 1V.

#### GENERAL CIRCUIT DESCRIPTION

The VP8708 is an analog video input interface capable of digitising signals at sample rates upto 30MHz.

The multiplexer uses the logic conditions on the selection pins (IO, I1) to select one of upto three signals applied to the video inputs (VIN0, VIN1, VIN2). This signal is then clamped to the required dc level by the action of the clamp control logic. The output of the multiplexer passes through the AGC amplifier, where the gain of the signal is adjusted such that after going through the driver amplifier, the signal fills the desired portion of the ADC range. This input to the ADC also drives three reference comparators which supply the signals necessary to control the clamp and AGC circuitry.

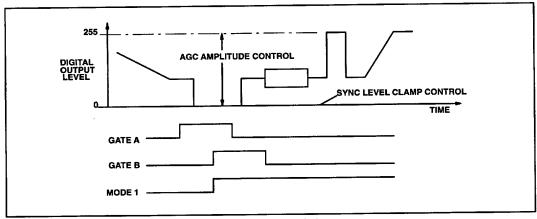

Two modes of operation are available; these being determined by the relative occurrences, during the sync and rear porch periods, of logic pulses at the GATE A and GATE B inputs.

Mode 1 (see Fig. 3) is employed initially to allow the device to reach its optimum operation point. The gain and dc level of the signal are roughly adjusted to set the sync level to ADC code 0 and the peak level to ADC code 255. This allows rapid recovery of the video synchronisation pulses.

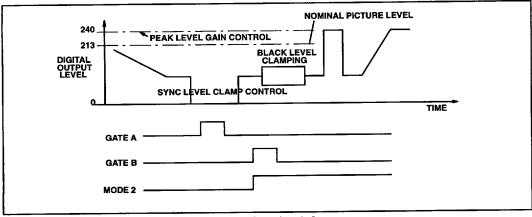

If the GATE A and GATE B pulses become distinct (see Fig. 4) then the VP8708 will switch into mode 2. In this

🖿 3768522 0024408 428 📟

#### Signal-to-Noise Ratio

The ratio of the RMS signal amplitude to the RMS value of "noise" which is defined as the sum of all other spectral components including harmonics, but excluding DC with a full-scale analog input signal.

#### Total Harmonic Distortion (THD)

The RMS addition of all peaks in a Fast Fourier Transform measurement, which occur at integer multiples of the fundamental frequency of the input signal.

#### Test Levels

| Level 1 | 100% production tested                  |

|---------|-----------------------------------------|

| Level 2 | 100% production tested at 25°C and      |

|         | sample tested at specified temperatures |

| Level 3 | Sample tested only                      |

| Level 4 | Parameter is guaranteed by design and   |

|         | characteristics testing                 |

| Level 5 | Parameter is a typical value only       |

configuration a more sophisticated control scheme is used in order to produce a 'fixed' digitised output from the device: Whilst the GATE A pulse (which must be within the sync period) is high, the sync level is adjusted to code 0, Similarly, the black level is adjusted to code 64 if the GATE B pulse occurs during the rear porch periods. Peak level control is always active such that maximum digital output will tend to lie below code 240. Nominal input signals, 1Vp-p, should have a peak output level equal to code 213.

For the device to operate, two external capacitors must be connected to the AGC and CLAMP pins. An optional external resistor may be attached to the RPEAK input to alter the maximum charge/discharge current into these capacitors. This varies the loop response time.

The format of the output data, updated at the sample rate, is determined by the logic level on the OF pin. The OF pin may also be used to force the outputs to a high impedance state.

The DEC ('decouple') pin is not connected on the VP8708. On similar devices (e.g. TDA8708) an external capacitor may be attached to this pin to stabilise the ADC reference voltage. The VP8708 has an internally stable reference and thus requires one less external component.

Fig. 3 Control mode 1

Fig. 4 Control mode 2

#### **VIDEO INPUTS**

Each of the three video inputs may be selected with the selection pins I0 and I1. Table 2 shows the action of these pins.

| 11 | 10 | SELECTED INPUTS |

|----|----|-----------------|

| 0  | 0  | VINO            |

| 0  | 1  | VIN1            |

| 1  | 0  | VIN2            |

| 1  | 1  | VIN2            |

Table 2 Video input selection

#### **OUTPUT FORMAT (OF PIN)**

The format of the output data is selectable via the OF pin as shown in Table 3. To improve noise immunity, a small (10nF) capacitor may be connected between this pin and ground if binary operation is required.

| OF   | D0 TO D7                 |  |  |  |  |

|------|--------------------------|--|--|--|--|

| 0    | Active, two's complement |  |  |  |  |

| Open | Active, binary           |  |  |  |  |

| 1    | High impedance           |  |  |  |  |

| 1    | High impedance           |  |  |  |  |

Table 3 Output format control

#### ANOUT AND ADCIN

The analog output (ANOUT) and ADC input (ADCIN) pins should have an external anti-aliasing filter connected betwen them. Care must be taken to ensure that the filter input impedance and filter output levels are in accordance with the specifications.

As an evaluatuion tool, two  $1.5k\Omega$  resistors may be used to form a potential divider between ANOUT and AV<sub>CC</sub>. The centre tap of this divider can then be used to connect the signal to ADCIN. It should be noted however, that dynamic device performance will not be maximum.

#### TIMING INFORMATION

Fig. 5 depicts the system relationship between sampling edge offset and output data.

The analog input signal is sampled  $t_{ds}$  seconds after the rising edge of the clock signal. Old data will remain valid for at

least  $t_{ho}$  and new data will become valid after at most  $t_d.$  Data may be latched on either the falling or rising edges of the clock signal.

Fig. 5 System timing

#### AGC AND CLAMP CONTOL

In both mode 1 and 2, AGC and clamp control is achieved by the charging and discharging of two external capacitors attached to the AGC and CLAMP pins. Suggested values for these capacitors are C<sub>agc</sub>=220nF and C<sub>cip</sub>=18nF.

For correct device operation, the relative occurrences of the control pulses at the GATE A and GATE B pins must be as given below:

MODE 1 – GATE A and GATE B must overlap, GATE B being delayed with respect to GATE A. This will ensure that the

signal fills the complete ADC range and thus allows quick recovery of the video sync pulses.

MODE 2 – GATE A must occur wholly within the sync period GATE B must occur wholly within the rear porch. This will tend to hold the output signal amplitude below code 240, the black level at code 64, and the sync tip at code 0.

Table 4 shows the control action of the device with reference to the logic states of the GATE A and GATE B inputs.

| GATE A | GATE B      | MODE                                                            | DIGITAL OUTPUT CODE | IAGC               | ICLP               |

|--------|-------------|-----------------------------------------------------------------|---------------------|--------------------|--------------------|

| 1      | ↑           | Device will enter mode 1                                        |                     |                    |                    |

|        |             | 1                                                               | Output >255         | -l <sub>peak</sub> | +5μΑ               |

|        |             | 1                                                               | Output <255         | +5μΑ               | -                  |

|        |             | 1                                                               | Output >0           | -                  | +5μA               |

|        |             | 1                                                               | Output <0           | +5μΑ               | -l <sub>peak</sub> |

| ↓<br>0 | 0<br>0<br>1 | This control sequence will<br>switch the device<br>into mode 2. |                     |                    |                    |

| 0      | 1           | 2                                                               | Output >240         | -l <sub>peak</sub> | +50µA              |

| 0      | 1           | 2                                                               | Output >64          | _                  | +50µA              |

| 0      | 1           | 2                                                               | Output <64          | _                  | 50µA               |

| 0      | 0           | 2                                                               | Output >240         | -l <sub>peak</sub> |                    |

| 1      | 0           | 2                                                               | Output >240         | -I <sub>peak</sub> | -                  |

| 1      | 0           | 2                                                               | Output >0           | -5μΑ               | -                  |

| 1      | 0           | 2                                                               | Output <0           | +5μΑ               |                    |

Table 4: Mode 1/Mode 2 control

| PIN | NAME             | DESCRIPTION                  |

|-----|------------------|------------------------------|

| 1   | D7               | Data Output Bit 7 (MSB)      |

| 2   | D6               | Data Output Bit 6            |

| 3   | D5               | Data Output Bit 5            |

| 4   | D4               | Data Output Bit 4            |

| 5   | CLK              | Clock Input                  |

| 6   | DV <sub>CC</sub> | Digital Supply Voltage       |

| 7   | ov <sub>cc</sub> | Output Buffer Supply Voltage |

| 8   | DGND             | Digital Ground               |

| 9   | OF               | Output Format/Chip Enable    |

| 10  | D3               | Data Output Bit 3            |

| 11  | D2               | Data Output Bit 2            |

| 12  | D1               | Data Output Bit 1            |

| 13  | DO               | Data Output Bit 0 (LSB)      |

| 14  | 10               | Input Selection Bit 0        |

| 1   |                  |                              |

#### PCB CONSTRUCTION

As with all high speed analog to digital converters, careful consideration must be given to the PCB layout.

In general, the best results will be obtained by tying all grounds to a 'solid' low impedance ground plane. Separate analog and digital ground planes will also help. Device connections to the ground plane should be as short as possible.

Supply decoupling is important when dealing with mixed analog and digital signals, it can provide a feedback path for

| PIN | NAME             | DESCRIPTION                                    |

|-----|------------------|------------------------------------------------|

| 15  | 11               | Input Selection Bit 1                          |

| 16  | VINO             | Video Input 0                                  |

| 17  | VIN1             | Video Input 1                                  |

| 18  | VIN2             | Video Input 2                                  |

| 19  | ANOUT            | Analog Output                                  |

| 20  | ADCIN            | ADC Input                                      |

| 21  | DEC              | Not Connected VP8708 is inter-<br>nally stable |

| 22  | AV <sub>CC</sub> | Analog Supply Voltage                          |

| 23  | AGND             | Analog Ground                                  |

| 24  | CLAMP            | Clamp Capacitor                                |

| 25  | AGC              | AGC Capacitor                                  |

| 26  | GATE B           | Black Level Control Pulse                      |

| 27  | GATE A           | Sync Level Control Pulse                       |

| 28  | RPEAK            | Peak Current Resistor                          |

the digital output currents. The VP8708 should therefore be decoupled as close to the supply pins as possible. Good quality, high frequency, low inductance capacitors. Isolation may be further improved by adding series inductors to the supplies.

Jitter and noise on the clock pin and its reference to ground must be minimised. Long clock lines should be avoided and all lines correctly terminated.

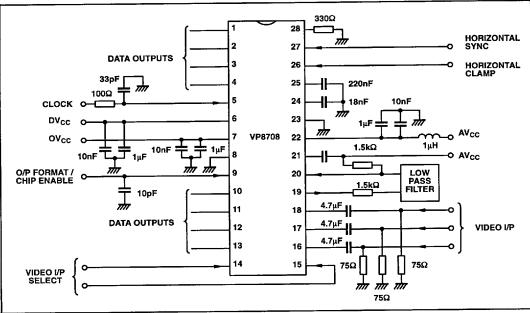

A typical application circuit is shown below.

Fig. 6 Typical application circuit

# 3768522 00244ll Tl2 🛾