Data Sheet 29319.20L

The UDN2916B, UDN2916EB, and UDN2916LB motor drivers are designed to drive both windings of a bipolar stepper motor or bidirectionally control two dc motors. Both bridges are capable of sustaining 45 V and include internal pulse-width modulation (PWM) control of the output current to 750 mA. The outputs have been optimized for a low output saturation voltage drop (less than 1.8 V total source plus sink at 500 mA).

For PWM current control, the maximum output current is determined by the user's selection of a reference voltage and sensing resistor. Two logic-level inputs select output current limits of 0, 33, 67, or 100% of the maximum level. A PHASE input to each bridge determines load current direction.

The bridges include both ground clamp and flyback diodes for protection against inductive transients. Internally generated delays prevent cross-over currents when switching current direction. Special power-up sequencing is not required. Thermal protection circuitry disables the outputs if the chip temperature exceeds safe operating limits.

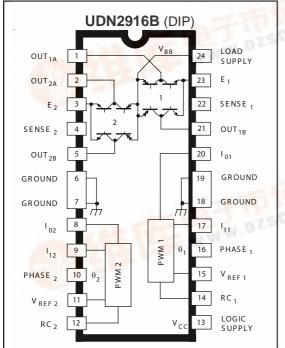

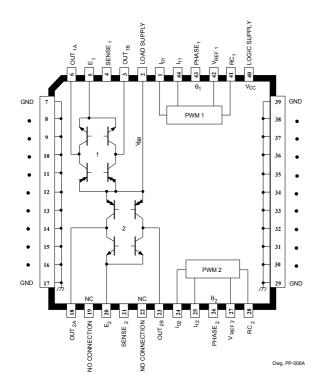

The UDN2916B is supplied in a 24-pin dual in-line plastic batwing package with a copper lead-frame and heat sinkable tabs for improved power dissipation capabilities. The UDN2916EB is supplied in a 44lead power PLCC for surface mount applications. The UDN2916LB is supplied in a 24-lead surface-mountable SOIC. Their batwing construction provides for maximum package power dissipation in the smallest possible construction. The UDN2916B, UDN2916EB, and UDN2916LB are available for operation from -20°C to 85°C. The UDQ2916B and UDQ2916LB are available for operation from -40°C to 105°C. All packages are lead (Pb) free, with 100% matte tin leadframe.

## **FEATURES**

- 45 V Output Sustaining Voltage

- Internal PWM Current Control

- Low Output Saturation Voltage

- Internal Thermal Shutdown Circuitry

- Similar to Dual PBL3717, UC3770

Dwg. PP-005

#### **ABSOLUTE MAXIMUM RATINGS** at T.≤150°C

| tor Supply Voltage, V <sub>BB</sub>               |

|---------------------------------------------------|

| tput Current, I <sub>OUT</sub>                    |

| (Peak) +1.0 A                                     |

| (Continuous) +750 mA                              |

| gic Supply Voltage, V <sub>CC</sub> 7.0 V         |

| gic Input Voltage Range,                          |

| $V_{\rm IN}$                                      |

| tput Emitter Voltage, V <sub>E</sub> <b>1.5 V</b> |

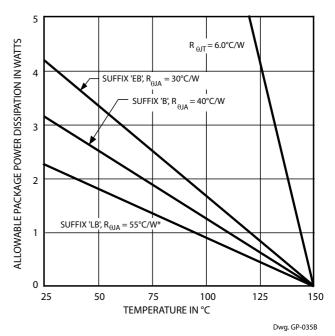

| ckage Power Dissipation,                          |

| P <sub>D</sub> See Graph                          |

| erating Temperature Range,                        |

| T 2000 to 10500                                   |

-20°C to +85°C Storage Temperature Range,

T<sub>s</sub> ..... -55°C to +150°C

Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed the specified peak current rating or a junction temperature of +150°C.

| Part Number   | Pb-free <sup>-</sup> | Package      | Packing       | Ambient<br>Temperature<br>(°C) |  |

|---------------|----------------------|--------------|---------------|--------------------------------|--|

| UDN2916B-T    | Yes                  | 24-Pin DIP   | 15 per tube   | -20 to 85                      |  |

| UDQ2916B-T    | Yes                  | 24-Pin DIP   | 15 per tube   | -40 to 105                     |  |

| UDN2916EB-T   | Yes                  | 44-Lead PLCC | 17 per tube   | -20 to 85                      |  |

| UDN2916EBTR-T | Yes                  | 44-Lead PLCC | 450 per reel  | -20 to 85                      |  |

| UDN2916LB-T   | Yes                  | 24-Lead SOIC | 31 per tube   | -20 to 85                      |  |

| UDN2916LBTR-T | Yes                  | 24-Lead SOIC | 1000 per reel | -20 to 85                      |  |

| UDQ2916LBTR-T | Yes                  | 24-Lead SOIC | 1000 per reel | -40 to 105                     |  |

### **Selection Guide**

<sup>\*</sup>Pb-based variants are being phased out of the product line. The variants cited in this footnote are in production but have been determined to be LAST TIME BUY. This classification indicates that sale of this device is currently restricted to existing customer applications. The variants should not be purchased for new design applications because obsolescence in the near future is probable. Samples are no longer available. Status change: October 31, 2006. Deadline for receipt of LAST TIME BUY orders: April 27, 2007. These variants include: UDN2916B, UDQ2916EB, UDN2916EB, UDQ2916EBTR, UDN2916EBTR, UDN2916LB, UDQ2916LBTR, and UDN2916LBTR.

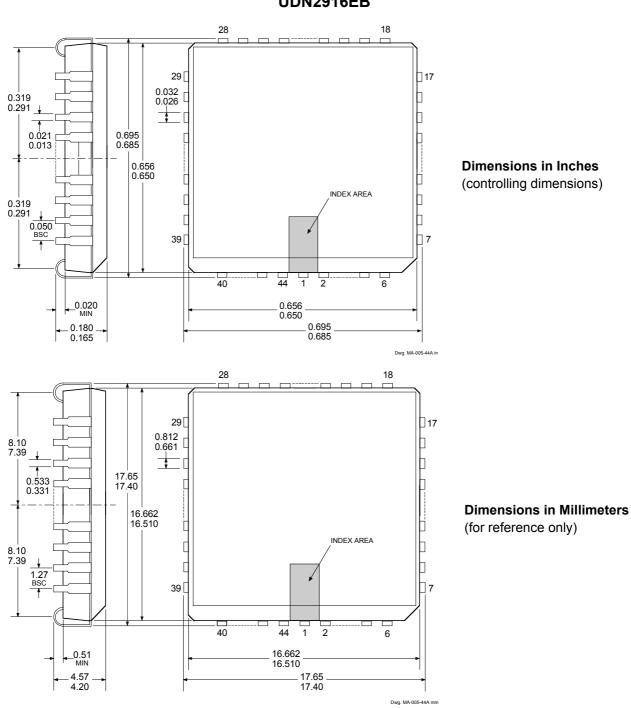

## UDN2916EB (PLCC)

UDN2916LB (SOIC)

\*Measured on a single-layer board, with 1 sq. in. of 2 oz copper area. For additional information, refer to the Allegro Web site.

#211earo

Dwg. EP-007B

SOURCE

DISABLE

⇒

Ст

ONE

SHOT

OUTB

L

Н

(14) RC

÷

# ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$ , $T_J \le 150^{\circ}C$ , $V_{BB} = 45$ V, $V_{CC} = 4.75$ V to 5.25 V, $V_{REF} = 5.0$ V (unless otherwise noted).

|                                              |                                      |                                                  | Limits |       |      |       |

|----------------------------------------------|--------------------------------------|--------------------------------------------------|--------|-------|------|-------|

| Characteristic                               | Symbol                               | Test Conditions                                  | Min.   | Тур.  | Max. | Units |

| Output Drivers ( $OUT_A \text{ or } OUT_B$ ) |                                      |                                                  |        |       |      |       |

| Motor Supply Range                           | V <sub>BB</sub>                      |                                                  | 10     | —     | 45   | V     |

| Output Leakage Current                       | I <sub>CEX</sub>                     | V <sub>OUT</sub> = V <sub>BB</sub>               | -      | < 1.0 | 50   | μA    |

|                                              |                                      | V <sub>OUT</sub> = 0                             | -      | <-1.0 | -50  | μA    |

| Output Sustaining Voltage                    | V <sub>CE(sus)</sub>                 | I <sub>OUT</sub> = ±750 mA, L = 3.0 mH           | 45     | —     | _    | V     |

| Output Saturation Voltage                    | V <sub>CE(SAT)</sub>                 | Sink Driver, I <sub>OUT</sub> = +500 mA          | -      | 0.4   | 0.6  | V     |

|                                              |                                      | Sink Driver, I <sub>OUT</sub> = +750 mA          | -      | 1.0   | 1.2  | V     |

|                                              |                                      | Source Driver, I <sub>OUT</sub> = –500 mA        | -      | 1.0   | 1.2  | V     |

|                                              |                                      | Source Driver, I <sub>OUT</sub> = –750 mA        | -      | 1.3   | 1.5  | V     |

| Clamp Diode Leakage Current                  | I <sub>R</sub>                       | V <sub>R</sub> = 45 V                            | -      | < 1.0 | 50   | μA    |

| Clamp Diode Forward Voltage                  | V <sub>F</sub>                       | l <sub>F</sub> = 750 mA                          | -      | 1.6   | 2.0  | V     |

| Driver Supply Current                        | I <sub>BB(ON)</sub>                  | Both Bridges ON, No Load                         | -      | 20    | 25   | mA    |

|                                              | I <sub>BB(OFF)</sub>                 | Both Bridges OFF                                 | -      | 5.0   | 10   | mA    |

| Control Logic                                | 1                                    | I                                                | 1      |       |      | 1     |

| Input Voltage                                | V <sub>IN(1)</sub>                   | All inputs                                       | 2.4    | _     | _    | V     |

|                                              | V <sub>IN(0)</sub>                   | All inputs                                       | -      |       | 0.8  | V     |

| Input Current                                | I <sub>IN(1)</sub>                   | V <sub>IN</sub> = 2.4 V                          | - 1    | <1.0  | 20   | μA    |

|                                              |                                      | V <sub>IN</sub> = 0.8 V                          | -      | - 3.0 | -200 | μA    |

| Reference Voltage Range                      | V <sub>REF</sub>                     | Operating                                        | 1.5    |       | 7.5  | V     |

| Current Limit Threshold<br>(at trip point)   | V <sub>REF</sub> /V <sub>SENSE</sub> | I <sub>0</sub> = I <sub>1</sub> = 0.8 V          | 9.5    | 10    | 10.5 | -     |

|                                              |                                      | I <sub>0</sub> = 2.4 V, I <sub>1</sub> = 0.8 V   | 13.5   | 15    | 16.5 | -     |

|                                              |                                      | I <sub>0</sub> = 0.8 V, I <sub>1</sub> = 2.4 V   | 25.5   | 30    | 34.5 | -     |

| Thermal Shutdown Temperature                 | TJ                                   |                                                  | - 1    | 170   |      | °C    |

| Total Logic Supply Current                   | I <sub>CC(ON)</sub>                  | I <sub>0</sub> = I <sub>1</sub> = 0.8 V, No Load | - 1    | 40    | 50   | mA    |

|                                              | I <sub>CC(OFF)</sub>                 | I <sub>0</sub> = I <sub>1</sub> = 2.4 V, No Load | -      | 10    | 12   | mA    |

| Fixed Off-Time                               | t <sub>off</sub>                     | R <sub>T</sub> = 56 kΩ, C <sub>T</sub> = 820 pF  | —      | 46    | _    | μs    |

## APPLICATIONS INFORMATION

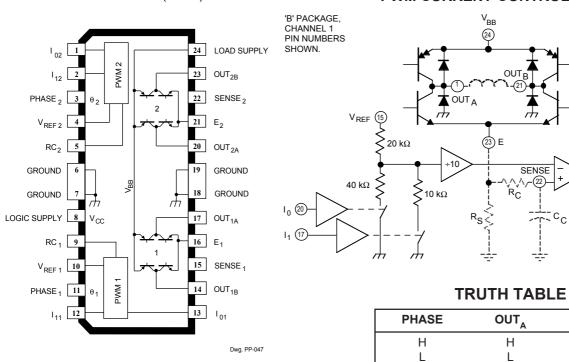

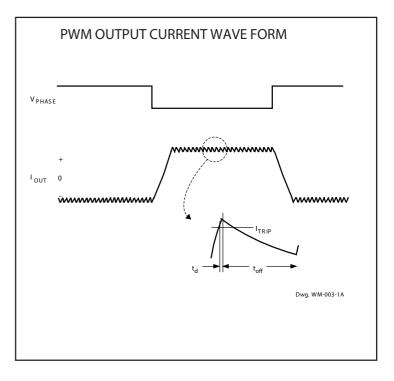

#### PWM CURRENT CONTROL

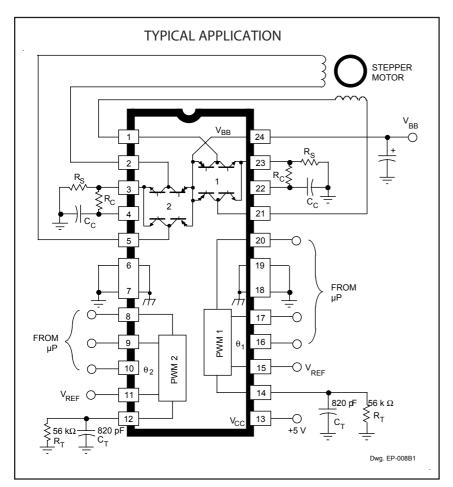

The UDN2916B/EB/LB dual bridges are designed to drive both windings of a bipolar stepper motor. Output current is sensed and controlled independently in each bridge by an external sense resistor (R<sub>s</sub>), internal comparator, and monostable multivibrator.

When the bridge is turned ON, current increases in the motor winding and it is sensed by the external sense resistor until the sense voltage ( $V_{\text{SENSE}}$ ) reaches the level set at the comparator's input:

$I_{\text{TRIP}} = V_{\text{REF}} / 10 \text{ R}_{\text{s}}$

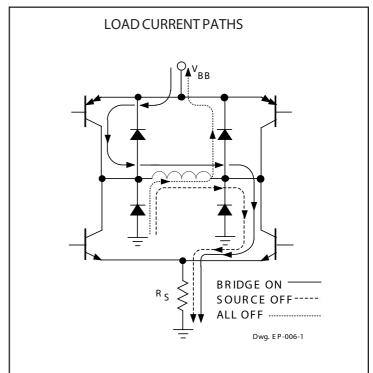

The comparator then triggers the monostable which turns OFF the source driver of the bridge. The actual load current peak will be slightly higher than the trip point (especially for low-inductance loads) because of the internal logic and switching delays. This delay (t<sub>d</sub>) is typically 2 µs. After turn-off, the motor current decays, circulating through the ground-clamp diode and sink transistor. The source driver's OFF time (and therefore the magnitude of the current decrease) is determined by the monostable's external RC timing components, where t<sub>off</sub> = R<sub>T</sub> C<sub>T</sub> within the range of 20 k  $\Omega$  to 100 k  $\Omega$  and 100 pF to 1000 pF.

The fixed-off time should be short enough to keep the current chopping above the audible range (< 46  $\mu$ s) and long enough to properly regulate the current. Because only slow-decay current control is available, short off times (< 10  $\mu$ s) require additional efforts to ensure proper current regulation. Factors that can negatively affect the ability to properly regulate the current when using short off times include: higher motor-supply voltage, light load, and longer than necessary blank time.

When the source driver is re-enabled, the winding current (the sense voltage) is again allowed to rise to the comparator's threshold. This cycle repeats itself, maintaining the average motor winding current at the desired level.

Loads with high distributed capaci-tances may result in high turn-ON current peaks. This peak (appearing across  $R_s$ ) will attempt to trip the comparator, resulting in erroneous current control or high-frequency oscillations. An external  $R_cC_c$  time delay should be used to further delay the action of the comparator. Depending on load type, many applications will not require these external components (SENSE connected to E).

#### LOGIC CONTROL OF OUTPUT CURRENT

Two logic level inputs ( $I_0$  and  $I_1$ ) allow digital selection of the motor winding current at 100%, 67%, 33%, or 0% of the maximum level per the table. The 0% output current condition turns OFF all drivers in the bridge and can be used as an OUTPUT ENABLE function.

#### CURRENT-CONTROL TRUTH TABLE

| ۱ <sub>0</sub> | I <sub>1</sub> | Output Current                                    |

|----------------|----------------|---------------------------------------------------|

| L              | L              | $V_{REF}$ /10 R $_{S}$ = I $_{TRIP}$              |

| н              | L              | $V_{REF}$ /15 R $_{S}$ = 2/3 I $_{TRIP}$          |

| L              | Н              | $V_{ m REF}$ /30 R $_{ m S}$ = 1/3 I $_{ m TRIP}$ |

| н              | Н              | 0                                                 |

These logic level inputs greatly enhance the implementation of  $\mu$ P-controlled drive formats.

During half-step operations, the I $_{_0}$  and I $_{_1}$  allow the  $\mu P$  to control the motor at a constant torque between all positions in an eight-step

sequence. This is accomplished by digitally selecting 100% drive current when only one phase is ON and 67% drive current when two phases are ON. Logic highs on both I<sub>0</sub> and I<sub>1</sub> turn OFF all drivers to allow rapid current decay when switching phases. This helps to ensure proper motor operation at high step rates.

The logic control inputs can also be used to select a reduced current level (and reduced power dissipation) for 'hold' conditions and/or increased current (and available torque) for start-up conditions.

#### GENERAL

The PHASE input to each bridge determines the direction motor winding current flows. An internally generated deadtime (approximately 2 µs) prevents crossover currents that can occur when switching the PHASE input.

All four drivers in the bridge output can be turned OFF between steps ( $I_0 = I_1 \ge 2.4 V$ ) resulting in a fast current decay through the internal output clamp and flyback diodes. The fast current decay is desirable in half-step and high-speed applications. The PHASE,  $I_0$ , and  $I_1$ inputs float high.

Varying the reference voltage (V<sub>REF</sub>) provides continuous control of the peak load current for micro-stepping applications.

Thermal protection circuitry turns OFF all drivers when the junction temperature reaches +170°C. It is only intended to protect the device from failures due to excessive junction temperature and should not imply that output short circuits are permitted. The output drivers are re-enabled when the junction temperature cools to +145°C.

The UDN2916B/EB/LB output drivers are optimized for low output saturation voltages—less than 1.8 V total (source plus sink) at 500 mA. Under normal operating conditions, when combined with the excellent thermal properties of the batwing package design, this allows continuous operation of both bridges simultaneously at 500 mA.

#### APPLICATION NOTES

#### **Current Sensing**

To minimize current sensing inaccuracies caused by ground trace IR drops, each current-sensing resistor should have a separate return to the ground terminal of the device. For low-value sense resistors, the IR drops in the PCB can be significant and should be taken into account. The use of sockets should be avoided as their contact resistance can cause variations in the effective value of R<sub>S</sub>.

Generally, larger values of R<sub>S</sub> reduce the aforementioned effects but can result in excessive heating and power loss in the sense resistor. The selected value of R<sub>S</sub> should not cause the absolute maximum voltage rating of 1.5 V, for the SENSE terminal, to be exceeded. The recommended value of R<sub>S</sub> is in the range of:

$$R_{\rm S} = 0.75 / I_{\rm TRIP}({\rm max}) \pm 50\%$$

.

If desired, the reference input voltage can be filtered by placing a capacitor from REFIN to ground. The ground return for this capacitor as well as the bottom of any resistor divider used should be independent of the high-current power-ground trace to avoid changes in REFIN due to IR drops.

#### **Thermal Considerations**

For reliable operation, it is recommended that the maximum junction temperature be kept below 110°C to 125°C. The junction temperature can be measured best by attaching a thermocouple to the power tab or batwing of the device and

measuring the tab temperature, T  $_{TAB}$  . The junction temperature can then be approximated by using the formula:

$$T_{\rm J} = T_{\rm TAB} + (2 \times I_{\rm LOAD} \times V_{\rm F} \times R_{\rm \theta JT})$$

where V<sub>F</sub> can be chosen from the electrical specification table for the given level of I<sub>LOAD</sub>. The value for R<sub> $\theta$ JT</sub> is approximately 6°C/W for both package styles.

The power dissipation of the batwing packages can be improved 20% to 30% by adding a section of printed circuit board copper (typically 6 to 18 square centimeters) connected to the batwing terminals of the device.

The thermal performance in applications that run at high load currents, high duty cycles, or both can be improved by adding external diodes from each output to ground in parallel with the internal diodes. Fast-recovery (≤200 ns) diodes should be used to minimize switching losses.

#### Load Supply Terminal

The load supply terminal, VBB, should be decoupled with an electrolytic capacitor (  $\geq 47 \mu F$  is recommended), placed as close to the device as is physically practical. To minimize the effect of system ground IR drops on the logic and reference input signals, the system ground should have a low-resistance return to the load supply voltage.

#### **Fixed Off-Time Selection**

With increasing values of t  $_{OFF}$ , switching losses decrease, low-level load current regulation improves, EMI reduces, PWM frequency decreases, and ripple current increases. The value of t<sub>OFF</sub> can be chosen for optimization of these parameters. For applications where audible noise is a concern, typical values of t<sub>OFF</sub> should be chosen in the range of 15 to 35 µs.

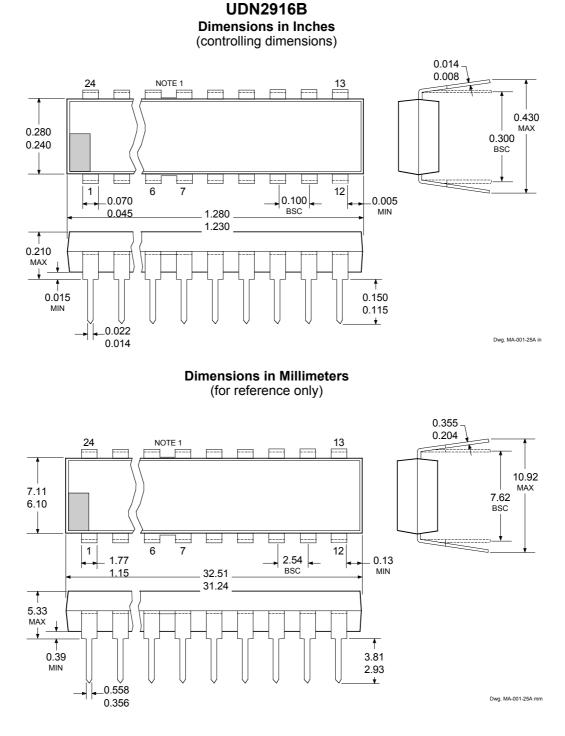

NOTES: 1. Webbed lead frame. Leads 6, 7, 18, and 19 are internally one piece.

- 2. Lead thickness is measured at seating plane or below.

- 3. Lead spacing tolerance is non-cumulative.

- 4. Exact body and lead configuration at vendor's option within limits shown.

115 Northoast Cutoff Day 15026

**UDN2916EB**

- OTES: 1. MO-047AC except for terminal shoulder height. Intended to meet new JEDEC Standard when that is approved. 2. Webbed lead frame. Leads 7-17 and 29-39 are internally one piece.

- 3. Lead spacing tolerance is non-cumulative.

- 4. Exact body and lead configuration at vendor's option within limits shown.

13 0.0125 0.0091 0.419 0.394 0.2992 0.2914 **Dimensions in Inches** (for reference only) 0.050 0.016 Н Н F Π Г 0.020 0.013 2 3 4 0.050 BSC 0.6141 0° TO 8° 0.5985 NOTE 1 NOTE 3 0.0926 0.1043 0.0040 MIN Dwg. MA-008-25A in 24 0.32 0.23 **Dimensions in Millimeters** 10.65 10.00 7.60 7.40 (controlling dimensions) 1.27 0.40 \_ Н -E H ŧ 0.51 0.33 1.27 BSC 2 3 15.60 15.20 0° то 8° NOTE 1 NOTE 3 2.65 2.35 0.10 MIN. Dwg. MA-008-25A mm

**UDN2916LB**

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the design of its products.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

- NOTES:1. Webbed lead frame. Leads indicated are internally one piece.

- 2. Lead spacing tolerance is non-cumulative.

3. Exact body and lead configuration at vendor's option within limits shown.

115 Northeast Cutoff Day 15026