## Laser Controller

### Description

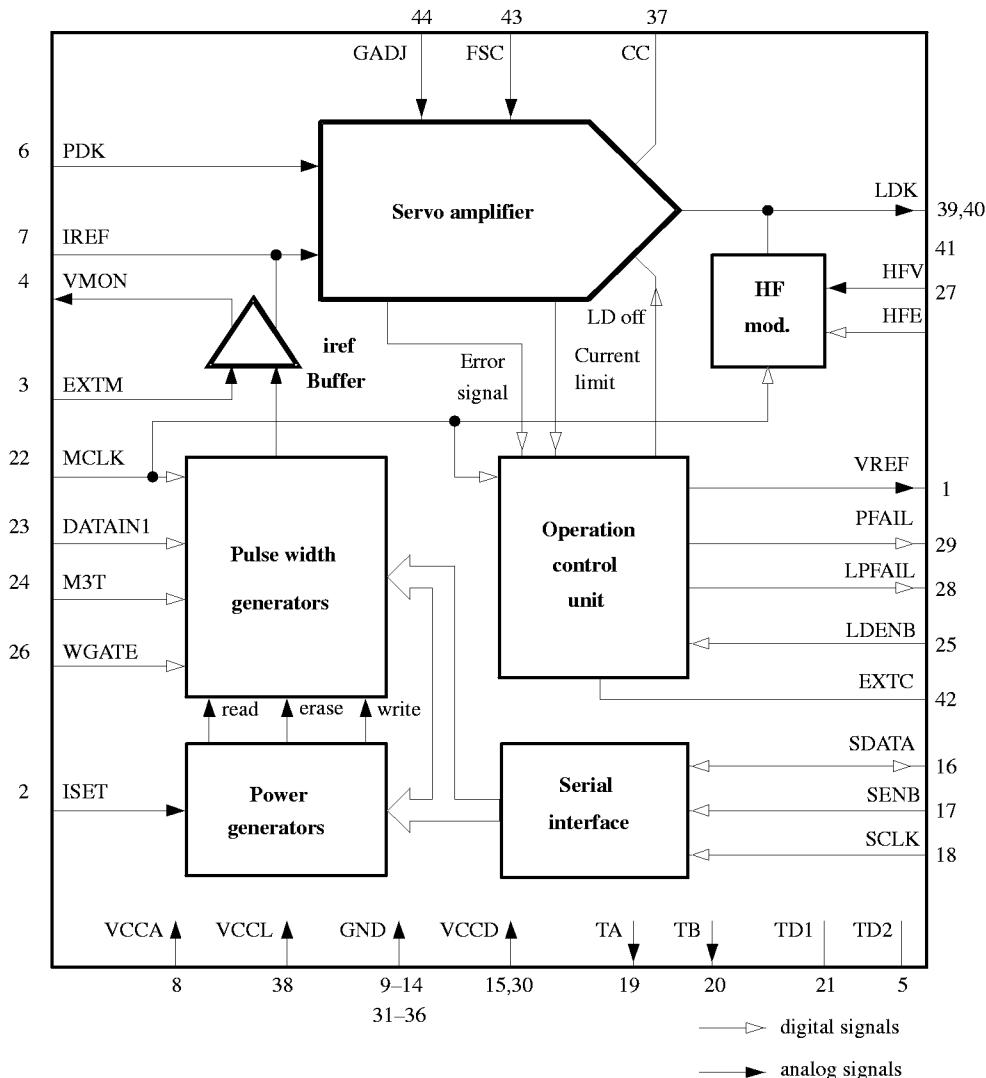

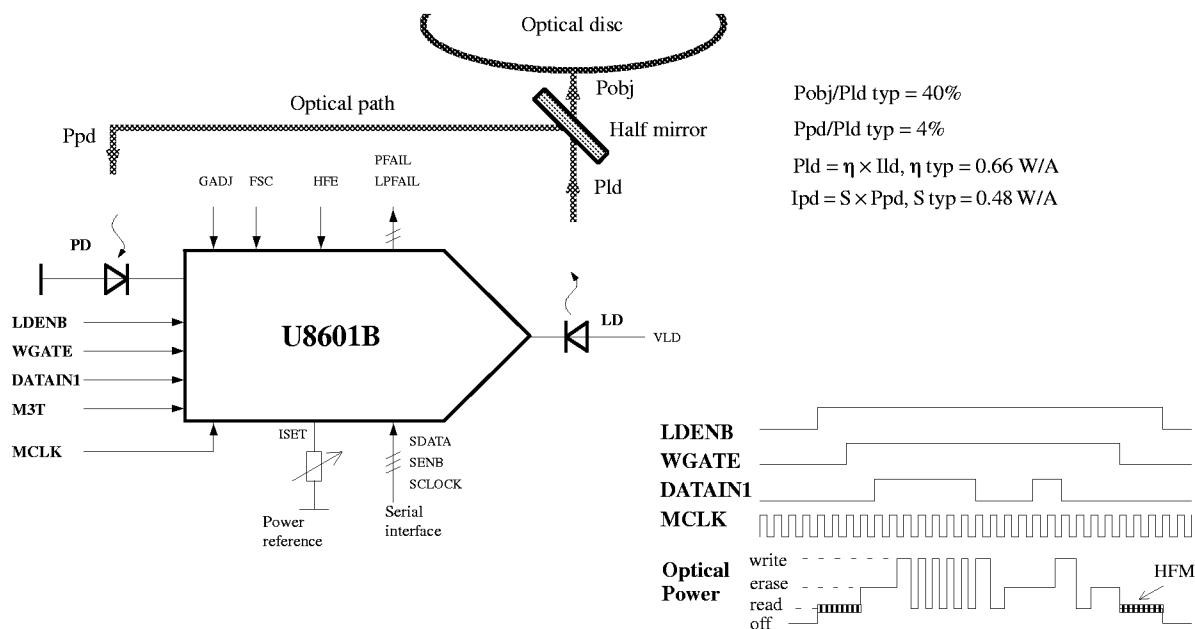

The U8601B is a very high-speed laser controller circuit for rewritable optical disk systems. It comprises servo amplifier, high frequency modulator, power generators, pulse width generators, serial interface, and operation control unit.

The wideband and high-gain **Servo Amplifier** drives the laser diode up to 180 mA. It performs noise reduction of the laser by a feedback loop via optical path and monitor diode. The reference input current for the servo loop is digitally controlled by power and pulse width generators.

For reduction of laser mode hopping noise during read mode, the **High Frequency Modulator** adds a weak modulation current with 288 to 456 MHz and a maximum swing of 5 mA.

Three **Power Generators** define read, erase, and write power levels with 4-bit resolution each.

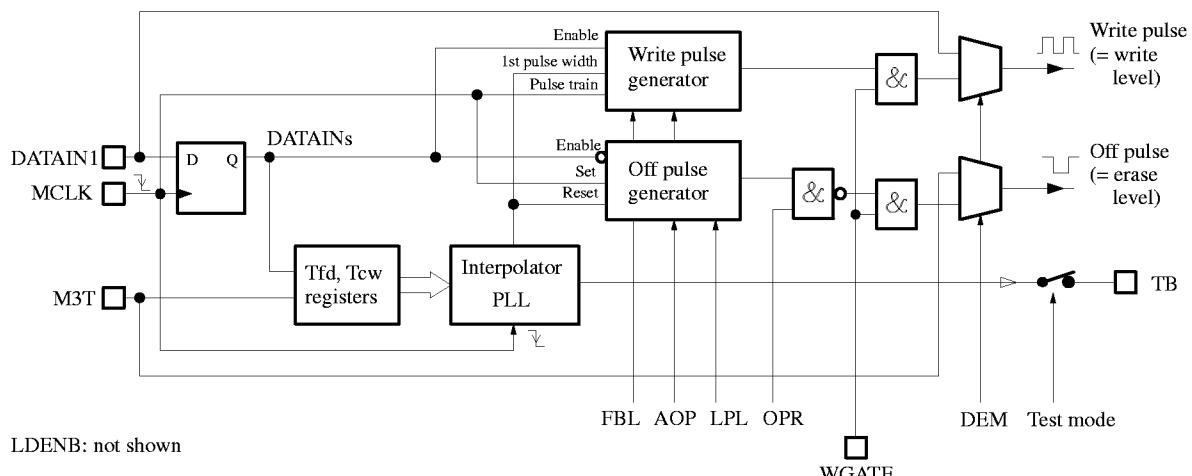

In write mode, two **Pulse Width Generators** generate write pulse trains and off pulses. Three different write

strategies are supported. The widths of the each first write pulse and of the off pulse width are variable in fractions of the master clock cycle.

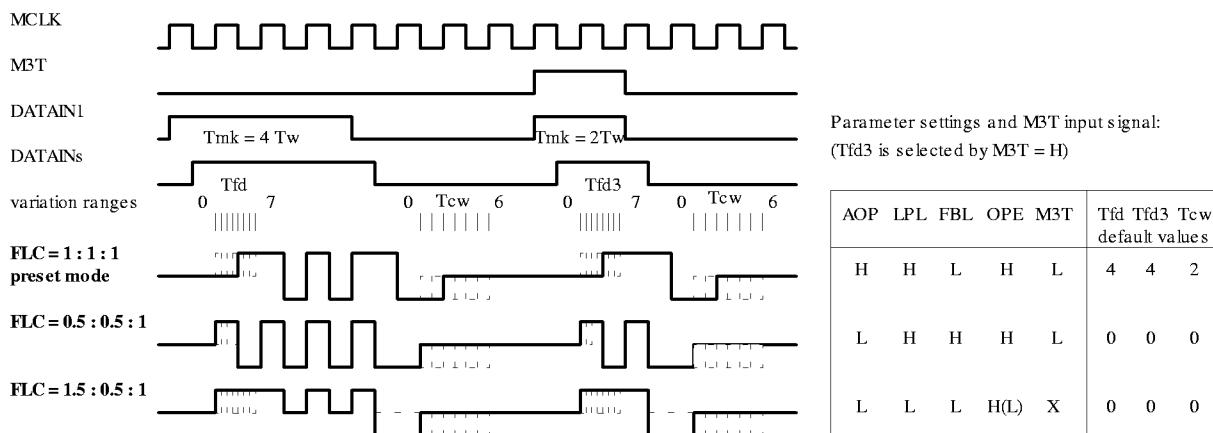

Read and write actions are controlled by write gate (WGATE), write data (DATAIN1), writing flag (M3T), and the master clock (MCLK).

Besides the built-in write pulse generation, external digital modulation (mode DEM) as well as external analog modulation (Pin EXTM) are possible.

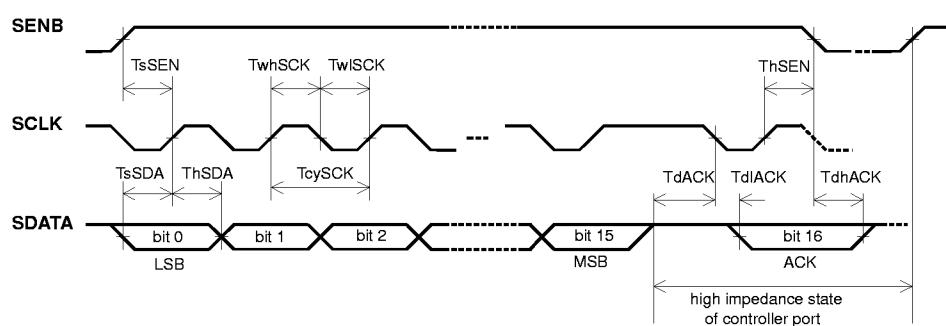

Parameters for power, pulse widths, and mode sets are programmed via the **Serial Interface**. Data packets of 16 bit length can be received with a maximum clock rate of 10 MHz. Reception is acknowledged by a 17<sup>th</sup> serial bit.

The **Operation Control Unit** supervises power supply voltage, servo amplifier error signal, current limiter status, and manages laser shutdown, slow start, and idle mode.

### Features

- Single + 5 V power supply

- Master clock range 24 MHz to 38 MHz

- Servo system

- 100 MHz closed loop bandwidth

- 110 dB DC gain

- up to 180 mA LD drive current

- 5 ns rise/fall times

- servo gain adjustable

- Noise reduction by servo loop and weak high frequency modulation

- Built-in pulse generation for DVD RAM

- supports 3 write strategies:

- FLC = 1:1:1, 1.5:0.5:1, and 0.5:0.5:1

- first write pulse width variable in Tw/8 steps

- off pulse width variable in Tw/4 steps

- OPE parameter for off pulse enable

- General purpose analog and digital modulation inputs

- On-chip generation of 3 power levels for read, erase, and write operations

- Control of power, pulse width and mode parameters by serial 3-wire interface

- External set resistor for basic power level

- Supervision of power supply, laser current and laser power

- Laser shutdown to prevent laser damage and data loss

- Idle mode for power saving

### Ordering Information

| Extended Type Number | Package | Remarks |

|----------------------|---------|---------|

| U8601B-B             | SSO44   |         |

## Block Diagram

Figure 1. Block diagram

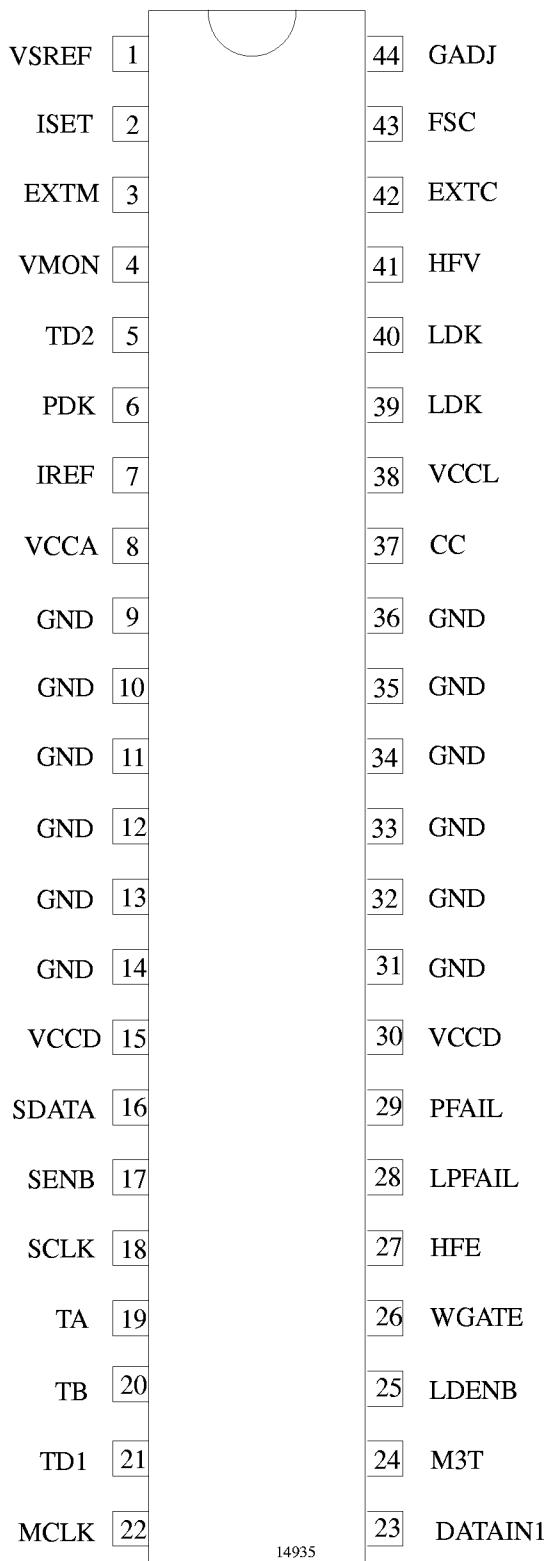

## Pin Description

| Pin   | Symbol  | Function                               |

|-------|---------|----------------------------------------|

| 1     | VREF    | Reference voltage output               |

| 2     | ISET    | Set input for basic power level        |

| 3     | EXTM    | External modulation signal input       |

| 4     | VMON    | Monitor current, servo reference       |

| 5     | TD2     | Test diode 2                           |

| 6     | PDK     | PD cathode, servo amplifier input      |

| 7     | IREF    | Connection to servo reference input    |

| 8     | VCCA    | Power supply                           |

| 9–14  | GND     | Ground & heat conduction               |

| 15    | VCCD    | Power supply                           |

| 16    | SDATA   | Serial data input                      |

| 17    | SENB    | Serial port enable input               |

| 18    | SCLK    | Serial clock input                     |

| 19    | TA      | Test output A                          |

| 20    | TB      | Test output B                          |

| 21    | TD1     | Temperature test diode 1               |

| 22    | MCLK    | Master clock input                     |

| 23    | DATAIN1 | Write data pulse and DEM input         |

| 24    | M3T     | Writing flag and DEM input             |

| 25    | LDENB   | LD control enable input                |

| 26    | WGATE   | Write mode gate input                  |

| 27    | HFE     | HFM enable input                       |

| 28    | LPFAIL  | Laser-power fail signal                |

| 29    | PFAIL   | Power-supply fail signal               |

| 30    | VCCD    | Power supply                           |

| 31–36 | GND     | Ground & heat conduction               |

| 37    | CC      | Connection to internal low-pass filter |

| 38    | VCCL    | Power supply                           |

| 39    | LDK     | LD cathode, servo amplifier output     |

| 40    | LDK     | LD cathode, servo amplifier output     |

| 41    | HFV     | HFM power-control input                |

| 42    | EXTC    | External slow starter capacitor        |

| 43    | FSC     | Frequency slope control input          |

| 44    | GADJ    | Gain adjust for servo amplifier        |

Figure 2. Pinning SSO44

## Absolute Maximum Ratings

| Parameters                                              | Symbol          | Value                | Unit |

|---------------------------------------------------------|-----------------|----------------------|------|

| Supply voltage                                          | $V_{CC}$        | -0.5 to +6.0         | V    |

| Supply voltage differences between VCCA, VCCL, and VCCD | $\Delta V_{CC}$ | $\pm 0.1$            | V    |

| Input voltage at any input                              | $V_{in}$        | -0.5 to $V_{CC}+0.5$ | V    |

| LD drive current                                        | $I_{LDK}$       | 200                  | mA   |

| Power dissipation                                       | $P_{tot}$       | 1                    | W    |

| Junction temperature                                    | $T_j$           | 125                  | °C   |

| Storage temperature range                               | $T_{stg}$       | -65 to +125          | °C   |

## Recommended Operating Conditions

| Parameters                  | Symbol    | Value        | Unit |

|-----------------------------|-----------|--------------|------|

| Supply-voltage range        | $V_{CC}$  | 4.75 to 5.25 | V    |

| Operating-temperature range | $T_{amb}$ | 0 to +75     | °C   |

## Thermal Resistance

| Parameters    | Symbol     | Value | Unit |

|---------------|------------|-------|------|

| Junction case | $R_{thJC}$ | 22    | °C/W |

## DC Characteristics

$V_{CCA} = V_{CCL} = V_{CCD} = 5$  V,  $T_{amb} = 25$  °C, unless otherwise specified

| Parameters                                                                                                                                         | Test Conditions / Pins              | Symbol       | Min.                             | Typ. | Max. | Unit  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------|----------------------------------|------|------|-------|

| <b>Power supply</b>                                                                                                                                |                                     |              |                                  |      |      |       |

| Idle mode, $VH = 5$ V, $VE = 0$ V, $LDENB = \text{low}$                                                                                            |                                     |              |                                  |      |      |       |

| Supply current, $V_{CCA}$                                                                                                                          | Pin 8                               | $I_{iVCCA}$  |                                  | 9    |      | mA    |

| Supply current, $V_{CCL}$                                                                                                                          | Pin 38                              | $I_{iVCCL}$  |                                  | 5    |      | mA    |

| Supply current, $V_{CCD}$                                                                                                                          | Pins 15 and 30                      | $I_{iVCCD}$  |                                  | 7    |      | mA    |

| Active mode,<br>$LDENB = HFE = \text{high}$ , $WGATE = \text{low}$ , power data = preset, $RSET = 11.2$ kΩ, $f_{MCLK} = 24$ MHz, $I_{LDK} = 50$ mA |                                     |              |                                  |      |      |       |

| Supply current, $V_{CCA}$                                                                                                                          | Pin 8                               | $I_{VCCA}$   | 40                               | 48   | 52   | mA    |

| Supply current, $V_{CCL}$                                                                                                                          | Pin 38                              | $I_{VCCL}$   | 18                               | 26   | 32   | mA    |

| Supply current, $V_{CCD}$                                                                                                                          | Pins 15 and 30                      | $I_{VCCD}$   | 18                               | 27   | 32   | mA    |

| Supply current vs. $I_{LDK}$                                                                                                                       | $I_{LDK} > 50$ mA                   | Pin 38       | $\Delta I_{LDK}/\Delta I_{VCCL}$ | 0.04 |      | mA/mA |

| <b>Servo amplifier</b>                                                                                                                             |                                     |              |                                  |      |      |       |

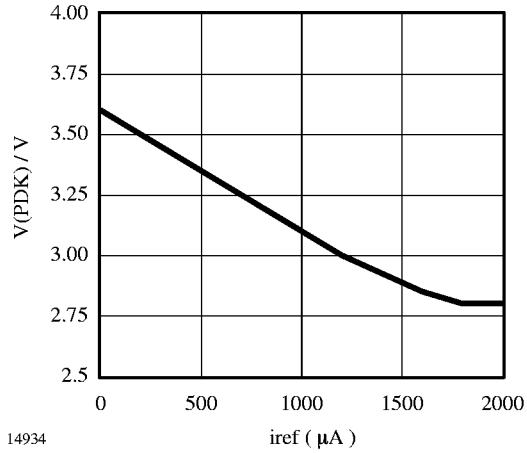

| Bias voltage                                                                                                                                       | Figure 13                           | Pin 6        | $V_{PDK}$                        | 2.5  |      | V     |

| Temperature drift                                                                                                                                  | $i_{ref} \geq 50$ μA                | Pin 6        | $\Delta V_{PDK}$                 |      | 0.8  | mV/°C |

| Offset voltage                                                                                                                                     |                                     | Pins 6 and 7 | $V_{PDK} - V_{IREF}$             | -5   |      | mV    |

| Offset current                                                                                                                                     | $i_{ref} = 0$ μA, $I_{LDK} = 50$ mA | Pin 6        | $I_{offPDK}$                     | -5   |      | μA    |

| Input voltage range                                                                                                                                |                                     | Pin 43       | $V_{FSC}$                        | 1.5  |      | V     |

|                                                                                                                                                    |                                     | Pin 44       | $V_{GADJ}$                       | 1.5  |      | V     |

| Bias voltage                                                                                                                                       |                                     | Pin 37       | $V_{CC}$                         |      | 2.5  | V     |

## DC Characteristics (continued)

VCCA = VCCL = VCCD = 5 V, T<sub>amb</sub> = 25°C, unless otherwise specified

| Parameters                                                        | Test Conditions / Pins       | Symbol                                    | Min.               | Typ. | Max. | Unit |       |

|-------------------------------------------------------------------|------------------------------|-------------------------------------------|--------------------|------|------|------|-------|

| Limiting current                                                  | Pins 39 and 40               | I <sub>LDKlim</sub>                       | 180                |      | 300  | mA   |       |

| Voltage compliance                                                | Pins 39 and 40               | V <sub>LDK</sub>                          | 1.0                |      | 5.5  | V    |       |

| <b>i<sub>ref</sub> buffer</b>                                     |                              |                                           |                    |      |      |      |       |

| Voltage compliance                                                | Pin 4                        | V <sub>VMON</sub>                         | 3.5                |      |      | V    |       |

| Bias voltage                                                      | I <sub>EXTM</sub> = 1 mA     | Pin 3                                     | V <sub>EXTM</sub>  | 0.8  |      | V    |       |

| Input current                                                     | Pin 3                        | I <sub>EXTM</sub>                         |                    |      | 2    | mA   |       |

| Current ratio                                                     | Pin 3                        | i <sub>ref</sub> /<br>I <sub>EXTM</sub>   |                    | 0.6  | 0.8  | –    |       |

| <b>HF modulator</b>                                               |                              |                                           |                    |      |      |      |       |

| Bias voltage                                                      | Pin 41                       | V <sub>HFV</sub>                          |                    | 1.6  |      | V    |       |

| Input current                                                     | Pin 41                       | I <sub>HFV</sub>                          |                    | 1    |      | mA   |       |

| Current ratio,<br>output current swing /<br>control input current | Pins 40 and 41               | i <sub>LDKhfm</sub> /<br>I <sub>HFV</sub> |                    | 6    |      | –    |       |

| <b>Power generators RSET = 11.2 kΩ</b>                            |                              |                                           |                    |      |      |      |       |

| Offset voltage                                                    | Pins 1 and 2                 | V <sub>ISET</sub> –<br>V <sub>VREF</sub>  | -3                 |      | 3    | mV   |       |

| External resistor                                                 | l <sub>offset</sub> < 3 mV   | Pin 2                                     | R <sub>SET</sub>   |      | 11.2 | kΩ   |       |

|                                                                   | l <sub>offset</sub> < 50 mV  | Pin 2                                     | R <sub>SET</sub>   | 7    |      | kΩ   |       |

| Temperature drift of i <sub>ref</sub>                             | Pin 4                        | ΔV <sub>VMON</sub>                        |                    | 0.3  |      | %/°C |       |

| Read level, LSB                                                   | Pin 4                        | I <sub>r1</sub>                           | 2                  | 4    | 6    | μA   |       |

| Read level,<br>rdata = 9 (preset)                                 | Pin 4                        | I <sub>r9</sub>                           | 32                 |      | 40   | μA   |       |

| Erase level, LSB                                                  | Pin 4                        | I <sub>e1</sub>                           | 12                 | 16   | 20   | μA   |       |

| Erase level,<br>edata = 9 (preset)                                | Pin 4                        | I <sub>e9</sub>                           | 128                |      | 160  | μA   |       |

| Write level, LSB                                                  | Pin 4                        | I <sub>w1</sub>                           | 21                 | 28   | 35   | μA   |       |

| Write level,<br>wdata = 9 (preset)                                | Pin 4                        | I <sub>w9</sub>                           | 238                |      | 266  | μA   |       |

| Offset current, read level                                        | WGATE = 0                    | I <sub>r0</sub>                           |                    |      | 0.3  | μA   |       |

| Offset current, erase level                                       | WGATE = 1                    | I <sub>e0</sub>                           |                    |      | 0.8  | μA   |       |

| Ratio, erase/read level                                           | Preset levels                | i <sub>e</sub> /i <sub>r</sub>            | 3.7                | 4    | 4.3  | –    |       |

| Ratio, write/read level                                           | Preset levels                | i <sub>w</sub> /i <sub>r</sub>            | 6.3                | 7    | 7.7  | –    |       |

| <b>Reference voltage</b>                                          |                              |                                           |                    |      |      |      |       |

| Output voltage                                                    | Pin 1                        | V <sub>VREF</sub>                         | 2.4                | 2.5  | 2.6  | V    |       |

| Temperature drift                                                 | T <sub>amb</sub> = 0 to 75°C | Pin 1                                     | TD <sub>VREF</sub> | -200 |      | 200  | μV/°C |

| Power supply rejection<br>ratio                                   | VCC = 4.5 to 5.5 V           | Pin 1                                     | PSRR               | -20  |      | 20   | mV/V  |

| Source resistance                                                 | Pin 1                        | r <sub>VREF</sub>                         |                    |      | 10   | Ω    |       |

| Limiting current                                                  | Pin 1                        | I <sub>VREFlim</sub>                      | 3                  |      | 10   | mA   |       |

## DC Characteristics (continued)

VCCA = VCCL = VCCD = 5 V, T<sub>amb</sub> = 25°C, unless otherwise specified

| Parameters                                                                     | Test Conditions / Pins   | Symbol                              | Min.                | Typ. | Max. | Unit  |

|--------------------------------------------------------------------------------|--------------------------|-------------------------------------|---------------------|------|------|-------|

| <b>Operation control unit</b>                                                  |                          |                                     |                     |      |      |       |

| Lower supply threshold voltage                                                 |                          | VCCthl                              | 4.5                 |      | 4.75 | V     |

| Upper supply threshold voltage                                                 |                          | VCCthh                              | 5.25                |      | 5.6  | V     |

| Supply voltage for power supply fail detection                                 |                          | VCCfail                             | 1.5                 |      | 7    | V     |

| Threshold for current limit switch-off                                         |                          | I <sub>LDKswoff</sub>               | 170                 |      | 280  | mA    |

| Switch-on current limit                                                        |                          | I <sub>LDKswon</sub>                |                     |      | 120  | mA    |

| Threshold for loop error switch-off                                            |                          | I <sub>PDK</sub> / i <sub>ref</sub> |                     | 1.5  |      | –     |

| <b>Slow starter</b>                                                            |                          |                                     |                     |      |      |       |

| Bias voltage, high status                                                      | Pin 42                   | V <sub>EXTChi</sub>                 |                     | 3.0  |      | V     |

| Saturation voltage, low status                                                 | I <sub>load</sub> = 2 mA | Pin 42                              | V <sub>EXTClo</sub> | 1    | 1.5  | V     |

| Charge current                                                                 | Pin 42                   | I <sub>EXTC</sub>                   | 9                   | 17   |      | μA    |

| <b>Digital inputs SDATA, SENB, SCLK, MCLK, DATAIN1, M3T, LDENB, WGATE, HFE</b> |                          |                                     |                     |      |      |       |

| L-input voltage                                                                |                          | V <sub>IL</sub>                     |                     |      | 0.8  | V     |

| H-input voltage                                                                |                          | V <sub>IH</sub>                     | 3.5                 |      |      | V     |

| Threshold voltage                                                              |                          | V <sub>th</sub>                     |                     | 2.5  |      | V     |

| L-input current                                                                |                          | I <sub>IL</sub>                     | -70                 |      |      | μA    |

| H-input current                                                                |                          | I <sub>IH</sub>                     |                     |      | 70   | μA    |

| <b>Open collector outputs PFAIL, LPFAIL</b>                                    |                          |                                     |                     |      |      |       |

| L-output voltage                                                               | I <sub>OL</sub> = 1 mA   | V <sub>OL</sub>                     |                     |      | 0.6  | V     |

| L-output current                                                               |                          | I <sub>OL</sub>                     |                     |      | 1    | mA    |

| Output leakage current                                                         |                          | I <sub>OH</sub>                     |                     |      | 10   | μA    |

| <b>Open collector output SDATA (acknowledge output)</b>                        |                          |                                     |                     |      |      |       |

| L-output voltage                                                               | R <sub>L</sub> = 2 kΩ    | V <sub>OL</sub>                     |                     |      | 0.6  | V     |

| L-output current                                                               |                          | I <sub>OL</sub>                     |                     |      | 3    | mA    |

| <b>Test outputs TA, TB</b>                                                     |                          |                                     |                     |      |      |       |

| Voltage range                                                                  |                          | dVO                                 | 3                   |      | 5    | V     |

| Source resistance                                                              |                          | R <sub>O</sub>                      |                     | 10   |      | kΩ    |

| <b>Temperature test diode TD1</b>                                              |                          |                                     |                     |      |      |       |

| Diode voltage                                                                  | I <sub>d</sub> = 100 μA  | V <sub>d</sub>                      |                     | 750  |      | mV    |

| Temperature dependancy                                                         |                          | ΔV <sub>d</sub> /Δθ                 |                     | 1.5  |      | mV/°C |

| Bias current                                                                   |                          | I <sub>d</sub>                      |                     |      | 300  | μA    |

## AC Characteristics

VCCA = VCCL = VCCD = 5 V, T<sub>amb</sub> = 25°C, unless otherwise specified

| Parameters                                                                                              | Test Conditions / Pins                                                                    | Symbol             | Min. | Typ.      | Max. | Unit  |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|------|-----------|------|-------|

| <b>Servo amplifier</b>                                                                                  |                                                                                           |                    |      |           |      |       |

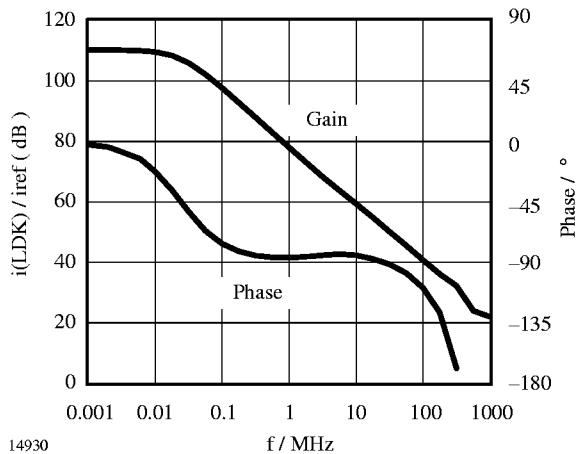

| Open loop parameters                                                                                    | Without LD,<br>I <sub>LDK</sub> = 100 mA                                                  |                    |      |           |      |       |

| DC gain                                                                                                 | V <sub>GADJ</sub> = V <sub>FSC</sub> = 2.5 V                                              | g <sub>DC</sub>    |      | 110       |      | dB    |

| Low frequency pole                                                                                      | V <sub>FSC</sub> = 2.5 V                                                                  | f <sub>PLF</sub>   |      | 60        |      | kHz   |

| High frequency pole                                                                                     | V <sub>GADJ</sub> = 2.5 V                                                                 | f <sub>PHF</sub>   |      | 10        |      | MHz   |

| High frequency gain                                                                                     | V <sub>GADJ</sub> = 2.5 V,<br>f = 100 MHz                                                 | g <sub>HF</sub>    |      | 42        |      | dB    |

| Phase margin                                                                                            | V <sub>GADJ</sub> = 2.5 V,<br>C <sub>PDK</sub> = C <sub>REF</sub> = 10 pF,<br>f = 100 MHz | Δφ                 |      | 70        |      | °     |

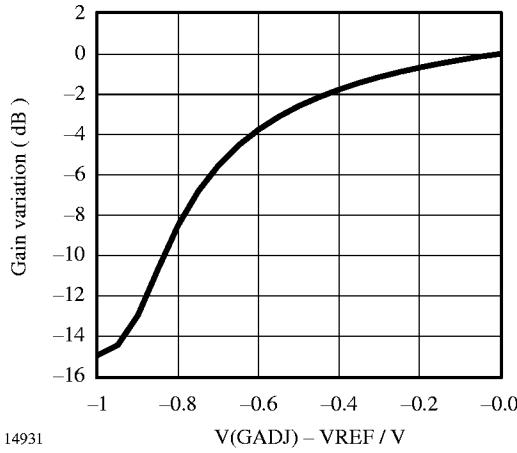

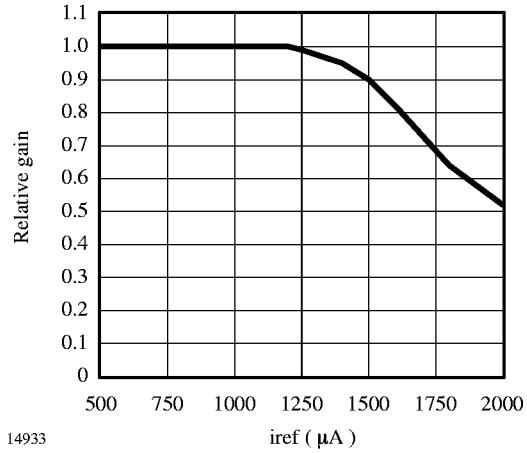

| Gain adjust range                                                                                       | V <sub>GADJ</sub> = 1.5 V to 2.5 V,<br>see figure 15                                      | Δg                 |      | 14        |      | dB    |

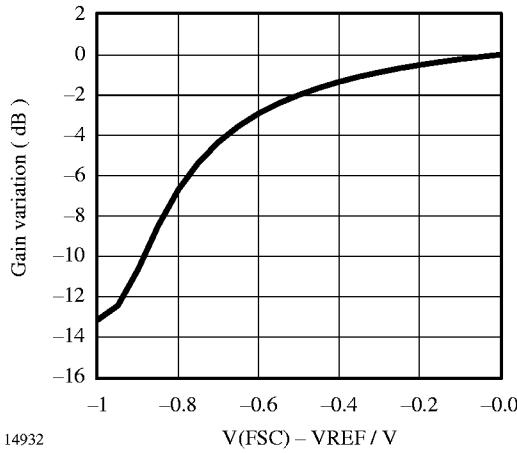

| Low frequency gain adjust range                                                                         | V <sub>FSC</sub> = 1.5 V to 2.5 V,<br>see figure 16                                       | Δg <sub>LF</sub>   |      | 12        |      | dB    |

| <b>Circuit parameters</b>                                                                               |                                                                                           |                    |      |           |      |       |

| Impedance                                                                                               | Pin 37                                                                                    | r <sub>CC</sub>    |      | 312    50 |      | Ω//pF |

| Series inductance                                                                                       | Pin 37                                                                                    | l <sub>CC</sub>    |      | 6         |      | nH    |

| Input dynamic range                                                                                     | 10% compression for max,<br>see figure 17                                                 | i <sub>ref</sub>   | 15   |           | 1000 | μA    |

| <b>Optical pulse parameters</b> V <sub>GADJ</sub> and V <sub>FSC</sub> adjusted for optimal pulse shape |                                                                                           |                    |      |           |      |       |

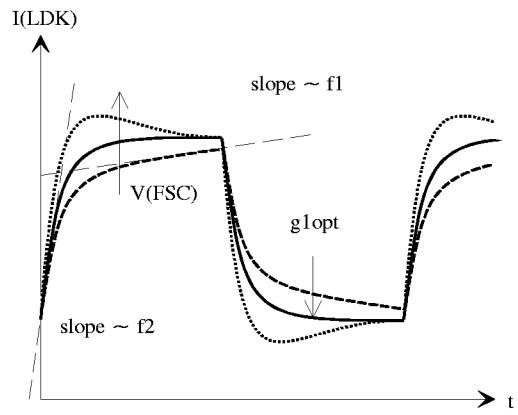

| Rise time                                                                                               | 10% → 90%                                                                                 | T <sub>r</sub>     |      | 5         |      | ns    |

| Fall time                                                                                               | 90% → 10%                                                                                 | T <sub>f</sub>     |      | 5         |      | ns    |

| Settling time to 5%                                                                                     |                                                                                           | T <sub>set</sub>   |      | 20        |      | ns    |

| Overshoot                                                                                               |                                                                                           | A <sub>os</sub>    |      | 15        |      | %     |

| <b>HF modulator</b>                                                                                     |                                                                                           |                    |      |           |      |       |

| Modulation frequency                                                                                    | f <sub>MCLK</sub> = 24 MHz                                                                | f <sub>mod</sub>   |      | 288       |      | MHz   |

|                                                                                                         | f <sub>MCLK</sub> = 38 MHz                                                                | f <sub>mod</sub>   |      | 456       |      | MHz   |

| Output current swing                                                                                    | I <sub>HFV</sub> = 833 μA                                                                 | I <sub>LDKpp</sub> |      | 5         |      | mA    |

| Switch-off attenuation                                                                                  |                                                                                           | a <sub>off</sub>   | 30   |           |      | dB    |

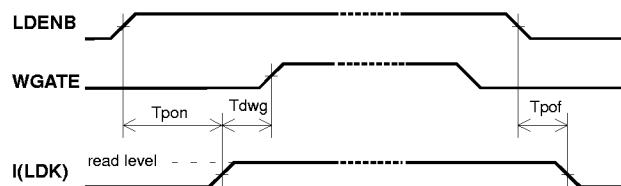

| <b>LDENB</b> see figure 3                                                                               |                                                                                           |                    |      |           |      |       |

| Slow starter delay                                                                                      | CEXT = 10 nF                                                                              | T <sub>pon</sub>   |      | 2         |      | ms    |

| Switch-off delay                                                                                        | CEXT = 10 nF                                                                              | T <sub>pooff</sub> |      | 100       |      | ns    |

| Delay time WGATE                                                                                        |                                                                                           | T <sub>dwg</sub>   | 200  |           |      | ns    |

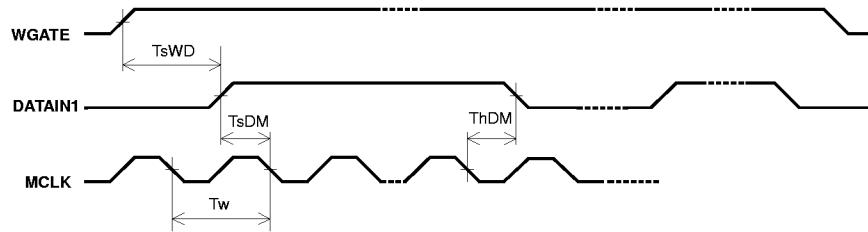

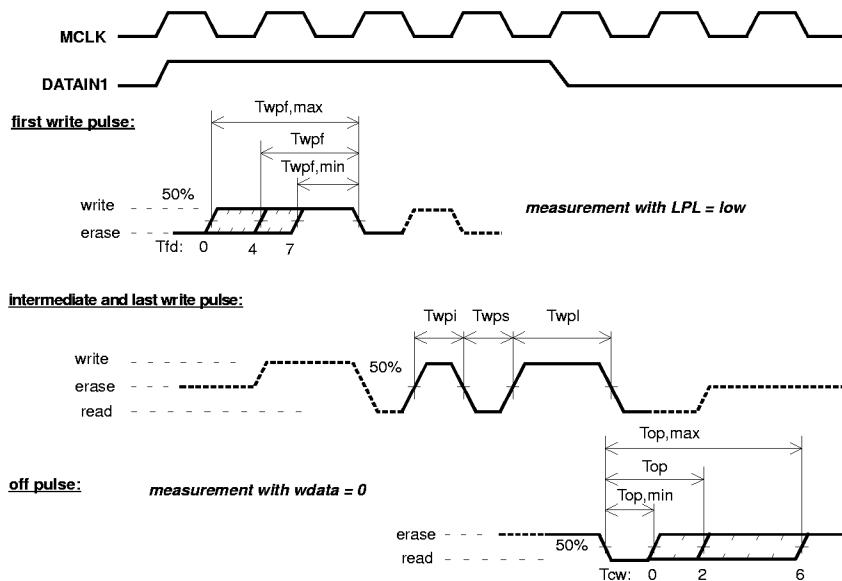

| <b>WGATE, DATAIN1, MCLK</b> see figure 4                                                                |                                                                                           |                    |      |           |      |       |

| WGATE set-up time                                                                                       |                                                                                           | T <sub>sWD</sub>   | 340  |           |      | ns    |

| DATAIN1 set-up time                                                                                     |                                                                                           | T <sub>sDM</sub>   | 10   |           |      | ns    |

| DATAIN1 hold time                                                                                       |                                                                                           | T <sub>hDM</sub>   | 10   |           |      | ns    |

| Period of MCLK                                                                                          |                                                                                           | T <sub>w</sub>     | 26   |           | 42   | ns    |

| Duty cycle of MCLK                                                                                      |                                                                                           | D <sub>CM</sub>    | 45   |           | 55   | %     |

| Parameters                                                     | Test Conditions / Pins                   | Symbol            | Min.       | Typ. | Max. | Unit    |

|----------------------------------------------------------------|------------------------------------------|-------------------|------------|------|------|---------|

| <b>LDK write pulse widths</b> $f_{MCLK} = 24$ MHz see figure 5 |                                          |                   |            |      |      |         |

| Width of first write pulse, $T_{fd} = 4$                       | $T_{DATAIN1} > 2$ Tw,<br>LPL = low       | $T_{wpf}$         | 39         | 41.6 | 44   | ns      |

| Width range of first write pulse, $T_{fd} = 0$ to 7            | $T_{DATAIN1} > 2$ Tw,<br>LPL = low       | $T_{wpf-min,max}$ | 44         |      | 65   | ns      |

| Width increment of first write pulse                           | LPL = low                                | $\Delta T_{wpf}$  | 3          | 5.2  | 7    | ns      |

| Width of last write pulse                                      | AOP = LPL = high                         | $T_{wpL}$         | 39         | 41.6 | 44   | ns      |

| Width of intermediate write pulses                             | AOP = LPL = high                         | $T_{wpI}$         | 18         | 20.8 | 23   | ns      |

| Duty cycle of intermediate write pulses                        | $f_{MCLK} = 38$ MHz,<br>AOP = LPL = high | $DC_{wp}$         | 40         |      | 60   | %       |

| <b>LDK off pulse widths</b>                                    |                                          |                   |            |      |      |         |

| Width, $T_{cw} = 2$                                            | AOP = LPL = high,<br>wdata = 0           | Top               | 39         | 41.6 | 44   | ns      |

| Width range, $T_{cw} = 0$ to 6                                 | AOP = LPL = high,<br>wdata = 0           | Top-min,max       | 19         |      | 86   | ns      |

| Width increment of off pulse                                   |                                          | $\Delta Top$      | 8          | 10.4 | 13   | ns      |

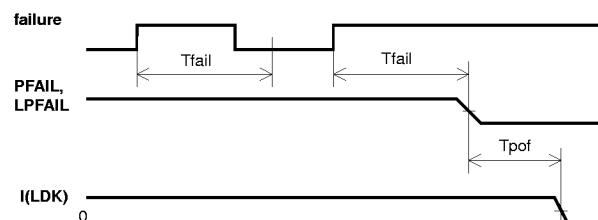

| <b>Operation control unit</b> see figure 6                     |                                          |                   |            |      |      |         |

| Fail period                                                    | $f_{MCLK} = 24$ MHz                      | $T_{fail1}$       |            | 5.3  |      | $\mu$ s |

|                                                                | $f_{MCLK} = 38$ MHz                      | $T_{fail2}$       |            | 3.4  |      | $\mu$ s |

| Master clock fail                                              | LPFAIL = low                             | Pin 28            | $f_{MCLK}$ |      | 15   | MHz     |

| <b>Serial interface</b> see figure 7                           |                                          |                   |            |      |      |         |

| SCLK pulse cycle                                               | Pin 18                                   | $T_{cySCK}$       | 100        |      |      | ns      |

| SCLK pulse width high                                          | Pin 18                                   | $T_{whSCK}$       | 40         |      |      | ns      |

| SCLK pulse width low                                           | Pin 18                                   | $T_{wlSCK}$       | 40         |      |      | ns      |

| SENB set up time                                               | Pins 18 and 17                           | $T_{sSEN}$        | 20         |      |      | ns      |

| SENB hold time                                                 | Pins 18 and 17                           | $T_{hSEN}$        | 20         |      |      | ns      |

| SDATA set up time                                              | Pins 16 and 18                           | $T_{sSDA}$        | 15         |      |      | ns      |

| SDATA hold time                                                | Pins 16 and 18                           | $T_{hSDA}$        | 15         |      |      | ns      |

| Acknowledge time margin                                        | Pins 16 and 18                           | $T_{dACK}$        | 0          |      |      | ns      |

| Acknowledge low level delay                                    | Pins 16 and 18                           | $T_{dlACK}$       | 10         |      | 50   | ns      |

| Acknowledge high level delay                                   | $C_{load} = 20$ pF<br>Pins 16 and 17     | $T_{dhACK}$       |            |      | 100  | ns      |

## Timing Diagrams

Figure 3. LDENB

Figure 4. DATAIN1

Figure 5. LDK pulses

Figure 6. Failures

Figure 7. Serial interface

## General

Figure 8. Simplified functional diagram

Figure 9. Write schemes

## Glossary

**MCLK:** Master Clock

**M3T:** writing 3T Mark

**DATAIN1:** NRZ Data Input

**DATAINs:** internal synchronized data

**FLC:** Widths of First-/Last-/Cool-Pulse

**AOP:** Add One Pulse

**LPL:** Lower Pulse-chain Level

**FBL:** First Bottom Level

**OPE:** Off Pulse Enable

## Detailed Description

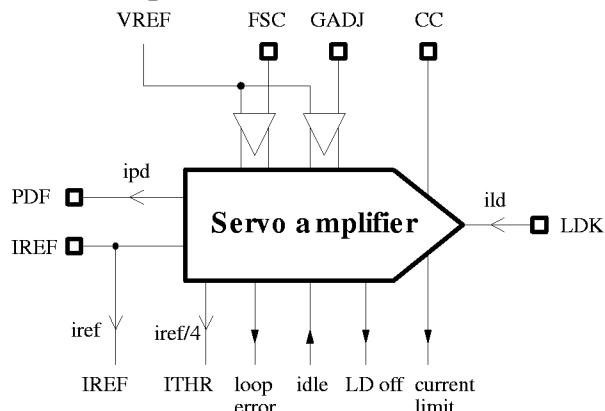

### Servo Amplifier

Figure 10. Block diagram

### Amplifier

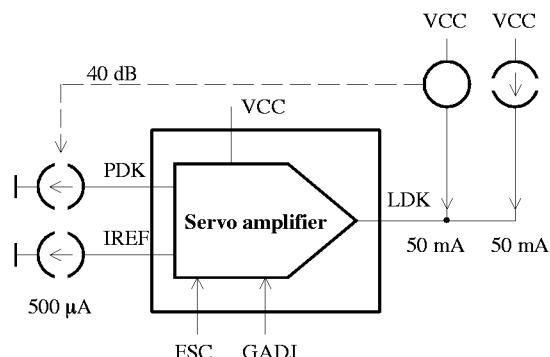

The servo amplifier drives the optical power of the laser diode according to the reference current,  $i_{ref}$ . The feedback loop is closed through the optical path and the photo diode which monitors the actual laser power.

The comparison of photo current,  $ipd$ , and reference current,  $i_{ref}$ , is performed within a transimpedance input stage, yielding low input impedance and biasing voltage for the operation of the grounded photo diode. For symmetry reasons a capacitor should be connected to the Pin IREF, corresponding to the total capacitance of photo diode and stray capacitance at the Pin PDK. This will improve bandwidth and noise.

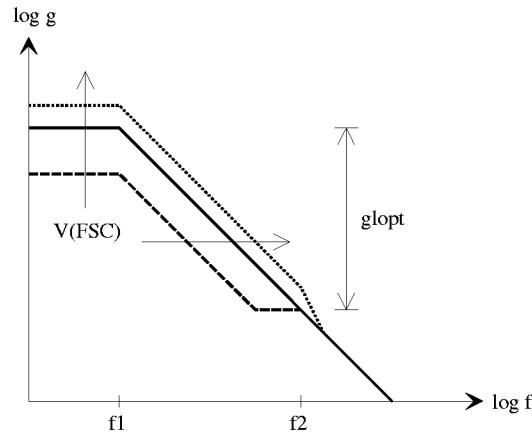

A parallel amplifier technique is used to satisfy the needs for high gain and high bandwidth. By means of its high gain path, an open loop DC gain of approximately 110 dB and a first pole frequency of  $f_1 \approx 60$  kHz is achieved. The pole frequency of its wideband path is set to  $f_2 \approx 10$  MHz. The control input FSC (Frequency Shift Control) facilitates the correct adjustment of the frequency response slopes of the two contributing amplifiers versus production tolerances (see section "FSC Adjustment").

The total closed loop gain (amplifier gain + laser efficiency + optical path attenuation + photo diode sensitivity) is controlled at the Pin GADJ (Gain ADJust).

Depending on tolerances of the optical parameters, the closed loop gain is adjusted by a control voltage to obtain good loop stability and pulse shape. For a closed loop bandwidth of approximately 100 MHz, the electro-optical attenuation,  $\Delta ipd/\Delta ild$ , has to be in the order of 36 to 40 dB.

The Pin CC is a direct connection to the integrated low-pass filter of the wideband amplifier. It can be used for possible manipulations of the frequency response, e.g., reduction of the pole frequency  $f_2$ .

The output stage is capable of driving up to 180 mA laser current.

### Supervision and Switch-off

Two parameters of the servo amplifier are supervised to indicate incorrect functions.

At the input, the photo current,  $ipd$ , is compared to the reference current,  $i_{ref}$ . A loop-error signal is generated if  $ipd$  exceeds  $i_{ref}$  by more than 50%. The variable threshold current for the detector is supplied through the ITHR terminal. At the output stage, a current-limit signal is generated, slightly below limiting condition.

Both error signals are fed into the operation control unit which generates a delayed LD-off signal to shut down the output stage. The idle input is provided to power down the complete servo amplifier.

### FSC Adjustment

The function of the FSC input is depicted in the figures 11 and 12. With the control voltage  $V_{FSC}$ , the gain of the high gain amplifier is varied, keeping its pole frequency  $f_1$  constant. The effect is a shift of the low frequency slope of the frequency response. Concerning the transient response, a left shift of the low frequency slope (dashed line) divides the transient response into two different slopes, depending on the pole frequencies  $f_1$  and  $f_2$ . Settling time is significantly increased. A right shift (dotted line) however causes an overshoot of the step response. Both deviations from the optimum frequency response yield amplitude errors for the short write and off pulses. It is recommended not to exceed  $V_{FSC}$  above the optimum value, in order to not decrease loop stability.

Figure 11. Principle of open loop frequency response

Figure 12. Transient response (closed loop)

## Typical Operating Conditions

14930

Figure 13. Open loop frequency response

(Simulation:  $V_{CC} = 5$  V,  $T_{amb} = 25^\circ\text{C}$ ,

$V_{GADJ} - V_{REF} = V_{FSC} - V_{REF} = 0$  V)

Figure 14. Simulation circuit

Figure 15. DC gain variation vs.  $V_{GADJ}$ ,

$V_{FSC} = 2.5$  V, (Simulation:  $VCC = 5$  V,  $T_{amb} = 25^\circ\text{C}$ )

Figure 16. DC gain variation vs.  $V_{FSC}$ ,

$V_{GADJ} = 2.5$  V (Simulation:  $VCC = 5$  V,  $T_{amb} = 25^\circ\text{C}$ )

Figure 17. Input compression (gain vs. input current, iref)

Figure 18. Bias voltage for photo diode vs iref

## High Frequency Modulator

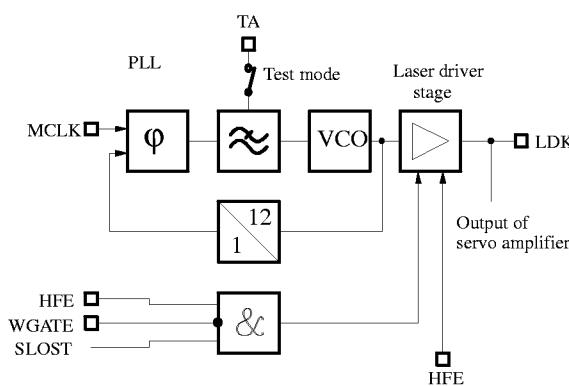

A High Frequency Modulator (HFM) is integrated on the chip to reduce mode hopping noise of the laser during read mode by weak modulation. The HFM comprises a PLL and a laser driver stage. The VCO frequency is controlled at 12 times the master clock frequency which corresponds to a HFM frequency range of 288 MHz to 456 MHz. The current swing of the laser driver stage is externally adjusted at the Pin HFV (IHFMpp  $\approx 6 \times (VCC - 0.9\text{ V}) / RHFV$ ; max. 5 mA), and enabled by the condition: HFE  $\times$  WGATE  $\times$  SLOST.

For test reasons, the VCO control signal is monitored to the test output, TA. It is separated for TM = H (test mode, see section "Serial Interface").

Figure 19. Simplified block diagram of HFM

## Power Generators

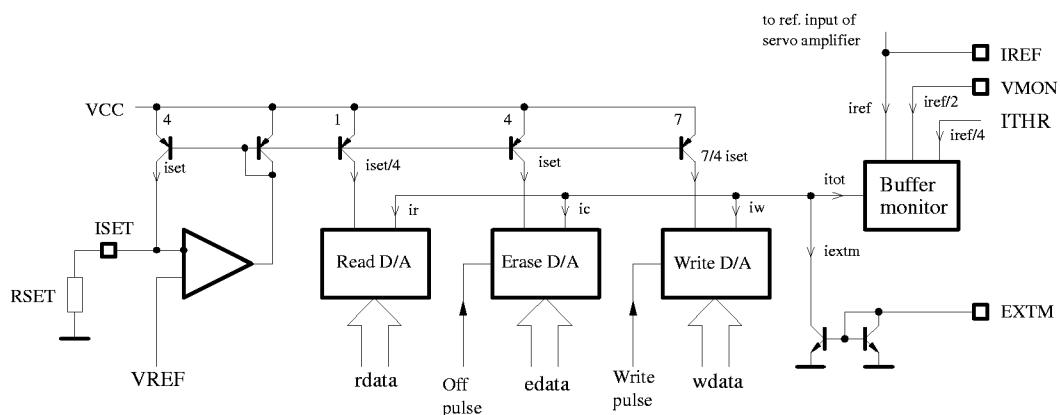

Read, erase, and write levels are generated by 3 D/A converters with 4-bit resolution each. Their weighting ratio is 1:4:7. According to the optical efficiency, the reference currents are set by the external resistor RSET.

The read current  $ir$  is continuously contributing to the total current,  $tot$ , whereas erase current,  $ie$ , and write current,  $iw$ , are switched according the off-pulse and write-pulse signals from the pulse-width generators. Furtheron, an external analog modulation current can be added at the Pin EXTM. The buffer/ monitor block splits the total current into the reference current,  $iref$ , for the servo loop, the monitor current at the Pin VMON, and the threshold current  $ITHR$  for the servo loop monitor. Their weighting ratio is 4:2:1.

## Equations for DA Currents

$$ir = \frac{iset}{4} \times \frac{rdata}{4}$$

$$ie = iset \times \frac{edata}{4}$$

$$iw = \frac{7}{4} iset \times \frac{wdata}{4}$$

## Equations for Buffer Monitor

$$itot = ir + ie + iw + iextm$$

$$iref = \frac{4}{7} itot$$

## DA Current Examples

$$RSET = 11.2\text{ k}\Omega \rightarrow iset = 2.5\text{ V} / 11.2\text{ k}\Omega = 224\text{ }\mu\text{A}$$

|            | Power Data | DA Output Currents<br>( $\mu\text{A}$ ) |      |     | Contributions to $iref$<br>( $\mu\text{A}$ ) |          |          |

|------------|------------|-----------------------------------------|------|-----|----------------------------------------------|----------|----------|

|            |            | ir                                      | ie   | iw  | $iref,r$                                     | $iref,e$ | $iref,w$ |

| 1 (LSB)    | 14         | 56                                      | 98   | 8   | 32                                           | 56       |          |

| 4          |            | 56                                      | 224  | 392 | 32                                           | 128      | 224      |

| 9 (preset) | 126        | 504                                     | 882  | 72  | 288                                          | 504      |          |

| 15 (max)   | 210        | 840                                     | 1470 | 120 | 480                                          | 840      |          |

Figure 20. Simplified block diagram of power generator

## Pulse Width Generators

This function block generates the signals for the write pulse train and the off pulse, switching the D/A converters for write and erase levels respectively.

### General

A mark on the optical disc is generated by a write pulse train during DATAIN1 is high. The duty cycle of the separated pulses corresponds to the one of the master clock MCLK. Due to the thermal interference on the disc, the individual pulses merge to one mark. The mark is delimited by one off pulse, "cooling" down the disc material.

Three principal write pulse schemes, described by FLC (relative widths of First-/Last-/Cool-pulse), can be selected by setting the three parameters FBL (First Bottom Level), LPL (Low Pulse-chain Level), and AOP (Add One Pulse), (see figure 9 "Write Schemes"). FLC = 1:1:1 is the default setting. It is also possible to set any other combination.

Table 1.

| FLC           | FBL | LPL | AOP | Tfd | Tcw |

|---------------|-----|-----|-----|-----|-----|

| 1 : 1 : 1     | L   | H   | H   | 4   | 2   |

| 0.5 : 0.5 : 1 | H   | H   | L   | 0   | 0   |

| 1.5 : 0.5 : 1 | L   | L   | L   | 0   | 0   |

An additional feature is implemented to slightly shift the mark boundaries on the optical disc. The width of each first write pulse, and the off pulse width can be varied in fractions of the master clock period, Tw. The according shift parameters, Tfd and Tcw, are stored in two registers. Tfd is assigned to the delayed start of the first write pulse in steps of Tw/8 with a value range of 0 to 7. Tcw is assigned to the lengthening of the off pulse in steps of

Tw/4 with a value range of 0 to 6. The default values of Tfd and Tcw are also displayed in the table above.

A special write pulse width parameter, Tfd3, is enabled by the M3T signal. It is provided simultaneously with the short data pulses Tmk = 2Tw.

### Circuit Description

The pulse generation circuit comprises two parallel paths for the write pulses and the off pulse respectively. A D-flip-flop for DATAIN1 synchronization, and the Interpolator PLL for pulse width variations are common for both paths.

The write pulse generator is enabled by the synchronized data DATAINs = H. At that time, the interpolator is addressed by the Tfd parameter.

The off-pulse generator is enabled by DATAINs = low and the interpolator is now addressed by the Tcw parameter. With OPE = L, the off pulse is completely suppressed.

Both write pulses and erase level are enabled by the WGATE signal.

The interpolator enables the small pulse widths variations in steps of Tw/8 or Tw/4 respectively by the use of a PLL circuit. Depending on the input data, a shifted master clock is generated. For test reasons, the PLL control signal is monitored to the test output TB. It is separated for TM = H (test mode, see chapter "Serial Interface").

### Digital External Modulation (DEM)

The versatility of the U8601B is further increased by the DEM feature. It allows the direct switching of the write and erase levels through the DATAIN1 and the M3T terminals independent from the WGATE state. The DEM mode is activated by a serial command (see chapter "Serial Interface").

Figure 21. Simplified block diagram of pulse width generators

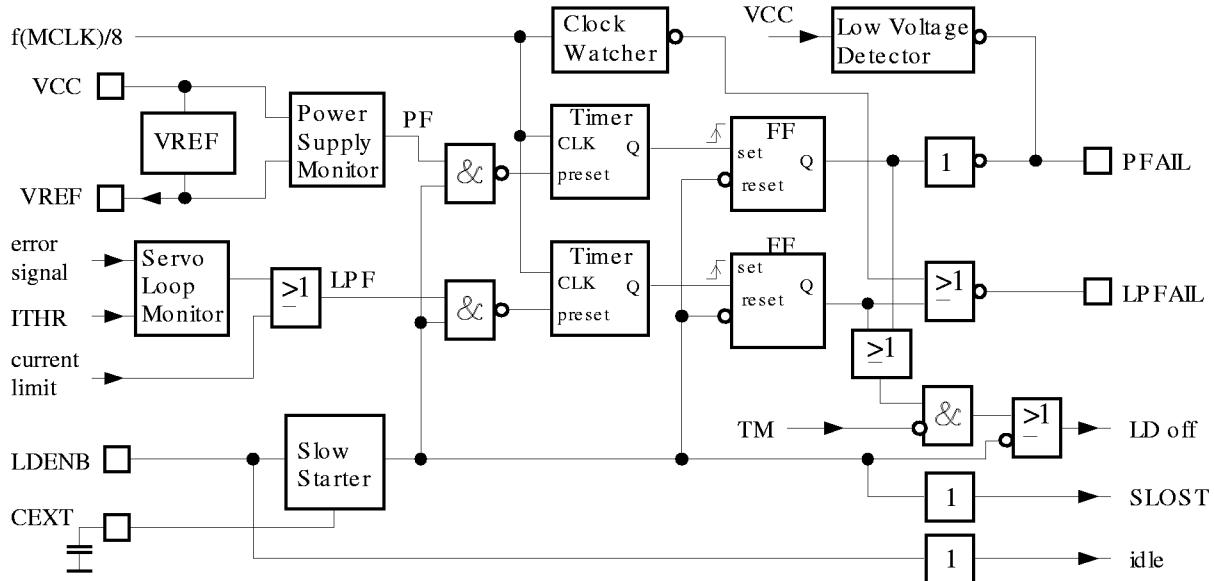

## Operation Control Unit

Figure 22. Block diagram of operation control unit

### PFAIL signal indicates

- Power supply voltage out of window

### LPFAIL signal indicates

- LDK current reaches limiting range

- LDK output transistor saturates

- Photo current exceeds reference current

- No master clock available

### Failure Conditions

Power supply monitor:  $V_{CC} < 4.5 \text{ V}$  to  $4.75 \text{ V}$

$V_{CC} > 5.25 \text{ V}$  to  $5.6 \text{ V}$

Low voltage detector:  $V_{CC} = 1.5 \text{ V}$  to  $3.5 \text{ V}$

Current limiter:

$i_{LDK} > 170 \text{ mA}$  to  $280 \text{ mA}$

Servo loop monitor:

$i_{PDK} > 1.5 \times i_{ref}$

Clock watcher

$f_{MCLK} < 8 \text{ MHz}$

### Timing Conditions

Timer:  $T_{fail} = 120 \times T_w$  to  $132 \times T_w$

$T_{fail} @ f_{MCLK} = 4 \mu\text{s}$  to  $4.4 \mu\text{s}$

Slow Starter:  $T_{pon} = 1 \text{ ms}$  to  $2 \text{ ms}$

$T_{poff} < 2 \mu\text{s}$

### Idle Mode (LDENB = low)

Slow starter circuitry and the VREF generator remain active in idle mode.

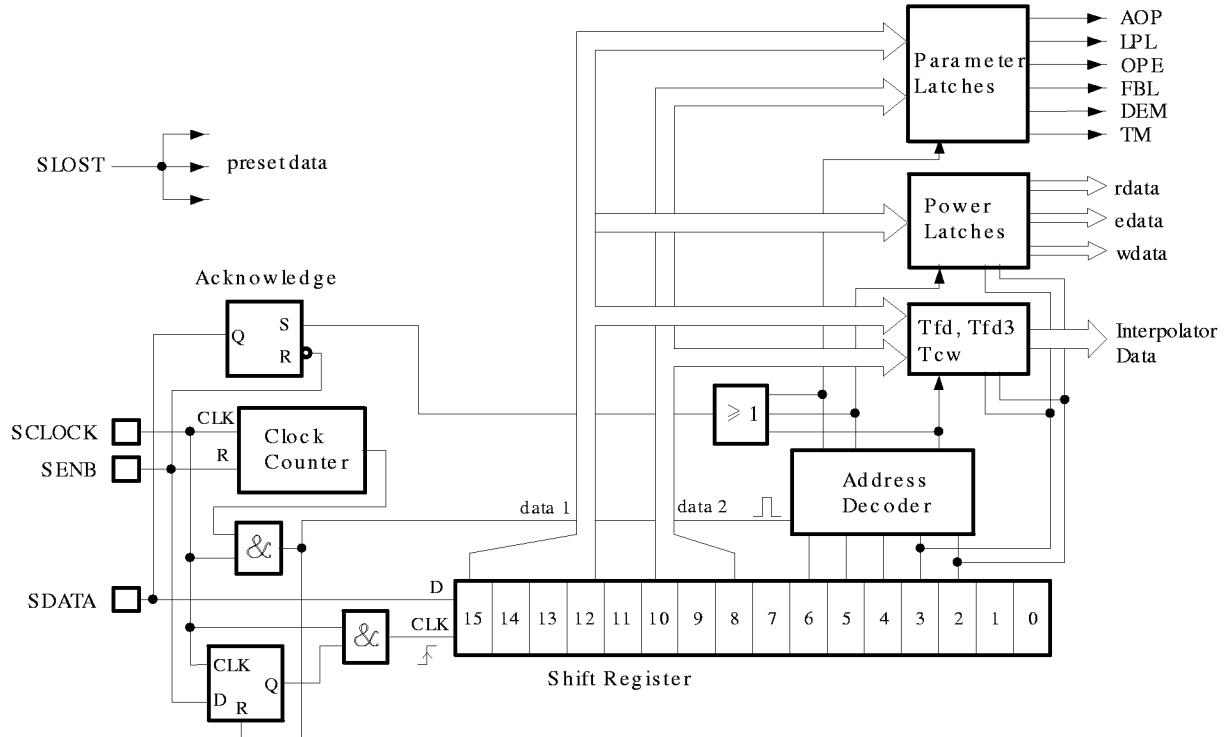

## Serial Interface

Figure 23. Simplified block diagram of serial interface

## Data Assignment Table

| 16      | 15    | 14  | 13  | 12  | 11    | 10 | 9   | 8   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0                   |                 |       |

|---------|-------|-----|-----|-----|-------|----|-----|-----|---------|---|---|---|---|---|---|---------------------|-----------------|-------|

| ACK out | data1 |     |     |     | data2 |    |     |     | address |   |   |   |   |   |   |                     | data assignment |       |

|         |       |     |     | lsb |       |    |     | lsb |         |   |   |   |   |   |   |                     | data1           | data2 |

| L       | D     | D   | D   | D   | x     | x  | x   | x   | H       | L | L | L | L | x | x | rdata               | —               |       |

| L       | D     | D   | D   | D   | x     | x  | x   | x   | H       | L | L | L | H | x | x | edata               | —               |       |

| L       | D     | D   | D   | D   | x     | x  | x   | x   | H       | L | L | H | L | x | x | wdata               | —               |       |

| L       | AOP   | LPL | OPE | FBL | x     | x  | DEM | TM  | x       | H | L | L | H | x | x | parameter set       |                 |       |

| H       | x     | x   | x   | x   | x     | x  | x   | x   | H       | L | H | x | x | x | x | not used            |                 |       |

| L       | x     | D   | D   | D   | x     | D  | D   | D   | H       | H | L | L | L | x | x | Tfd                 | Tcw             |       |

| L       | x     | D   | D   | D   | x     | x  | x   | x   | H       | H | L | L | H | x | x | Tfd3                | —               |       |

| H       | x     | x   | x   | x   | x     | x  | x   | x   | H       | H | L | H | x | x | x | not used            |                 |       |

| H       | x     | x   | x   | x   | x     | x  | x   | x   | H       | H | H | x | x | x | x | not used            |                 |       |

| H       | x     | x   | x   | x   | x     | x  | x   | x   | L       | x | x | x | x | x | x | U8601B not selected |                 |       |

rdata: read power data

preset: 9

edata: erase power data

preset: 9

wdata: write power data

preset: 9

Tfd: parameter for start delay of 1st write pulse

preset: 4

Tfd3: parameter for start delay of 1st write pulse enabled by the M3T flag

preset: 4

Tcw: parameter for off pulse lengthening

preset: 2

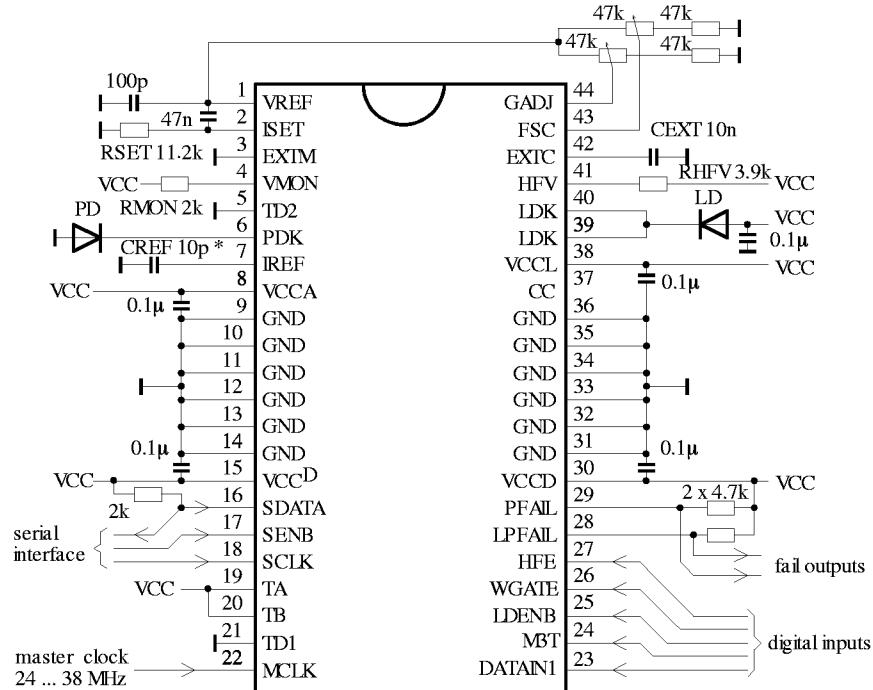

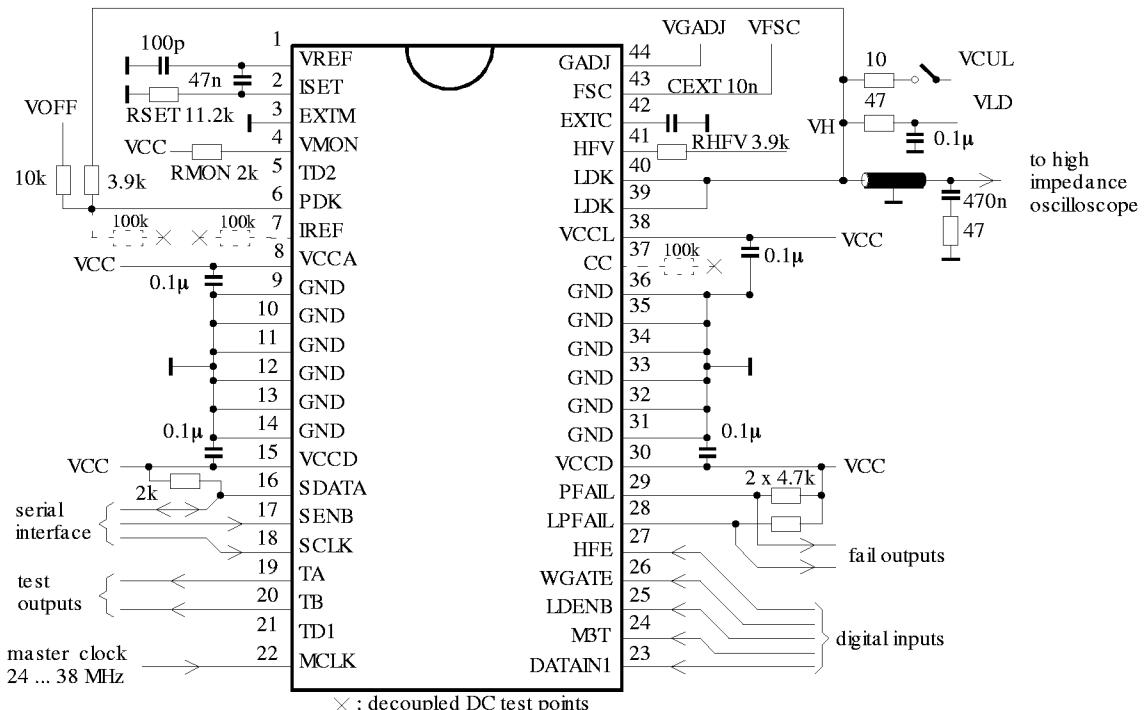

## Typical Operating Circuit

\*: value of CREF should be approx. corresponding to total capacitance of PD

Figure 24.

## Test Circuit (Electrical Feedback)

Figure 25.

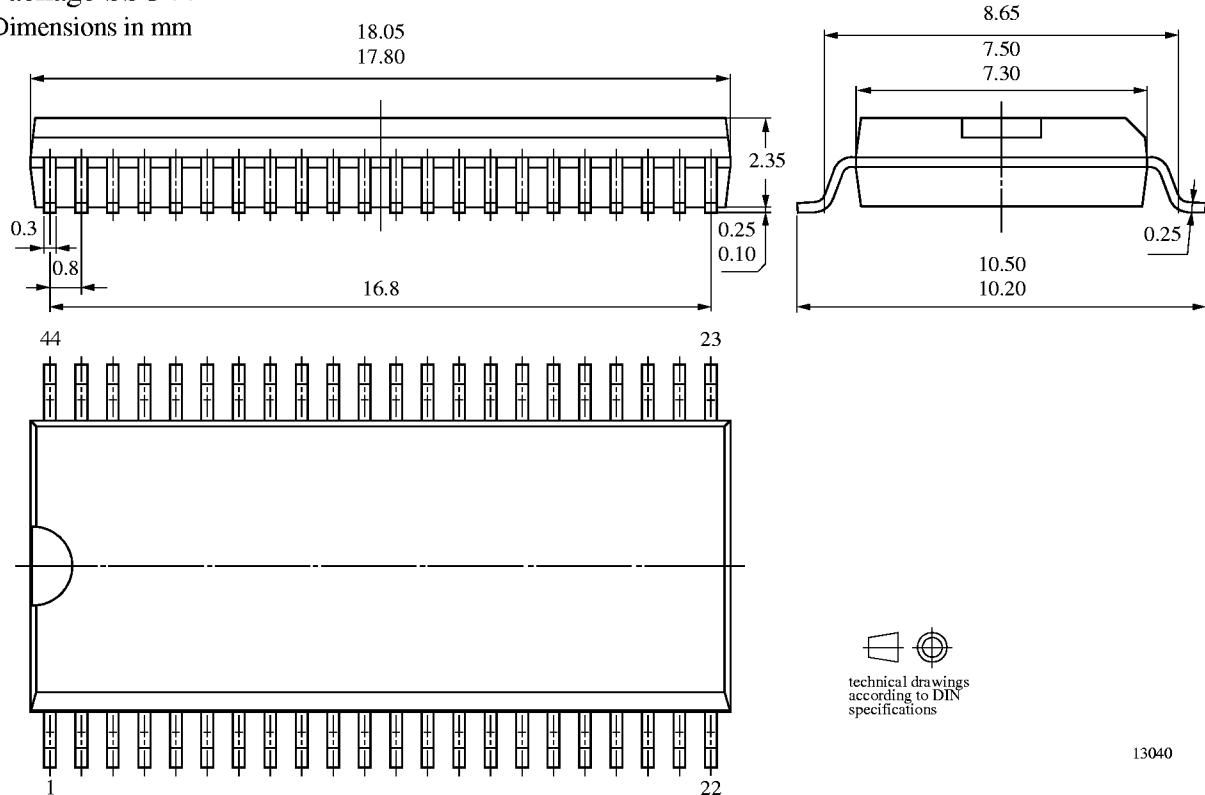

## Package Information

### Package SSO44

Dimensions in mm

technical drawings

according to DIN

specifications

13040

## Ozone Depleting Substances Policy Statement

It is the policy of **TEMIC Semiconductor GmbH** to

1. Meet all present and future national and international statutory requirements.

2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC Semiconductor GmbH** has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC Semiconductor GmbH** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

**We reserve the right to make changes to improve technical design and may do so without further notice.**

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify TEMIC Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany

Telephone: 49 (0)7131 67 2594, Fax number: 49 (0)7131 67 2423